`` 1

BAB I

DASAR-DASAR ELEKTRONIKA DIGITAL

Pada bahan ajar ini dan berikutnya kita akan mempelajari

Elektronika Digital. Bahan ajar ini membahas dasar-dasar

elektronika digital, yaitu pengertian tentang logika biner dan

bilangan biner, beberapa pengertian dan penerapan pintu

logika, rangkaian elektronika dibalik pintu-pintu logika, dan

terakhir tentang flip-flop. Pada bab-bab terakhir pembahasan

kita lanjutkan hingga mencakup komponen-komponen digital

yang lebih canggih. Sudah barang tentu kita tak akan

1.1 SISTEM BILANGAN), (b) Simbul flip-flop JK Tabel 1-17. Tabel kebenaran JK FF Ck J K Q n+1

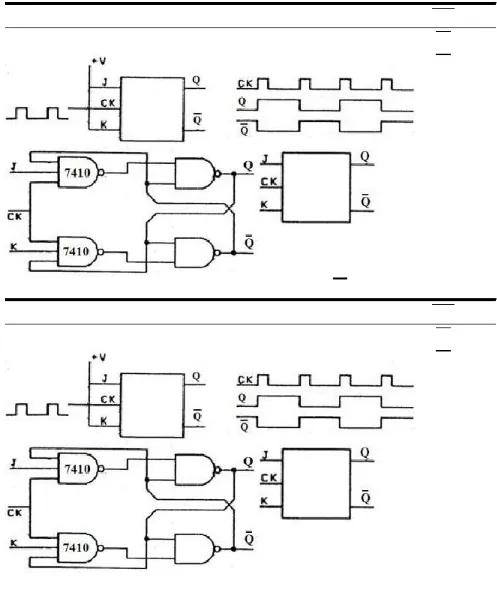

Dari tabel kebenaran tampak bahwa bila kedua maskan ada pada keadaan L maka keluaran akan berubah keadaan setiap kali CK menjadi H. Agar jelas ini dilukiskan dengan diagram timing (Gambar 1-29). (a)

17

Gambar 1-30. (a) Flip-flop JK dengan preset dan clear (b) Simbul flip-flop JK Tabel 1-18. Tabel kebenaran Flip-flop JK dengan preset dan clear PR CLR J K G

Q n+1

1 n Q

L X X X X Tak tentu Tak tentu L H X X X L H H L X X X H L H H X X X Q

n Q

Masukan CK disebut masukan clock. Tampak bahwa masukan PR dan CLR berlaku seperti masukan RS pada RS LATCH. Flip-flop JK masih mempunyai masalah yaitu isyarat pada CK harus amat sempit, yaitu harus lebih sempit dari waktu propagasi pintu togika dan latch. Agar bekerja baik, pulsa CK tak boleh lebih lebar dari 30 nS. Pulsa sempit seperti ini dapat dibuat suatu monostabil. Masalah pulsa trigger sempit ini dapat diatasi dengan menggunakan flip-flop dengan trigger tepi (edge-triggered flip-flop) atau dengan flip-flop master slave. Cara kerja edge-triggered flip-flop dapat diterangkan dengan diagram timing seperti pada Gambar 1-31 untuk pentriggeran tepi negatif (negativ edge triggering). Pada Gambar 1-31 (a) tanda pada masukan CK menyatakan bahwa keadaan masukan akan ditransfer kepada keluaran pada transisi negatif. Contoh flip-flop JK dengan trigger adalah 74H101, 74H102, 74H103, 74H105, 74H108 dari Texas Instruments. Flip-flop masterslave terdiri dari dua flip-flop yang dihubungkan seri, flip-flop pertama disebut master dan flip-flop kedua disebut slave. Transver keadaan masukan ke keadaan keluaran terdiri dari empat tahap, seperti ditunjukan Gambar 1-32.

18

Gambar 1-31. (a) Flip-flop JK master slave sebagai flip-flop (b) diagram timing Gambar 1-32. Keadaan masukan-keluaran Tahapan-tahapan tersebut adalah: 1 - 2 isolasi slave dari master 2 - 3 transfer data dari masukan kepada master 3 - 4 non aktifkan masukan data 4 transfer data dari master ke slave . Diagram timing untuk flip-flop masterslave JK pada Gambar 1-33 (b) Gambar 1-33. (a) Flip-flop master slave 7473 (b) Diagram timing Pada diagram timing tanpak bahwa flip-flop masterslave dapat meneruskan pulsa data pada pulsa clock no 4. Ini berlaku asalkan pulsa data lebih lebar dari 20 ns. Untuk edge triggered flip-flop pulsa sata ini tidak diterima oleh karena saat transisi negatif pulsa data sudah berakhir. Flip-f lop masterslave dengan data lock-ouc memungkinkan menerima pulsa data tanpa isyarat bahwa data harus stabil selama pulsa clock pada keadaan H