ORGANISASI KOMPUTER

Bentuk Operasi Pada ALU

Untuk melaksanakan tugasnya ALU dibantu oleh register Y dan Z. Register Y berfungsi untuk

menahan suatu data yang akan diproses oleh ALU menunggu data ke dua, karena untuk proses yang menggunakan dua data, kedua data tersebut

harus masuk secara bersamaan. Sedang register Z digunakan untuk menampung sementara hasil

Misal akan dilakukan operasi matematis di

bawah ini :

R3

R1 + R2

Maka langkah-langkah yang dilakukan adalah

sebagai berikut :

1. R1

out, Y

in2. R2

out, Add, Z

inEksekusi Sebuah Instruksi

Untuk melaksanakan sebuah instruksi secara lengkap, langkah-langkah yang diperlukan adalah sbb:

Misal pada instruksi Add R1,(R3) 1. Baca instruksi

2. Ambil operand yang berada di memory (dengan alamat yang tersimpan di R3)

Untuk langkah-langkah di atas maka prosessor

memberikan urutan sinyal control seperti

di bawah ini :

1. Pc

out, MAR

in, Read, Clear Y, Set Carry-in to

ALU, Add, Z

in2. Z

out, PC

in, WMFC

3. MDR

out, IR

in4. R1

out, Y

in5. R3

out, MAR

in, Read, WMFC

6. MDR

out, Add, Z

inPenjelasan :

1. Mula-mula prosessor mengambil instruksi yang alamatnya tersimpan pada PC, sambil menunggu

datangnya instruksi dari memori, PC mengupdate isinya (ditambah dengan 1)

2. Setelah instruksi didapat, instruksi ini diterjemahkan oleh rangkaian control melalui IR, dan didapatkan instruksi Add R1,(R3)

3. Operand pertama letaknya di register langsung di bawa ke register Y, sedang operand ke dua di baca dari

memori yang alamatnya disimpan di register R3.

4. Ketika operand kedua didapatkan langsug di bawa ke ALU untuk dijumlahkan dan hasilnya disimpan di

Branching

Sebagaimana sudah kita ketahui untuk melakukan

proses branch maka prosessor akan mengupdate isi PC sebelumnya dengan alamat baru yang akan

dieksekusi.

Pengubahan isi PC dilakukan dengan menambah isi PC dengan nilai offset X. Misal pada saat CPU

mengeksekusi instruksi di alamat 1000 yang berisi branch 1050, maka X harus berisi 49.

Eksekusi dari program diatas adalah sbb :

1. PC

out, MAR

in, Read, Clear Y, Set carry-in to

ALU, Add, Z

in2. Z

out, PC

in, WMFC

3. MDR

out, IR

in4. PC

out, Y

in5. Offset-field-of-IR

out, Add, Z

inPENGERTIAN URUTAN SINYAL- SINYAL

CONTROL (SEQUENCE OF CONTROL

SIGNALS)

Untuk melaksanakan suatu instruksi, CPU

mempunyai beberapa cara utk

membang-kitkan sinyal control dlm urutan yang benar.

Dua cara membangkitkan sinyal yang umum

adalah :

•

Hardwired control

Hardwired Control

- Memerlukan pengaturan waktu untuk tiap step

secara tepat.

- Dapat dilakukan dg menggunakan counter yg

dikendalikan oleh clock, dg asumsi:

Tiap step memerlukan waktu yang sama.

Tiap state/ count dari counter tsb

Krn itu sinyal control yang diperlukan secara

unik / khas ditentukan oleh :

- Isi control step counter

- Isi instruction register

- Isi condition code dan status flag.

Status flag : sinyal - sinyal yang mewakili

Perhatikan gambar control unit

organization.

Decoder - encoder block merupakan

suatu rangkaian combinational yang

menghasilkan output control yang

Gb. A. Control Unit Organization

Clock Control Step Counter

Gb. B. Pemisahan Fungsi Decoding dan Encoding

Clock Control Step

Gambar A dan B di atas adalah blok diagram untuk menghasilkan sinyal kontrol yang digunakan

untuk mengeksekusi suatu instruksi, yang

diterjemahkan dalam beberapa sinyal kontrol dari

instruction decoder (INS1 … INSm).

Sinyal step docoder dan instruction decoder

dipadukan dengan sinyal dari status flag

dan condition codes, menghasilkan sinyal

control individu seperti Pc

out, Y

in, Add, End,

dan sebagainya.

Contoh :

Misal untuk mengimplementasikan fungsi

logic:

Zin = T

1+ T

6. Add + T

5. BR + …

Gb. Diagram rangkaian untuk

sinyal kontrol Zin

ADD BR

T5 T6

T1

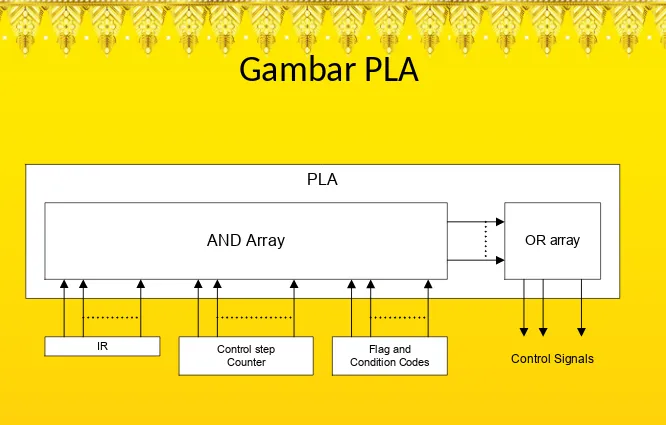

PLA (Programmable Logic Array)

Dari gambar di atas dapat kita lihat bahwa untuk

mengimplementasikan suatu fungsi dapat diguna-kan gerbang-gerbang dasar. Dan untuk untuk me-nerapkan hal ini digunakan VLSI (Very Large Scale Integration) Technology. Dalam Chip VLSI

PLA ter-diri dari barisan gerbang AND yang

diikuti de-ngan barisan gerbang OR dan

dapat digunakan untuk menerapkan

fungsi-fungsi logika kombinasi dari beberapa

variable. Semua kombinasi rangkaian dalam

Encoder dan Decoder dapat diterapkan

Gambar PLA

PLA

AND Array OR array

IR Control step

Counter

Flag and

CPU-Memory Interaction

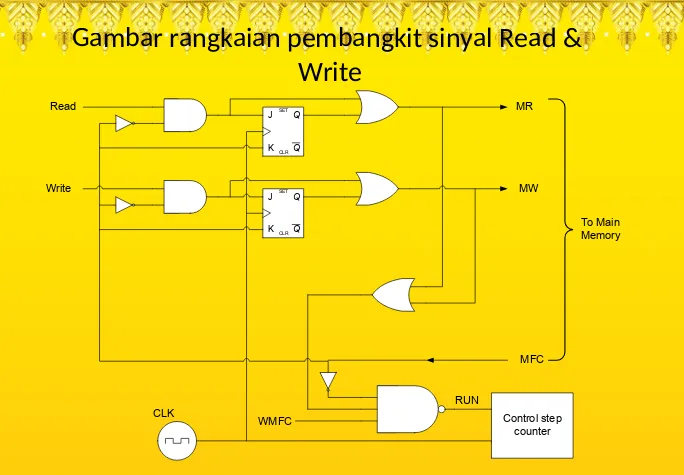

Interaksi antara CPU dengan memory adalah

berupa proses menulis dan membaca data

oleh CPU ke dan dari memory. Dimana bus

data external dari CPU terhubung dengan

MDR.

Di bawah ini adalah gambar rangkaian yang

Gambar rangkaian pembangkit sinyal Read &

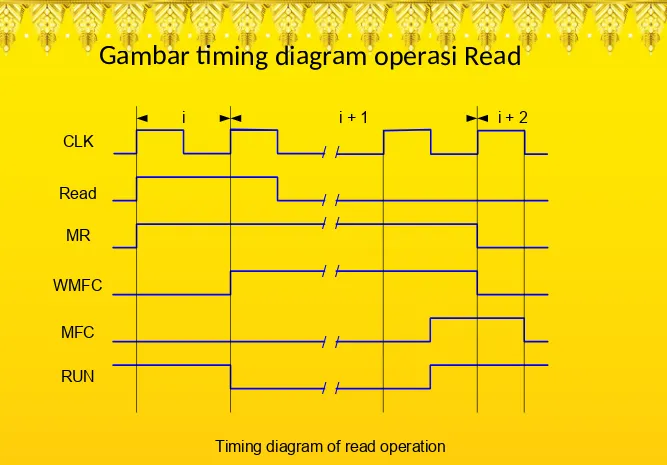

Gambar timing diagram operasi Read

Rangkaian di atas dapat digunakan untuk memory yang berkecepatan tinggi (fast memory) maupun rendah (slow memory). Fast memory

membutuhkan satu clock cycle untuk setiap

transfer data sedang slow memory membutuhkan lebih itu.

Perhatikan gambar timing diagram untuk

operasi read memory. Saat sinyal read

diberikan (high) maka sinyal MR (memory

read) juga ikut ‘high’. Dan sinyal MR ini

akan tetap ‘high’ meskipun sinyal read

telah berubah ‘low’. Saat itulah CPU

mengaktifkan WMFC (wait memory

Bila data telah terkirim, memory mengirim

sinyal MFC. Sinyal ini akan mematikan sinyal

read dari gerbang and dan flip-flop (pin K)

sekaligus menghentikan sinyal run dari

Microprogrammed Control

Merupakan cara lain untuk membangkitkan sinyal

kontrol. Hal-hal utama mengenai microprogrammed control ini adalah sbb:

Pengaturan sinyal kontrol dilakukan dengan

microinstruction (lihat gambar di bawah).

Control word (CW) adalah word yang terdiri dari

beberapa bit, dimana tiap bitnya mewakili berbagai sinyal kontrol.

Setiap langkah / step pada urutan control (control

sequence) sebuah instruksi mendefinisikan

Urutan perintah dalam CW menyatakan urutan sinyal control dari sebuah instruksi mesin

(machine instruction), atau merupakan

microroutine bagi instruksi mesin tsb. Dan satu baris (word) pada CW disebut sebagai

microinstruction.

Microprogram suatu komputer disimpan dalam

memory khusus yang disebut control store.

Control unit dapat menghasilkan sinyal kontrol

Organisasi control unit untuk microprogrammed digambarkan sebagai berikut :

IR

Starting address generator

µPC

Control Store Clock

Untuk membaca CW secara berurutan digunakan

microprogram counter (µPC). Setiap instruksi baru masuk ke IR, maka sebuah “starting address

generator” diload ke dalam µPC. Berikutnya secara otomatis meng-increment alamat yang diberikan dengan ditriger oleh clock.

Dalam praktisnya organisasi control unit tidaklah cukup seperti gambar di atas. Gambar diatas digunakan hanya untuk instruksi yang berjalan

Microinstruction dengan instruksi Branch

Address Microinstruction

0 PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin

1 Zout, PCin, WMFC 2 MDRout, IRin

3 Branch to starting address of appropriate microroutine ………

25 PCout, Yin, If N=0 then branch to microinstruction 0 26 Offset-field-of-IRout, Add, Zin

Untuk mengimplementasikan microroutine dengan

Dengan menggunakan organisasi di atas

maka dapat dilakukan instruksi branch.

Untuk branch tanpa syarat dilakukan

dengan memasukkan nilai alamat yang

akan dituju (di dapat dari instruksi) ke µPC.

Sedang untuk branch bersyarat hampir sama

dengan cara di atas dan dipadukan dengan

informasi dari status flag dan condition

Microinstructions

Dalam penulisan microinstructions pemakaian bit secara individu untuk setiap sinyal kontrol akan sangat panjang jika banyak sinyal kontrol yang harus dikendalikan melalui penulisan CW.

Untuk menghitung jumlah bit CW yang diperlukan maka dapat diperhitungkan dari :

Jumlah register (R0, R1, R2, …)

Jumlah operasi yang dilakukan (read, write, clear

Y, Set Carry-in, WMFC, …)

Jumlah fungsi arithmatic & logic (add, subtract,

Jika ditotal kira-kira diperlukan sebanyak 42 sinyal

kontrol. Dan ini ukuran cukup panjang bagi sinyal kontrol. Untuk itu dilakukan penyederhanaan

dengan cara mengelompokkan sinyal kontrol berdasarkan fungsinya dan kombinasi bit.

Disamping dalam prakteknya terdapat hal-hal sbb:

Sebagian besar sinyal ini tidak diperlukan secara

contoh : sinyal Add pada ALU, Sinyal read dan Write,

R0 out dan R1 out dll). Sehingga beberapa mikro

instruksi kebanyakan dapat diwakili dalam satu mikrooperasi.

Untuk operasi ALU dapat diwakili dengan 4 bit

untuk 16 fungsi yang berbeda (Add, Sub, OR, And, ….. XOR).

Sinyal kontrol keluaran untuk masing-masing

register dapat dikelompokkan.

Gambar pengelompokan sinyal kontrol

F1 (4 bit) F2 (3 bit) F3 (2 bit) F4 (2 bit)

F5 (4 bit) F6( 2 bit)

0000 : No transfer 0001 : PC out

1000 : SOURCE out 1001 : DESTIN out 1010 : TEMP out 1011 : Address out

000 : No transfer 001 : PC in

00 : No transfer 01 : MAR in 10 : MDR in 11 : TEMP in

00 : No transfer 01 : Y in

0:Carry-in = 0 1:Carry-in = 1

0 : No action 1 :WMFC

Dengan pengelompokan seperti di atas 42 sinyal kontrol dapat disederhanakan menjadi 20 bit. Pengkodean dari 42 bit sebenarnya dapat

dikodekan hanya dengan 6 bit (26 = 64 bit),