LAPORAN

PRAKTIKUM MIKROKONTROLLER

UNIVERSAL SYNCHRONOUS AND ASYNCHRONOUS

SERIAL RECEIVER TRANSMITTER (USART)

Oleh :

Mei Rahayu Puspitasari

1541160040

JTD 2B

JARINGAN TELEKOMUNIKASI DIGITAL

JURUSAN TEKNIK ELEKTRO

POLITEKNIK NEGERI MALANG

2017

UNIVERSAL SYNCHRONOUS AND ASYNCHRONOUS SERIAL RECEIVER TRANSMITTER (USART)

I. Tujuan

Setelah melakukan praktikum ini, mahasiswa diharapkan mampu:

1. Menyusun algoritma, flowcart dan program dengan memanfaatkan unit USART, unit ADC dan unit input-output ATMega16 untuk proses telemetri dan telekontrol.

2. Mengaplikasikan program komunikasi Serial dengan menggunakan ATMega16.

II. Alat dan Bahan

1. Code Vision AVR (Software) 2. Progisp (Software)

3. ISP Downloader : 1 Unit

4. Modul Rangkaian : 1 Unit

5. ATMega 16 : 1 Unit

6. Kabel Penghubung : Secukupnya

7. 7 segment : 1 buah

III. Teori Dasar

Universal Synchronous dan Asynchronous dan Transmitter (USART) adalah perangkat komunikasi serial yang sangat fleksibel. Fitur-fitur utama adalah sebagai berikut:

Operasi full duplex

Operasi asinkron atau sinkron

Master atau slave clock pada operasi sinkron

Generator baud rate resolusi tinggi

Mendukung frame serial dengan 5, 6, 7, 8, atau 9 bit data dan 1 atau 2 bit stop

Paritas ganjil atau genap

Deteksi data over run

Deteksi kesalahan framing

Filter terhadap gangguan termasuk deteksi bit start palsu dan low pass filter digital

Mode Komunikasi Multi-prosesor

Kecepatan ganda pada mode komunikasi asinkron

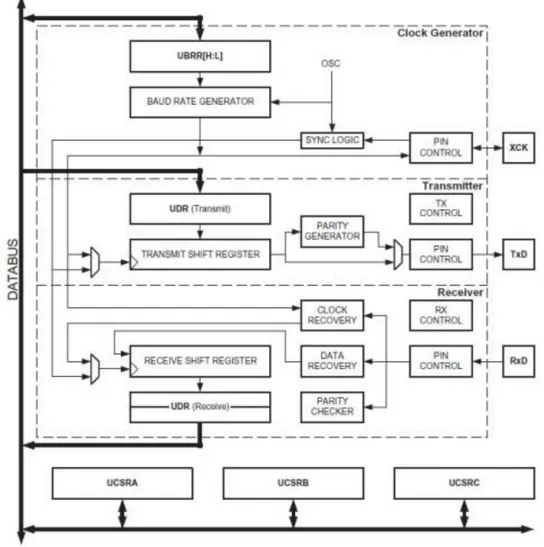

Blok diagram sederhana dari USART ditunjukkan pada Gambar 5.1 dan untuk Register I/O dan pin I/O yang dapat diakses ditampilkan dengan huruf tebal seperti Register UCSRA, UCSRB, UCSRC, UDR dan UBRR, serta pin RxD, TxD dan XCK.

Gambar 4.1. Blok Diagram USART pada ATMega 16 (ATMega16,2010;144) Dalam Gambar 4.1, kotak-kotak yang putus-putus dalam blok diagram memisahkan tiga bagian utama dari USART yaitu: Generator Clock, Transmitter dan Receiver. Register Kontrol dibagi ke semua unit. Clock pembangkit logika terdiri dari logika sinkronisasi untuk masukan clock eksternal yang digunakan oleh operasi sinkron slave dan generator baud rate. Pin XCK (Clock Transfer) hanya digunakan oleh mode Transfer Sinkron. Transmitter terdiri dari buffer register tulis, serial Shift regiseter, generator paritas dan kontrol logika untuk menangani berbagai format bingkai (frame)

serial. Buffer register tulis70 memungkinkan transfer data yang berkelanjutan tanpa ada penundaan antara frame. Pada receiver merupakan bagian paling kompleks dari modul USART karena clock dan unit pemulihan data. Unit-unit pemulihan digunakan untuk penerimaan data asinkron. Tambahan fungsi untuk unit pemulihan berupa pemeriksa paritas penerima (receiver), logika kontrol, Shift Register dan dua tingkat receive buffer (UDR). Receiver mendukung format frame yang sama seperti transmitter, dan dapat mendeteksi kesalahan frame, overrun data dan kesalahan paritas.

Untuk dapat menggunakan USART, perlu diketahui dari fungsi-fungsi masing-masing register yang ada di dalam Blok diagram pada Gambar 4.1.

Register-register tersebut sebagai berikut:

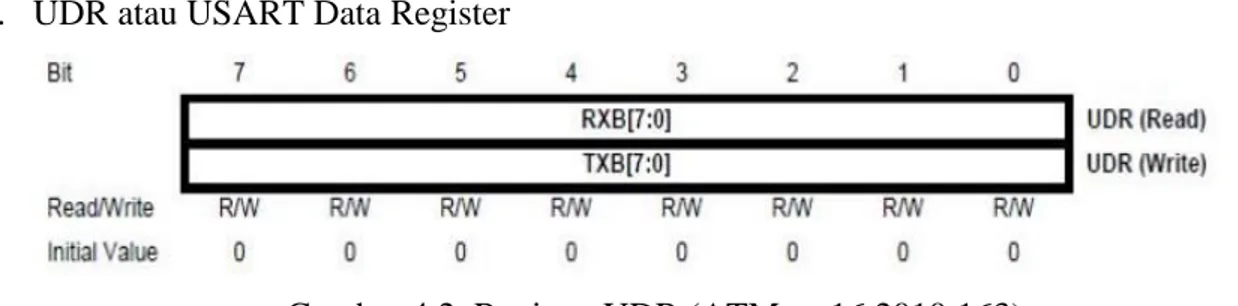

1. UDR atau USART Data Register

Gambar 4.2. Register UDR (ATMega16,2010;163)

USART Transmit Data Buffer Register dan USART Receive Data Buffer Register menggunakan alamat I/O yang sama yang disebut USART Data Register atau UDR. Transmitter Data Buffer Register (TXB) akan menjadi tujuan dari penulisan data ke lokasi register UDR sedangkan saat membaca register UDR akan mendapatkan isi dari Receiver Data Buffer Register (RXB) seperti yang ditunjukkan dalam Gambar 4.2.

2. UCSRA atau USART Control Status Register A

Nama bit-bit UCSRA ditunjukkan dalam Gambar 4.3.

Gambar 4.3. Bit-Bit Register UCSRA (ATMega16,2010;164) Keterangan bit-bit Register UCSRA adalah sebagai berikut:

Merupakan bit tanda bahwa ada data yang telah masuk secara serialmelalui pin RxD. Bernilai logika satu bila ada data masuk ke bufferpenerima dan belum dibaca, bila data sudah dibaca maka akan berubahmenjadi nol. Bit RXC ini juga digunakan untuk membangkitkan intrupsi

Receive Complete.

- Bit 6 – TXC: USART Transmit Complete

Merupakan bit tanda bila semua data sudah komplit dikirim secara serialmelalui pin TxD. Bernilai logika satu bila transmit shift register telahkosong dan tidak ada data baru dalam transmit buffer (UDR). Bit TXC iniakan berubah menjadi nol secara otomatis saat intrupsi transmit complete dikerjakan atau dapat di-nol-kan dengan menuliskan satu ke bit ini. TandaTXC juga membangkitkan sebuah intrupsi Transmit Complete.

- Bit 5 – UDRE: USART Data Register Empty

Tanda UDRE menunjukkan jika transmit buffer (UDR) siap menerimadata. Bila UDRE berlogika satu buffer kosong, berarti siap untuk ditulis.Tanda UDRE dapat membangkitkan intrupsi Data Register Empty. UDREberlogika satu untuk

menunjukkan bagian transmitter siap.

- Bit 4 – FE: Frame Error

Bit berlogika satu jika karakter berikutnya dalam buffer penerima terjadiframe error ketika menerima yaitu saat stop bit pertama dari karakterberikutnya dalam buffer penerima (receiver) adalah nol. Bit FE adalah nolketika stop bit data yang diterima adalah satu. Beri bit ini nol saat menuliske UCSRA.

- Bit 3 – DOR: Data OverRun

Bit ini berlogika satu jika kondisi over run data terdeteksi. Sebuah dataoverrun terjadi ketika buffer penerima penuh (dua karakter), ada karakterbaru yang

menunggu dalam shift Registre penerima, dan start bit baruterdeteksi. Beri bit ini ke nol saat menulis ke UCSRA.

- Bit 2 – PE: Parity Error

Bit ini berlogika satu jika karakter berikutnya dalam buffer penerimamemiliki kesalahan paritas (Parity Error) saat diterima dan pengecekan paritas telah diaktifkan

pada bagian UPM1 = 1. Beri bit ini nol saatmenulis ke UCSRA.

- Bit 1 – U2X: Double the USART Transmission Speed

Bit ini hanya berpengaruh untuk operasi asinkron. Beri bit ini nol bila menggunakan sinkron operasi. Bila bit ini diberi nilai logika satu makaakan mengurangi pembagi dari pembagi baud rate dari 16 ke 8 sehinggasecara efektif menggandakan transfer rate untuk komunikasi asinkron.

- Bit 0 – MPCM: Multi-processor Communication Mode

Bit ini memungkinkan Modus komunikasi multi-prosesor. Apabila bitMPCM diberi logika satu, maka semua frame yang diterima oleh penerimaUSART yang tidak mengandung informasi alamat akan diabaikan.Transmiiter tidak dipengaruhi oleh pengaturan MPCM.

3. UCSRB atau USART Control Status Register B

Nama bit-bitnya ditunjukkan dalam Gambar 4.4.

Gambar 4.4. Bit-bit Register UCSRB (ATMega16,2010;165) Keterangan bit-bit Register UCSRB adalah sebagai berikut:

- Bit 7 – RXCIE: RX Complete Interrupt Enable

Bit ini digunakan untuk mengaktifkan intrupsi saat ada data masuk dibuffer penerima atau saat RXC bernilai satu. Jika diberi logika satu makaintrupsi diaktifkan dan bila diberi nol maka intrupsi tidak aktif.

- Bit 6 – TXCIE: TX Complete Interrupt Enable

Bit ini digunakan untuk mengaktifkan intrupsi saat data sudah selesaidikirimkan atau saat TXC sama dengan satu. Jika diberi logika satu makaintrupsi diaktifkan dan bila diberi nol maka intrupsi tidak aktif.

- Bit 5 – UDRIE: USART Data Register Empty Interrupt Enable

Bit ini digunakan untuk mengaktifkan intrupsi saat UDRE sama dengansatu. Jika diberi logika satu maka intrupsi diaktifkan dan bila diberi nolmaka intrupsi tidak aktif.

Bit ini digunakan untuk mengaktifkan bagian penerima (receiver)USART, dan pin RxD digunakan sebagai jalur komunikasi serial. Biladiberi logika satu akan aktif dan logika nol untuk non aktif

- Bit 3 – TXEN: Transmitter Enable

Bit ini digunakan untuk mengaktifkan bagian pengirim (transmitter)USART, dan pin TxD digunakan sebagai jalur komunikasi serial. Biladiberi logika satu akan aktif dan logika nol untuk non aktif

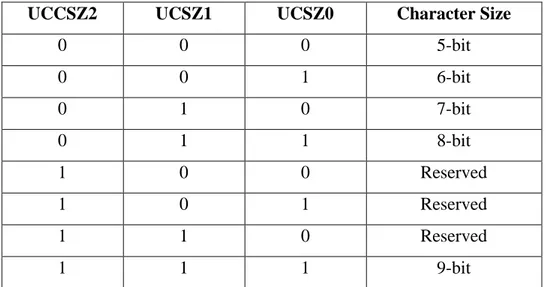

- Bit 2 – UCSZ2: Character Size

Bit UCSZ2 dikombinasikan dengan bit UCSZ1 dan UCSZ0 bit dalamregister UCSRC untuk menetapkan jumlah bit data atau ukuran karakterdalam frame untuk penerima (receiver) dan pemancar (transmitter).

- Bit 1 – RXB8: Receive Data Bit 8

RXB8 adalah bit data kesembilan dari karakter yang diterima ketikaberoperasi dengan frame serial dengan sembilan bit data. Harus dibacasebelum membaca bit rendah dari UDR.

- Bit 0 – TXB8: Transmit Data Bit 8

TXB8 adalah bit data yang kesembilan dari karakter yang akan dikirimketika beroperasi dengan frame serial dengan sembilan bit data. Harusditulis sebelum menulis bit rendah untuk UDR.

4. UCSRC atau USART Control Status Register C

Nama bit-bit dari Register UCSRC ditunjukkan dalam Gambar 4.5.

Gambar 4.5. Bit-bit Register UCSRC (ATMega16,2010;166)

Alamat lokasi register UCSRC berbagi dengan register UBRRH. Sedanguntuk keterangan bit-bit Register UCSRC adalah sebagai berikut:

Bit ini digunakan untuk memilih antara mengakses register UCSRC atauregister UBRRH. Bila diberi logika satu maka digunakan sebagai registerUCSRC.

- Bit 6 – UMSEL: USART Mode Select

Bit ini digunakan untuk memilih mode operasi komunikasi serial, biladiberi logika ‘0’ maka mode Asikron dan bila diberi logika ‘1’satu makamode Sinkron

- Bit 5:4 – UPM1dan UPM0: Parity Mode

Bit-bit yang digunakan untuk mengaktifkan dan menetapkan jenis generasi dan memeriksa paritas. Jika diaktifkan, bagian pemancar akan secara otomatis menghasilkan dan mengirim bit paritas dari data yang dikirimkan dalam setiap frame. Dan pada bagian penerima (receiver) akanmenghasilkan nilai paritas dari data yang masuk dan bandingkan dengan pengaturan UPM0. Jika ketidakcocokan terdeteksi, maka tanda bit PE diUCSRA akan bernilai satu. Untuk pengaturan bit-bit UPM1 dan UPM0ditunjukkan dalam Tabel 4.1.

UCCSZ2 UCSZ1 UCSZ0 Character Size

0 0 0 5-bit 0 0 1 6-bit 0 1 0 7-bit 0 1 1 8-bit 1 0 0 Reserved 1 0 1 Reserved 1 1 0 Reserved 1 1 1 9-bit

Tabel 4.1.Pengaturan bit-bit UPM (ATMega16,2010;166)

- Bit 3 – USBS: Stop Bit Select

Bit ini digunakan untuk memilih jumlah Bit Stop yang akan dimasukkanoleh bagian pengirim. Sedang untuk bagian penerima enerimamengabaikan pengaturan ini. Bila USBS = 0 maka diatur menggunakan 1bit stop, sedang bila USBS = 1 maka diatur mengunakan 2 bit stop.

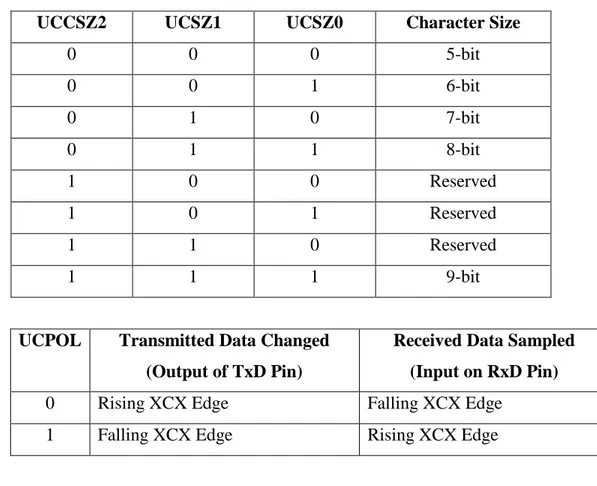

bit UCSZ1 dan UCSZ0 dikombinasikan dengan bit UCSZ2 bit dalamregister UCSRB untuk menetapkan jumlah bit data atau ukuran karakterdalam frame untuk penerima dan pemancar. Dan untuk pengaturan UCSZ2sampai UCSZ0 ditunjukkan dalam Tabel 5.2.

- Bit 0 – UCPOL: Clock Polarity

Bit ini digunakan untuk mode Sinkron saja. Untuk mode Asikron diberilogika 0. Bit UCPOL menetapkan hubungan antara perubahan output data dan sampel input data, dan clock sinkron (XCK). Untuk pengaturan bit

UCPOL ditunjukkan dalam tabel 5.3

Tabel 4.2. Kombinasi UCSZ2 sampai UCSZ0 untuk Pengaturan Ukuran Karakter (ATMega16,2010;167)

UCCSZ2 UCSZ1 UCSZ0 Character Size

0 0 0 5-bit 0 0 1 6-bit 0 1 0 7-bit 0 1 1 8-bit 1 0 0 Reserved 1 0 1 Reserved 1 1 0 Reserved 1 1 1 9-bit

UCPOL Transmitted Data Changed (Output of TxD Pin)

Received Data Sampled (Input on RxD Pin)

0 Rising XCX Edge Falling XCX Edge

1 Falling XCX Edge Rising XCX Edge

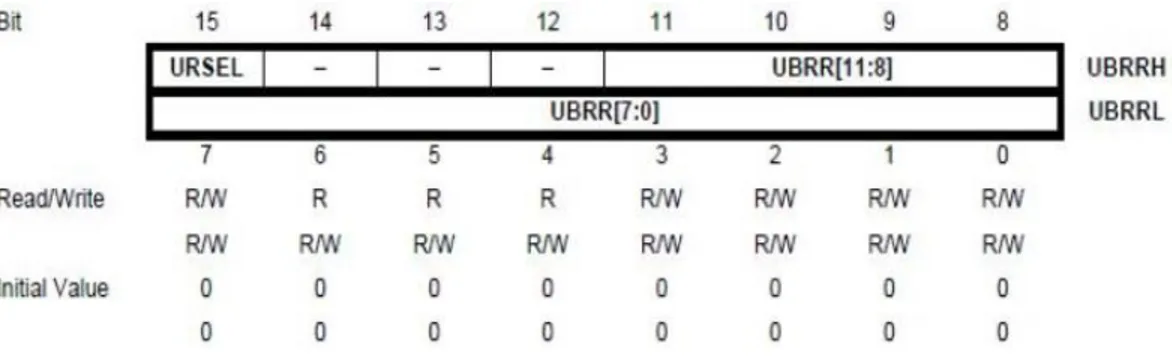

5. UBRR atau USART Baud Rate Register

UBRR terdiri dari dua buah register yaitu UBRRH dan UBRRL, registerregister ini digunakan untuk mengatur kecepatan pengiriman data atau Baud

Rate. Untuk alamat register UBRRH digunakan bersama dengan register UCSRC. Bit-bit dari UBRRH dan UBBRL ditunjukkan dalam Gambar 4.6.

Gambar 4.6. Bit-bit Register UBRRH dan UBRRL (ATMega16,2010;167)

- Bit 15 – URSEL: Register Select

- Bit yang digunakan untuk memilih penggunaan register UBRRH atau UCSRC, harus diberi logika 0 saat digunakan untuk register UBRRH

- Bit 14 sampai 12, cadangan

- Bit 11 sampai bit 0

- Merupakan register 12-bit yang berisi USART baud rate. Regiseter UBRRH ini berisi empat bit MSB, dan UBRRL tersebut berisi 8 bit LSB dari USART baud rate.

Untuk perhitungan Baud Rate dan nilai register UBRR ditunjukkan dalam tabel 5.4.

Tabel 5.4. Perhitungan Baud Rate dan nilai Register UBRR (ATMega16,2010;147)

Catatan:

1. Baud rate didefinisikan sebagai kecepatan transfer dalam bit per detik (bps). 2. BAUD = Baud rate

VI. Script pada code vision

VII. Prosedur Praktikum

1. Persiapan Program

a. Mengklik File New Project

b. Menekan tombol Yes untuk masuk ke menu

c. Memilih tipe chip, karena kita menggunakan Atmega, maka pilih yang atas

d. Pada menu Windows CodeWizard AVR, karena pada hal ini sedang melakukan praktikum input output, maka yang di setting adalah bagian Port dan Chip

e. Ketika semua sudah selesai, langkah selanjutnya Generate, Save and Exit

(Catatan : pemberian nama file sebanyak 3x, dengan nama file yang sama, hindari kalimat yang panjang, capital, dan spasi)

f. Kemudian masuk ke bagian USART, centang Tx dan Rx nya seperti pada gambar. Menu Chip Pengaturan Chip Pengaturan X_Tal

g. Setelah selesai memberi nama file, akan muncul bagian utama untuk proses pembuatan program

h. Mengisi script

i. Mengklik Compile dan Build All Project File

2. Memasukkan Program ke Modul Rangkaian Menggunakan Progisp

a. Menghubungkan modul rangkaian dengan kabel isp downloader, kemudian menghubungkan kabel-kabel female, sesuai dengan port input output-nya

b. Membuka Software progisp

c. Kemudian mengunduh file program dari komputer ke modul mikro dengan Mengklik “Load Flash”, lalu Memilih file

d. Mengklik bagian “...”, kemudian centang jtagen sehingga menjadi angka 1 Skrip tidak ada

e. Mengklik tulisan command, dan pilih menu write flash

f. Menguji modul mikro dengan mengirim menu tampilan menggunakan aplikasi Hercules.

VIII. Hasil Praktikum

Menu “1” untuk menampilkan nama “rahayu”

Menu “2” untuk menampilkan NIM“1541160040”

Menu “3” untuk menampilkan tanggal lahir “19-05-1998”

Menu “4” untuk menampilkan nomor hp “085726052337”

Menu “5” untuk menampilkan nilai adc potensiometer “0”-“255”

Menu “6” untuk menampilkan kondisi ldr “gelap” atau “redup” atau “terang”

IX. Analisis

Dalam mendeklarasi variable, yakni menggunakan unsigned char, dengan kode yang digunakan untuk membentuk angka pada seven segment adalah hexa. Untuk menampilkan secara berurutan, maka menggunakan fungsi for, dan sela waktu nya diatur dalam delay.

Menu diatur dalam fungsi if (jika 0) sehingga variabel memiliki sifat khusus untuk menampilkan satu fungsi saja.

Di bagian Usart ini terdapat ADC berupa POT untuk mengetes tegangan input yang masuk ke ATmega, dan ATmega akan mencoba membacanya, ATmega akan membaca isyarat tegangan ini jika program telah dituliskan read_adc. Untuk mengatur tegangan yang masuk ini, POT diberi putaran tertentu, agar dapat menampilkan nilai tegangan sesuai program yang telah dibentuk sebelumnya.

X. Kesimpulan

Dari hasil praktikum kali ini, dapat disimpulkan beberapa hal sebagai berikut : 1. Program yang dibuat sesuai prosedur sehingga tidak terdapat masalah yang serius. 2. Mahasiswa mengetahui bahwa ATmega 16 memiliki banyak kelebihan dan praktis

dalam penggunaan nya sehingga mungkin kedepannuya dapat dikembangkan dalam alat-alat elektronika yang bermanfaat

3. PORT untuk input dan output pada mikrokontroller bebas untuk ditetapkan pada praktikum 1 I/O USART ini. Pada bagian input hanya diperlukan satu kabel female saja untuk ditancapkan ke port input, tidak seperti praktikum sebelumnya yang membutuhkan empat kabel female. Kemudian memerlukan kabel tambahan yakni RS-232 sebagai jembatan antara PC dan ATmega.