Disain & Implementasi Command & Data Handling

System (CDHS) Pada Satelit IiNUSAT-1

MS. Hendriyawan A.

1, Thomas Sri Widodo

2, Litasari

31,2,3

Jurusan Teknik Elektro dan Teknologi Informasi, Universitas Gadjah Mada

Jl. Grafika No 2, Jogjakarta 55281

1

[email protected]

2[email protected]

3[email protected]

Abstraksi—Pada wahana satelit nano terjadi banyak proses dalam bentuk tugas yang harus diselesaikan agar misi utama bisa tercapai. Semakin banyak proses yang terjadi yang melibatkan komunikasi antar sub-sistem penyusun, maka membutuhkan pengendalian proses oleh sebuah unit yang disebut sebagai command & data handling system (CDHS). Sub-sistem CDHS berperan dalam mengatur lalu-lintas komunikasi data antar sub-sistem penyusun baik berupa informasi hasil akuisisi maupun perintah yang harus dikerjakan ke/dari stasiun bumi sesuai misi yang diemban. Dengan menggunakan mikroprosesor ARM 32-bit yang memiliki kemampuan komputasi yang cepat sangat menentukan kehandalan kinerja CDHS. Untuk mendukung operasi penanganan tugas yang kritis, dibutuhkan rancangan arsitektur perangkat keras meliputi jenis mikroprosesor utama, jalur komunikasi antar sub-sistem dan redundansi. Secara perangkat lunak, yaitu menerapkan RTOS (real time operating system) untuk mengelola tugas yang kritis secara realtime dengan waktu latensi seminimal mungkin dan menerapkan algoritma deteksi kesalahan (error detection) untuk memastikan komunikasi data berlangsung dengan benar.

Kata kunci: Mikroprosesor ARM 32-bit, Redundansi, Real Time Operating System (RTOS), Error Detection.

I. PENDAHULUAN

Satelit IiNUSAT-1 merupakan subyek penelitian bersama yang dijalankan oleh 6 institusi pendidikan yaitu: UGM, UI, ITB, ITS, PENS, ITT TELKOM, dan 1 institusi pemerintah yaitu: LAPAN, dan tergabung dalam bentuk konsorsium bernama INSPIRE (Indonesian Nano-Satellite Platform

Initiative for Research and Education) [1]. Satelit IiNUSAT-1

tersusun dari beberapa sub-sistem yang saling terintegrasi, salah satunya adalah CDHS (command data handling system). CDHS berfungsi sebagai pengendali keseluruhan proses pada satelit dengan cara berkomunikasi dengan sub-sistem lain. Setiap sub-sistem yang terhubung dengan CDHS merepresentasikan tugas yang harus selesaikan secara

real-time, untuk itu CDHS harus menyelesaikan tugas berdasarkan

jadwal (scheduler) maupun pelayanan interupsi (interrupt

driven) secepat mungkin tanpa ada kesalahan. Sehingga

dibutuhkan rancangan baik perangkat lunak maupun perangkat keras dalam membangun sub-sistem CDHS.

Ada 2 aspek yang dibutuhkan dalam merancang CDHS, yaitu perangkat keras dan perangkat lunak. Pada rancangan perangkat keras terdapat beberapa pertimbangan dalam

merancang, pertama yaitu menentukan jenis mikroprosesor untuk pengendali utama [2] yang akan digunakan ditinjau dari jumlah tugas yang harus dilaksanakan secara realtime serta daya tahannya terhadap potensi gangguan radiasi angkasa [3] berdasarkan hasil pengujian maupun dari pengalaman yang sudah menggunakannya. Kedua yaitu metode komunikasi dengan sub-sistem yang lain (electronic power sub system [EPS], telemetry & telecommand [TTC], payload dan attitude

determination & control system [ADCS]) apakah digunakan

mode komunikasi bersama (shared bus) atau peer to peer [4]. Ketiga yaitu menyediakan pengendali cadangan jika pengendali utama gagal melakukan tugas, konsep redundansi ini bisa diterapkan dalam konfigurasi COLD Redundant maupun HOT redundant [4].

Pada perancangan perangkat lunak terdapat pertimbangan dalam merancang, pertama yaitu menerapkan sistem operasi pada pengendali utama yang bekerja secara real time dalam mengelola semua proses yang ada baik keluar maupun masuk untuk menyelesaikan tugas. Pemilihan jenis RTOS didasarkan pada kebutuhan sumber daya (resource) pada mikroprosesor yang digunakan, jenis preemptive maupun cooperative [5]. Kedua yaitu menerapkan algoritma deteksi kesalahan pada komunikasi data antara CDHS dengan sub-sistem yang lain. Deteksi kesalahan merupakan upaya untuk mencegah interpretasi yang salah oleh sebuah sistem dari data yang diterimanya, algoritma deteksi kesalahan yang umum digunakan adalah cyclic redundancy check (CRC) dengan menerapkan prinsip polynomial yang mudah diterapkan dan handal dalam mendeteksi kesalahan [6]. Dengan mengetahui adanya kesalahan pada paket data yang diterima, bisa dilakukan koordinasi 2 arah untuk mendapatkan kembali data yang benar, atau bahkan bisa dilakukan koreksi dengan algoritma yang lain.

Pada paper ini, konsep CDHS menggunakan mikroprosesor jenis ARM 32-bit Cortex M3 sebagai pengendali utama yang harganya cukup murah jika dibandingkan dengan kemampuan yang dimiliki, baik dalam hal kecepatan maupun fasilitasnya. Dalam menyelesaikan semua tugas secara real time digunakan RTOS jenis preemptive untuk mengelola sumber daya/fasilitas dari mikroprosesor pengendali utama. Operasi yang dijalankan oleh RTOS pada dasarnya ada 2 hal yaitu polling berupa tugas-tugas yang sudah terjadwal seperti housekeeping, data

logging dan heart beating, dan interrupt driven berupa

sikap dari stasiun bumi. CDHS menggunakan 4 jalur komunikasi peer to peer jenis serial tak sinkron (UART) untuk berhubungan dengan 4 sub-sistem yang lain (EPS-TTC-PAYLOAD-ADCS). Metode deteksi kesalahan CRC diterapkan pada setiap komunikasi data serial untuk menjamin tidak terjadinya eksekusi perintah yang salah atau interpretasi data akuisisi yang salah. Implementasi rancangan akan dibahas pada bagian 2.

II. KONSEP RANCANGAN SISTEM

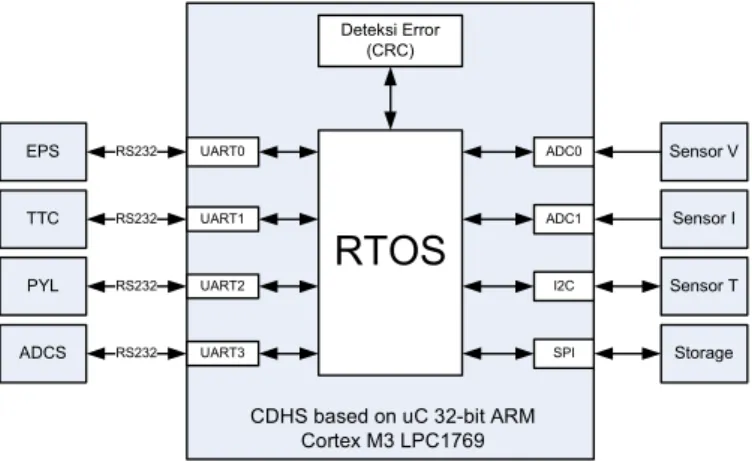

Rancangan CDHS yang diajukan dapat dilihat pada gambar 1. Sistem tersusun dari beberapa bagian, yaitu satu pengendali utama berbasis mikrokontroler ARM 32-bit Cortex M3, driver komunikasi RS-232, sensor suhu, sensor arus, sensor tegangan dan external storage.

A. Mikrokontroler pada CDHS

Mikrokontroler yang digunakan adalah LPC1769 produksi NXP yang sudah melewati beberapa tahap pengujian standar militer sehingga sudah layak dijadikan sebagai pengendali utama CDHS pada satelit [7]. Terdapat banyak fasilitas yang bisa digunakan sesuai misi yang dijalankan, yaitu tersedia empat jalur komunikasi serial (USART) secara mandiri (bukan hasil multiplekser) yang mampu bekerja dengan kecepatan hingga 115200 bps, sehingga mampu melayani komunikasi data full duplex kecepatan tinggi dan akses empat jalur komunikasi bisa dilakukan secara real time tanpa terganggu adanya mutual exclusion (mutex) seperti pada jalur komunikasi bersama (I2C dan CAN) [8]. Selain itu, mikrokontroler tersebut juga menyediakan fasilitas ADC 12-bit yang bisa digunakan untuk proses akuisisi data analog, seperti suhu, arus dan tegangan CDHS yang bisa digunakan untuk mengukur kondisi lingkungan dan kesehatan sistem.

UART0 UART1 UART2 UART3 EPS TTC PYL ADCS RS232 RS232 RS232 RS232 ADC0 Sensor V

RTOS

Sensor I ADC1 Sensor T I2C SPI StorageCDHS based on uC 32-bit ARM Cortex M3 LPC1769

Deteksi Error (CRC)

Gambar 1. Skema Kerja CDHS

Seluruh proses yang dikerjakan oleh RTOS dijadwal dengan kecepatan yang ditentukan dari tick time yang digunakan [5]. Pada umumnya digunakan 10 mdetik untuk menjamin hasil eksekusi secara real time yang diperoleh dari timer internal mikrokontroler. Mikrokontroler berkomunikasi dengan sub-sistem lain menggunakan port serial UART secara terpisah. Sehingga dalam penerapan RTOS akan dibuat tugas

penanganan komunikasi serial untuk setiap jalur komunikasi, hal ini bertujuan untuk menghindari terjadinya mutex pada jalur komunikasi serial, sehingga akan meningkatkan bandwith komunikasi antara CDHS dengan sub-sistem lain. Implementasi deteksi kesalahan berupa fungsi yang akan digunakan pada setiap proses komunikasi data serial untuk memeriksa kesalahan paket data yang masuk dan keluar.

B. Real Time Operating System (RTOS)

Skema kerja RTOS pada CDHS yang terjadwal secara garis besar dapat dilihat pada gambar 2. Terdapat beberapa tugas terjadwal yang dikerjakan oleh RTOS, setiap tugas memiliki waktu penyelesaian yang berbeda-beda tergantung pada banyaknya proses yang dikerjakan. Dapat dilihat bahwa tugas mengumpulkan data housekeeping dari sub-sistem selain CDHS (task2,3,4,5) bisa didapatkan tanpa saling menunggu karena bisa dilakukan secara serentak oleh RTOS. Untuk task6 dan task7 akan selesai jika task2,3,4,5 juga selesai. Untuk task8 berfungsi sebagai generator detak (heart beat) untuk mereset nilai watch dog timer (WDT) sebagai penanda untuk unit redundant bahwa kendali utama masih bekerja dengan baik.

RTOS

Task-1 Housekeeping CDHS Task-2 Housekeeping EPS Task-3 Housekeeping TTC subsys. Task-4 Housekeeping Payload subsys. Task-5 Housekeeping ADCS Task-8 Heart Beating Task-6 Housekeeping Data Logging Task-7 Transmitting BEACONGambar 2. Skema Kerja RTOS pada CDHS

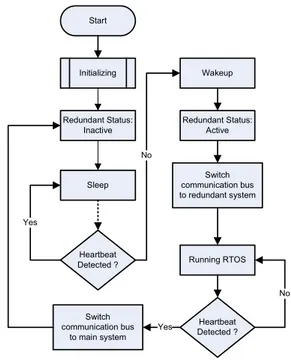

C. Konsep Redundansi

CDHS memiliki fungsi yang sangat penting pada operasional satelit dan tidak boleh terjadi kegagalan sistem yang fatal, sehingga harus tersedia sistem cadangan yang bisa menggantikan pengendali utama dalam bekerja [9]. Pada gambar 3 dapat dilihat skema redundansi CDHS. sistem redundansinya menggunakan jenis COLD yang tidak menyediakan image memory dari proses yang berlangsung sebelumnya, dan ini merupakan kelemahan dari sistem ini. Namun dari sisi lain memiliki kemudahan implementasi pada satelit dengan misi sederhana. Sistem cadangan secara normal dalam kondisi sleep sehingga tidak menghabiskan daya yang besar dan akan terbangun jika sistem utama gagal melakukan prosedur standar. Kegagalan sistem utama dideteksi oleh

sistem cadangan dengan menggunakan output watch dog timer (WDT) yang nilainya selalu di reset oleh detak aktifitas (heart

beat) dari sistem utama dengan periode konstan. Jika sistem

utama berhenti mengeluarkan detak aktifitas maka WDT akan terpicu dan membangunkan sistem cadangan untuk menggantikan sistem utama.

Gambar 3. Skema COLD Redundant pada CDHS

Alur kerja sistem cadangan bisa dilihat pada gambar 4. Secara normal, kondisi sistem cadangan adalah sleep dan akan terbangun jika mendapatkan signal wakeup dari WDT sebagai indikasi sistem utama yang gagal. Dalam konsep ini tidak ada image memory dari proses terakhir sistem utama yang digunakan oleh sistem cadangan karena memang tidak tersedia, hal ini akan mengakibatkan kehilangan informasi status proses terbaru maupun data terbaru yang diterima oleh sistem utama dan itu adalah kelemahan dari model ini. Namun kehilangan data dari proses yang belum selesai pada sistem utama karena gagal bekerja juga akan dialami oleh CDHS dengan sistem cadangan yang menggunakan image memory, dengan asumsi terjadi kegagalan yang fatal, misalkan terjadi shut down secara mendadak. Setelah bangun dari kondisi tidur, sistem cadangan akan mengeluarkan output bernilai HIGH pada pin acknowledge, hal ini bertujuan agar saat sistem utama kembali pulih akan menunggu sistem cadangan selesai mengerjakan semua tugas secara penuh dan bus komunikasi dikembalikan pada mode normal, hingga output acknowedge kembali bernilai LOW yang menandakan bahwa sistem utama sepenuhnya berhak mengendalikan operasi CDHS. Saat sistem cadangan aktif, seluruh komunikasi data serial dengan sub-sistem lain dialihkan menuju port komunikasi serial dari sistem cadangan menggunakan piranti saklar digital. Tidak ada perbedaan prosedur operasi komunikasi data antara sistem utama dengan sistem cadangan, akan tetapi identitas yang ditanam pada sistem yang akan membedakannya.

Start Initializing Sleep Heartbeat Detected ? Yes Wakeup No Redundant Status: Active Running RTOS Heartbeat Detected ? Switch communication bus to main system Yes No Redundant Status: Inactive Switch communication bus to redundant system

Gambar 4. Diagram Alir Kerja Sistem Cadangan.

D. Deteksi Kesalahan

Dengan kondisi ruang angkasa yang penuh dengan potensi gangguan berupa radiasi kosmis dan suhu, sangat mungkin mengganggu jalur komunikasi data serial antara CDHS dengan sub-sistem lain yang terhubung. Kerusakan data bisa menimbulkan interpretasi yang salah bagi unit yang menerimanya. Sehingga perlu rancangan perangkat lunak untuk mendeteksi adanya kerusakan data pada sebuah paket informasi. Pada penelitian ini menggunakan deteksi koresi dengan metode cyclic redundancy check (CRC) yang umumnya banyak digunakan pada komunikasi data karena sederhana dan handal [6]. CRC pada dasarnya menggunakan operasi pembagian polynomial dari byte data informasinya. Yang terpenting adalah antara dua sisi yang berkomunikasi memiliki kesepakatan penggunaan generator polynomial yang akan digunakan untuk mengetahui informasi aslinya agar diketahui apakah terjadi kerusakan data.

Untuk menghitung polinomial dari bit data informasi ditunjukkan oleh rumus 1. Nilai piadalah kosntanta berupa bit ke-i dari informasi [6].

( )

=∑

n= i i ix p x u 0 (1)Nilai polinomial u(x) yang diperoleh selanjutnya diproses bersama polinomial generator g(x) untuk menghasilkan nilai CRC dari informasi yang akan dikirimkan s(x), bisa dilihat pada rumus 2 [6].

s

( ) ( )

x =u x xn−k+v( )

x. (2)

Pada rumus 2, nilai v(x) adalah sisa dari pembagian

( )

n k x xu . − oleh g(x), Dalam kasus ini nilai g(x) = x5+ x4+ x2+ 1 yang sebelumnya sudah disepakati oleh pengirim dan

penerima [6]. Gambar 5 menunjukkan alur proses pengiriman paket informasi pada sisi pengirim yang disertai dengan CRC sebagai informasi pendukung untuk mendeteksi kesalahan oleh penerima.

Gambar 5. Diagram Alir Pengiriman Paket Informasi

Pada sisi penerima, dengan menggunakan polinimial generator yang sama seperti pada sisi pengirim, dilakukan kalkulasi CRC dari paket data yang diterima dan kemudian membandingkannya dengan nilai CRC yang disertakan pada paket data terima. Gambar 6 menunjukkan alur proses penerimaan paket data.

Gambar 6. Diagram Alir Penerimaan Paket Informasi

III. IMPLEMENTASI SISTEM

Eksperimen yang dilakukan fokus pada 2 hal, yaitu implementasi jalur komunikasi serial dengan format RS232 pada CDHS untuk berkomunikasi dua arah full duplex dengan sub-sistem yang lain (EPS-TTC-PAYLOAD-ADCS), dan implementasi RTOS dalam penanganan seluruh tugas yang harus diselesaikan oleh CDHS.

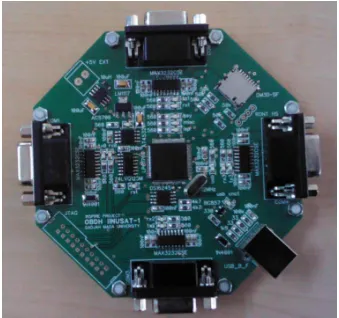

A. Komunikasi Data Serial

Gambar 7 menunjukkan purwarupa CDHS menggunakan mikrokontroler 32-bit ARM LPC1769 dengan clock sebesar 100MHz. Terdapat 4 jalur komunikasi serial yang bisa digunakan secara parallel. Dengan menggunakan konsep FIFO secara internal akan mecegah kehilangan data saat terjadi interupsi serial masuk pada beberapa port secara bersamaan. Dalam eksperimen ini kapasitas FIFO yang digunakan sebesar 16 karakter.

Gambar 7. Purwarupa CDHS

Masing-masing port komunikasi serial menggunakan format komunikasi RS-232 tak sinkron dengan kecepatan hingga 115200 bps, 8-bit data, tidak menggunakan bit parity dan 1-bit stop. Tabel 1 menunjukkan hasil pengujian nilai error yang sudah dilakukan dengan beragam kecepatan dalam kondisi ideal tanpa ada gangguan lingkungan dengan mengirimkan data dengan lebar 100 karakter.

TABEL I. UJI ERROR BAUDRATE

No Kecepatan (bps) Error (%) 1 1200 0 2 2400 0 3 4800 0 4 9600 0 5 19200 0 6 38400 0 7 115200 0

B. Implementasi RTOS

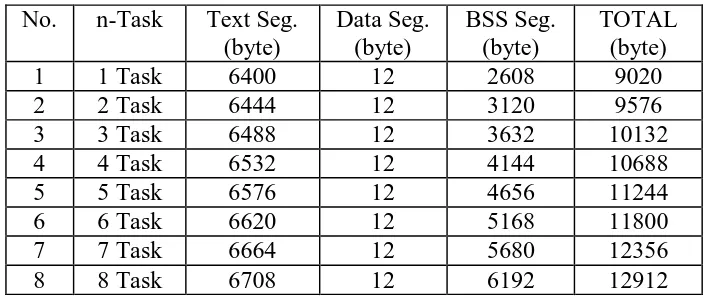

Pada eksperimen dilakukan pengamatan terhadap foot print pada memory RAM internal mikrokontroler, yang menunjukkan pemakaian memory untuk operasional. RTOS yang digunakan pada percobaan adalah CoOS dari CooCox dengan jenis preemptive. Pada tabel 2 menunjukkan penggunaan segmen memori RAM untuk operasional RTOS berdasarkan jumlah task yang dikerjakan. Pada eksperimen, setiap task hanya berisi fungsi tunda sebesar 50 * tick_time dan nilai tick time yang digunakan adalah sebesar 10mdetik.

TABEL II. UJI MEMORY FOOTPRINT PADA RTOS No. n-Task Text Seg.

(byte) Data Seg. (byte) BSS Seg. (byte) TOTAL (byte) 1 1 Task 6400 12 2608 9020 2 2 Task 6444 12 3120 9576 3 3 Task 6488 12 3632 10132 4 4 Task 6532 12 4144 10688 5 5 Task 6576 12 4656 11244 6 6 Task 6620 12 5168 11800 7 7 Task 6664 12 5680 12356 8 8 Task 6708 12 6192 12912

Sesuai dengan tabel 2, setiap penambahan satu jumlah task nya mengakibatkan penambahan ruang RAM sebesar 556 byte. Jika dibandingkan dengan kapasitas RAM yang dimiliki oleh mikrokontroler LPC1769 sebesar 32Kbyte, nilai kenaikan tersebut masih sangat layak.

Pada tabel 3 menunjukkan hubungan antara jumlah task yang dimiliki terhadap konsumsi daya yang dibutuhkan. Dan hasilnya menunjukkan bahwa kedua parameter tersebut tidak ada hubungan secara linier, artinya kenaikan jumlah task tidak mempengaruhi secara signifikan terhadap konsumsi daya yang digunakan. Hal ini karena dengan menggunakan metode penjadwalan oleh scheduler berdasar pada periode tick time untuk melakukan pengirisan terhadap semua task yang dikerjakan. Sehingga dalam 1 tick hanya ada 1 task.

TABEL III. JUMLAH TASK VS DAYA

No. n-Task Daya (mwatt)

1 1 384.556 2 2 402.844 3 3 384.048 4 4 388.112 5 5 383.032 6 6 403.352 7 7 393.192 8 8 385.064 IV. KESIMPULAN

Pada penelitian ini, implementasi CDHS dititik beratkan pada rancangan komunikasi serial menggunakan non shared

bus, yaitu konsep komunikasi parallel antara CDHS dengan 4

sub-sistem lain pada jalur yang terpisah untuk meningkatkan kinerja dan kemudahan dalam membangun komunikasi data. Dari percobaan yang dilakukan sudah berhasil dilakukan komunikasi data pada 4 port serial dengan berbagai tingkat kecepatan dan memiliki nilai error 0%. Dengan menggunakan format RS-232 sangat cocok digunakan pada wahana satelit

yang bersifat modular yang membutuhkan solusi komunikasi saat terdapat jarak yang terlalu panjang dan cukup beresiko tinggi menimbulkan kerusakan data jika digunakan jenis komunikasi serial lain, misal I2C.

Probabilitas terjadi kerusakan data pada komunikasi serial pasti ada, terlebih di ruang angkasa, sehingga disetiap komunikasi data serial digunakan metode deteksi kesalahan yang populer digunakan yaitu cyclic redundancy check (CRC). Semakin panjang polinomial yang digunakan maka semakin baik dalam mendeteksi kesalahan. Dengan konsep CRC yang disepakati antara pengirim dan penerima, maka kesalahan bit akan mudah dideteksi dan juga bisa diterapkan koreksi kesalahan.

Dari sisi perangkat lunak digunakan real time operating

system (RTOS) untuk mengelola seluruh aplikasi yang

dijalankan oleh CDHS. Salah satu alasan pemilihan RTOS didasarkan pada seberapa besar ruang memory RAM yang digunakan. Dengan menggunakan RTOS, seluruh tugas dikerjakan mendekati waktu nyata sehingga tidak ada tugas maupun even masukan yang terlewatkan.

REFERENCES

[1] INSPIRE (Indonesian Nano-Satellite Platform Initiative for Research & Education). Available at: www.inspire.or.id. Last visited: November, 2011.

[2] Gerard Aalbers, Georgi N. Gaydadijev, Rouzbeh Amini, ”CDHS Design for a University Nano-Satellite”, IAC-06-B5.7.05, 2005.

[3] Jake A. Schaffner, “The Electronic System Design, Analysis, Integration, and Construction of the Cal Poly State University CP1 CubeSat”, 16th

AIAA/USU Conference on Small Satellites, 2002.

[4] S. de Jong, G.T. Aalbers, J. Bouwmeester, “Improved Command And Data Handling System”, 59th International Astronautical Congress, Glasgow, Scotland, UK, 29 September - 3 October, 2008.

[5] S. Ramanarayana Reddy, “Selection of RTOS for an Efficient Design of Embedded Systems”, IJCSNS International Journal of Computer Science and Network Security, VOL.6 No.6, June 2006.

[6] P. Koopman, T. Chakravarty, “Cyclic Redundancy Code (CRC) Polynomial Selection For Embedded Networks”, The International Conference on Dependable Systems and Networks, DSN-2004. [7] NXP Product Brochure - High performance aerospace and defense

solutions. Available at: www.nxp.com/documents/.../75017008.pdf. Last visited: November, 2011.

[8] NXP Semiconductors. UM10360 - LPC17xx user manual. Available:

http://ics.nxp.com/support/documents/microcontrollers/pdf/user.manual. lpc17xx.pdf. Last visited: November, 2011.

[9] David D. Stott. et.al. “The NEAR Command and Data Handling System”, Johns Hopkins Apl Technical Digest, Volume 19, Number 2. 1998.