DESAIN DAN REALISASI MODULATOR OFDM (ORTHOGONAL FREQUENCY DOMAIN MULTIPLEXING) UNTUK JARINGAN JALA-JALA LISTRIK TEGANGAN RENDAH BERBASIS FPGA

(DESIGN AND REALIZATION OFDM (ORTHOGONAL FREQUENCY DOMAIN MULTIPLEXING) MODULATOR FOR LOW VOLTAGE POWERLINE COMMUNICATION SYSTEM BASED ON FPGA) Wicaksono Widiatmoko1

Basuki Rahmat, Ir., M.T.2 ([email protected])

Denny Darlis, S.Si.,M.T.3 ([email protected])

Fakultas Elektro Dan Komunikasi – Institut Teknologi Telkom Jl. Telekomunikasi, Dayeuh Kolot Bandung 40257 Indonesia

ABSTRAK

Power Line Communication (PLC) adalah sebuah teknologi yang memanfaatkan jaringan jala-jala listrik untuk melewatkan pengiriman data dan informasi. Keuntungan yang paling utama pemanfaatan teknologi PLC system karena jaringan yang sudah existing berupa jaringan listrik pada setiap rumah atau bangunan dijadikan sebagai media transmisi fisiknya sehingga penggunaan PLC system akan menghemat biaya dan waktu instalasi jaringan. Namun PLC system juga mempunyai kekurangan yakni media transmisi power line mempunyai karakteristik dan parameter yang tidak konstan salah satunya bergantung pada jumlah dan jenis peralatan yang tersambung dengan listrik. Salah satu elemen penting pada PLC system adalah perangkat Modem. Alat ini digunakan untuk mengkondisikan dan mengkonversi sinyal agar dapat dikirim dan diterima dengan baik melalui jaringan jala-jala listrik. Modem merupakan penggabungan dari analog dan digital circuit sehingga dapat diuraikan menjadi tiga blok yakni pertama AFE (analog front end) merupakan blok yang memproses sinyal analog yang terdiri dari filter dan kopling. Kedua analog to digital converter (ADC) dan digital to analog converter (DAC). Ketiga modem, modem menjalankan fungsi memproses sinyal digital dan juga menjalankan operasi memodulasi dan mendemodulasi sinyal.

Blok bagian dari PLC system terdiri dari modulator, demodulator, dan kanal power line. Dengan meningkatnya variasi layanan yang dapat dilakukan pada PLC system maka perlu suatu teknik encoding dan decoding yang lebih kompleks seperti OFDM (orthogonal frequency division multiplexing). Untuk itu direalisasikan modulator OFDM. OFDM mempunyai keunggulan data rate yang tinggi Teknik multiplexing pada OFDM menggunakan beberapa buah frekuensi (multicarrier) yang saling tegak lurus (orthogonal). Masing-masing sub-carrier dimodulasikan dengan teknik modulasi konvensional pada rasio simbol yang rendah. Penggunaan karena teknik multiplexing ini akan mengefisienkan saluran transmisi.

Hasil yang direalisasikan adalah dapat digunakan untuk berkomunikasi menggunakan teknik multiplexing OFDM dengan cara mengirimkan bit-bit data masukan dari generator sinyal, lalu mengirimkannya melalui jaringan jala-jala listrik melalui interface modulator PLC.

Kata kunci : PLC, AFE, ADC, DAC, modem, modulator, demodulator, PLC system, OFDM, multiplexing, interface ABSTRACT

Power Line Communication (PLC) is a technology that utilizes the grid network to pass data and information delivery. The main advantage of technology utilization for PLC systems already existing network of power lines on each house or building used as a physical transmission medium so that the use of the PLC system will save costs and time network installation. But the PLC system also lacks the power line transmission medium characteristics and parameters are not constant one of which depends on the amount and type of equipment that is connected with electricity. One important element in the PLC system is a modem device. This tool is used to condition and convert the signals to be sent and received well through the grid network. Modem is a combination of analog and digital circuit that can be decomposed into three blocks of the first AFE (analog front end) is an analog signal processing block that consists of filter and coupling. Both analog to digital converter (ADC) and digital to analog converter (DAC). Third modem, the modem digital signal processing function and also run the operation signal to modulate and demodulate.

Block part of the PLC system consists of the modulator, demodulator, and channel power line. With the increasing variety of services that can be done on a PLC system it is necessary encoding and decoding techniques are more complex such as OFDM (orthogonal frequency division multiplexing). For the OFDM modulator is realized. OFDM has the advantage of high data rate in OFDM multiplexing technique using several frequencies (multicarrier) are mutually perpendicular (orthogonal). Each sub-carrier modulated with a conventional modulation technique at a low symbol rate. Use of this multiplexing technique because it will simplify the transmission line.

The results can be realized is used to communicate using a multiplexing technique OFDM by sending the bits of data input from the signal generator, and then send it through the grid network via PLC modulator interface.

Keyword : PLC, AFE, ADC, DAC, modem, modulator, demodulator, PLC systems, OFDM, multiplexing, interface

I.PENDAHULUAN 1.1. Latar Belakang

Power Line Communication (PLC) adalah sebuah teknologi yang memanfaatkan jaringan jala-jala listrik untuk melewatkan pengiriman data dan informasi. Saat ini teknologi

PLC semakin menyebar dan terus dikembangkan standar-standar, teknik modulasi, dan perangkat untuk terus meningkatkan performansi PLC. Keuntungan yang paling utama pemanfaatan teknologi PLC system karena jaringan yang sudah existing berupa jaringan listrik pada setiap rumah atau bangunan dijadikan sebagai media transmisi fisiknya sehingga

penggunaan PLC system akan menghemat biaya dan waktu instalasi jaringan. Namun PLC system juga mempunyai kekurangan yakni media transmisi power line mempunyai karakteristik dan parameter yang tidak konstan salah satunya bergantung pada jumlah dan jenis peralatan yang tersambung dengan listrik. Salah satu elemen penting pada PLC system adalah Modem. Alat ini digunakan untuk mengkondisikan dan mengkonversi sinyal agar dapat dikirim dan diterima dengan baik melalui jaringan jala-jala listrik. Modem merupakan penggabungan dari analog dan digital circuit sehingga dapat diuraikan menjadi tiga blok yakni pertama AFE (analog front end) merupakan blok yang memproses sinyal analog yang terdiri dari filter dan kopling. Kedua analog to digital converter (ADC) dan digital to analog converter (DAC). Ketiga modem, modem menjalankan fungsi memproses sinyal digital dan juga menjalankan operasi memodulasi dan mendemodulasi sinyal.

Blok bagian dari PLC system terdiri dari modulator, demodulator, dan media power line. Dengan meningkatnya variasi layanan yang dapat dilakukan pada PLC system maka perlu suatu modem dengan teknik encoding dan decoding yang lebih kompleks seperti OFDM (orthogonal frequency division multiplexing). OFDM mempunyai keunggulan data rate yang tinggi. Teknik multiplexing pada OFDM menggunakan beberapa buah frekuensi (multicarrier) yang saling tegak lurus (orthogonal). Masing-masing sub-carrier dimodulasikan dengan teknik modulasi konvensional pada rasio simbol yang rendah. Penggunaan karena teknik multiplexing ini akan mengefisienkan saluran transmisi.

1.2. Tujuan

Tujuan dari tugas akhir ini adalah menganalisa dan menghasilkan prototype modulator dengan teknik multiplexing OFDM (orthogonal frequency domain multiplexing) yang dapat bekerja pada jaringan jala-jala listrik (power line communication) dengan standar minimum dapat mengirimkan bit data dengan benar.

1.3. Rumusan Masalah

Rumusan masalah pada tugas akhir ini : 1. Merancang blok analog front end (AFE).

2. Merancang blok OFDM dan antarmuka dengan analog front end (AFE).

3. Merealisasikan modulator dengan OFDM untuk PLC 4. Pengukuran parameter-parameternya

1.4. Batasan Masalah

Tugas Akhir ini mempunyai batasan masalah yaitu : 1. Perancangan modulator hanya pada level baseband. 2. Data yang ditransmisikan adalah data bit karakter. 3. Menggunakan 64 titik IFFT pada blok OFDM. 4. Parameter jarak antara pengirim dan penerima

diabaikan dan saluran dengan kondisi ideal. 5. Mapper yang digunakan adalah 4-QAM. 6. FPGA yang digunakan Xilink Virtex-4 1.5. Metodologi Penelitian

a. Studi Literatur

Pada tahap ini dilakukan pencarian dan pengumpulan literatur dan kajian-kajian yang berkaitan dengan permasalahan yang ada pada Tugas Akhir ini, baik berupa artikel, buku referensi, internet atau sumber lain yang berhubungan dengan Tugas Akhir ini. b. Perancangan dan Realisasi

Pada tahapan ini, akan dibuat suatu rancangan maupun desain modulator OFDM untuk PLC dan juga sistem pengujian serta pengukuran yang kemudian akan direalisasikan. Namun sebelum dilakukan pengukuran dan pengambilan data, terlebih dahulu sistem akan di-troubleshoot untuk mengetahui kelayakannya untuk pengujian dan pengukuran selanjutnya.

c. Pengukuran dan Pengambilan

Setelah modulator OFDM untuk PLC dan sistem telah dibuat, maka untuk selanjutnya akan dilakukan pengukuran dan pengambilan data sesuai dengan parameter uji yang telah ditentukan di awal.

d. Analisis Kinerja modulator OFDM untuk PLC Tahap akhir dalam penelitian Tugas Akhir ini adalah menganalisis data pengukuran yang telah didapatkan pada tahap sebelumnya dan membandingkan hasilnya dengan pelbagai paper dan jurnal yang mungkin telah ada sebelumnya serta menutup penelitian ini dengan suatu simpulan dan saran terhadap penelitian selanjutnya. Implementasi secara keseluruhan blok modulator OFDM PLC dan troubleshooting.

1.6. Sistematika Penulisan

Secara umum keseluruhan Tugas Akhir ini dibagi menjadi lima bab bahasan, ditambah dengan lampiran dan daftar istilah yang diperlukan. Penjelasan masing - masing bab adalah sebagai berikut:

Bab 1 : Pendahuluan

Bab ini berisi gambaran umum dari penelitian yang dilakukan. Tercakup di dalamnya yaitu latar belakang, perumusan masalah, tujuan, batasan masalah, metode penelitian serta sistematika penulisan.

Bab 2 : Dasar Teori

Pada bab ini berisi paparan umum tentang powerline communication (PLC), prinsip kerja PLC, karakteristik kanal PLC, ulasan tentang OFDM, prinsip dasar OFDM, analog front end (AFE) yang terdiri dari filter, penguat, D/A, dan terakhir membahas tentang FPGA .

Bab 3 : Perancangan Sistem

Bab ini membahas mengenai model sistem, parameter kerja dan asumsi yang digunakan, perancangan hardware serta perancangan blok OFDM.

Bab 4 : Sintesis, Pengukuran, Dan Analisa Sistem

Bab ini menganalisis dan menjelaskan hasil yang didapat dari simulasi pada Modelsim serta analisis dari hasil simulasi tersebut. juga sintesis rangkaian pada Xilinx. Dari hasil sintesis dapat dianalisis resource FPGA yang terpakai. Serta analisa hasil pengukuran masing-masing blok

Bab 5 : Kesimpulan dan Saran

Pada bab ini merupakan bab terakhir dari laporan tugas akhir yaitu berupa kesimpulan untuk sistem yang penulis kerjakan, serta saran untuk penelitian berikutnya.

II. LANDASAN TEORI II.1 PLC

Power Line Communicatios (PLC) adalah teknologi komunikasi menggunakan jaringan jala-jala tenaga listrik sebagai media transmisi data. Jala-jala listrik yang memiliki fungsi utama menyalurkan energi listrik, dapat dipakai sebagai media transmisi data. Prinsip dasarnya adalah menginjeksikan sinyal data ke dalam saluran listrik pada frekuensi di atas frekuensi dasar listrik (50-60 Hz).

Gambar 2.1 Spektrum pada Jaringan Listrik II.1.1Pembagian Spektrum Frekuensi

a. Narrowband PLC, jaringan PLC yang beroperasi pada range frekuensi ini distandarkan oleh CENELEC

Tabel 2.1 Pembagian CENELEC Band

b. Broadband PLC, sistem ini dapat menyediakan transfer data dengan kecepatan data lebih dari 2Mbps. Sistem ini dapat melebihi jaringan PLC narrowband

melewatkan beberapa kanal suara dan transmisi data dengan bitrate yang sangat rendah. Broadband

mendukung layanan yang beragam seperti

transfer data kecepatan tinggi, transfer sinyal video, dan mendukung semua layanan yang ada narrowband

II.1.2Karakteristik Kanal PLC

Kanal PLC merupakan saluran yang sama digunakan untuk distribusi daya listrik berupa kawat tembaga untuk menghantarkan daya sampai titik pelanggan. Transmisi data pada PLC menggunakan frekuensi tinggi dengan daya yang rendah namun sebaliknya untuk transmisi listrik digunakan frekuensi rendah 50/60Hz dengan daya yang tinggi 110/220V. Saluran ini sebenarnya tidak dipersiapkan untuk berkomunikasi. sehingga setiap sinyal informasi yang diinjeksikan ke jaringan listrik akan tersebar ke seluruh jaringan dan diserap oleh beban listrik. Kanal listrik mempunyai sifat karakteristik yang tidak menguntungkan seperti noise dan atenuasi yang tinggi kemudian komponen multipath yang muncul

terminasi yang tidak sempurna dan adanya impedansi yang tidak cocok serta penggunaan bermacam,macam jenis kabel yang digunakan yang menyebabkan terjadinya pantulan sinyal pada saluran. Karakteristik powerline communication yang meliputi level noise yang tinggi, redaman, distorsi, impedansi modulasi, masalah beban komplek, kanal time varying, loss kabel , propagasi multipath, dan noise membuat kanal powerline kurang cocok untuk dijadikan sebagai media komunikasi data maupun suara. Semakin besar

level noise yang ditimbulkan akan menyulitkan penerima untuk mendeteksi sinyal informasi karena sinyal tersebut telah tercampur noise.

II.2 OFDM

OFDM (Orthogonal Frequency Division Multiplex bentuk khusus dari multi-carrier modulation

membagi sebuah aliran data informasi menjadi beberapa aliran pararel untuk ditransmisikan melalui beberapa

Dalam OFDM, data masukan dialirkan ke beberapa pararel ortogonal yang memiliki laju data yang lebih rendah

Berikut adalah blok diagram OFDM secara garis besar.

Gambar 2.2 Blok OFDM

Band untuk PLC

PLC, sistem ini dapat menyediakan transfer data dengan kecepatan data lebih dari 2Mbps. Sistem ini dapat yang hanya dapat melewatkan beberapa kanal suara dan transmisi data dengan Broadband PLC dapat mendukung layanan yang beragam seperti voice connection, transfer data kecepatan tinggi, transfer sinyal video, dan

narrowband PLC.

saluran yang sama digunakan untuk distribusi daya listrik berupa kawat tembaga untuk menghantarkan daya sampai titik pelanggan. Transmisi data pada PLC menggunakan frekuensi tinggi dengan daya yang rendah namun sebaliknya untuk transmisi listrik digunakan frekuensi rendah 50/60Hz dengan daya yang tinggi 110/220V. Saluran ini sebenarnya tidak dipersiapkan untuk berkomunikasi. yang diinjeksikan ke jaringan listrik akan tersebar ke seluruh jaringan dan diserap oleh beban mempunyai sifat karakteristik yang tidak menguntungkan seperti noise dan atenuasi yang tinggi kemudian komponen multipath yang muncul sebagai akibat dari terminasi yang tidak sempurna dan adanya impedansi yang tidak cocok serta penggunaan bermacam,macam jenis kabel yang digunakan yang menyebabkan terjadinya pantulan sinyal pada saluran. Karakteristik powerline communication yang ti level noise yang tinggi, redaman, distorsi, impedansi modulasi, masalah beban komplek, kanal time varying, loss kabel , propagasi multipath, dan noise membuat kanal powerline kurang cocok untuk dijadikan sebagai media

emakin besar gangguan dan menyulitkan penerima untuk mendeteksi sinyal informasi karena sinyal tersebut telah

Orthogonal Frequency Division Multiplex) adalah carrier modulation (MCM) yang membagi sebuah aliran data informasi menjadi beberapa aliran pararel untuk ditransmisikan melalui beberapa sub-carrier. Dalam OFDM, data masukan dialirkan ke beberapa sub-carrier

yang lebih rendah.

OFDM secara garis besar.

Blok OFDM

II.3AFE (analog front end)

AFE pada PLC merupakan interface antara kanal PLC dengan blok modulasi atau demodulasi. Sinyal yang dikirimkan pada kanal PLC adalah sinyal analog

sehingga sinyal yang telah diproses dan dimodulasi secara digital sebelumnya harus diubah ke dalam bentuk sinyal analog yang selanjutnya akan diinjeksikan ke dalam kanal PLC. AFE terdiri dari filter (BPF dan HPF), ADC (

converter), DAC (digital to analog converter kopling.

II.3.1 Filter

Filter adalah suatu rangkaian elektrik yang berfungsi untuk menghilangkan / meredam suatu komponen sinyal dengan frekuensi tertentu, dan menguatkan atau meneruskan komponen frekuensi yang diinginkan.

a. High Pass Filter (HPF)

Suatu filter yang melewatkan sinyal

atas frekuensi cut off dan meredam sinyal dengan frekuensi di bawahnya.

Gambar 2. 3 Rangkaian filter HPF sederhana b. Band Pass Filter (BPF)

Suatu filter yang melewatkan suatu sinyal dengan range frekuensi tertentu dan meredam semua sinyal

tersebut

Gambar 2. 4 Rangkaian filter BPF sederhana II.3.2 Kopling

Rangkaian kopling dalam Power Line Communication (PLC) adalah suatu rangkaian yang menghubungkan antara transmitter maupun receiver dengan kanal transmisi PLC.

Gambar 2.5 Contoh rangkaian kopling magnetik sederhana II.3.3 DAC (digital to analog converter)

Mengkonversi bilangan digital (biner) ke analog. DAC ini menerima masukan digital dan mengubahnya ke nilai tegangan (atau arus). Jika ini diulang terus menerus diberikan masukan digital yang berurutan akan terbentuk gelombang analog.

Prinsip kerja blok DAC sebagai berikut :

Gambar 2.6 Skematik DAC

AFE pada PLC merupakan interface antara kanal PLC dengan blok modulasi atau demodulasi. Sinyal yang dikirimkan analog yang telah termodulasi. sehingga sinyal yang telah diproses dan dimodulasi secara ubah ke dalam bentuk sinyal analog yang selanjutnya akan diinjeksikan ke dalam kanal PLC. AFE terdiri dari filter (BPF dan HPF), ADC (analog to digital digital to analog converter), line driver, dan

suatu rangkaian elektrik yang berfungsi untuk menghilangkan / meredam suatu komponen sinyal dengan frekuensi tertentu, dan menguatkan atau meneruskan komponen

Suatu filter yang melewatkan sinyal dengan frekuensi di dan meredam sinyal dengan frekuensi di

Rangkaian filter HPF sederhana

Suatu filter yang melewatkan suatu sinyal dengan range frekuensi tertentu dan meredam semua sinyal selain range

Rangkaian filter BPF sederhana

Rangkaian kopling dalam Power Line Communication (PLC) adalah suatu rangkaian yang menghubungkan antara transmitter maupun receiver dengan kanal transmisi PLC.

Contoh rangkaian kopling magnetik sederhana

DAC (digital to analog converter)

Mengkonversi bilangan digital (biner) ke analog. DAC ini menerima masukan digital dan mengubahnya ke nilai tegangan (atau arus). Jika ini diulang terus menerus diberikan masukan digital yang berurutan akan terbentuk gelombang analog.

C sebagai berikut :

II.3.4 Line Driver

Line driver adalah penguat digunakan untuk menguatkan daya sinyal analog atau digital sebelum dimasukan ke dalam saluran transmisi dengan tingkat yang lebih tinggi dibandingkan sinyal normal. Daya disesuaikan dengan karakteristik kanal transmisi. Line driver atau penguat adalah rangkaian komponen elektronika yang dipakai untuk menguatkan daya (arus dan tegangan). Amplifier akan menguatkan sinyal pada bagian masukannya sehingga menjadi arus listrik yang lebih kuat di bagian keluarannya. Besarnya penguatan ini sering dikenal dengan istilah gain. Jadi gain merupakan hasil bagi dari daya di bagian output (Pout) dengan daya di bagian inputnya (Pin) dalam bentuk fungsi frekuensi. Ukuran dari gain, (G) ini biasanya memakai decibel (dB). Dalam bentuk rumus hal ini dinyatakan sebagai berikut:

G(dB)=10log( II.4 FPGA

FPGA (Field Programmable Logic Array) merupakan suatu IC (Integrated Circuit) tipe HDL (High speed IC Description Language) yang dapat diprogram untuk melakukan fungsi-fungsi logika tertentu sesuai dengan kebutuhan. FPGA merupakan Programable Logic Device (PLD) yang dibangun dari sekumpulan sel fungsi logika dasar yang dapat diprogram. Sel-sel logika ini terhubung satu sama lain melalui suatu jaringan interkoneksi yang juga dapat diprogram. Istilah “Field Programmable” mengandung arti bahwa chip ini dapat diprogram diluar dari pabriknya, dengan kata lain, dapat diprogram oleh pengguna (end user). FPGA mempunyai kelebihan sebagai berikut:

Dikonfigurasi oleh end user

Tidak memerlukan proses Fabrikasi

Tersedia solusi yang mendukung chip customized VLSI Secara umum arsitektur bagian dalam dari IC FPGA terdiri atas tiga elemen utama yaitu Input/Output Block ( IOB ), Configurable Logic Block (CLB) dan Interkoneksi.

Bahasa pemrograman yang digunakan untuk memprogram FPGA salah satunya adalah VHDL. VHDL (VHSIC Hardware Description Language) merupakan bahasa pemrograman untuk memodelkan rangkaian digital (Hardware Description Language). VHDL merupakan salah satu dari jenis HDL. VHDL adalah penyempurnaan dari VHSIC (Very High Speed Integrated Circuit) yang pertama kali digunakan pada tahun 1983. Pada tahun 1985 muncul VHDL dengan memiliki library IEEE.

III. PERANCANGAN SISTEM III.1 Pendahuluan

Penggunaan kanal listrik untuk tujuan komunikasi akan menenemui gangguan seperti noise dan redaman. Karena sebenarnya kanal distribusi listrik tidak diciptakan untuk berkomunikasi. Dalam penggunaannya kanal listrik untuk distribusi daya listrik menduduki frekuensi yang rendah yakni pada frekuensi 50/60 Hz namun mempunyai daya yang sangat tinggi, hal ini berbanding terbalik dengan frekuensi yang digunakan untuk komunikasi yakni pada frekuensi tinggi 9 Khz – 30 Mhz dengan daya yang rendah. Kesulitan pentransmisian pada PLC adalah adanya gangguan noise dan redaman yang tinggi sehingga akan mempengaruhi jarak antara pengirim dan penerima. Redaman dan noise kanal PLC akan semakin bertambah besar jika semakin banyak perangkat listrik yang terhubung dengan listrik. Pemilihan teknik modulasi harus sesuai untuk suatu sistem komunikasi dan sangat bergantung pada sifat dan karakteristik media transmisi tersebut. Karakteristik saluran PLC bersifat non-linier sehingga modulasi PLC harus dapat mengatasi permasalahan ini. Penggunaan modulator dengan teknik modulasi OFDM diharapkan akan lebih tahan terhadap gangguan yang ada pada kanal PLC karena OFDM telah diketahui bahwa lebih tahan terhadap lingkungan yang kurang baik. Pada tugas akhir ini hanya akan direalisasikan modulator OFDM untuk menginjeksikan informasi ke kanal PLC. Sebuah blok sistem PLC yang lengkap (Gambar 3.1)

terdiri dari modulator, kanal PLC, dan demodulator. Untuk blok modulator OFDM yang direalisasikan seperti pada gambar 3.1.

Gambar 3.1 Modem PLC dengan OFDM III.2 Blok Sistem Modulator PLC dengan OFDM

Gambar 3.2 Modulator PLC OFDM III.3 Perancangan Blok Analog Front End (AFE)

Blok AFE terdiri DAC, filter BPF, line driver, dan kopling.

III.3.1 Digital to analog converter ( DAC )

adalah sebuah piranti yang dirancang untuk mengubah sinyal digital menjadi sinyal analog. Blok DAC pada modulator ini digunakan untuk mengkonversikan sinyal digital dari keluaran blok OFDM pada FPGA yang dikeluarkan secara parale 8 pin.

Gambar 3.3 Rangkaian Blok DAC

IC DAC0808 mempunyai dua catuan Vcc (+)= +5 V dan Vee(-)= -15V dengan nilai tegangan referensi VREF = +10V.

Selanjutnya keluaran IC DAC 0808 berupa arus diubah ke dalam bentuk tegangan dengan op amp yang digunakan sebagai current to voltage converter.

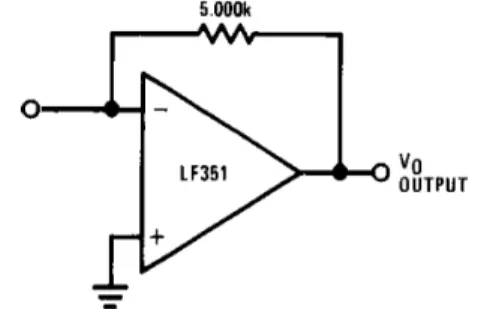

Gambar 3.4 Rangkaian Current To Voltage Converter III.3.2 Penguat daya

Suatu amplifier biasanya menerima suatu input dari suatu transducer ataupun sumber lainnya dan memberikan nilai keluaran yang lebih besar dari masukannya. Biasanya rangkaian penguat daya direalisasikan dengan menggunakan FET (Field Effect Transistor), BJT (Bipolar Junction Transistor), maupun Op-Amp dengan jenis tertentu.

Tabel 3. 1 pembagian class penguat daya

Dalam realisasinya, penguat yang akan digunakan adalah penguat dengan class A yang menghasilkan sinyal yang penuh dengan fidelitas yang cukup baik.

Gambar 3.5 Rangkaian Penguat Daya Kelas A Dalam perealisaian power amplifier ini nilai R1 dan R2 akan menentukan nilai arus IB yang berpengaruh pada besar penguatan.

Gambar 3.6 Rangkaian Power Amplifier Yang Direalisasikan

III.3.3 Kopling

Kopling adalah sebuah rangkaian yang digunakan untuk menghubung-kan antara power system dan communication system.

Gambar 3.7 Kopling Isolasi Sistem

Kopling induktif ini direalisasikan dengan trafo dengan spesifikasi khusus untuk powerline transformer tipe VAC4085-X003 dengan daerah frekuensi operasi antara 1 MHz – 30 MHz.

Gambar 3.8 Konfigurasi Pin VAC4085-X003

Berikut adalah gambar dari skema rangkaian kopling yang digunakan :

Gambar 3. 9 Skema Rangkaian Kopling

Pada rangkaian kopling ditambahkan diode zener dengan Vz = 5 V untuk membatasi tegangan yang masuk dan keluar dari rangkaian kopling, sehingga apabila terjadi kondisi over voltage tidak akan merusak rangkaian.

III.3.4 Level converter

Blok level converter terdiri dari sejumlah transistor yang bekerja pada daerah cut off dan saturasi sebagai aplikasi switching. Digunakan untuk mengkorvesi tegangan pada sinyal info seberar 3.3 V ke bentuk tegangan TTL 5 V .

Gambar 3. 10 Rangkaian Level Converter OFDM menjadi pilihan teknik modulasi yang paling tepat bagi lingkungan kanal yang bergantung terhadap waktu di mana efek multijalur serta derau impulsif menjadi hambatan utama seperti kondisi kanal saluran listrik. Dalam OFDM base band, deretan bit data pertama-tama diubah dengan memodulasinya agar simbol tahan terhadap distorsi kanal. Teknik modulasi standar yang dipilih menggunakan metode pemetaan bit 4-QAM untuk kemudian dimodulasi kembali ke subcarrier- subcarrier ortogonal, dengan jarak frekuensi yang sama satu dengan lainnya sebesar ∆f NT Hz.dimana Ts adalah waktu sampling dan N adalah jumlah total sub-carrier. Sampling dan N adalah jumlah total sub-carrier.

III.4 Perancangan Model OFDM

OFDM menjadi pilihan teknik modulasi yang paling tepat bagi lingkungan kanal yang bergantung terhadap waktu di mana efek multijalur serta derau impulsif menjadi hambatan utama seperti kondisi kanal saluran listrik. Dalam OFDM base band, deretan bit data pertama-tama diubah dengan memodulasinya agar simbol tahan terhadap distorsi kanal. Teknik modulasi standar yang dipilih menggunakan metode pemetaan bit 4-QAM untuk kemudian dimodulasi kembali ke subcarrier- subcarrier ortogonal, dengan jarak frekuensi yang sama satu dengan lainnya sebesar ∆f NT Hz.dimana Ts adalah waktu sampling dan N adalah jumlah total sub-carrier. Sampling dan N adalah jumlah total sub-carrier. Sinyal OFDM base band didapatkan dengan penjumlahan N sub-carrier sinyal- sinyal termodulasi dan dapat dituliskan sebagai:

Untuk menghindari interferensi antar simbol (ISI) dan interferensi antar kanal (ICI), sejumlah sampel dari bagian akhir symbol OFDM diduplikasi kebagian awal. Bagian yang ditambahkan disebut cyclic prefix. Akhirnya, sinyal multicarrier baseband D(t) yang riil akan dibangkitkan setelah windowing dan pemfilteran low-pass dari sampel-sampel ranah waktu ini. Untuk mengacu pada kecepatan data sekitar 12 Mb/s, lebar pita yang berguna bagi kanal saluran listrik ialah sekitar 25 MHz.

Tabel 3.2 Parameter sistem OFDM bagi prototipe modem PLC mengacu pada

standar Homeplug 1.0

Gambar 3.11 Model Sistem Prototipe Modem PLC III.4.1 Representasi Bilangan

Pada penelitian ini dipilih format bilangan 2’s Complement Fixed-Point bertanda sepanjang 16-bit sebagai berikut :

dimana X adalah representasi 2’s Complement dari sebuah bilangan desimal 16-bit, pada jangkauan [-128 hingga 127,99609375], xn adalah bit-bit biner 0 dan 1. Sebagai contoh :

1101110100 0000002 = -896010 / 25610 =3510 0000010001 1011002 = 113210 / 25610 = 4,42187510 III.4.2 Diagram Alir Perancangan

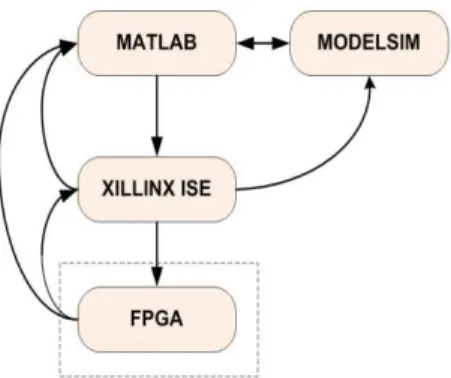

Gambar 3.12 Diagram Perancangan FPGA

IV. SINTESIS, PENGUKURAN DAN ANALISA IMPLEMENTASI

IV.1 Implementasi blok OFDM

Perangkat FPGA yang digunakan FPGA tipe Memec Virtex-4TM LC Development Kit yang menggunakan FPGA Xilinx XC4VLX25, 64MB DDR SDRAM, 10/100 Ethernet PHY, 100 MHz Clock source, RS-232 Port, dan rangkaian pendukung tambahan untuk mengembangkan sistem lengkap. Board ini juga dilengkapi dengan modul ekspansi standar Memec P160. Yang berisi chip digital berbasis RAM (Random Access Memory) yang dapat diprogram untuk melakukan fungsi-fungsi logika tertentu. Penyusun dasar dari FPGA adalah rangkaian CLB (Configurable Logic Block) dan LUT (Look-Up Table). Kedua rangkaian dasar inilah yang dapat disusun untuk membentuk rangkaian yang lebih kompleks. Berikut gambar dari blok tersebut :

Gambar 4.1 Xilinx Virtex-4 XC4VLX25 Penjelasan bagian dari masing-masing blok yang implementasikan pada FPGA adalah sebagai berikut :

IV.1.1. RS232 UART (Universal Asynchronous Receive and

Transmission)

UART digunakan untuk interfacing komputer dengan FPGA. Transmitter pada PC mengubah data karakter berupa data parallel menjadi bentuk serial dan secara otomatis menambahkan bit start, parity, dan bit stop.

Gambar 4. 2 Format Data UART

Pada blok yang diimplementasikan komunikasi serial menggunakan baud rate 115200 bps, bit data menggunakan 8 bit, 1 stop bit, dan flow control dipilih none.

Gambar 4.3 RS232 interface pada board FPGA Perangkat lunak yang digunakan pada komputer adalah serial port monitor seperti hyper terminal digunakan sebagai data masukan berupa data karakter. Berikut tampilan hyper terminal yang sudah dikoneksikan dengan RS232 pada FPGA.

Gambar 4. 4 Tampilan Serial Port Monitor Dan berikut gambar hasil desain RS232 setelah disintesis,

Gambar 4. 5 Blok RS232

IV.1.2. Serial ke Paralel / Paralel ke Serial

Pada blok pengubah serial ke paralel, bit-bit serial yang diterima Xi,k akan diubah per 2 bit untuk dikodekan menjadi simbol di blok selanjutnya. Begitu pula di bagian penerima, blok pengubah parallel ke serial akan mengubah setiap 2 bit yang telah diproses blok sebelumnya menjadi bit-bit yang akan dikeluarkan secara serial sesuai dengan baudrate yang telah dipilih.

Gambar 4. 6 Mapper 4-QAM IV.1.3.

Mapper

Bit-bit data yang telah dipecah secara parallel selanjutnya direpresentasikan dalam konstelasi 4 simbol kompleks yang berbeda oleh mapper 4 QAM. Selain dipetakan, simbol tersebut sekaligus dikalikan dengan konstanta

√ = + 0,707 dan -0,707 yang direpresentasikan dalam 16 bit format bilangan fixed point untuk menyamakan bobot tiap simbol hasil konstelasi. Pemetaan dilakukan berdasarkan tabel berikut.

Tabel 4. 1 Pengkodean 4 QAM

IV.1.4. Blok IFFT

Blok IFFT berfungsi sebagai osilator bank yang menghasilkan subcarrier yang saling orthogonal. Dari keseluruhan blok OFDM yang dirancang, blok Inverse/Fast Fourier Transfom merupakan blok yang paling besar memakan resource FPGA. Blok ini menerima dan mengeluarkan 64 data berupa symbol yang terdistribusi secara paralel. Blok ini terdiri dari beberapa blok pengolah data masukan mulai dari blok pengalamatan (address), blok dual RAM, blok IFFT.

Gambar 4. 7 Blok IFFT 64 titik

IV.1.5. FFT Radix-8

Perhitungan cepat FFT dilakukan dengan membagi 64 data masukan menjadi 8 data untuk diproses masing-masing dengan menggunakan FFT radix-8. Implementasi blok FFT radix-8 dibuat dengan menggunakan operator- operator yang telah dibuat pada library IEEE.STD_LO-GIC_ARITH, library IEEE.STD_LO-GIC_SIGNED, dan library IEEE. MATH_REAL.

Dengan penggunaan operator dari library-library ini, perhitungan FFT 8-titik dibangun langsung dengan state-machine dengan beberapa kondisi yang diarahkan untuk menghasilkan representasi keluaran data yang sama dengan hasil simulasi menggunakan MATLAB. Masukan dan keluaran blok ini telah dirancang dengan jumlah bit yang sama yakni 16 bit. Sehingga tidak ada faktor koreksi jumlah bit hasil masukan dan keluaran.

Data masukan yang diberikan merupakan bit-bit biner yang mere-presentasikan bilangan desimal dengan format fixed-point di mana 8 bit pertama termasuk MSB merepresentasikan bagian bilangan bulat integer) dan 8 bit selanjutnya termasuk LSB merepresentasikan bilangan pecahan. Bilangan bertanda direpresentasikan secara normal menggunakan aturan 2’s complement pada bilangan biner.

Gambar 4. 8 FFT radix 8 IV.1.6. Penyusunan Urutan Data

Data yang masuk ke RAM-keluaran diatur pada alamat yang memiliki jeda 8 indeks yakni 0,8,16,24,32,40,48,56 untuk delapan urutan pertama dan seterusnya serta dikeluarkan dengan indeks berurutan.

Gambar 4. 9 Aliran Data Blok Dasar RAM IV.1.7. Pembagi untuk inverse IFFT

Masukan yang masuk ke blok IFFT adalah data kompleks konjugat yang kemudian di FFT-kan kemudian keluarannya dibagi dengan 64 atau dikalikan 1/64. Pengimplementasian modul pembagi 64 cukup memakan resource pada FPGA dibanding dengan pengali 1/64. Oleh karena itu pada saat sinyal invert = ’1’, hasil keluaran FFT akan dikalikan dengan factor 0,015625 yang direpresentasikan oleh 16-bit bilangan biner 0000 0000 0000 0100. Untuk proses FFT, di mana sinyal invert =’0’, hasil perhitungan FFT cukup dikalikan dengan faktor 1 yang direpresentasikan oleh 16-bit bilangan biner 0000 0001 0000 0000.

Gambar 4. 10 Aliran data blok da IV.1.8. Blok transmitter modulator OFDM

Gambar 4. 11 Transmiter Modulator OFDM IV.1.9. Hasil Simulasi pada Modelsim

IV.1.9.1 RS232

Gambar 4. 12 Simulasi RS232

IV.1.9.2 Mapper

Gambar 4. 13 Simulasi Mapper IV.1.9.3. Parallel 32 To Parallel 8

Gambar 4. 14 Simulasi Parallel 32 To Parallel 8 asar RAM Blok transmitter modulator OFDM

Transmiter Modulator OFDM

Simulasi RS232

Mapper

Simulasi Parallel 32 To Parallel 8

IV.1.9.4. Transmitter Modulator OFDM

Gambar 4. 15 Simulasi Transmitter Modulator

IV.3 Implementasi pada FPGA

Gambar 4. 16 Diagram Alir Implementasi Pada FPGA

IV.3.1 Design Entity

Dalam langkah awal implementasi ini, dilakukan pembuatan atau penambahan kode VHDL berupa file dalam modul rancangan pada perangkat lunak Xilinx.

Gambar 4. 17 File Blok Transmiter

IV.3.2 Assigned Package Pin

Pada tahapan ini, dilakukan pemilihan pin masukan dan keluaran dengan disesuaikan dengan resource pada board FPGA yang digunakan, yaitu Xilinx Virtex IV.

Transmitter Modulator OFDM

Simulasi Transmitter Modulator OFDM

Diagram Alir Implementasi Pada FPGA

Dalam langkah awal implementasi ini, dilakukan pembuatan atau penambahan kode VHDL berupa file .vhd ke dalam modul rancangan pada perangkat lunak Xilinx.

File Blok Transmiter

Pada tahapan ini, dilakukan pemilihan pin masukan dan dengan resource pada board FPGA yang digunakan, yaitu Xilinx Virtex IV.

Gambar 4 18 Assigned Package pin keluaran

Pin yang berwarna biru merupakan pin

digunakan dalam board pin FPGA, warna merah menunjukan VCC sedangkan warna hijau merupakan pin ground.

IV.3.3 Sintesis

Gambar 4. 19. Tampilan IC RTL skematik

Gambar 4. 20 Tampilan IC RTL skematik

IV.3.4 Resource FPGA

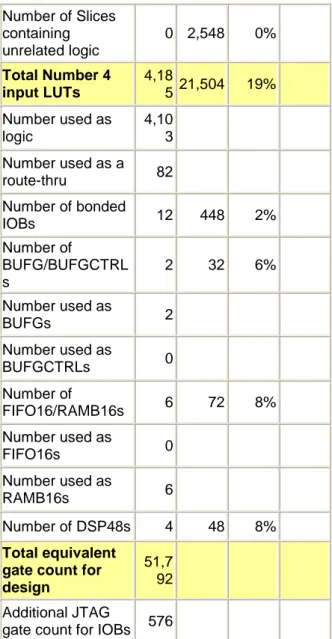

Tabel 4. 2 Penggunaan resource pada FPGA Device Utilization Summary

Logic Utilization Used Availa

ble Total Number Slice Registers 1,19 3 21,504 Number used as Flip Flops 1,19 2 Number used as Latches 1 Number of 4 input LUTs 4,10 3 21,504 Logic Distribution Number of occupied Slices 2,54 8 10,752 Number of Slices containing only related logic 2,54 8 2,548

Assigned Package pin masukan dan

berwarna biru merupakan pin-pin yang digunakan dalam board pin FPGA, warna merah menunjukan VCC sedangkan warna hijau merupakan pin ground.

Tampilan IC RTL skematik

Tampilan IC RTL skematik

Penggunaan resource pada FPGA Device Utilization Summary

Utiliza tion Note(s ) 5% 19% 23% 100% Number of Slices containing unrelated logic 0 Total Number 4 input LUTs 4,18 5 Number used as logic 4,10 3 Number used as a route-thru 82 Number of bonded IOBs 12 Number of BUFG/BUFGCTRL s 2 Number used as BUFGs 2 Number used as BUFGCTRLs 0 Number of FIFO16/RAMB16s 6 Number used as FIFO16s 0 Number used as RAMB16s 6 Number of DSP48s 4 Total equivalent gate count for design

51,7 92 Additional JTAG

gate count for IOBs 576

IV.4 Implementasi Blok Analog

Pada sub bab ini hasil implementasi blok analog dilakukan pengukuran satu persatu, yang selanjutnya setelah pengukuran dilakukan analisa terhadap kinerja serta

analog dan blok digital. IV.4.1 Pengukuran DAC

Pada pengukuran menunjukan hasil dari blok DAC adalah berupa level dekuantisasi dari bit modulator

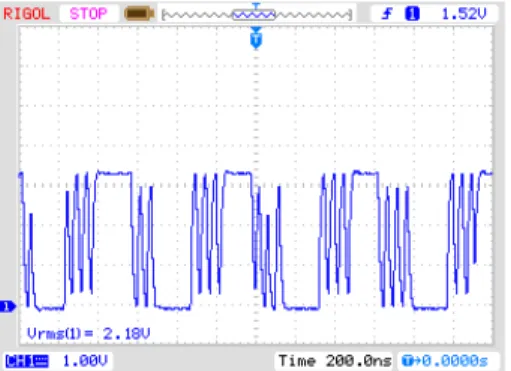

Gambar 4. 21 Keluaran Blok D/A IV.4.2 Pengukuran Penguat

Pada blok ini level tegangan sinyal hasil modulator dinaikan dari tegangan sekitar 4Vpp menjadi level tegangan sekitar 13,2Vpp. 2,548 0% 21,504 19% 448 2% 32 6% 72 8% 48 8%

Pada sub bab ini hasil implementasi blok analog dilakukan pengukuran satu persatu, yang selanjutnya setelah pengukuran dilakukan analisa terhadap kinerja serta penggabungan blok

Pada pengukuran menunjukan hasil dari blok DAC adalah berupa level dekuantisasi dari bit modulator.

Keluaran Blok D/A

Pada blok ini level tegangan sinyal hasil modulator Vpp menjadi level tegangan

Gambar 4. 22 Pengukuran Blok Penguat

IV.4.3 Pengukuran Level Converter

Dari hasil pengukuran level converter hasil konversi nilai tegangan inputan sebesar 3.3 v yang berasal dari FPGA, diubah menjadi level tegangan 5 V.

Gambar 4. 23 Pengukuran Blok Level Konverter

IV.4.4 Pengukuran kopling

Hasil pengukuran kopling magnetik tipe 4085 X003 menunjukan tingkat fidelitas yang baik terhadap sinyal artinya memiliki kemiripan sinyal inputan dengan sinyal keluaran setelah melewati kopling tersebut. Kopling ini mempunyai respon band pass filter.

Gambar 4. 24 Pengukuran Blok Kopling Kesimpulan

Pada penelitian desain dan realisasi modulator OFDM untuk jaringan jala-jala listrik tegangan rendah berbasis FPGA. Dapat diambil beberapa kesimpulan yaitu :

a. Pada blok power amplifier level tegangan sinyal hasil modulator. Sedangkan level tegangan dinaikkan dari 4 Vpp menjadi 13.2 Vpp.

b. Kopling magnetic mempunyai redaman yang besar, denagan nilai rata-rata redaman 6 db pada daerah stabil.

c. Pada blok DAC waktu konversi lebih lambat dibandingkan hasil keluaran FPGA mengakibatkan ketidakstabilan konversi.

d. Sistem OFDM hasil perancangan dapat diimplementasikan pada FPGA sehingga menghasilkan output 256 subcarrier termodulasi dengan modulasi masing-masing sub carrier 4-QAM.

e. Noise yang terdapat pada keluaran dari FPGA mengganggu kinerja blok analog.

f. Hasil sintesis pada Xilinx 8i menunjukkan periode minimum yang dibutuhkan untuk memproses sistem transmitter OFDM adalah 15.137ns, dengan delay kedatangan minimum input sebelum clock adalah 4.484ns, frekuensi maksimum yang didapat adalah 66.065 MHz, dan delay maksimum setelah clock adalah 4.007ns

Saran

1. Sebaiknya ditambahkan pengkodean kanal pada proses digital agar data lebih tahan terhadap noise. 2. Diperlukan analisa noise lebih mendalam untuk

mengetahui karakterisktik kanal PLC pada lingkungan IT TELKOM.

3. Untuk penelitian selanjutnya diwujudkan suatu blok modulator dan demodulator secara lengkap sehingga dapat diimplementasikan

DAFTAR PUSTAKA

[1] H. Hrasnica, A. Haidine, and R. Lehnert. Broadband Powerline Communication Network. John Willey & Sons Ltd. 2004, pp. 15.

[2] G. Held, Understanding Broadband over Power Line. New York: Auerbach Publication Taylor & Francis Group. 2006.

[3] S. Hara and R. Prasad, “Overview of Multicarrier CDMA”, IEEE Commun. Mag., vol.35pp. 126-133, Dec. 1997

[4] Pedroni, Volnei A., “Circuit Design with VHDL” MIT Press, London, England, 2004 [5] Darlis, Denny, “Perancangan dan Implementasi

Prosesor OFDM Baseband untuk Prototipe Modem PLC pada FPGA”, IT Telkom, Bandung, 2010

[6] R. Boylestad, L. Nashelky. Electronic Device and Circuit Theory. New Jersey: Prentice-Hall, Inc., 1992, pp. 671, 154-155, 673-674.

[7] P.A. Janse Van Rensburg. “Effective Coupling For Power-Line Communication.” D.Ing Dissertations, University of Johannesburg, South Africa, 2008

[8] Kadiran, Kamaru A. 2005. Design and Implementation of OFDM Transmitter adn Receiver on FPGA Hardware. Thesis pada Universiti Teknologi Malaysia : Tidak Diterbitkan.

[9] Orfanidis J., Sophocles. 2010. Introduction to Signal Processing. Rutgers University