UNIVERSITAS BINA NUSANTARA

Jurusan Sistem Komputer Skripsi Sarjana Komputer Semester Genap tahun 2003/2004

SISTEM PENGENALAN NUMERIK MENGGUNAKAN MATLAB DAN FPGA BERBASISKAN NEURAL NETWORK

Ryan Sudibyo 0400540435 Mimi Halim 0400540813 Delvi Kasydy 0400541192

Abstrak

Sistem pengenalan pola ini dibuat untuk analisa jaringan saraf tiruan dan melakukan implementasi pada FPGA. Manfaat yang diperoleh adalah agar sistem ini dapat diterapkan pada aplikasi yang lebih lanjut seperti pengenalan tulisan tangan atau pengenalan kode pos pada surat. Dalam sistem ini digunakan program Matlab pada komputer untuk melakukan perhitungan jaringan saraf tiruan dan konversi gambar serta FPGA sebagai media pengenalan numerik. Metode yang digunakan adalah jaringan saraf tiruan dengan menggunakan backpropagation. Berdasarkan hasil pengujian, didapatkan data bahwa dengan 15 neuron dan 40 input training dapat mendeteksi 57 karakter dari 60 karakter yang diujikan. Kesimpulan yang didapat dari percobaan ini adalah FPGA dapat digunakan untuk proses pengenalan numerik, semakin banyak input training maka jaringan saraf tiruan akan semakin pintar.

Kata kunci :

PRAKATA

Segala puji syukur penulis panjatkan kepada Tuhan Yang Maha Esa atas berkat dan rahmat-Nya sehingga penulisan skripsi ini dapat diselesaikan. Skripsi ini disusun untuk memenuhi salah satu syarat dalam menyelesaikan study strata-1 pada Sistem Komputer Fakultas Ilmu Komputer Universitas Bina Nusantara.

Skripsi dengan judul “Sistem Pengenalan Numerik Menggunakan Matlab dan FPGA Berbasiskan Neural Network” ini disusun atas bantuan dan dukungan secara langsung maupun tidak langsung dari berbagai pihak. Oleh sebab itu penulis menyampaikan ucapan terima kasih yang sebesar-besarnya kepada :

1. Orang tua dan keluarga, atas kasih sayang dan dukungannya yang luar biasa, baik secara moril maupun materiil kepada penulis.

2. Ibu Dr. Th. Widia S., MM. selaku Rektor Universitas Bina Nusantara yang telah memberikan kepercayaan dan kesempatan kepada penulis untuk menyelesaikan skripsi ini.

3. Bapak Iman H. Kartowisastro, Ph.D., selaku Ketua Jurusan Sistem Komputer yang telah memberikan kepercayaan kepada penulis untuk menyelesaikan skripsi ini. 4. Bapak Robby Saleh, S.Kom, selaku Sekretaris Jurusan Sistem Komputer yang telah

memberikan saran, bimbingan kepada penulis dalam penulisan buku.

5. Bapak Ario Witjakso.,MT, selaku dosen pembimbing yang telah memberikan ide, saran, dorongan dan bimbingan kepada penulis untuk menyelesaikan penyusunan skripsi ini.

7. Saudara Sofyan, S.Kom atas bimbingan, ide dan waktu yang telah diberikan kepada penulis dalam penyelesaian skripsi ini.

8. Saudara Antony Iskandar, S.Kom atas bimbingan, ide dan waktu yang telah diberikan kepada penulis dalam penyelesaian skripsi ini.

9. Rekan-rekan asisten lab UPT Perangkat Keras yang telah memberi masukan, ide, serta fasilitas yang mendukung di dalm penulisan skripsi ini.

10. Segenap civitas akademika Universitas Bina Nusantara tempat penulis menimba ilmu dan berkarya selama ini.

Akhirnya penulis merasa sangat bersyukur apabila skripsi ini dapat berguna bagi kepentingan orang banyak. Semoga karya tulis ini dapat bermanfaat bagi rekan-rekan pembaca dan dapat memberikan sumbangsih kepada Almamater dalam pengembangan ilmu pengetahuan dan teknologi.

Jakarta, 24 Juni 2004

DAFTAR ISI

Halaman

Halaman Judul Luar ... i

Halaman Judul Dalam ... ii

Halaman Persetujuan Hardcover ... iii

Halaman Pernyataan Dewan Penguji ... iv

Abstrak ... .. vii

Kata Pengantar ... viii

Informasi Pembuatan Buku ... x

Daftar Isi ... xi

Daftar Tabel ... xiv

Daftar Gambar ... xv

Daftar Lampiran ... xix

BAB 1 PENDAHULUAN 1. 1 Latar Belakang ... 1

1.2 Ruang Lingkup ... 2

1.3 Tujuan dan Manfaat ... 3

1.4 Metodologi Penulisan ... 3

BAB 2 LANDASAN TEORI

2.1 Pengenalan Pola ... 6

2.1.1 Binary Image ... 7

2.2 Jaringan Saraf Tiruan (Neural Network) ... 7

2.2.1 Model Jaringan Saraf Tiruan... 8

2.2.1.1 Neuron Sederhana ... 9

2.2.1.2 Fungsi Transfer atau Fungsi Aktivasi ... 10

2.2.1.3 Neuron dengan Input Vektor ... 11

2.2.2 Arsitektur Jaringan Saraf Tiruan ... 12

2.2.2.1 Single Layer of Neurons ……… 12

2.2.2.2 Multiple Layers of Neurons ………... 14

2.2.3 Learning Rule ... 15

2.2.3.1 Supervised Learning... 15

2.2.3.2 Unsupervised Learning... 16

2.2.3.3 Reinforcement Learning... 16

2.3 FPGA (Field Programmable Gate Array) ... 18

2.3.1 VHDL... 21

2.3.2 Xilinx Spartan ... 22

2.4 Matlab ... 22

2.5 Komunikasi Serial dan Paralel ... 22

2.5.1 Komunikasi Serial... 22

2.5.2 Komunikasi Paralel ... 23

2.6 Memory ... 23

2.6.2 RAM (Random Access Memory) ... 26

2.7 Seven Segment Display ... 27

BAB 3 PERANCANGAN SISTEM 3.1 Perancangan Dasar Sistem ... 31

3.1.1 Perancangan Input... 31

3.1.2 Perancangan Dasar Jaringan Saraf Tiruan ... 32

3.1.3 Perancangan Output ... 34

3.2 Perancangan Software... 35

3.2.1 Perancangan dengan Matlab ... 35

3.2.1.1 Pengolahan Gambar ... 36

3.2.1.2 Perancangan Jaringan Saraf Tiruan dengan Backpropagation 39 3.2.2 Perancangan Program Pengiriman Data ... 42

3.2.3 Perancangan dengan VHDL... 45

3.2.3.1 Perancangan Modul Utama ... 46

3.3 Perancangan Media Penyimpanan ... 48

BAB 4 IMPLEMENTASI DAN EVALUASI 4.1 Spesifikasi Sistem ... 51

4.2 Prosedur Operasional ... 52

4.2.1 Proses Konversi Input Gambar Menjadi Matriks ... 52

4.2.2 Proses Pengiriman Data ke FPGA dengan Parallel Port... 52

4.2.3 Proses Pengujian dalam FPGA... 53

4.3 Evaluasi Data ... 53

4.3.1.1 Analisa Mengenai Jumlah Neuron ... 54

4.3.1.2 Analisa Data Mengenai Jumlah Input Training... 60

4.3.2 Analisa Hasil Pengenalan Pola dengan FPGA... 66

4.4 Rangkuman Hasil Percobaan ... 86

BAB 5 KESIMPULAN 5.1 Kesimpulan ... 88

5.2 Saran... 88

DAFTAR PUSTAKA... 89

RIWAYAT HIDUP ... 91 LAMPIRAN-LAMPIRAN

DAFTAR TABEL

Tabel 2.1 Nama-nama Pin ROM ... 26

Tabel 3.1 Tabel Seven Segment ... 35

Tabel 3.2 Tabel Hubungan pin ROM dengan pin FPGA... 49

Tabel 4.1 Percobaan dengan 10 Neuron ... 55

Tabel 4.2 Percobaan dengan 15 Neuron ... 57

Tabel 4.3 Percobaan dengan 20 Neuron ... 58

Tabel 4.4 Percobaan dengan 20 Input Training ... 61

Tabel 4.5 Percobaan dengan 10 Input Training ... 62

Tabel 4.6 Percobaan dengan 30 Input Training ... 62

Tabel 4.7 Percobaan dengan 40 Input Training ... 64

Tabel 4.8 Perbandingan Hasil Testing pada FPGA ... 87

DAFTAR GAMBAR

Gambar 2.1 Perbandingan antara output dengan target ………... 8

Gambar 2.2 (a) Neuron sederhana tanpa bias (b) Neuron sederhana dengan bias… 9 Gambar 2.3 Fungsi aktifasi Hard Limit …………...……… 10

Gambar 2.4 Fungsi Aktifasi Linear …..…………...……….... 10

Gambar 2.5 Fungsi Aktifasi Log-Sigmoid ………...……….... 11

Gambar 2.6 Neuron dengan input vektor .…….…...……….... 12

Gambar 2.7 Single layer pada neuron …..…….…...……….... 13

Gambar 2.8 Matriks weight ………..…….…...……….... 13

Gambar 2.9 Multiple layer pada neuron ..…….…...……….... 14

Gambar 2.10 Notasi sederhana dari jaringan 3 layer ... 15

Gambar 2.11 Jaringan Adaline ………. 16

Gambar 2.12 Kategori Utama dari FPGA ……… 18

Gambar 2.13 Elemen Utama FPGA ………. 19

Gambar 2.14 Skematik CLB ……… 20

Gambar 2.15 Komunikasi Serial ... 22

Gambar 2.16 Komunikasi Paralel ... 23

Gambar 2.17 Pin EEPROM AT2816 ……… 25

Gambar 2.18 Seven Segment Display ……… 27

Gambar 2.19 Rangkaian Skematik CA ………. 28

Gambar 2.20 Rangkaian Skematik CC ………. 29

Gambar 3.1 Blok Diagram Sistem ……… 30

Gambar 3.2 Blok Diagram Perancangan Input ……… 31

Gambar 3.4 Rangkaian Seven Segment ……… 34

Gambar 3.5 LED Seven Segment pada FPGA ……….. 35

Gambar 3.6 Flowchart Jaringan Saraf Tiruan ……….. 39

Gambar 3.7 Tampilan awal program ………... 43

Gambar 3.8 Tampilan program input yang telah dikonversi ……… 43

Gambar 3.9 Flowchart Pengiriman Data ………. 44

Gambar 3.10 Rangkaian eksternal ROM ………. 48

Gambar 4.1 Input dan Output angka 0 Times New Roman ………. 66

Gambar 4.2 Input dan Output angka 1 Times New Roman ………. 67

Gambar 4.3 Input dan Output angka 2 Times New Roman ………. 67

Gambar 4.4 Input dan Output angka 3 Times New Roman ………. 67

Gambar 4.5 Input dan Output angka 4 Times New Roman ………. 68

Gambar 4.6 Input dan Output angka 5 Times New Roman ………. 68

Gambar 4.7 Input dan Output angka 6 Times New Roman ………. 68

Gambar 4.8 Input dan Output angka 7 Times New Roman ………. 69

Gambar 4.9 Input dan Output angka 8 Times New Roman ………. 69

Gambar 4.10 Input dan Output angka 9 Times New Roman ………... 69

Gambar 4.11 Input dan Output angka 0 MS Sans Serif ……… 70

Gambar 4.12 Input dan Output angka 1 MS Sans Serif ……… 70

Gambar 4.13 Input dan Output angka 2 MS Sans Serif ……… 70

Gambar 4.14 Input dan Output angka 3 MS Sans Serif ……… 71

Gambar 4.15 Input dan Output angka 4 MS Sans Serif ……… 71

Gambar 4.16 Input dan Output angka 5 MS Sans Serif ……… 71

Gambar 4.18 Input dan Output angka 7 MS Sans Serif ………... 72

Gambar 4.19 Input dan Output angka 8 MS Sans Serif ……… 72

Gambar 4.20 Input dan Output angka 9 MS Sans Serif ……… 73

Gambar 4.21 Input dan Output angka 0 Comic Sans Serif ………... 73

Gambar 4.22 Input dan Output angka 1 Comic Sans Serif ………... 73

Gambar 4.23 Input dan Output angka 2 Comic Sans Serif ……… 74

Gambar 4.24 Input dan Output angka 3 Comic Sans Serif ……… 74

Gambar 4.25 Input dan Output angka 4 Comic Sans Serif ……… 74

Gambar 4.26 Input dan Output angka 5 Comic Sans Serif ……… 75

Gambar 4.27 Input dan Output angka 6 Comic Sans Serif ……… 75

Gambar 4.28 Input dan Output angka 7 Comic Sans Serif ……… 75

Gambar 4.29 Input dan Output angka 8 Comic Sans Serif ……… 76

Gambar 4.30 Input dan Output angka 9 Comic Sans Serif ……… 76

Gambar 4.31 Input dan Output angka 0 Lucida Sans Unicode ………. 76

Gambar 4.32 Input dan Output angka 1 Lucida Sans Unicode ………. 77

Gambar 4.33 Input dan Output angka 2 Lucida Sans Unicode ………. 77

Gambar 4.34 Input dan Output angka 3 Lucida Sans Unicode ………. 77

Gambar 4.35 Input dan Output angka 4 Lucida Sans Unicode ………. 78

Gambar 4.36 Input dan Output angka 5 Lucida Sans Unicode ………. 78

Gambar 4.37 Input dan Output angka 6 Lucida Sans Unicode ………. 78

Gambar 4.38 Input dan Output angka 7 Lucida Sans Unicode ………. 79

Gambar 4.39 Input dan Output angka 8 Lucida Sans Unicode ………. 79

Gambar 4.40 Input dan Output angka 9 Lucida Sans Unicode ………. 79

Gambar 4.42 Input dan Output angka 1 Tahoma ……….. 80

Gambar 4.43 Input dan Output angka 2 Tahoma ……….. 80

Gambar 4.44 Input dan Output angka 3 Tahoma ……….. 80

Gambar 4.45 Input dan Output angka 4 Tahoma ……….. 81

Gambar 4.46 Input dan Output angka 5 Tahoma ……….. 81

Gambar 4.47 Input dan Output angka 6 Tahoma ……….. 81

Gambar 4.48 Input dan Output angka 7 Tahoma ……….. 82

Gambar 4.49 Input dan Output angka 8 Tahoma ……….. 82

Gambar 4.50 Input dan Output angka 9 Tahoma ……….. 82

Gambar 4.51 Input dan Output angka 0 Verdana ………. 83

Gambar 4.52 Input dan Output angka 1 Verdana ………. 83

Gambar 4.53 Input dan Output angka 2 Verdana ………. 83

Gambar 4.54 Input dan Output angka 3 Verdana ………. 84

Gambar 4.55 Input dan Output angka 4 Verdana ………. 84

Gambar 4.56 Input dan Output angka 5 Verdana ………. 84

Gambar 4.57 Input dan Output angka 6 Verdana ………. 85

Gambar 4.58 Input dan Output angka 7 Verdana ………. 85

Gambar 4.59 Input dan Output angka 8 Verdana ………. 85

Gambar 4.60 Input dan Output angka 9 Verdana ………. 86

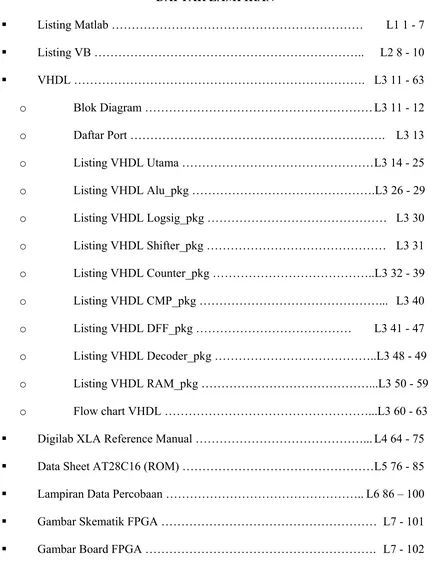

DAFTAR LAMPIRAN

Listing Matlab ……… L1 1 - 7

Listing VB ……….. L2 8 - 10

VHDL ………. L3 11 - 63

o Blok Diagram ……… L3 11 - 12

o Daftar Port ………. L3 13

o Listing VHDL Utama ……… L3 14 - 25

o Listing VHDL Alu_pkg ……….L3 26 - 29

o Listing VHDL Logsig_pkg ……… L3 30

o Listing VHDL Shifter_pkg ……… L3 31

o Listing VHDL Counter_pkg ………..L3 32 - 39

o Listing VHDL CMP_pkg ………... L3 40

o Listing VHDL DFF_pkg ……… L3 41 - 47

o Listing VHDL Decoder_pkg ………..L3 48 - 49

o Listing VHDL RAM_pkg ………...L3 50 - 59

o Flow chart VHDL ………...L3 60 - 63