Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 1

MODUL 6 PROYEK PERANCANGAN RANGKAIAN DIGITAL

Reno Rasyad (13511045)

Yonas Dwiananta (18011015)

Asisten: Rizka Widyarini

Tanggal Percobaan: 5/12/2012

EL2195-Praktikum Sistem Digital

Laboratorium Dasar Teknik Elektro - Sekolah Teknik Elektro dan Informatika ITB

Abstrak

Percobaan yang dilakukan kali ini adalah merancang sendiri

rangkaian digital yang terdiri dari tahapan desain,

implementasi, dan pengujuan sistem. Persyaratannya adalah :

menggunakan satu atau lebih interface yang ada di board

(VGA, soundcard, LCD, USB, dan lainnya), interaktif

(mempunyai input, push button, mouse, keyboard),

mempunyai bagian FSM, seidikitnya terdiri dari 3 blok.

Kata kunci: FPGA, VHDL, VGA.

1. P

ENDAHULUANPercobaan kali ini dilakukan dengan tujuan:

1. Menspesifikasikan suatu system digital

sederhana.

2. Membagi system menjadi satu atau lebih

jalur data dan kembali.

3. Mendesain jalur data untuk sistem.

4. Mendesain kendali untuk sistem.

5. Mengintegrasikan jalur data dan kendali ke

dalam sistem secara keseluruhan.

6. Melakukan tes menyeluruh terhadap sistem.

7. Mengimplementasikan

sistem

digital

menggunakan FPGA dan komponen

tambahan yang diperlukan.

8. Menguji dan menganalisa sistem yang

sudah dibangun

Untuk

itu,

dilakukan

percobaan

seperti

menghasilkan keluaran berwarna merah dan putih,

seperti bendera Indonesia pada layar, agar

praktikan mengerti apa saja yang sebenarnya

dibutuhkan untuk menghasilkan keluaran seperti

diatas. Percobaan membuat kotak bertujuan sama,

agar praktikan lebih paham lagi tentang kode

VHDL. Percobaan terakhir dilakukan agar

praktikan lebih mengerti fungsi counter dan cara

kerja menggerakkan suatu objek pada VGA.

2. S

TUDIP

USTAKA2.1

FSM

Ada dua jenis rangkaian yaitu rangkaian

kombinasional

dan

rangkaian

sekuensial.

Perbedaan mendasar dari kedua rangkaian

tersebut adalah ada tidaknya memori state.

Keluaran rangkaian sekuensial bergantung pada

state dan bergantung pada masuknya (rangkaian

Mealy) atau hanya tergantung pada state saja

(rangkaian Moore)

salah satu model yang sering digunakan untuk

membantu merancang rangkaian sekuensial

adalah Finite State Machine (FSM). Dinamakan

FSM karena jumlah state yang mungkin terbatas

dan rangkaian sekuensial bekerja mirip dengan

mesin yang beroperasi dengan urutan state.

Level abstaksi perancangan FSM pun

bertingkat-tingkat. pada perancangan dengan level behavioral,

sebelum mengimplementasikan menggunakan

VHDL, kita cukup membuat state diagram atau

flow chart statenya. Deklarasi-deklarasi yang harus

ada pada state diagram adalah deklarasi input dan

output, definisi state, transisi dan keluarannya.

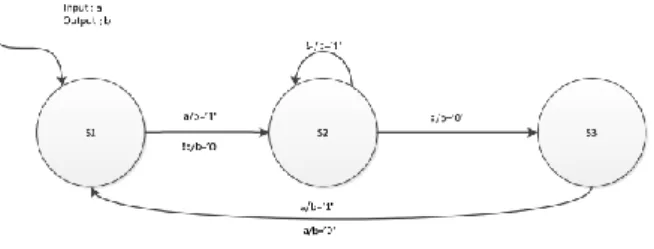

Gambar di bawah adalah contoh gambar state

diagram FSM Mealy .

2.2

VGA

Video Graphics Array (VGA) masih menjadi

interface yang populer untuk sebuah tampilan.

VGA interface ini masih banyak ditemukan di

beberapa device sekarang, misalnya layar LCD dan

proyektor. VGA interface ini terdapat juga di board

altera yang kita gunakan saat ini.

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 2

Pada percobaan kali ini tampilan VGA

digunakan agar tampilan hasil desain yang kita

rancang menjadi lebih menarik, tidak terbatas

hanya pada LED atau 7-Segment. Tujuan

percobaan kali ini juga adalah memberikan

ilustrasi penggunaan interface I/O yang ada pada

FPGA, misalnya GPIO, komunikasi serial

menggunakan RS232, Audio CODEC, LCD

karakter 16x2, dll. Interface ke VGA menggunakan

2 jenis sinyal, yaitu : sinyal warna (Merah, Hijau,

dan Biru) dan sinyal sinkron (horizontal dan

vertical). Berikut adalah penjelasan beberapa sinyal

yang digunakan :

a. Horizontal Sync (TTL level)

Sinyal ini akan aktif pada range piksel

kolom 0 sampai dengan 639. Sehingga

kalau sinyal ini tidak aktif, yang terjadi

adalah pergantian baris.

b. Vertical Sync (TTL level)

Sinyal ini akan aktif pada range piksel baris

0 sampai dengan 479. Sehingga kalau

sinyal ini tidak aktif, yang terjadi adalah

pergantian layar, atau kembali ke baris

pertama.

c. Sinyal RGB (Analog 3 pin: 0,7 – 1 V)

Sinyal ini merepresentasikan intensitas

untuk masing2 komponen warna merah,

hijau, dan biru untuk setiap pixel yang saat

itu aktif. Sehingga yang terjadi ketiga

sinyal ini berubah- ubah sesuai pixel yang

sedang aktif dalam proses scanning (dari

kiri ke kanan untuk setiap baris,

selanjutnya dari baris paling atas sampai

baris paling bawah).

3. M

ETODOLOGIPeralatan yang digunakan para percobaan ini

antara lain:

1. Komputer/PC

yang

telah

terinstal

program Quartus II

2. Catu daya + kabel dan konektor tambahan

serta kabel downloader

3. Monitor LCD

4. FPGA devepment board tipe ALTERA DE1

3.1

P

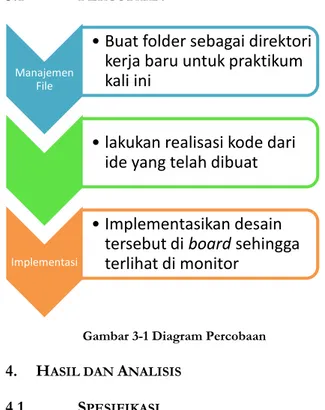

ERCOBAANGambar 3-1 Diagram Percobaan

4. H

ASIL DANA

NALISIS4.1

S

PESIFIKASIProyek yang praktikan buat adalah sebuah game

ping-pong sederhana. Game ini terdiri dari modus:

1. Modus 2 pemain: Game ini hanya

memungkinkan untuk dimainkan oleh dua orang

pemain

2. Single ball mode/ Multi-ball mode: Mode

standar adalah mode single-ball, sehingga pada

layar hanya terdapat satu bola saja. Sedangkan

apabila

mode

multi-ball

diaktifkan,

memungkinkan untuk adanya bola lebih dari satu

3. Reset score: Memungkinkan user untuk mereset

scorenya

Gameplay:

Bola akan berjalan dengan arah kanan-bawah pada

awalnya, lalu apabila menabrak dinding kanan,

arah horizontal bola akan berubah menjadi ke kiri

namun arah vertikal tetap. Apabila menabrak

dinding kanan juga arah horizontal akan berubah

menjadi ke kanan namun arah vertikal tetap.

Sedangkan apabila menabrak dinding atas, bawah,

ataupun kedua paddle arah vertikal bola akan

berubah (apabila awalnya ke arah atas akan

menjadi ke arah bawah, begitupun sebaliknya) dan

arah horizontal akan tetap.

Apabila bola memantul dikarenakan menabrak

dinding atas, score pada pemain yang di bawah

akan bertambah 1, dan apabila bola memantul

dikarenakan menabrak dinding bawah, score pada

pemain yang di atas akan bertambah 1.

Manajemen File

• Buat folder sebagai direktori

kerja baru untuk praktikum

kali ini

• lakukan realisasi kode dari

ide yang telah dibuat

Implementasi

• Implementasikan desain

tersebut di board sehingga

terlihat di monitor

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 3

Tugas pemain atas adalah menjaga agar bola tidak

memantul di batas atas dengan menggerakan

paddle yang dimilikinya ke kiri atau ke kanan,

demikian sebaliknya untuk pemain bawah. Pemain

dengan score terbanyak akan memenangkan game

ini.

4.2

P

ROSESD

ESAINTidak dibutuhkan waktu lama untuk membuat

konsep permainan ini, yang membutuhkan waktu

ialah merealisasikan konsep ini menjadi deretan

kode. Pada praktikum sebelumnya, kami telah

berhasil membuat permainan ping-pong sederhana

ini, tp tanpa scoring.

Setelah praktikum, kode untuk scoring dibuat.

Akan tetapi, pada saat hari praktikum selanjutnya,

score tidak muncul ke layar, sehingga dilakukan

perbaikan kode sampai akhirnya scoring bisa

muncul di layar monitor.

4.3

H

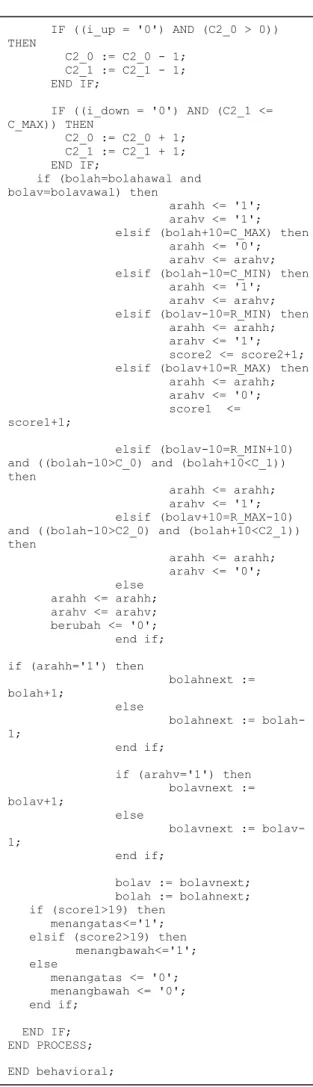

ASILBerikut adalah kode yang digunakan untuk

membuat game ping-pong ini:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY color_rom_vhd IS PORT( i_clk : IN STD_LOGIC; i_left : IN STD_LOGIC; i_right : IN STD_LOGIC; i_up : IN STD_LOGIC; i_down : IN STD_LOGIC; i_25 : IN STD_LOGIC; i_10 : IN STD_LOGIC; i_5 : IN STD_LOGIC; i_pixel_column : IN STD_LOGIC_VECTOR( 9 DOWNTO 0 ); i_pixel_row : IN STD_LOGIC_VECTOR( 9 DOWNTO 0 ); o_red : OUT STD_LOGIC_VECTOR( 7 DOWNTO 0 ); o_green : OUT STD_LOGIC_VECTOR( 7 DOWNTO 0 ); o_blue : OUT STD_LOGIC_VECTOR( 7 DOWNTO 0 )); END color_rom_vhd;

ARCHITECTURE behavioral OF color_rom_vhd IS

SHARED VARIABLE C_0 : INTEGER := 300; SHARED VARIABLE C_1 : INTEGER := 500; SHARED VARIABLE C2_0 : INTEGER := 300; SHARED VARIABLE C2_1 : INTEGER := 500; CONSTANT R_MAX : INTEGER := 480;

CONSTANT C_MAX : INTEGER := 640; CONSTANT C_scoreatas1 : INTEGER := 20; CONSTANT C_scoreatas2 : INTEGER := 40; CONSTANT C_scorebawah1 : INTEGER := 420; CONSTANT C_scorebawah2 : INTEGER := 440; CONSTANT R_MIN : INTEGER := 0;

CONSTANT C_MIN : INTEGER := 0; CONSTANT bolahawal : INTEGER := 600; CONSTANT bolavawal : INTEGER := 240; SHARED VARIABLE bolah : INTEGER:= 600; SHARED VARIABLE bolav : INTEGER:= 240; SHARED VARIABLE bolahnext : INTEGER:= 0; SHARED VARIABLE bolavnext : INTEGER:= 0; SIGNAL score1, score2, score1pul, score2pul : INTEGER:= 0;

SIGNAL div : BIT; SIGNAL M : STD_LOGIC; SIGNAL B : STD_LOGIC; SIGNAL arahh : STD_LOGIC; SIGNAL arahv : STD_LOGIC; SIGNAL berubah : STD_LOGIC; CONSTANT R1 : INTEGER := 277; CONSTANT R4 : INTEGER := 335; CONSTANT R7 : INTEGER := 306; CONSTANT C1kiri : INTEGER := 12; CONSTANT C4kiri : INTEGER := 12; CONSTANT C7kiri : INTEGER := 12; CONSTANT C1kanan : INTEGER := 37; CONSTANT C4kanan : INTEGER := 37; CONSTANT C7kanan : INTEGER := 37; CONSTANT C2 : INTEGER := 39; CONSTANT C3 : INTEGER := 39; CONSTANT C5 : INTEGER := 10; CONSTANT C6 : INTEGER := 10; CONSTANT R2atas : INTEGER := 284; CONSTANT R3atas : INTEGER := 313; CONSTANT R5atas : INTEGER := 313; CONSTANT R6atas : INTEGER := 284; CONSTANT R2bawah : INTEGER := 309; CONSTANT R3bawah : INTEGER := 338; CONSTANT R5bawah : INTEGER := 338; CONSTANT R6bawah : INTEGER := 309; SIGNAL seg_atkir1 : STD_LOGIC; SIGNAL seg_atkir2 : STD_LOGIC; SIGNAL seg_atkir3 : STD_LOGIC; SIGNAL seg_atkir4 : STD_LOGIC; SIGNAL seg_atkir5 : STD_LOGIC; SIGNAL seg_atkir6 : STD_LOGIC; SIGNAL seg_atkir7 : STD_LOGIC; SIGNAL seg_atkan1 : STD_LOGIC; SIGNAL seg_atkan2 : STD_LOGIC; SIGNAL seg_atkan3 : STD_LOGIC; SIGNAL seg_atkan4 : STD_LOGIC; SIGNAL seg_atkan5 : STD_LOGIC; SIGNAL seg_atkan6 : STD_LOGIC; SIGNAL seg_atkan7 : STD_LOGIC;

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 4

SIGNAL seg_bawkir1 : STD_LOGIC; SIGNAL seg_bawkir2 : STD_LOGIC; SIGNAL seg_bawkir3 : STD_LOGIC; SIGNAL seg_bawkir4 : STD_LOGIC; SIGNAL seg_bawkir5 : STD_LOGIC; SIGNAL seg_bawkir6 : STD_LOGIC; SIGNAL seg_bawkir7 : STD_LOGIC; SIGNAL seg_bawkan1 : STD_LOGIC; SIGNAL seg_bawkan2 : STD_LOGIC; SIGNAL seg_bawkan3 : STD_LOGIC; SIGNAL seg_bawkan4 : STD_LOGIC; SIGNAL seg_bawkan5 : STD_LOGIC; SIGNAL seg_bawkan6 : STD_LOGIC; SIGNAL seg_bawkan7 : STD_LOGIC; SIGNAL menangatas : STD_LOGIC; SIGNAL menangbawah : STD_LOGIC; COMPONENT CLOCKDIV IS

PORT (i_25: IN std_logic; i_10: IN std_logic; i_5: IN std_logic; CLK: IN std_logic; DIVOUT: buffer BIT); end COMPONENT; BEGIN clock : CLOCKDIV PORT MAP( i_25 => i_25, i_10 => i_10, i_5 => i_5, CLK => i_clk, DIVOUT => div ); PROCESS(score1, score2) BEGIN IF (score2 =2) THEN seg_bawkir1 <= '0'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '0'; seg_bawkir5 <= '0'; seg_bawkir6 <= '0'; seg_bawkir7 <= '0'; ELSIF (score2 =4 ) THEN

seg_bawkir1 <= '1'; seg_bawkir2 <= '1'; seg_bawkir3 <= '0'; seg_bawkir4 <= '1'; seg_bawkir5 <= '1'; seg_bawkir6 <= '0'; seg_bawkir7 <= '1'; ELSIF (score2 =6 ) THEN

seg_bawkir1 <= '1'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '1'; seg_bawkir5 <= '0'; seg_bawkir6 <= '0'; seg_bawkir7 <= '1'; ELSIF (score2 =8 ) THEN

seg_bawkir1 <= '0'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '0'; seg_bawkir5 <= '0'; seg_bawkir6 <= '1'; seg_bawkir7 <= '1'; ELSIF (score2 =10 ) THEN

seg_bawkir1 <= '1'; seg_bawkir2 <= '0'; seg_bawkir3 <= '1'; seg_bawkir4 <= '1'; seg_bawkir5 <= '0'; seg_bawkir6 <= '1'; seg_bawkir7 <= '1';

ELSIF (score2 =12 ) THEN seg_bawkir1 <= '1'; seg_bawkir2 <= '0'; seg_bawkir3 <= '1'; seg_bawkir4 <= '1'; seg_bawkir5 <= '1'; seg_bawkir6 <= '1'; seg_bawkir7 <= '1'; ELSIF (score2 =14 ) THEN

seg_bawkir1 <= '1'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '0'; seg_bawkir5 <= '0'; seg_bawkir6 <= '0'; seg_bawkir7 <= '0'; ELSIF (score2 =16 ) THEN

seg_bawkir1 <= '1'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '1'; seg_bawkir5 <= '1'; seg_bawkir6 <= '1'; seg_bawkir7 <= '1'; ELSIF (score2 =18 ) THEN

seg_bawkir1 <= '1'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '1'; seg_bawkir5 <= '0'; seg_bawkir6 <= '1'; seg_bawkir7 <= '1'; ELSE seg_bawkir1 <= '1'; seg_bawkir2 <= '1'; seg_bawkir3 <= '1'; seg_bawkir4 <= '1'; seg_bawkir5 <= '1'; seg_bawkir6 <= '1'; seg_bawkir7 <= '0'; END IF; IF (score1 =2) THEN seg_atkir1 <= '0'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '0'; seg_atkir5 <= '0'; seg_atkir6 <= '0'; seg_atkir7 <= '0'; ELSIF (score1 =4 ) THEN

seg_atkir1 <= '1'; seg_atkir2 <= '1'; seg_atkir3 <= '0'; seg_atkir4 <= '1'; seg_atkir5 <= '1'; seg_atkir6 <= '0'; seg_atkir7 <= '1'; ELSIF (score1 =6 ) THEN

seg_atkir1 <= '1'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '1'; seg_atkir5 <= '0'; seg_atkir6 <= '0'; seg_atkir7 <= '1'; ELSIF (score1 =8 ) THEN

seg_atkir1 <= '0'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '0'; seg_atkir5 <= '0'; seg_atkir6 <= '1'; seg_atkir7 <= '1';

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 5

ELSIF (score1 =10 ) THEN seg_atkir1 <= '1'; seg_atkir2 <= '0'; seg_atkir3 <= '1'; seg_atkir4 <= '1'; seg_atkir5 <= '0'; seg_atkir6 <= '1'; seg_atkir7 <= '1'; ELSIF (score1 =12 ) THEN

seg_atkir1 <= '1'; seg_atkir2 <= '0'; seg_atkir3 <= '1'; seg_atkir4 <= '1'; seg_atkir5 <= '1'; seg_atkir6 <= '1'; seg_atkir7 <= '1'; ELSIF (score1 =14 ) THEN

seg_atkir1 <= '1'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '0'; seg_atkir5 <= '0'; seg_atkir6 <= '0'; seg_atkir7 <= '0'; ELSIF (score1 =16 ) THEN

seg_atkir1 <= '1'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '1'; seg_atkir5 <= '1'; seg_atkir6 <= '1'; seg_atkir7 <= '1'; ELSIF (score1 =18 ) THEN

seg_atkir1 <= '1'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '1'; seg_atkir5 <= '0'; seg_atkir6 <= '1'; seg_atkir7 <= '1'; ELSE seg_atkir1 <= '1'; seg_atkir2 <= '1'; seg_atkir3 <= '1'; seg_atkir4 <= '1'; seg_atkir5 <= '1'; seg_atkir6 <= '1'; seg_atkir7 <= '0'; END IF; END PROCESS; PROCESS(i_pixel_row,i_pixel_column, i_left, i_right, i_up, i_down) BEGIN

IF ((i_pixel_column > C_0) AND

(i_pixel_column < C_1) AND (i_pixel_row = R_MIN+10) ) OR ((i_pixel_column > C2_0) AND (i_pixel_column < C2_1) AND

(i_pixel_row = R_MAX-10) ) THEN M <= '1'; ELSIF ((i_pixel_column > bolah-10) AND (i_pixel_column < bolah+10) AND

(i_pixel_row > bolav-10) AND (i_pixel_row < bolav+10) ) THEN M <= '1';

ELSIF ((i_pixel_column > C1kiri) AND (i_pixel_column < C1kanan) AND

(i_pixel_row = R1) AND (seg_bawkir1 = '1')) THEN M <= '1';

ELSIF ((i_pixel_column > C1kiri) AND (i_pixel_column < C1kanan) AND

(i_pixel_row = R4) AND (seg_bawkir4 = '1')) THEN M <= '1';

ELSIF ((i_pixel_column > C1kiri) AND (i_pixel_column < C1kanan) AND

(i_pixel_row = R7) AND (seg_bawkir7 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R2atas) AND (i_pixel_row < R2bawah) AND

(i_pixel_column = C2) AND (seg_bawkir2 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R3atas) AND (i_pixel_row < R3bawah) AND

(i_pixel_column = C3) AND (seg_bawkir3 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R5atas) AND (i_pixel_row < R5bawah) AND

(i_pixel_column = C5) AND (seg_bawkir5 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R6atas) AND (i_pixel_row < R6bawah) AND

(i_pixel_column = C6) AND (seg_bawkir6 = '1')) THEN M <= '1';

ELSIF ((i_pixel_column > C1kiri) AND (i_pixel_column < C1kanan) AND

(i_pixel_row = R1-100) AND (seg_atkir1 = '1')) THEN M <= '1';

ELSIF ((i_pixel_column > C1kiri) AND (i_pixel_column < C1kanan) AND

(i_pixel_row = R4-100) AND (seg_atkir4 = '1')) THEN M <= '1';

ELSIF ((i_pixel_column > C1kiri) AND (i_pixel_column < C1kanan) AND

(i_pixel_row = R7-100) AND (seg_atkir7 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R2atas-100) AND (i_pixel_row < R2bawah-100) AND

(i_pixel_column = C2) AND (seg_atkir2 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R3atas-100) AND (i_pixel_row < R3bawah-100) AND

(i_pixel_column = C3) AND (seg_atkir3 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R5atas-100) AND (i_pixel_row < R5bawah-100) AND

(i_pixel_column = C5) AND (seg_atkir5 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > R6atas-100) AND (i_pixel_row < R6bawah-100) AND

(i_pixel_column = C6) AND (seg_atkir6 = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > 0) AND

(i_pixel_row < 240) AND (i_pixel_column > 0) AND (menangbawah = '1')) THEN M <= '1';

ELSIF ((i_pixel_row > 240) AND (i_pixel_row < 639) AND (i_pixel_column > 0) AND (menangatas = '1')) THEN M <= '1'; ELSE

M <= '0'; END IF;

IF (B = '1') THEN o_red <= X"00"; o_green <= X"00"; o_blue <= X"FF"; ELSIF (M = '1') THEN o_red <= X"FF"; o_green <= X"00"; o_blue <= X"00"; ELSIF (M = '0') THEN o_red <= X"FF"; o_green <= X"FF"; o_blue <= X"FF"; END IF;

IF ((div'EVENT) AND (div = '1')) THEN IF ((i_left = '0') AND (C_0 > 0)) THEN C_0 := C_0 - 1; C_1 := C_1 - 1; END IF; IF ((i_right = '0') AND (C_1 <= C_MAX)) THEN C_0 := C_0 + 1; C_1 := C_1 + 1; END IF;

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 6

Setelah diimplementasikan, game ping-pong ini

berhasil ditampilkan di layar monitor dan

berfungsi dengan baik.

Gambar 4-1 Hasil Implementasi Percobaan, ditampilkan di layar monitor

Gambar 4-2 Hasil Implementasi Percobaan, ditampilkan di layar monitor

Gambar 4-3 Hasil Implementasi Percobaan, ditampilkan di layar monitor

Dapat dilihat bahwa implementasi berhasil

dilakukan, dengan menampilkan score di bagian

kiri layar (dapat dilihat di video).

4.4

K

ESESUAIANH

ASILD

ENGANS

PESIFIKASIPada spesifikasi awal, kami menginginkan adanya:

modus 2 pemain, single dan multi-ball mode, serta

reset score. Pada akhirnya, yang terealisasikan

adalah modus 2 pemain dan single-ball mode,

dengan

score

berbentuk

7segment

yang

ditampilkan pada layar monitor.

IF ((i_up = '0') AND (C2_0 > 0)) THEN C2_0 := C2_0 - 1; C2_1 := C2_1 - 1; END IF; IF ((i_down = '0') AND (C2_1 <= C_MAX)) THEN C2_0 := C2_0 + 1; C2_1 := C2_1 + 1; END IF; if (bolah=bolahawal and bolav=bolavawal) then arahh <= '1'; arahv <= '1'; elsif (bolah+10=C_MAX) then

arahh <= '0'; arahv <= arahv; elsif (bolah-10=C_MIN) then

arahh <= '1'; arahv <= arahv; elsif (bolav-10=R_MIN) then

arahh <= arahh; arahv <= '1'; score2 <= score2+1; elsif (bolav+10=R_MAX) then

arahh <= arahh; arahv <= '0'; score1 <= score1+1;

elsif (bolav-10=R_MIN+10) and ((bolah-10>C_0) and (bolah+10<C_1)) then

arahh <= arahh; arahv <= '1'; elsif (bolav+10=R_MAX-10) and ((bolah-10>C2_0) and (bolah+10<C2_1)) then arahh <= arahh; arahv <= '0'; else arahh <= arahh; arahv <= arahv; berubah <= '0'; end if; if (arahh='1') then bolahnext := bolah+1; else bolahnext := bolah-1; end if; if (arahv='1') then bolavnext := bolav+1; else bolavnext := bolav-1; end if; bolav := bolavnext; bolah := bolahnext; if (score1>19) then menangatas<='1'; elsif (score2>19) then

menangbawah<='1'; else menangatas <= '0'; menangbawah <= '0'; end if; END IF; END PROCESS; END behavioral;

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 7