VERIFIKASI FORMAL ALGORITMA TERDISTRIBUSI UNTUK MASALAH ALOKASI KANAL BERBASIS MUTUAL EXCLUSION PADA JARINGAN SELULAR

MENGGUNAKAN PROMELA/SPIN

Formal Verification of Distributed Algorithms for Channel Allocation Problem-Based Mutual Exclusion on a Cellular Network using Promela / Spin

Andi Yulia Muniar1

, Armin Lawi2, Merna Baharuddin3

Fakultas Teknik Universitas Hasanuddin [email protected]

Abstrak

Penelitian ini bertujuan membangun model formal algoritma terdistribusi (distributed algorithm) untuk masalah alokasi kanal berbasis Mutual Exclusion pada jaringan selular yang mana hanya ada satu kanal dalam jaringan selular dan jarak minimum reuse-nya tidak terhingga (infinity) menggunakan bahasa pemrograman PROMELA. Serta memverifikasi kebenaran algoritma dari spesifikasi masalah sistem terdistribusi dan menganalisis kinerja algoritma dengan menggunakan tools SPIN. Masalah mendasar dari Distributed Mutual Exclusion (DME) adalah pada waktu yang bersamaan hanya satu proses yang dapat masuk pada critical section. Dengan kata lain tidak ada dua proses yang berada di critical section pada saat yang bersamaan. Jika proses-proses ingin mengeksekusi critical resource pada waktu yang bersamaan, maka proses-proses tersebut harus bersaing untuk masuk ke dalam critical section. Hasil penelitian yang diperoleh yaitu dalam membangun model formal yang pertama dilakukan adalah merancang algoritma terdistribusi (distributed algorithm) untuk masalah alokasi kanal berbasis Mutual Exclusion kemudian algoritma diterjemahkan ke dalam bahasa pemrograman PROMELA, yang kemudian memverifikasi kebenaran algoritma tools SPIN.

Kata Kunci : Model formal, Distributed Mutual Exclusion, PROMELA/SPIN

1. Pendahuluan

Belakangan ini istilah “formal methods” (atau dapat diterjemahkan ke dalam bahasa Indonesia menjadi Metoda Formal) mulai ramai dibicarakan di majalah, jurnal, dan sumber informasi yang berhubungan dengan disain perangkat keras (hardware). Metode formal diperlukan diantaranya untuk melakukan verifikasi terhadap suatu pemodelan sistem, dan keperluan ini berkembang seiring dengan semakin kompleksnya sistem hardware yang dikembangkan oleh manusia.

Pada penelitian ini diteliti implementasi metode formal untuk kasus

ada dua proses yang berada di critical section pada saat yang bersamaan. Jika proses-proses ingin mengeksekusi critical resource pada waktu yang bersamaan, maka proses-proses tersebut harus bersaing untuk masuk ke dalam critical section.

Jadi dalam penelitian ini kami akan memperlihatkan hubungan antara kedua masalah pengalokasian kanal dan DME.

Secara khusus, kami akan

memperkenalkan verifikasi formal algoritma terdistribusi dalam menyelesaikan masalah alokasi kanal berbasis Mutual Exclusion (Mutex).

2. Tinjauan Pustaka

2.1. Teknologi Komunikasi Selular

Teknologi komunikasi terus berkembang seiring dengan bertambahnya tahun. Komunikasi tanpa kabel (wireless) cukup diminati di berbagai negara sebagai salah satu solusi untuk mencukupi kebutuhan sarana telekomunikasi. (I, Katzela et.al. 1996)

Peranan telekomunikasi bergerak, khususnya sistem komunikasi selular dirasakan semakin dibutuhkan keberadaannya. Karena diharapkan dengan adanya sarana telekomunikasi bergerak tersebut akan lebih dapat memudahkan bagi para pengguna untuk berkomunikasi. Sistem telekomunikasi bergerak selular, merupakan sistem telekomunikasi yang dapat menghubungkan pemakai pada telepon biasa dan pemakai telepon selular yang lain. cakupannya masing-masing dan beroperasi secara khusus. Jumlah sel pada suatu

daerah geografis adalah berdasarkan pada jumlah pelanggan yang beroperasi di daerah tersebut. (S, Faruque. 1996)

Suatu sel pada dasarnya merupakan pusat komunikasi radio yang berhubungan dengan MSC yang mengatur panggilan yang masuk. Jangkauan pengiriman sinyal pada sistem komunikasi bergerak selular dapat diterima dengan baik tergantung pada kuatnya sinyal batasan sel para pemakainya. Tetapi, masih terdapat faktor lain yang dapat menjadi kendala untuk sinyal yang dikirim dapat diterima dengan baik. Faktor lain yang dimaksud adalah faktor geografis (alam).

Ukuran sel pada system komunikasi selular dapat dipengaruhi oleh:

1. Kepadatan pada traffic.

2. Daya pemancar, yaitu Base Station (BS) dan Mobile Station (MS).

3. Dan faktor alam, seperti udara, laut, gunung, gedung-gedung, dan lain-lain.

Akan tetapi batasan-batasan tersebut akhirnya ditentukan sendiri oleh

critical resource. (G, Ricart, A.K, Agrawala. 1997)

Jadi, pada waktu yang bersamaan hanya satu proses yang dapat masuk pada critical section. Dengan kata lain, tidak ada dua proses yang berada di critical section pada saat yang bersamaan. Jika proses-proses ingin mengeksekusi critical resource pada waktu yang bersamaan, maka proses-proses tersebut harus bersaing untuk masuk ke dalam critical section.

2.4. Masalah Mutual Exclusion

Masalah mutual exclusion adalah suatu masalah mengatur akses untuk resource tunggal yang tidak dapat dibagi yang hanya dapat mendukung satu user pada suatu waktu. Hal ini dapat dipandang sebagai permasalahan dalam memastikan bahwa bagian-bagian tertentu kode program dieksekusi dalam daerah kritis (critical section), dimana tidak boleh 2 proses diizinkan dalam daerah kritis pada waktu yang sama.

Akses user ke resource dimodelkan sebagai suatu daerah kritis (critical section), yang mana adalah hanya ditunjuk suatu subset dari state-statenya. Ketika user tidak berniat menggunakan resource untuk mengeksekusi daerah kritisnya, maka user dikatakan berada dalam daerah sisa (remainder/non-critical section). Agar memperoleh hak masuk ke daerah kritis, user mengeksekusi trying protocol, dan setelah menggunakan resource, user mengeksekusi suatu exit protocol. Prosedur ini dapat diulang, sehingga masing-masing user mengikuti suatu siklus, perpindahan dari daerah remainder-nya (remainder section), R, ke daerah trying-nya (trying protocol), T, kemudian ke daerah kritis-nya (critical section), C, kemudian ke daerah exit-nya(exit protocol), E, dan kemudian kembali lagi ke daerah remainder-nya, R.

2.5. Algoritma Channel Allocation berbasis Mutual Exclusion

Seperti yang telah dipaparkan sebelumnya bahwa kanal sebagai critical resource dan sejumlah sel sebagai proses-proses yang bersaing untuk mengakses critical resource. Sebelumnya kita mulai dari perancangan algoritma untuk 2 proses (sel) yang bersaing memperebutkan critical resource. Dan selanjutnya untuk n -proses.

2.5.1. Algoritma dengan 2 Proses Algoritma Peterson2P:

, initially 0, writable by

i rem

2.5.2. Algoritma dengan n- Proses Algoritma Peterson nP: writable and readable by all processes

for every

, initially 0, writable

by

khususnya protokol komputer. PROMELA, yang merupakan kependekan dari PROcess MEta LAnguage, menggunakan basis CSP, bahasa C, dan SDL (Specification

Description Language). Selain

mengembangkan bahasanya, Holzmann juga mengembangkan sebuah tools yang diberi nama SPIN untuk melakukan validasi , tepatnya model checking terhadap spesifikasi yang ditulis dalam bahasa PROMELA. (Holzmann, Gerrard J. 1991)

Deskripsi dalam bahasa PROMELA ditulis dalam bentuk statement. Dalam variable atau isi dari message channel. Jika kondisinya benar (holds) maka statement melakukan model checking terhadap sistem yang ditulis dalam bahasa PROMELA. (Holzmann, Gerrard J. 1991)

(partial order reduction) search untuk spesifikasi yang besar.

Cara yang paling mudah untuk menggunakan SPIN adalah dengan simulasi. Simulasi akan berhenti ketika spesifikasi diakhiri/ terminate atau ketika terjadi fail/kegagalan. SPIN dapat melakukan suatu strict

analysis dari spesifikasi dengan

exhaustively searching p ad a s e mu a gagal/fail untuk menemukan spesifikasinya, custom analyzer akan menghasilkan path yang memaksa berbagai tahapan yang ditempuh agar hasil penelitian yang diperoleh memenuhi kaidah-kaidah ilmiah yang dilaksanakan secara cermat dan sistematis. Tahapan

menggunakan bahasa pemrograman PROMELA.

4. Verifikasi, melakukan model checking terhadap model yang telah

dirancang dalam bahasa PROMELA dengan menggunakan tools SPIN.

4. Hasil dan Pembahasan bahasa PROMELA sebagai berikut :

Algoritma dengan 2 Proses

Algoritma dengan n- Proses

4.1.2 Spesifikasi Model

Setelah kita merancang algoritma dan membangun model formal algoritma, kemudian dilakukan simulasi dan verifikasi dengan memasukkan model formal algoritma ke dalam tools SPIN.

#define true 1

4.2. Hasil Simulasi dan Verifikasi Model 4.2.1. Hasil Simulasi Model

Pada bagian ini dilakukan proses simulasi pada setiap model yang dibangun untuk melihat perilaku dari model dengan menggunakan SPIN.

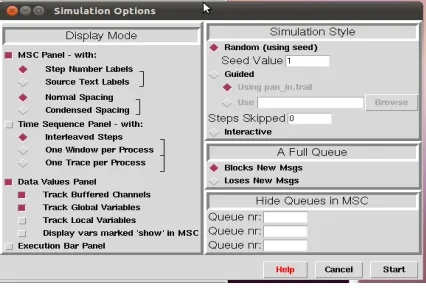

Dengan menggunakan XSPIN, parameter simulasi dapat diatur dengan jendela seperti terlihat pada gambar 1.

Gambar 1. Jendela Parameter Simulasi

Pada interface gambar 32 ada beberapa hal yang dapat diatur berkaitan dengan simulasi yang akan dilakukan. Yang pertama adalah panel apa saja yang akan ditampilkan selain panel standar

Simulation Output. Panel Message

Sequence Chart (MSC) akan menampilkan representasi grafis dari interaksi (pertukaran message) antar proses. Gambar yang muncul secara default dapat disimpan dalam file msc.ps. Panel Time Sequence (TS) menghasilkan representasi tekstual dari informasi yang serupa dengan yang muncul pada MSC. Tampilan dari TS ini dapat disimpan secara default ke file seq.out. Panel Data Value (DV) menghasilkan kondisi variabel-variabel lokal, global, maupun buffer selama simulasi berlangsung. Seluruh kondisi variable dapat disimpan secara default ke file var.out. Panel Execution Bar (EB) menampilkan informasi tentang berapa banyak (persentase) step yang dieksekusi oleh tiap proses. Tampilan grafis EB dapat disimpan secara default ke file panbar.ps.

Simulasi dari setiap model penyelesaian masalah mutual exclusion yang dibangun sebagai berikut:

Simulasi Algoritma dengan 2 Proses

Simulasi algoritma Peterson dengan 2 proses dengan menggunakan tools SPIN sebagai berikut :

a. Snapshot panel Simulation output :

Gambar 2 Awal Simulasi

Sedangkan pada snapshot akhir simulasi dapat dilihat pada gambar berikut.

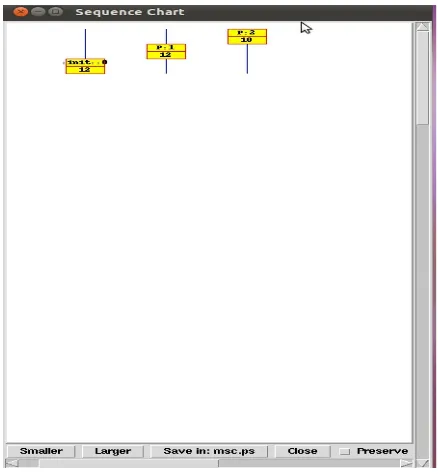

Gambar3 Akhir Simulasi b. Snapshot panel Message Sequence Chart.

Pada panel Message Sequence

Chart (MSC) akan menampilkan

representasi grafis dari interaksi (pertukaran message) antar proses. Berdasarkan hasil simulasi MSC diperoleh bahwa ada 3 proses dianataranya proses initiasialisasi (proses 0), proses 1 dan proses 2. Dimana proses 0 (init) terminate

pada step ke-12, proses 1 terminate pada step ke-10, dan proses 2 terminate pada step ke-12. Berikut snapsot panel MSC dari algoritma 2 proses.

Gambar 4 Tampilan Akhir MSC c. Snapshot panel Data value :

Gambar 5 Data Value d. Snapshot panel execution bar chart

Gambar 6. Awal execution bar chart Pada gambar 6 terlihat bahwa proses 0 (initialisasi) dilakukan dengan 1 step, yakni pada step 0 sesuai dengan snapshot simulation output.

Gambar7 Akhir execution bar chart Pada gambar 7 terlihat bahwa dari ketiga proses yang dibuat, hasil execution bar chart-nya diantaranya proses 0 dieksekusi sebanyak 2 step yakni pada step 2 dan step 12. Proses 1 dieksekusi sebanyak 5 step dan proses 2 sebanyak 5 step yang masing-masing dapat dilihat dari hasil simulation output sebelumnya.

Jadi, dari simulasi dapat dilihat bahwa 2 proses 1 dan 2 dapat saling bergantian memasuki critical section. Prinsip masuk ke critical section, proses P0

mengeset flag[0] = true, dan melihat apakah ada proses lain yang mencoba masuk critical section (turn=1). Jika tidak ada maka P0 masuk ke critical section.

Simulasi Algoritma dengan n-Proses

Simulasi algoritma Peterson dengan n-proses, dimana n=5 dengan menggunakan tools SPIN sebagai berikut :

a. Snapshot panel Simulation output :

Gambar 8 Awal Simulasi

Sedangkan pada snapshot akhir simulasi dapat dilihat pada gambar berikut.

Gambar 9 Akhir Simulasi

Dari gambar dilihat bahwa ada 6 proses yang dibuat diantaranya proses 0 (initialisasi), proses 1, proses 2, proses 3, proses 4 dan proses 5 dan diproses sebanyak 425 step.

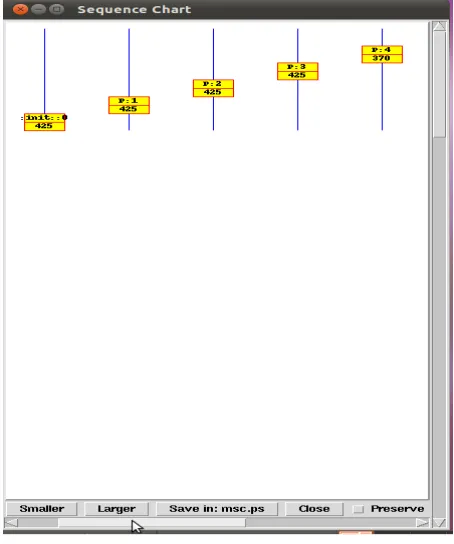

b. Snapshot panel Message Sequence Chart.

Pada panel Message Sequence

Chart (MSC) akan menampilkan

representasi grafis dari interaksi (pertukaran message) antar proses. Berdasarkan hasil simulasi MSC diperoleh 6 proses yang dibuat diantaranya proses 0

(initialisasi), proses 1, proses 2, proses 3, proses 4 dan proses 5. Dimana proses 0 (init) terminate pada step ke-425, proses 1 terminate pada step ke-425, proses 2 terminate pada step ke-425, begitu seterusnya sampai denagn proses 5. Berikut snapsot panel MSC dari algoritma n proses (n=5).

Gambar 10. Tampilan Akhir MSC c. Snapshot panel Data value :

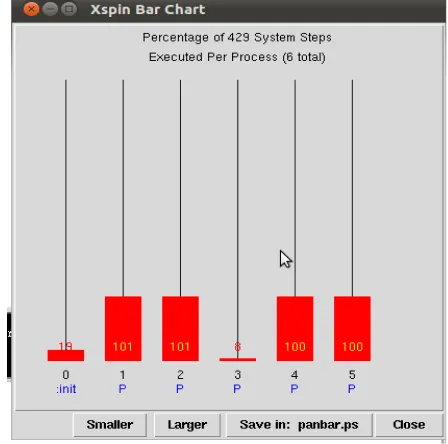

Gambar 11 Data Value d. Snapshot panel execution bar chart

Gambar 12 Awal execution bar chart Pada gambar 12 terlihat bahwa proses 0 (initialisasi) dilakukan dengan 1 step, yakni pada step 0 sesuai dengan snapshot simulation output.

Gambar 13 Akhir execution bar chart Pada gambar 13 terlihat bahwa dari ketiga proses yang dibuat, hasil execution bar chart-nya diantaranya proses 0 dieksekusi sebanyak 19, Proses 1 dieksekusi sebanyak 101 step, Proses 2 dieksekusi sebanyak 101 step, Proses 3 dieksekusi sebanyak 8 step, Proses 4 dieksekusi sebanyak 100 step dan proses 5 sebanyak 100 step yang masing-masing dapat dilihat dari hasil simulation output sebelumnya.

Jadi dari simulasi dapat dilihat bahwa proses-proses dapat saling bergantian memasuki critical section melihat nilai flag prosesor i dan variable turn yang dimiliki setiap level. Setelah prosesor i melewati semua level atau dengan kata lain bahwa prosesor i telah sampai pada variabel turn yang ke-n, maka prosesor i dapat masuk ke critical section.

2. Verifikasi Model

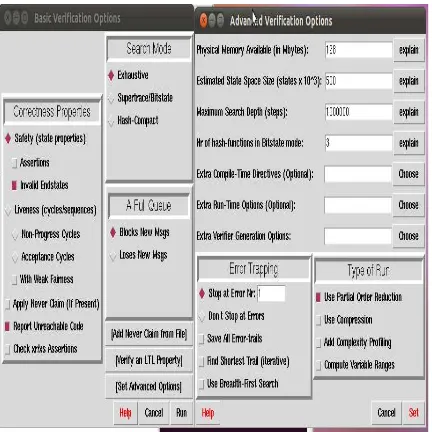

Dengan XSPIN, setting parameter verifikasi dilakukan pada window Verification Option, seperti terlihat pada gambar. Kalau dirasa masih kurang, dapat dilakukan setting lanjutan pada window Advanced Verification Option.

Gambar 14 window Verification Option Verifikasi setiap model penyelesaian masalah mutual exclusion yang dilakukan adalah dari segi :

1. Safety (state properties) dengan option

assertion dan invalid endstates

dihidupkan.

2. Liveness (cycles/seguence) dengan option non -progress cycles dihidupkan dan with weak fairness dihidupkan.

Verifikasi Algoritma 2P

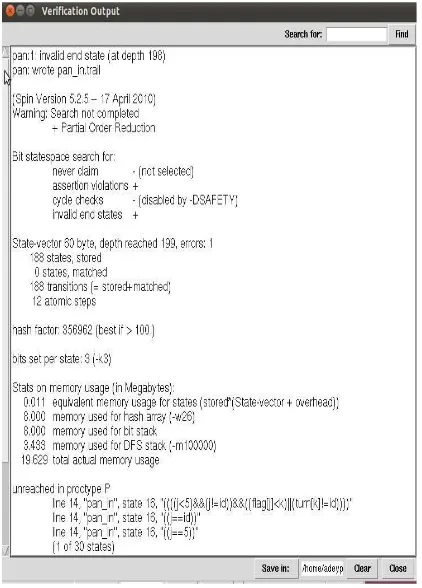

Verifikasi dari segi Safety (state properties) dengan option assertion dan invalid endstates dihidupkan, mode search supertrace/bitstate, didapat verifikasi sebagai berikut :

Verifikasi dari segi Liveness (cycle/sequence) dengan option non-progress cycles dihidupkan, dan with weak

fairness dihidupkan, mode search

supertrace/bitstate didapat verifikasi sebagai berikut :

non-progress cycles, malah terjadi fairness dalam memasuki critical section (tidak ada perlombaan untuk memasuki critical section).

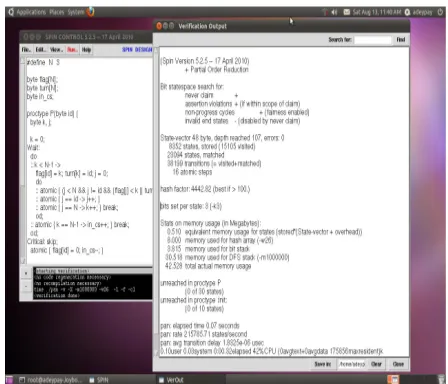

Verifikasi Algoritma n-P

Verifikasi dari segi Safety (state properties) dengan option assertion dan invalid endstates dihidupkan, mode search supertrace/bitstate, didapat verifikasi sebagai berikut :

Dari verifikasi ini dapat dilihat bahwa algoritma n-P mengalami invalid endstate pada depth 198 sehingga mutual exclusion tidak dapat ditangani. Untuk lebih jelasnya dapat dilihat pada simulasi dibawah ini :

Hasil simulasi baru setelah verifikasi :

Gambar 15 Awal simulasi

Gambar 17 Data Value

Gambar 18 Tampilan Message Sequence Chart

Verifikasi dari segi Liveness (cycle/sequence) dengan option non-progress cycles dihidupkan, dan with weak

fairness dihidupkan, mode search

supertrace/bitstate didapat verifikasi sebagai berikut :

Dari verifikasi ini dapat dilihat bahwa algoritma n-Proses juga tidak mengalami non-progress cycles, malah terjadi fairness dalam memasuki critical section (tidak ada perlombaan untuk memasuki critical section).

5.1 Kesimpulan

Berdasarkan penelitian yang telah dilakukan, maka dapat disimpulkan bahwa :

1. Dalam membangun model formal yang pertama dilakukan adalah merancang algoritma terdistribusi (distributed algorithm) untuk masalah alokasi kanal berbasis Mutual

Exclusion kemudian algoritma

diterjemahkan ke dalam bahasa pemrograman PROMELA.

2. Dalam memverifikasi kebenaran algoritma, model formal yang telah dibangun dimasukkan ke dalam tools SPIN kemudian disimulasi dan diverifikasi.

3. Bila simulasi yang dilakukan berhasil, belum tentu bahwa model tersebut diverifikasi kerjanya sudah benar

5.2. Saran

Dengan semakin kompleks dan besarnya sistem yang ada, menuntut pengujian model yang lebih teliti dan lebih cermat. Untuk itu kita harus melakukan rancangan algoritma secara baik dan benar. Tahapan yang dilakukan adalah membuat spesifikasi model secara formal, simulasi dan verifikasi.

Daftar Pustaka

[1] Djamal, Hidayanto. 2009. Perencanaan Sistem Terestrial. Jurusan Elektro FT-PKK. Universitas Mercu Buana.

[2] G, Ricart, A.K, Agrawala. 1997. An Optimal Algoritm for Mutual Exclusion in Computer Networks. Comm. ACM, pp. 9-17.

[3] Holzmann, Gerrard J. 1991. Design and Validation of Computer Protocols. Prentice-Hall.

[4] Hariyanto, Bambang. 1999. Sistem Operasi. Edisi 2. Informatika. Bandung.

[5] I, Katzela et.al. 1996. Channel Assigment Schemes for Cellular Mobile

Telecommunications Systems. IEEE

personal communication 10-31.

[6] Lynch, Nancy A., 1996. Distributed

Algorthms. Morgan Kaufman

Publishers,Inc. San Fransisco, California.

[7] Lawi, A., 2008. Quorum Based Conflict Resolution Algorithms in Distributed Systems. Department of Mathematics, Hasanuddin University. Makassar.

[8] Rahardjo, Budi. 1996. Formal Verification of Asynchronous Systems. University of Manitoba.

[9] Rahardjo, Budi. 2002. Paper Metoda Formal. Institut Teknologi Bandung. Bandung.