PENDAHULUAN

TINJAUAN PUSTAKA

- Kajian Pustaka

- Landasan Teori

- Cara Kerja Doppler RDF

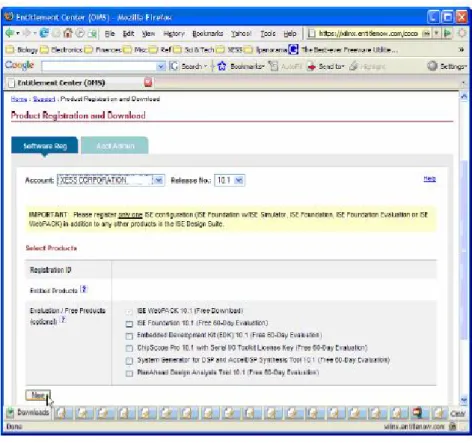

- Software Xilinx ISE Webpack 10.1

Sistem adaptif dapat membantu sistem menerima informasi kemudi blok berdasarkan intensitas sinyal tertinggi. Pesawat yang berada pada jarak tertentu akan menerima sinyal yang dipancarkan oleh DVOR untuk menentukan arah dan lokasinya. Sinyal yang diterima dari antena dikirim ke pemancar pada frekuensi yang lebih tinggi dari transmisi sebenarnya.

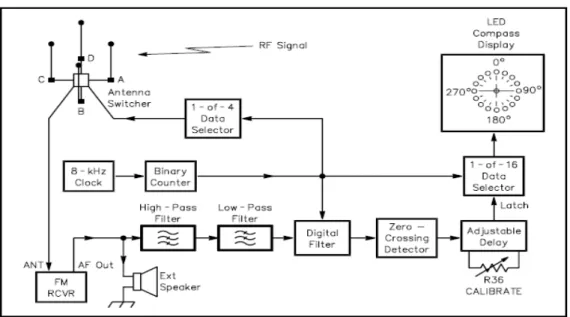

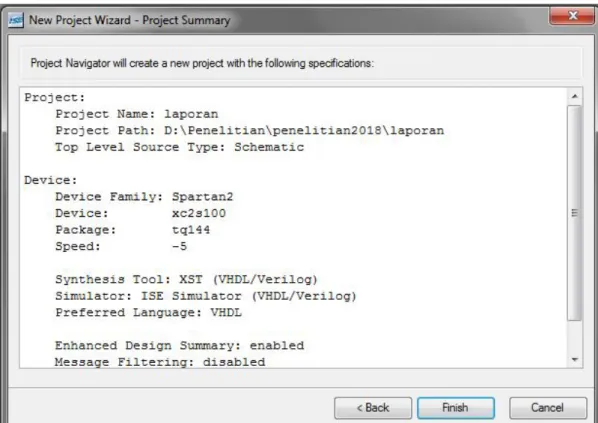

Sinyal yang diterima antena dikirim ke sumber transmisi sebenarnya pada frekuensi yang lebih rendah seperti yang ditunjukkan pada Gambar 2.1. Frekuensi sinyal yang diterima berkurang saat antena bergerak dari titik A ke titik B dan dari titik B ke titik C. Frekuensi sinyal yang diterima dari titik C sama dengan sinyal dari pemancar (tidak berubah) karena antena tidak lebih dekat atau lebih jauh dari sumber pencarian.

Sinyal RF yang diterima oleh antena pencarian dihubungkan ke antena input dari penerima FM VHF ke UHF pada Gambar 2.2. Langkah selanjutnya adalah masuk ke halaman tempat mendownload software ISE WebPACK 10.1 Klik opsi Download files individual lalu klik link download seperti pada Gambar 2.5.

METODOLOGI PENELITIAN

Alat dan Bahan Penelitian

Diagram Alir Penelitian

Desain counter 4 bit dan led dekoder

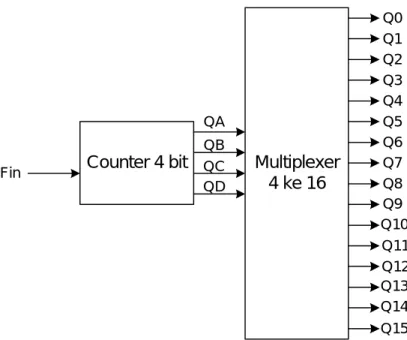

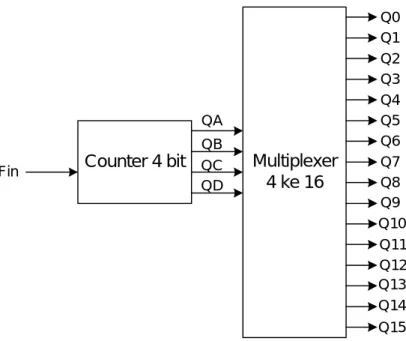

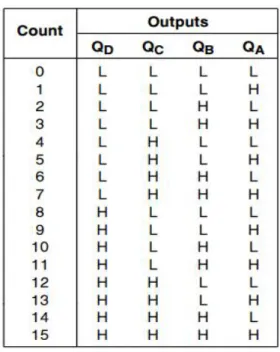

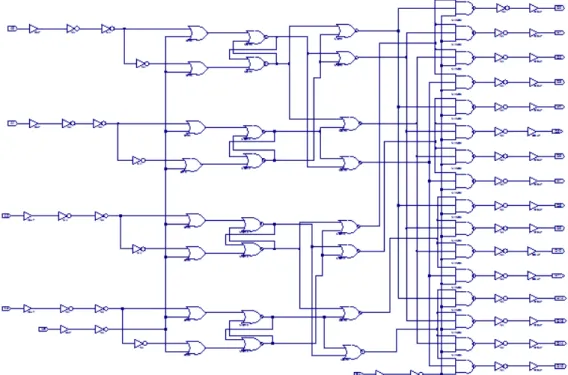

Rangkaian terdiri dari dua sub blok yaitu rangkaian pencacah 4 bit dan rangkaian LED dekoder 4 bit. Keluaran pencacah berupa BCD 4 bit (Qa, Qb, Qc dan Qd) yang diterapkan pada input dari rangkaian LED decoder yang berisi rangkaian 4 hingga 16 multiplexer.

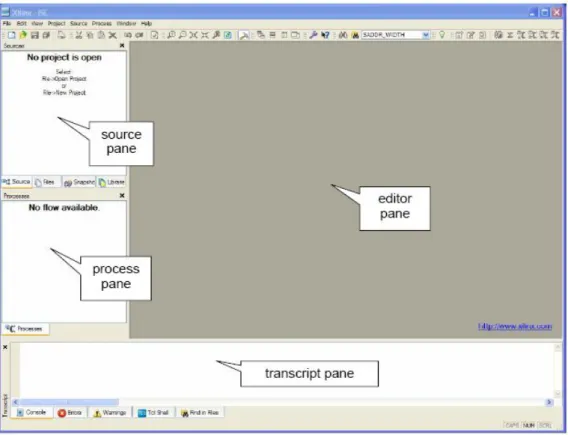

ISE project navigator

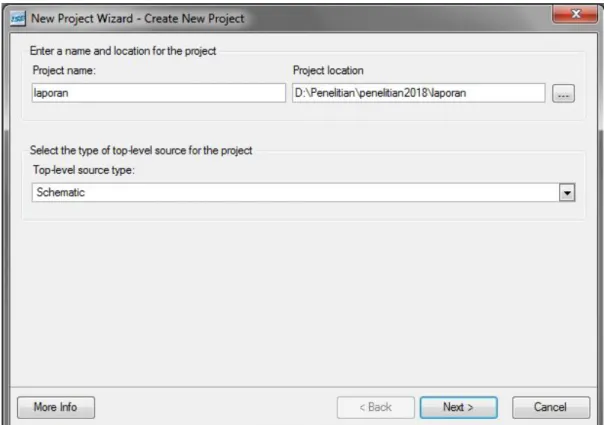

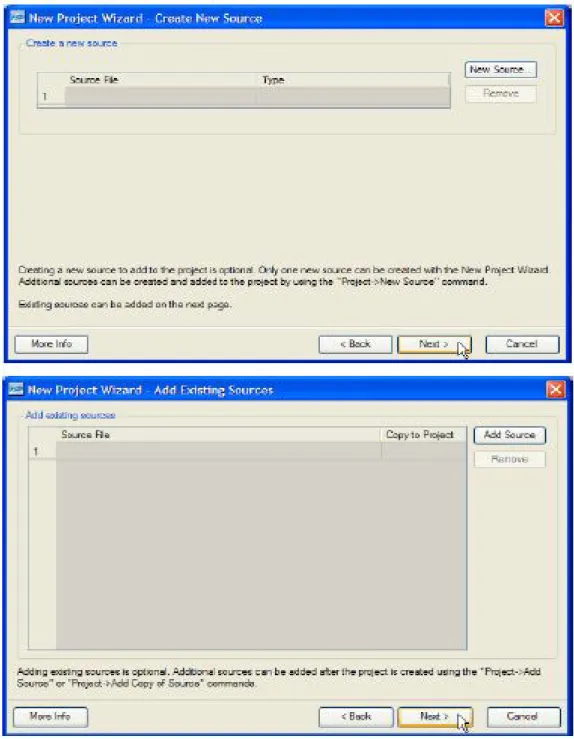

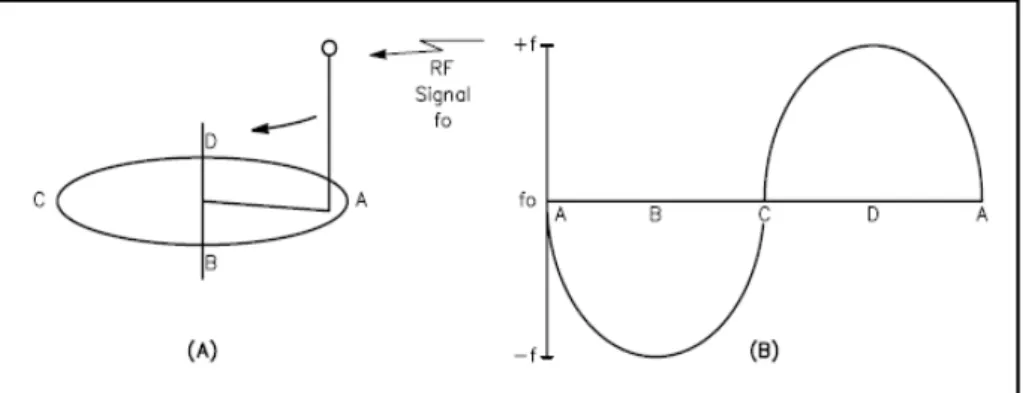

Panel sumber, organisasi file sumber desain, ada 4 tab sehingga kita dapat melihat modul fungsional, file sumber, snapshot, atau pustaka HDl untuk proyek tersebut. Mulailah mendesain proyek baru dengan memilih File → New Project untuk memunculkan jendela New Project Wizard di mana kita dapat mengetikkan nama proyek, lokasi file, dan jenis desain tingkat atas seperti yang ditunjukkan pada Gambar 3.4. Input desain yang akan digunakan untuk decoder LED menggunakan Skema, sehingga sumber tingkat atas adalah Skema.

Jenis FPGA yang meliputi: keluarga perangkat, nomor keluarga, paket dan kelas kecepatan ditunjukkan pada Tabel 3.1. Perancangan LED decoder menggunakan board XSA-100 sehingga nilai dapat dimasukkan pada jendela device properties seperti pada Gambar 3.5. Klik tombol berikutnya untuk menambahkan file dalam dua jendela (kami belum memiliki file untuk ditambahkan ke proyek).

Perancangan counter 4 bit dan multiplexer 4 ke 16

Langkah selanjutnya adalah menggambar rangkaian desain skematik yang terdiri dari pencacah 4 bit dan multiplekser 4 hingga 16 di jendela project.sch. Hasil simulasi menunjukkan bahwa rangkaian pencacah 4 bit yang telah dirancang sesuai dengan tabel kebenaran pencacah 4 bit. Desain pencacah 4 bit dan multiplekser 4 hingga 16 disimulasikan terlebih dahulu pada Xilinx ISE 10.1 untuk menentukan apakah kinerja pencacah 4 bit dan multiplekser 4 hingga 16 konsisten dengan hasil desain.

Simulasi pencacah 4 bit dan multiplexer 4 sampai 16 diawali dengan memberikan stimulus (input) pada rangkaian pencacah 4 bit dan multiplexer 4 sampai 16. Langkah selanjutnya adalah mensimulasikan rangkaian 4-bit counter dan multiplexer 4 to 16 yang inputnya diberikan seperti pada Gambar 4.8. Hasil simulasi menunjukkan bahwa rangkaian 4 bit counter dan 4 to 16 multiplexer yang dirancang sesuai dengan hasil rancangan.

Hasil simulasi menunjukkan bahwa desain skema rangkaian counter dan decoder 4 bit sudah sesuai dengan yang diharapkan. Rancangan pencacah dan dekoder 4 bit yang akan digunakan dalam pencari deteksi radio ditunjukkan pada Gambar 1. Hasil simulasi yang dihasilkan oleh ISE 10.1 harus dicocokkan dengan tabel kebenaran pencacah 4 bit.

Langkah selanjutnya adalah mensimulasikan rangkaian pencacah 4 bit dan multiplekser 4 hingga 16 diberikan sebagai input seperti yang ditunjukkan pada Gambar 10.

HASIL DAN PEMBAHASAN

Hasil pengujian rangkaian counter 4 bit

Hasil pengujian rangkaian multiplexer 4 ke 16

Langkah selanjutnya adalah mensimulasikan rangkaian multiplexer 4 sampai 16 saat menerima input seperti pada Gambar 4-5. Hasil simulasi yang dihasilkan oleh ISE 10.1 harus direkonsiliasi dengan tabel kebenaran multiplexer 4 hingga 16, seperti yang ditunjukkan pada Tabel 4.2. Setelah selesai mendesain pencacah 4 bit dan multiplekser 4 hingga 16 menggunakan input gambar skematis, langkah selanjutnya sebelum mengunduhnya ke chip FPGA adalah mensimulasikan program yang dibuat dengan program Xilinx ISE Simulator (ISim) versi 10.1.

Desain FPGA kedua adalah dekoder LED yang pada dasarnya terdiri dari multiplekser 4 hingga 16. Langkah selanjutnya adalah mensimulasikan rangkaian multiplexer 4 to 16 yang inputnya diberikan seperti pada Gambar 7. Hasil simulasi yang dihasilkan ISE 10.1 harus dicocokkan lagi dengan tabel kebenaran multiplexer 4 to 16.

Hasil simulasi menunjukkan bahwa rangkaian multiplexer 4 to 16 yang dirancang sesuai dengan tabel kebenaran multiplexer 4 to 16.

Hasil pengujian rangkaian counter dan multiplexer

PENUTUP

Kesimpulan

Pemindahan aliran bit ke cip FPGA XC2S100 telah dijalankan dan cip FPGA berfungsi mengikut hasil reka bentuk.

Saran

Ketersediaan IC tujuan khusus terkadang terbatas karena tidak lagi diproduksi dan menghilang dari pasar, sehingga dalam penelitian ini akan dirancang rangkaian pencacah dan dekoder 4-bit berdasarkan Sparta2 Field Programmable Gate Array (FPGA). Jenis chip Xc2S100 pada board XSA-100 dari Xess Corp, dengan desain input menggunakan skematik. Penelitian ini meliputi perancangan led counter dan decoder 4 bit menggunakan skematik, mensimulasikan hasil perancangan menggunakan perangkat lunak ISim, dan mentransfer program ke FPGA Xilinx Spartan 2. Pencacah 4-bit dapat terdiri dari 4 RS flip-flop yang saling terhubung antara output flip-flop dan input clock.

Frekuensi masukan yang diberikan pada rangkaian pencacah 4 bit ini adalah 8 KHz untuk menghasilkan frekuensi Doppler 500 Hz pada keluaran Q3 atau QD. Stimulus berupa test bench waveform berupa sinyal persegi yang diterapkan pada input Fin seperti pada Gambar 5. Langkah selanjutnya adalah mensimulasikan rangkaian ciunter 4 bit pada saat input seperti pada gambar 5.

Stimulus berupa test bench waveform berupa sinyal kotak yang diumpankan ke input D0, D1, D2 dan D3 seperti terlihat pada Gambar 7. Stimulus berupa test bench waveform berupa sinyal persegi panjang diumpankan ke input Fin seperti yang ditunjukkan pada Gambar 10.