IX.

IX.

RANGKAIAN LOGIKA KOMBINASIONAL

RANGKAIAN LOGIKA KOMBINASIONAL

AA.. PENDAHULUANPENDAHULUAN

-- SuatuSuatu rangkaianrangkaian diklasifikasikandiklasifikasikan sebagai

sebagai kombinasionalkombinasional jikajika memilikimemiliki sifat

sifat yaituyaitu keluarannyakeluarannya ditentukanditentukan hanya

hanya oleholeh masukkanmasukkan eksternaleksternal sajasaja.. hanya

hanya oleholeh masukkanmasukkan eksternaleksternal sajasaja..

-- SuatuSuatu rangkaianrangkaian diklasifikasikandiklasifikasikan sequential

sequential jikajika iaia memilikimemiliki sifatsifat keluarannya

keluarannya ditentukanditentukan oleholeh tidaktidak hanya

hanya masukkanmasukkan eksternaleksternal tetapitetapi jugajuga oleh

Lanjutan…….

Rangkaian Logika

Kombinasional Sequential

Sinkron/Clock mode Asinkron

Fundamental Pulse mode Gambar Rangkaian Logika

MODEL RANGKAIAN KOMBINASIONAL

MODEL RANGKAIAN KOMBINASIONAL

Rangkaian Logika Kombinasional (Komponen t1 t2 I1 I2 I F1 F2 F t1 t2 t Dengan Dengan :: F

F11 == FF11 (I(I11,, II22,,……IInn ;; tt11 == FF11 setelahsetelah tt11 F

F22 == FF22 (I(I11,, II22,,……IInn ;; tt22 == FF22 setelahsetelah tt22 --F

Fnn == FFnn (I(I11,, II22,,……IInn ;; ttnn == FFnn setelahsetelah ttnn (Komponen

tak ada Delay) t n

Lanjutan ……..

Lanjutan ……..

F

F (( kapitalkapital )) == SinyalSinyal steadysteady statestate dengandengan asumsi

asumsi tidaktidak adaada delaydelay.. tt (( kecilkecil )) == SifatSifat dinamisdinamis daridari sinyalsinyal tt (( kecilkecil )) == SifatSifat dinamisdinamis daridari sinyalsinyal

yang

yang dapatdapat berubahberubah selamaselama interval

B.

B. PROSEDUR PERANCANGAN

PROSEDUR PERANCANGAN

aa.. PokokPokok permasalahanpermasalahan sudahsudah ditentukanditentukan yaitu

yaitu jumlahjumlah inputinput yangyang dibutuhkandibutuhkan sertaserta jumlah

jumlah outputoutput yangyang tertentutertentu.. b

b.. SusunSusun kedalamkedalam tabeltabel kebenarankebenaran (Truth(Truth b

b.. SusunSusun kedalamkedalam tabeltabel kebenarankebenaran (Truth(Truth Table)

Table)..

cc.. KondisiKondisi don’tdon’t carecare dapatdapat diikutdiikut sertakansertakan apabila

C.

C. DECODER

DECODER

Decoder

Decoder adalahadalah rangkaianrangkaian kombinasikombinasi yangyang akanakan memilih

memilih salahsalah satusatu keluarankeluaran sesuaisesuai dengandengan konfigurasi

konfigurasi inputinput.. DecoderDecoder memilikimemiliki nn inputinput dan

dan 22nn outputoutput..

Blok

Blok DiagramDiagram DecoderDecoder.. Blok

Blok DiagramDiagram DecoderDecoder..

Decoder

n to 2

n IO I1 In YO Y1 Y (2n-1)Lanjutan ……..

Lanjutan ……..

Untuk

Untuk DecoderDecoder 22 toto 44

Decoder

IO Y ODecoder

n to 2

n I1 Y1 Y2 Y3Lanjutan …….

Lanjutan …….

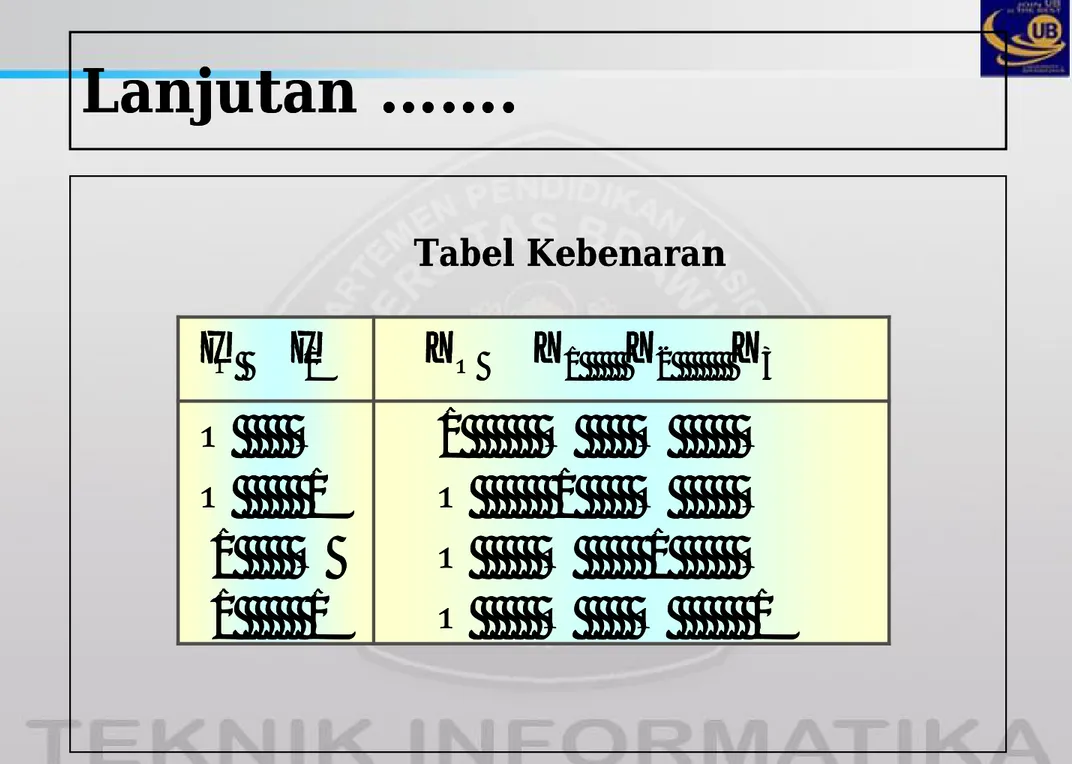

Tabel

Tabel KebenaranKebenaran

II

O OII

11Y

Y

O OY

Y

1 1Y

Y

2 2Y

Y

33O O

O O

O 1

O 1

1 O

1 O

1 1

1 1

1 O O O

1 O O O

O 1 O O

O 1 O O

O O 1 O

O O 1 O

O O O 1

O O O 1

RANGKAIAN LOGIKA

RANGKAIAN LOGIKA

I0 Y 0 Y1 I1 Y1 Y2 Y3Untuk

Untuk merancangmerancang rangkaianrangkaian kombinasionalkombinasional dapat

dapat digunakandigunakan DecoderDecoder dandan eksternaleksternal OROR gate

gate (rangkaian(rangkaian kombinasikombinasi nn -- inputinput dandan mm–– output

output dapatdapat diimplementasikandiimplementasikan dengandengan nn to

to 22nn lineline decoderdecoder dandan mm –– OROR gate)gate)..

Contoh Contoh..

Implementasikan

Implementasikan suatusuatu FullFull AdderAdder dengandengan memakai

memakai DecoderDecoder dandan 22 gerbanggerbang OROR Jawab

Jawab :: Sum

Sum == AA ⊕⊕ BB ⊕⊕ CinCin == ΣΣ 11,,22,,44,,77 Carry

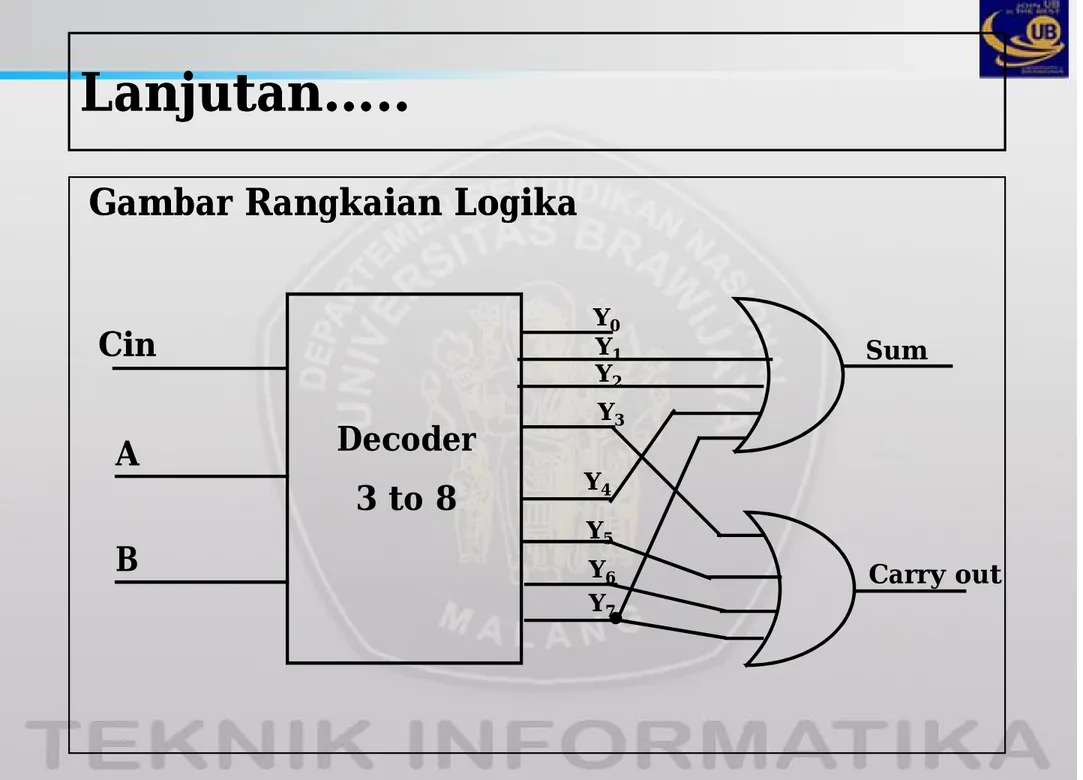

Lanjutan…..

Lanjutan…..

Gambar

Gambar RangkaianRangkaian LogikaLogika

Cin Y1 Y0 Y2 Sum Decoder 3 to 8 A B Y3 Y4 Y5 Y6 Y7 Carry out

CONTOH PERANCANGAN DECODER

CONTOH PERANCANGAN DECODER

Rancang

Rancang BCDBCD toto DesimalDesimal DecoderDecoder untukuntuk mengubah

mengubah BCDBCD keke sevenseven segmentsegment ?? Catatan

Catatan :: SevenSeven SegmentSegment.. a d g b c f e

D.

D. ENCODER

ENCODER

Encoder

Encoder adalahadalah rangkaianrangkaian kombinasikombinasi yangyang merupakan

merupakan kebalikankebalikan daridari DecoderDecoder yaituyaitu manghasilkan

manghasilkan outputoutput kodekode binerbiner yangyang berkorespondensi

berkorespondensi dengandengan nilainilai inputinput.. EncoderEncoder memiliki

memiliki 22nn inputinput dandan nn outputoutput..

memiliki

memiliki 22nn inputinput dandan nn outputoutput..

Tabel kebenaran Encoder 4 to 2 Tabel kebenaran Encoder 4 to 2

INPUT

INPUT OUTPUTOUTPUT II0 0 II1 1 II2 2 II3 3 X YX Y 1 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 X = II2 + 2 + II33 Y = II1 + 1 + II33

E.

E. MULTIPLEXER ( MUX )

MULTIPLEXER ( MUX )

Blok

Blok DiagramDiagram LogikaLogika MuxMux..

Mux 0

1

Input Data Output

N x 1 n

A B

Input Data

PROSEDUR PERANCANGAN RANGKAIAN PROSEDUR PERANCANGAN RANGKAIAN

KOMBINASIONAL DENGAN MUX KOMBINASIONAL DENGAN MUX

1

1.. BuatBuat tabeltabel kebenarankebenaran sesuaisesuai dengandengan kondisikondisi input

input dandan outputoutput sertaserta nomornomor MintermnyaMintermnya.. 2

2.. SalahSalah satusatu variabelvariabel inputinput digunakandigunakan sebagaisebagai Data

Data dandan sisanyasisanya daridari variabelvariabel inputinput sebagaisebagai address/selector

address/selector.. 3

3.. BuatBuat tabeltabel ImplementasiImplementasi dandan lingkarilingkari nomornomor 3

3.. BuatBuat tabeltabel ImplementasiImplementasi dandan lingkarilingkari nomornomor Mintermnya

Mintermnya yangyang sesuaisesuai dengandengan outputnyaoutputnya.. 4

4.. JikaJika 22 MintermnyaMintermnya dalamdalam satusatu kolomkolom dilingkari,

dilingkari, makamaka inputinput MuxMux adalahadalah 11 dandan sebaliknya

sebaliknya inputinput MuxMux adalahadalah berlogikaberlogika 00 5

5.. JikaJika nomornomor MintermnyaMintermnya hanyahanya dilingkaridilingkari padapada salah

salah satusatu barisbaris dalamdalam kolomkolom yangyang sama,sama, makamaka input

input MuxMux akanakan berlogikaberlogika sesuaisesuai dengandengan barisbaris persamaan

Contoh Contoh !!

Implementasikan

Implementasikan F(ABC)F(ABC) == ΣΣ11,,33,,55,,66 dengan

dengan MuxMux ((44xx 11)).. Jawab Jawab:: Tabel Kebenaran. Tabel Kebenaran. Minterm Minterm I N P U TI N P U T O U T P U T O U T P U T Minterm Minterm A B C A B C FF 0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 0 0

Lanjutan………

Lanjutan………

Catatan

Catatan..

Input

Input Variabel

Variabel A

A diambil

diambil sebagai

sebagai data

data

sedangkan

sedangkan B

B dan

dan C

C sebagai

sebagai address

address..

Tabel Implementasi.

Tabel Implementasi.

Tabel Implementasi.

Tabel Implementasi.

II

00II

11II

22II

33A

A

0

0

1

1

0

0

1

1

A

A

0

0

1

1

1

1

0

0

0

0

1

1

A

A

A

A

GAMBAR RANGKAIAN LOGIKA GAMBAR RANGKAIAN LOGIKA

Mux I0 I1 I A F 4 X 1 I2 I3 B C A

F.

F. DEMULTIPLEXER (DEMUX)

DEMULTIPLEXER (DEMUX)

Blok

Blok Diagram

Diagram Logika

Logika DEMUX

DEMUX

DEMUX I Y0 Y1 DEMUX 1 x (n + 1) I Input Select/addressA B Y1 Y n

X.

X.

RANGKAIAN LOGIKA KOMBINASIONAL

RANGKAIAN LOGIKA KOMBINASIONAL

A

A.. ADDER

ADDER

Manipulasi matematika seperti

Manipulasi matematika seperti

menjumlah,mengurang,mengali dan

menjumlah,mengurang,mengali dan

membagi dapat dilakukan dengan

membagi dapat dilakukan dengan

membagi dapat dilakukan dengan

membagi dapat dilakukan dengan

logika penjumlahan.

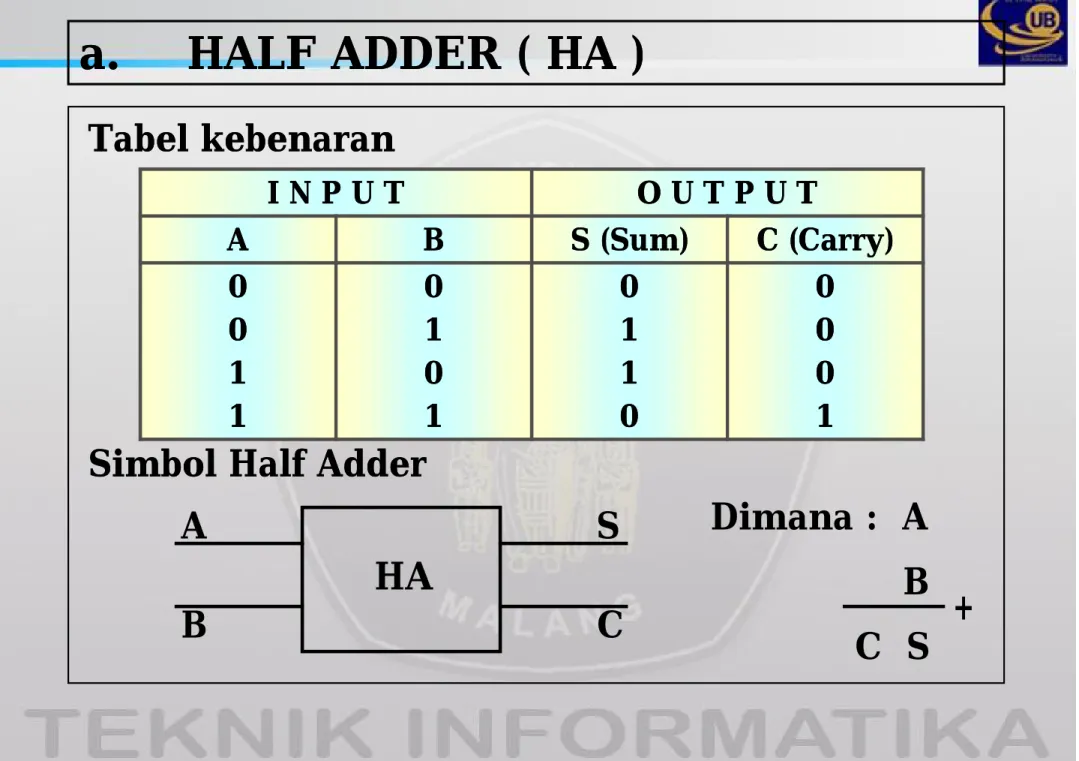

a.

a.

HALF ADDER ( HA )

HALF ADDER ( HA )

Tabel

Tabel kebenarankebenaran I N P U T

I N P U T O U T P U TO U T P U T

A

A BB S (Sum)S (Sum) C (Carry)C (Carry)

0 0 0 0 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 0 0 Simbol

Simbol HalfHalf AdderAdder 1 1 1 1 0 0 1 1 1 1 0 0 0 0 1 1 HA A C B S Dimana : A B C S +

Lanjutan…….

Lanjutan…….

Persamaan

Persamaan outputoutput Untuk

Untuk SumSum

1 1 0 0 A’ A’ B B B’ B’ S = AB’ + A’B = A S = AB’ + A’B = A ⊕⊕ BB Untuk Carry Untuk Carry C = AB C = AB 1 1 0 0 A’ A’ 0 0 1 1 A A 0 0 0 0 A’ A’ 1 1 0 0 A A B B B’ B’

Lanjutan ……..

Lanjutan ……..

Rangkaian

Rangkaian LogikaLogika A

S B

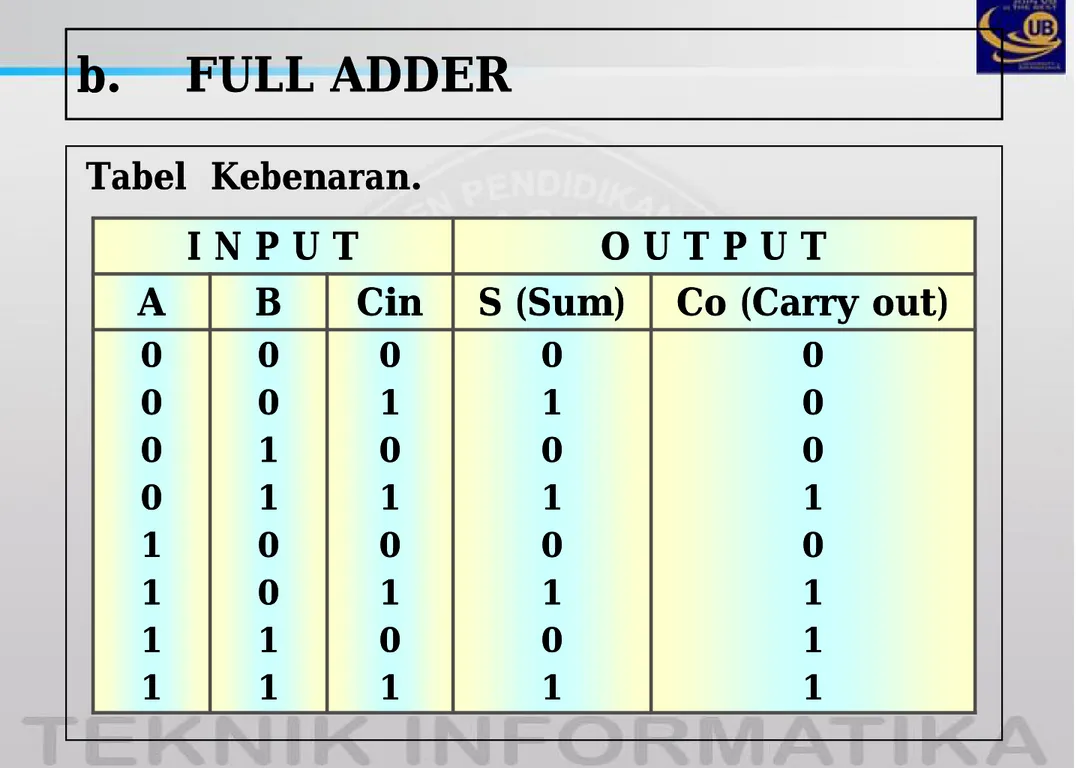

b.

b.

FULL ADDER

FULL ADDER

Tabel

Tabel KebenaranKebenaran..

I N P U T

I N P U T O U T P U TO U T P U T A

A BB CinCin S (Sum)S (Sum) Co (Carry out)Co (Carry out)

0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 0 0 0 0 1 1 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 0 1 1 0 0 1 1 1 1 1 1

Lanjutan ……..

Lanjutan ……..

Simbol

Simbol FullFull AdderAdder

F A A B Cin S Co Cin Co Cin A B Co S +

Persamaan Output (Metode Minterm)

Persamaan Output (Metode Minterm)

S

S == A’B’CinA’B’Cin ++ ABCin’ABCin’ ++ AB’Cin’AB’Cin’ ++ ABCinABCin =

= A’A’ (B’Cin(B’Cin ++ BCin’)BCin’) ++ AA (B’Cin’(B’Cin’ ++ BCin)BCin) =

= A’A’ (B(B ⊕⊕ Cin)Cin) ++ AA (B(B ⊕⊕ Cin)’Cin)’ =

= AA ⊕⊕ BB ⊕⊕ CinCin Co

Co == A’BCinA’BCin ++ AB’CinAB’Cin ++ ABCin’ABCin’ +ABCin+ABCin =

= CinCin (A’B(A’B ++ AB’)AB’) ++ ABAB (Cin’(Cin’ ++ Cin)Cin) =

Gambar Rangkaian Logika

Gambar Rangkaian Logika

Cin

S

A B

Lanjutan ……..

Lanjutan ……..

Atau

Atau

HA Cin S HA HA A B CoB.

B. SUBTRACTOR

SUBTRACTOR

Untuk

Untuk memahami

memahami azas

azas –– azas

azas rangkaian

rangkaian

pengurang

pengurang (subtractor)

(subtractor) kita

kita ikuti

ikuti aturan

aturan

pengurangan

pengurangan biner

biner sebagai

sebagai berikut

berikut ::

1

1.. Half

Half Subtractor

Subtractor (HS)

(HS)..

1

1.. Half

Half Subtractor

Subtractor (HS)

(HS)..

A

A –– B

B =

= D

D (Difference)

(Difference).. B

B (Borrow)

(Borrow)

0

0 –– 0

0 =

= 0

0

0

0 –– 1

1 =

= 1

1

1

1 –– 0

0 =

= 1

1

1

1 –– 1

1 =

= 0

0

dan Borrow 1Lanjutan ……

Lanjutan ……

Aturan

Aturan tersebut

tersebut kita

kita nyatakan

nyatakan dalam

dalam

tabel

tabel kebenaran

kebenaran..

I N P U T I N P U T O U T P U T O U T P U T I N P U T I N P U T O U T P U T O U T P U T A B A B DIDI BOBO 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 0 0 0 0 1 1 0 0 0 0 A B Bo DI +

Lanjutan ……

Lanjutan ……

Simbol

Simbol Half

Half Subtractor

Subtractor (HS)

(HS)

HS

A DI

Persamaan

Persamaan output

output..

Untuk

Untuk

DI

DI =

= A’B

A’B +

+ A’B

A’B =

= A

A +

+ B

B

Bo

Bo =

= A’

A’ B

B

RANGKAIAN LOGIKA HS

RANGKAIAN LOGIKA HS

DI A B BO B2.

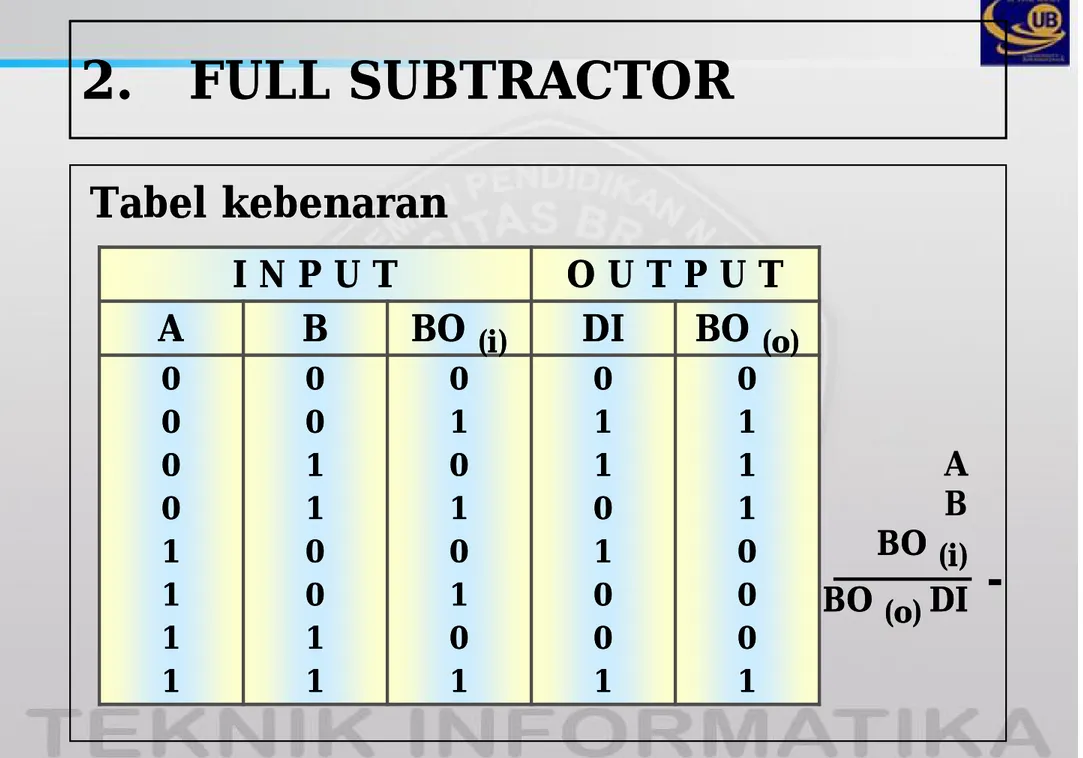

2. FULL SUBTRACTOR

FULL SUBTRACTOR

Tabel

Tabel kebenaran

kebenaran

I N P U T

I N P U T O U T P U TO U T P U T A

A BB BO BO (i)(i) DIDI BO BO (o)(o) 0 0 00 00 00 00 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 0 0 1 1 0 0 0 0 1 1 0 0 1 1 1 1 1 1 0 0 0 0 0 0 1 1 A B BO BO (i)(i) BO BO (o)(o) DIDI

-Lanjutan ………

Lanjutan ………

Simbol

Simbol Full

Full Subtractor

Subtractor (FS)

(FS)

BO

(i)FS

A

B

DI

BO

(o)RANGKAIAN LOGIKA FULL SUBTRACTOR

RANGKAIAN LOGIKA FULL SUBTRACTOR

DI BO (i)

BO (o) A

Lanjutan…….

Lanjutan…….

Atau

Atau

HS BO (i) DI HS HS A B BO (o)C.

C. COMPARATOR

COMPARATOR

Adalah

Adalah suatu

suatu rangkaian

rangkaian kombinasi

kombinasi yang

yang

berfungsi

berfungsi sebagai

sebagai pembanding

pembanding 2

2 variabel

variabel

dengan

dengan multi

multi bit

bit..

Gambar

Gambar Blok

Blok Diagram

Diagram Comparator

Comparator

Gambar

Gambar Blok

Blok Diagram

Diagram Comparator

Comparator

Comparator A>B A<B A=B A B

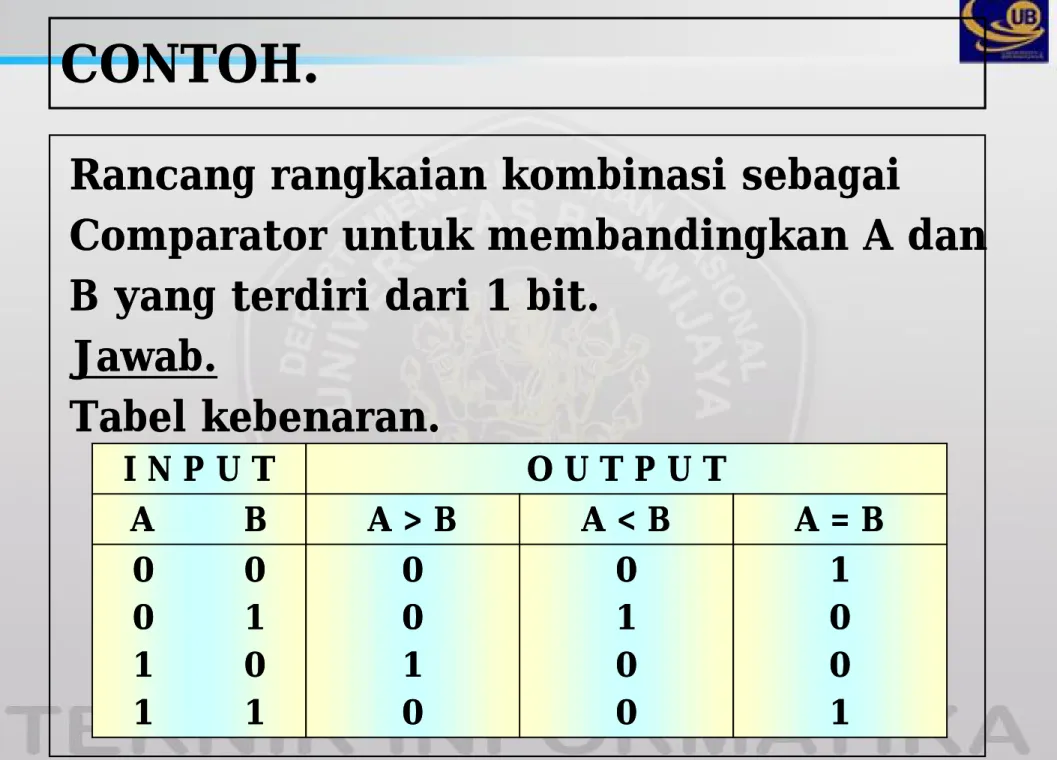

CONTOH.

CONTOH.

Rancang

Rancang rangkaian

rangkaian kombinasi

kombinasi sebagai

sebagai

Comparator

Comparator untuk

untuk membandingkan

membandingkan A

A dan

dan

B

B yang

yang terdiri

terdiri dari

dari 1

1 bit

bit..

Jawab

Jawab..

Jawab

Jawab..

Tabel

Tabel kebenaran

kebenaran..

I N P U T I N P U T O U T P U TO U T P U T A B A B A > BA > B A < BA < B A = BA = B 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1

Lanjutan ……..

Lanjutan ……..

Persamaan

Persamaan Boolean

Boolean

F

F (A

(A >

> B)

B) =

= AB’

AB’

F

F (A

(A <

< B)

B) =

= A’B

A’B

F

F (A

(A <

< B)

B) =

= A’B

A’B

F

F (A

(A =

= B)

B) =

= (AB)’

(AB)’ +

+ AB

AB =

= (A

(A +

+ B)’

B)’

Lanjutan …….

Lanjutan …….

Rangkaian Logika A B A>B A<B Tugas.Rancang dengan Comparator untuk

membandingkan A dan B yang masing – masing variabel terdiri dari 2 bit

B A<B