Available online at : http://bit.ly/InfoTekJar

InfoTekJar : Jurnal Nasional Informatika dan

Teknologi Jaringan

ISSN (Print) 2540-7597 | ISSN (Online) 2540-7600

System Digital

Model Dan Simulasi Prototype Rangkaian Digital Konversi Gerbang AND,

OR, NOT Menjadi Gerbang NAND Dan NOR

Helmi Fauzi Siregar

1, Muhammad Dedi Irawan

21,2Program Studi Teknik Informatika, Universitas Asahan,Jl. Jend. Ahmad Yani Kisaran 21244, Sumatera Utara, Telp : (0623) 347222

KEYWORDS

A B S T R A K

Gerbang AND, OR, NOT, Rangkaian

Multilevel, Gerbang NAND dan NOR, Prototype

Dalam mempelajari rangkaian digital, khususnya pada materi gerbang logika pada sistem digital ada sebuah Rangkaian kombinasi Gerbang AND, OR, NOT yang dapat dikonversi ke Rangkaian Gerbang NAND dan NOR. Pada konversi Rangkaian kombinasi tersebut dapat dilakukan dengan 2 (dua) cara, yaitu Melalui penyelesaian persamaan logika/boolean dan langsung dari gambar padanan. Gerbang

NAND dan NOR ini disebut juga Rangkaian Multilevel yang artinya dengan mengimplementasikan Gerbang NAND atau NOR, akan ada banyak level / tingkatan mulai dari sisi input sampai dengan sisi output. Pada penelitian ini fokus pembahasan pada proses konversi dari Rangkaian kombinasi AND, OR, NOT ke Rangkaian menggunakan Gerbang NAND dan NOR. Dengan ini penelitian akan membuat suatu Prototype Rangkaian kombinasi Gerbang AND, OR, NOT yang dikonversi dengan Rangkaian Gerbang NAND dan NOR sebagai model alat simulasinya.

CORRESPONDENCE

Phone: 085362553530E-mail: [email protected]

PENDAHULUAN

Rangkaian digital adalah matakuliah yang ada di setiap perguruan tinggi baik swasta maupun negeri. Pada rangkaian digital dipelajari tentang karakteristik Gerbang Logika. Dimana Gerbang Logika itu sendiri terdiri dari tujuh bagian, yaitu AND, OR, NOT, NAND, NOR, Ex-OR, dan Ex-NOR. Pada gerbang logika ada dua gerbang yang dikenal gerbang Multilevel yaitu gerbang NAND dan NOR. Gerbang Multilevel inilah yang dapat dijadikan sebagai gerbang untuk melakukan konversi Rangkaian kombinasi AND, OR, NOT menjadi Rangkaian Gerbang NAND dan NOR. Dimana pemakaian Gerbang NAND dan NOR dalam sebuah Rangkaian Digital adalah untuk dapat mengoptimalkan pemakaian seluruh gerbang yang terdapat dalam sebuah IC, sehingga menghemat biaya.

Konversi Rangkaian kombinasi gerbang AND, OR, NOT ke Rangkaian Gerbang NAND, dan NOR berdasarkan referensi-referensi yang didapat ada dua cara, yaitu Melalui penyelesaian persamaan logika/boolean dan langsung dari gambar padanan..

Penulis ingin membahas pada penelitian ini, yaitu pada

rangkaian kombinasi gerbang AND, OR, NOT dapat merubah rangkaian kombinasi tersebut menjadi Rangkaian NAND dan NOR saja. Dimana rangkaian kombinasi nanti akan diberikan input 3(tiga) input bit dan mengahasilkan output yang sama. Kemudian Rangkaian kombinasi tersebut akan dikomversikan menjadi Rangkaian Gerbang NAND dan NOR saja yang akan menghasilkan output yang sama.

Penulis ingin menyajikan pada penelitian ini dalam bentuk Prototype untuk menjadi alat yang dapat membantu memahami konversi rangkaian kombinasi tersebut ke dalam Rangkaian Gerbang NAND dan NOR saja. Kemudian yang ingin penulis ungkap pada penelitian ini adalah bahwa Rangkaian kombinasi tersebut dapat dirubah dengan cepat dengan hanya Rangkaian Gerbang NAND dan NOR saja.

Rumusan Masalah

Rumusan masalah dari penelitian ini adalah sebagai berikut : 1. Bagaimana Rangkaian kombinasi AND, OR, NOT

dikonversikan dengan menggunakan Gerbang NAND dan NOR ?

2. Bagaimana hasil output antara rangkaian kombinasi AND, OR, NOT setelah dikonversi dengan rangkaian NAND dan NOR ?

Batasan Masalah

Batasan masalah yang digunakan dalam penelitian ini adalah :

1. Penelitian ini hanya membahas konversi Rangkaian kombinasi AND, OR, NOT dengan menggunakan Rangkaian Gerbang NAND dan NOR saja.

2. Hasil konversi akan ditampilkan pada LCD

3. Konversi Rangkaian kombinasi dilakukan dengan menggunakan Prototype Rangkaian Gerbang NAND dan NOR.

Tujuan Penelitian

1. Membuat dan menerapkan model Prototype untuk alat praktek di dalam memahami proses konversi Rangkaian kombinasi Gerbang AND, OR, NOT.

2. Mengevaluasi rangkaian kombinasi dengan rangkaian yang menggunakan gerbang logika NAND dan NOR.

3. Membuat alat simulasi berupa Prototype di dalam mempraktekkan proses konversi Rangkaian kombinasi AND, OR, NOT dengan Rangkaian Gerbang NAND dan NOR.

Manfaat Penelitian

Adapun manfaat dari penelitian ini adalah :

1. Dapat memberikan hasil secara cepat, tepat, dan akurat dalam melakukan konversi Rangkaian kombinasi AND, OR, NOT dengan Rangakaian yang menggunakan Gerbang NAND dan NOR.

2. Dapat membantu mahasiswa dikalangan perguruan tinggi swasta maupun negeri dalam memahami proses konversi Rangkaian kombinasi Gerbang NAND dan NOR yang dilakukan.

METODE

Metode Penelitian yang digunakan adalah : 1. Metode Deskriptif

Pada metode ini data yang ada dikumpulkan, disusun, dikelompokkan, dianalisa sehingga diperoleh beberapa gambaran yang jelas pada masalah penelitian tersebut. 2. Metode Komperatif

Pada metode ini penganalisaan di lakukan dengan cara membandingkan teori dan praktek sehingga diperoleh gambaran yang jelas tentang persamaan dan perbedaan diantara keduanya.

Adapun kerangka kerja dari penelitian ini dapat dilihat pada gambar 1 berikut:

Gambar 1. Kerangka kerja penelitian Untuk tahapan perancangan ini ada beberapa tahapan yang penulis lakukan :

1. Penggambaran model rancangan dengan UML (Unified Modelling Language)

2. Penggambaran simulasi dinamis dari prototype yang dibuat

3. Mekanisme Implementasi dan Pengujian dari prototype yang dibuat.

HASIL DAN DISKUSI

Analisa sistem yang didapatkan dengan menggunakan metode deskriptif adalah perancangan rangkaian gerbang logika yang menggunakan power supply sebagai input (masukan) tegangan ke PCB rangkaian dengan IC 7400 dan 7402 sebagai rangkaian gerbang logika NAND dan NOR dengan terhubung pada saklar togle untuk logika input 0 (Low) dan 1 (high) dan output keluaran yang dihasilkan adalah dengan lampu LED hidup untuk logika 1 (High) dan lampu LED mati untuk logika 0 (Low).

1. Arsitektur Sistem Rangkaian Gerbang Logika

Gambar 2. Asitektur Sistem Rangkaian Gerbang Logika

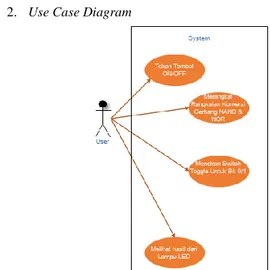

2. Use Case Diagram

Gambar 3. Use Case Diagram Sistem Digital Trainer

Keterangan : User menghidupkan Digital Trainer dengan menekan tombol ON/OFF, kemudian merangkai rangkaian

Kabel AC IC Gerbang Saklar Togle LED

konversi Gerbang NAND dan NOR. Setelah itu menekan Switch Toggle untuk memberikan Bit 0/1 dan melihat hasilnya apakah sudah sesuai dengan hasil dari rangkaian asal.

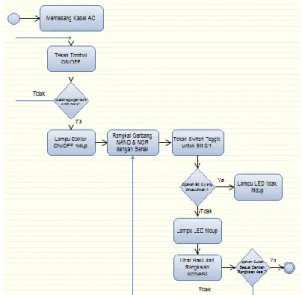

3. State Machine Diagram

State Machine Diagram merupakan gambaran perlakuan terhadap sistem Digital Trainer yang dibuat. Dimana User melakukan kegiatan untuk merangkai rangkaian konversi dengan Gerbang NAND dan NOR dari Rangkaian Asal yang di Uji Coba. Berikut ini gambar 4. State Machine Diagram aliran behavior pada sistem.

Gambar 4. State Machine Diagram Sistem Digital Trainer

4. Component Diagram

Component diagram merepresentasikan paket fisik dari Digital Trainer. Component diagram juga menunjukkan interface yang digunakan untuk komunikasi antar komponen. Berikut ini adalah gambar 5. component diagram dari sistem yang dibangun.

Gambar 5. Component Diagram Sistem Digital Trainer

5. Rangkaian Asal

Berikut ini adalah gambar dari Rangkaian Asal yang akan dikonversikan :

Gambar 6. Rangkaian Asal

Dari gambar 6. Apabila diinputkan dengan 3-input Bilangan Biner adalah sebagai berikut :

Tabel Kebenaran 3-Input

INPUT OUTPUT Y A B C 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1 6. Rangkaian Konversi

6.1 Rangkaian Konversi Dengan Gerbang NAND

Berikut ini adalah gambar rangkaian konversi dengan gerbang NAND :

Gambar 7. Rangkaian Konversi Dengan Gerbang NAND

6.2Rangkaian Konversi Dengan Gerbang NOR

Berikut ini adalah gambar rangkaian konversi dengan gerbang NOR :

Gambar 8. Rangkaian Konversi Dengan Gerbang NOR

Dari gambar rangkaian konversi diatas didapatkan dari penyederhanaan dengan menggunakan Tabel Padanan Gambar (Tocci R.J., 2007) berikut ini :

Maka tabel kebenaran dari Rangkaian Konversi diatas adalah sama hasil outputnya dengan tabel kebenaran Rangkaian Asal.

Tabel Kebenaran 3-Input INPUT OUTPUT Y A B C 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1

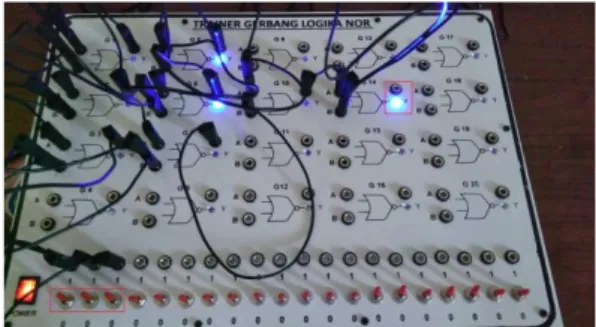

7. IMPLEMENTASI DAN PEMBAHASAN

5.1 Tahapan Implementasi

Berikut ini adalah implementasi Prototype Digital Trainer yang dibuat dan dilakukan pada Rangkaian Asal ketika dikonversikan menggunakan Rangkaian Gerbang NAND dan NOR :

1. Hasil Konversi Dari Rangkaian Gerbang NAND

Gambar 9. Prototype Digital Trainer Dengan Input 0,0,0.

Dari Gambar 9 diatas, terlihat prototype digital trainer dengan inputan 0,0,0 menghasilkan output Y = 0.

Gambar 10. Prototype Digital Trainer Dengan Input 0,0,1.

Dari Gambar 10 diatas, terlihat prototype digital trainer dengan inputan 0,0,1 menghasilkan output Y = 1.

Gambar 11. Prototype Digital Trainer Dengan Input 0,1,0.

Dari Gambar 11 diatas, terlihat prototype digital trainer dengan inputan 0,1,0 menghasilkan output Y = 0.

Gambar 12. Prototype Digital Trainer Dengan Input 0,1,1.

Dari Gambar 12 diatas, terlihat prototype digital trainer dengan inputan 0,1,1 menghasilkan output Y = 1.

Gambar 13. Prototype Digital Trainer Dengan Input 1,0,0.

Dari Gambar 13 diatas, terlihat prototype digital trainer dengan inputan 1,0,0 menghasilkan output Y = 0.

Gambar 14. Prototype Digital Trainer Dengan Input 1,0,1.

Dari Gambar 14 diatas, terlihat prototype digital trainer dengan inputan 1,0,1 menghasilkan output Y = 1.

Gambar 15. Prototype Digital Trainer Dengan Input 1,1,0.

Dari Gambar 15 diatas, terlihat prototype digital trainer dengan inputan 1,1,0 menghasilkan output Y = 1.

Gambar 16. Prototype Digital Trainer Dengan Input 1,1,1.

Dari Gambar 16 diatas, terlihat prototype digital trainer dengan inputan 1,1,1 menghasilkan output Y = 1.

2. Hasil Konversi Dari Rangkaian Gerbang NOR

Gambar 17. Prototype Digital Trainer Dengan Input 0,0,0.

Dari Gambar 17 diatas, terlihat prototype digital trainer dengan inputan 0,0,0 menghasilkan output Y = 0.

Gambar 18. Prototype Digital Trainer Dengan Input 0,0,1.

Dari Gambar 18 diatas, terlihat prototype digital trainer dengan inputan 0,0,1 menghasilkan output Y = 1.

Gambar 19. Prototype Digital Trainer Dengan Input 0,1,0.

Dari Gambar 19 diatas, terlihat prototype digital trainer dengan inputan 0,1,0 menghasilkan output Y = 0.

Gambar 20. Prototype Digital Trainer Dengan Input 0,1,1.

Dari Gambar 20 diatas, terlihat prototype digital trainer dengan inputan 0,1,1 menghasilkan output Y = 1.

Gambar 21. Prototype Digital Trainer Dengan Input 1,0,0.

Dari Gambar 21 diatas, terlihat prototype digital trainer dengan inputan 1,0,0 menghasilkan output Y = 0.

Gambar 22. Prototype Digital Trainer Dengan Input 1,0,1.

Dari Gambar 22 diatas, terlihat prototype digital trainer dengan inputan 1,0,1 menghasilkan output Y = 1.

Gambar 23. Prototype Digital Trainer Dengan Input 1,1,0.

Dari Gambar 23 diatas, terlihat prototype digital trainer dengan inputan 1,1,0 menghasilkan output Y = 1.

Gambar 24. Prototype Digital Trainer Dengan Input 1,1,1.

Dari Gambar 24 diatas, terlihat prototype digital trainer dengan inputan 1,1,1 menghasilkan output Y = 1.

KESIMPULAN

Prototype yang dihasilkan dari penelitian ini dapat dipergunakan sebagai alat simulasi pembelajaran sistem digital dalam memahami rangkaian multilevel NAND dan NOR.

Prototype yang dihasilkan dapat memberikan hasil output yang sama dari rangkaian asal yang dibentuk dari rangkaian Gerbang AND, OR, NOT dengan rangkaian konversi yang dibentuk dari Rangkaian Gerbang NAND dan NOR.

Prototype yang dibuat ini dapat memberikan pengetahuan kepada mahasiswa bahwa membuat rangkaian multilevel tersebut dapat dengan mudah diimplementasikan.

UCAPAN TERIMA KASIH

Penulis mengucapkan banyak terima kasih Kepada Direktur Riset dan Pengabdian Masyarakat (DRPM) Kementerian Riset, Teknologi dan Pendidikan Tinggi atas pembiayaan Penelitian Dosen Pemula (PDP) sebesar Rp. 19.647.000,- dengan SK. Nomor T/199/L1.3.1/PT.01.03/2019.

REFERENSI

[1]. Mathius Nugroho. 2015. Rangkaian Adder Dengan Seven Segment. Skripsi. Fakultas Teknologi Industri Universitas Internasional, Batam

[2]. Muhammad Irmansyah. 2009. Gerbang Logika Berbasis Programmable Logic Device (PLD). Elektron. Vol. 1, No. 1. 75-81.

[3]. Kurniawan, Fredly.2005. Jurnal Sistem Digital Konsep Dam Aplikasi Volume 3.Yogyakarta: Gava Media

[4]. Abdul Jabar. (2011). “Pemodelan dan Simulasi Dinamis Pendeteksi Dini Gempa Pada Gedung “. Universitas Putra Indonesia YPTK Padang : Tesis M.Kom.

[5]. Law, A. and Kelton W., 2000, “Simulation Modelling and Analysis”, 3rd, Mc Graw-Hill.

[6]. Tocci R.J., et al. (2007). “Digital Systems Principles And Aplications”, 10ed, Pearson Prentice Hall.

[7]. Martin Fowler. (2005). “UML Distilled.” 3th. Ed. A Brief

Guide to the Standard Object Modelling Language : Andi. 151-160.

BIOGRAPI PENULIS

Helmi Fauzi Siregar

Bekerja sebagai Dosen di Perguruan Tinggi Swasta Universitas Asahan dari Tahun 2016 sampai dengan sekarang. Telah memenangkan PDP Hibah DIKTI sebanyak dua kali dan banyak membuat artikel-artikel ilmiah yang dimuat di dalam jurnal Nasional.

Muhammad Dedi Irawan

Bekerja sebagai Dosen di Perguruan Tinggi Swasta Universitas Asahan dari Tahun 2016 sampai dengan sekarang. Telah memenangkan PDP Hibah DIKTI sebanyak 1 kali dan membuat artikel-artikel ilmiah yang dimuat di dalam jurnal Nasional dan International.