i

TUGAS AKHIR

PENGUJI KEBENARAN GERBANG LOGIKA NAND, NOR, DAN

NOT, SERTA ENKODER 8 KE 3, PENJUMLAH BINER 4-BIT, DAN

JK FLIP-FLOP UNTUK PAPAN UNTAI DIGITAL

TEKNIK ELEKTRO

Diajukan Untuk Memenuhi Salah Satu Syarat Memperoleh Gelar Sarjana Teknik

Program Studi Teknik Elektro

Oleh :

PETRA RYANDITHA EMMANUELA NIM : 055114022

PROGRAM STUDI TEKNIK ELEKTRO

FAKULTAS SAINS DAN TEKNOLOGI

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

ii

FINAL PROJECT

THE TRUTH DETECTOR OF NAND, NOR, AND NOT LOGIC

GATES, WITH ENCODER 8-3, 4-BIT BINARY FULL ADDER, AND

JK FLIP-FLOP FOR ELECTRICAL ENGINEERING DIGITAL

LOGIC TRAINER

Presented as Partial Fulfillment of the Requirements To Obtain the Sarjana Teknik Degree

In Electrical Engineering Study Program

PETRA RYANDITHA EMMANUELA NIM : 055114022

ELECTRICAL ENGINEERING STUDY PROGRAM

SCIENCE AND TECHNOLOGY FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

vi

HALAMAN PERSEMBAHAN DAN MOTTO HIDUP

MOTTO:

“

Only a live lived for others is a life worthwhile.

”

- Albert Enstein -

Skripsi ini kupersembahkan untuk…

Tuhan Yesus Kristus sumber kekuatan ku

Papa, Mama, Adik, dan Keluarga Besar ku yang terkasih

viii

INTISARI

Papan untai digital merupakan salah satu alat penting dan sering digunakan saat praktikum. Namun, karena berbagai faktor papan untai digital dapat rusak. Pengecekan kerusakan papan untai digital secara manual membutuhkan waktu yang cukup lama, sehingga dapat mengganggu jalannya praktikum. Alat penguji yang dapat menguji apakah papan untai dalam keadaan baik atau tidak sangat dibutuhkan.

Alat penguji ini akan dihubungkan dengan masukan dan keluaran gerbang logika atau rangkaian logika pada papan untai digital dengan menggunakan kabel. Masukan dan keluaran papan untai digital dihubungkan sesuai keterangan pada alat tersebut. Gerbang logika atau rangkaian logika yang akan diuji dipilih menggunakan push button. Pilihan gerbang logika dan rangkaian logika, proses pengujian, dan hasil akhir pengujian ditampilkan pada LCD.

ix

ABSTRACT

Digital logic trainer is one of important device and often used during practical work. However, digital logic trainer can be broken due to various factors. Checking digital logic trainer damage manually can take quiet long time, so it will disrupt practical work. Tester that could test whether the digital logic trainer in a good or bad condition are urgently needed.

This tester will be connected with inputs and outputs of the logic gates or logic circuits on the digital logic trainer using jumper cables. The digital logic trainer inputs and outputs will be connected correspond to description at this device. Logic gates or logic circuits to be tested is selected using the push button. Option of logic gates and logic circuits, the testing process, and the end of the test results displayed on the LCD.

x

KATA PENGANTAR

Syukur dan terima kasih kepada Tuhan atas segala rahmat dan berkat-Nya sehingga tugas akhir dengan judul “PENGUJI KEBENARAN GERBANG LOGIKA NAND, NOR, DAN NOT, SERTA ENKODER 8 KE 3, PENJUMLAH BINER 4-BIT, DAN JK FLIP-FLOP UNTUK PAPAN UNTAI DIGITAL TEKNIK ELEKTRO” ini dapat diselesaikan dengan baik.

Selama menulis tugas akhir ini, penulis menyadari bahwa ada begitu banyak pihak yang telah memberikan bantuan dengan caranya masing-masing, sehingga tugas akhir ini bisa diselesaikan. Oleh karena itu penulis ingin mengucapkan terima kasih kepada:

1. Orangtua tercinta atas doa, kesabaran dan dukungannya. 2. Bapak Martanto,S.T.,M.T. selaku dosen pembimbing.

3. Teman – teman yang telah banyak membantu penulis untuk menyelesaikan tugas akhir ini. Rangga yang terus mengingatkan dan bersedia membantu saat dibutuhkan, Terry yang mau menjadi teman senasib seperjuangan; Esti, Anggi dan Tari yang selalu memberi semangat; Chris yang mau meminjamkan peralatan dan pikiran; Tina yang bersedia meminjamkan kamera; juga semua teman-teman teknik elektro yang ikut memberi semangat dan membantu penulis menyelesaikan tugas akhir ini. 4. Seluruh dosen dan laboran program studi teknik elektro yang telah membagi ilmu

dan pengetahuan kepada penulis selama kuliah.

Dengan rendah hati penulis menyadari bahwa tugas akhir ini masih jauh dari sempurna, oleh karena itu berbagai kritik dan saran untuk perbaikan tugas akhir ini sangat diharapkan. Akhir kata, semoga tugas akhir ini dapat bermanfaat bagi semua pihak. Terima kasih.

Yogyakarta, 2 Juli 2012

xii

DAFTAR ISI

HALAMAN JUDUL DALAM BAHASA INDONESIA ………...

HALAMAN JUDUL DALAM BAHASA INGGRIS ……….... HALAMAN PERSETUJUAN ……….... HALAMAN PENGESAHAN ………... PERNYATAAN KEASLIAN KARYA ………... HALAMAN PERSEMBAHAN DAN MOTTO HIDUP ………... LEMBAR PERNYATAAN PERSETUJUAN PUBLIKASI KARYA

xiii

2.5 Flip-Flop ………...………….………..…..

2.5.1 JK Flip-Flop ………..…….

2.6 Mikrokontroler AVR ………..…... 2.6.1 Arsitektur dan Konfigurasi Pin ATmega8535 ………..….

2.6.2 Peta Memori ………...………..….

2.7 LCD M1632 ………..….

2.7.1 DDRAM (Display Data RAM), CGROM (Character Generator ROM), dan CGRAM (Character Generator RAM ... 2.7.2 Register Perintah ……….……….. 2.7.3 Register Data ………...………..….... BAB III RANCANGAN PENELITIAN ....………..…….. 3.1 Perancangan Perangkat Keras …...………..……..

3.1.1 Mikrokontroler ATmega8535 ……….……..

3.1.2 Push Button ……….……..

3.1.3 Konektor ke Papan Untai Digital dan Konektor dari Papan Untai

Digital ………...…………..…...

3.1.4 Penampil LCD ………...…..…..

3.2 Perancangan Perangkat Lunak ……….…. 3.2.1. Pilih Menu ……….…………..…... 3.2.2. Pengujian Gerbang Logika dan Rangkaian Logika ………..…. 3.2.3. Menampilkan Hasil Akhir Pengujian ………....…... BAB IV HASIL DAN PEMBAHASAN ………... 4.1 Perangkat Keras Alat Penguji Kebenaran ………. 4.2 Perangkat Lunak Alat Penguji Kebenaran ………....

4.2.1 Program Utama ………..

4.2.2 Pilih Menu ……….

4.2.3 Pengujian Gerbang Logika dan Rangkaian Logika ………... 4.2.4 Hasil Akhir Pengujian ………... 4.3 Pembahasan Hasil Percobaan Pada Alat Penguji Kebenaran ………... 4.3.1 Percobaan Pengujian Gerbang NAND ………. 4.3.2 Percobaan Pengujian Gerbang NOR ………. 4.3.3 Percobaan Pengujian Gerbang NOT ……… 4.3.4 Percobaan Pengujian Enkoder 3 Ke 8 ………..

xiv

4.3.5 Percobaan Pengujian Penjumlah Biner 4-bit ……… 4.3.6 Percobaan Pengujian JK flip-flop ………. BAB V KESIMPULAN DAN SARAN ……….

5.1 Kesimpulan ………...

5.2 Saran ……….

DAFTAR PUSTAKA ……….……... LAMPIRAN……….……...

xv

DAFTAR GAMBAR

Gambar 2.1 Simbol Logika Gerbang NOT ……….. Gambar 2.2 Simbol Logika Gerbang NAND ………... Gambar 2.3 Simbol Logika Gerbang NOR ……….. Gambar 2.4 Konfigurasi Pin IC 74148 [1] ………... Gambar 2.5 Penjumlahan Biner 1-bit [4] ………. Gambar 2.6 Penjumlahan Biner 2-bit [2] ………. Gambar 2.7 Rangkaian Logika Half Adder [2] ………

Gambar 2.8 Rangkaian Logika Full Adder [4] ……….

Gambar 2.9 Diagram Blok (a) Half Adder (b) Full Adder [2] ……….

Gambar 2.10 Simbol Logika IC 7483 [8] ………... Gambar 2.11 (a) Clock Aktif Tinggi (b) Clock Aktif Rendah (c) Clock Pinggiran

Positif (d) Clock Pinggiran Negatif [1] ………

Gambar 2.12 Simbol JK Flip-Flop [1] ………... Gambar 2.13 Simbol JK Flip-Flop [1] ………... Gambar 2.14 Konfigurasi Pin ATmega8535 [6] ……… Gambar 2.15 (a) Peta Memori Data (b) Peta Memori Program [5] ………... Gambar 2.16 Konfigurasi Pin HD44780 ……… Gambar 2.17 Alamat DDRAM pada LCD 16x2 [7] ……….. Gambar 3.1 Diagram Blok Sistem Keseluruhan ……….. Gambar 3.2 Layout Port I/O Papan Untai Digital ………

Gambar 3.3 Blok Rangkaian Mikrokontroler ATmega8535 ……… Gambar 3.4 Blok Rangkaian Push Button ………

Gambar 3.5 Blok Rangkaian Konektor (a) ke Papan Untai Digital

(b) dari Papan Untai Digital ………..

Gambar 3.7 Blok Rangkaian Penampil LCD ………... Gambar 3.8 Diagram Alir Program Utama Enkoder 8 ke 3 ………..……... Gambar 3.9 Diagram Alir Sub Rutin Pilih Menu Penjumlah Biner ………. Gambar 3.10 Diagram Alir Sub Rutin Pengujian Gerbang Logika dan Rangkaian

Logika ………...

xvi

Gambar 4.1 Rangkaian Keseluruhan Alat Penguji Kebenaran ………. Gambar 4.2 Skema Port Mikrokontroler untuk Konektor Masukan dan

Konektor Keluaran ………

Gambar 4.3 Layout Penguji Kebenaran Papan Untai Digital ………...

Gambar 4.4 Tampilan Awal Pilih Menu ………...

Gambar 4.5 Tampilan Pilih Menu ………

Gambar 4.6 Tampilan LCD setelah Pemilihan ………. Gambar 4.7 Tabel Pengujian Gerbang NAND untuk Look-Up Table Pada

Program ……….

Gambar 4.8 Tampilan LCD pada Proses Pengujian (a) Gerbang NAND, (b) Gerbang NOR, (c) Gerbang NOT, (d) Enkoder 8 ke 3,

(e) Penjumlah Biner 4-bit, (f) JK flip-flop ……… Gambar 4.9 Tampilan Hasil Akhir Pengujian (a) yang Berhasil, (b) yang Gagal Gambar 4.10 Timing Diagram dari Hasil Percobaan Pengujian JK Flip-Flop

yang dalam Keadaan Baik ……….

Gambar 4.11 Timing Diagram dari Hasil Percobaan Pengujian JK Flip-Flop pada Penjumlah Biner 4-bit ………...

35

36 37 40 40 41

46

46 47

79

xvii

DAFTAR TABEL

Halaman Tabel 2.1. Nilai Bit Bilangan Biner ... Tabel 2.2. Tabel Kebenaran Gerbang NOT [2] ... Tabel 2.3. Tabel Kebenaran Gerbang NAND [2] ... Tabel 2.4. Tabel Kebenaran Gerbang NOR [2] ... Tabel 2.5. Tabel Fungsi IC 74148 [1] ... Tabel 2.6. Tabel Penjumlahan LSB [2] ... Tabel 2.7. Tabel Penjumlahan MSB [2] ... Tabel 2.8. Tabel Kebenaran IC 7483 [8] ... Tabel 2.9. Tabel Kebenaran JK Flip-Flop [4] ... Tabel 2.10. Tabel Kebenaran IC 7476 [4] ... Tabel 3.1. Tabel Jumlah Masukan dan Keluaran Gerbang Logika dan Rangkaian

Logika ... Tabel 3.2. Tabel Pengujian Gerbang NAND ... Tabel 3.3. Tabel Pengujian Gerbang NOR ... Tabel 3.4. Tabel Pengujian Gerbang NOT ... Tabel 3.5. Tabel Pengujian Enkoder 8 ke 3 ... Tabel 3.6. Tabel Pengujian Penjumlah Biner 4-bit ... Tabel 3.7. Tabel Pengujian JK flip-flop ... Tabel 4.1. Tabel Pengujian Gerbang NAND ... Tabel 4.2. Tabel Perbandingan Keluaran Gerbang NAND yang Baik pada Papan Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.3. Tabel Hasil Pengujian Gerbang NAND yang Baik ... Tabel 4.4. Tabel Data Pengujian Gerbang NAND pada Gerbang NOR ... Tabel 4.5. Tabel Pengujian Gerbang NOR ... Tabel 4.6. Tabel Perbandingan Keluaran Gerbang NOR yang Baik pada Papan

Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.7. Tabel Hasil Pengujian Gerbang NOR yang Baik ... Tabel 4.8. Tabel Data Pengujian Gerbang NOR pada Gerbang NAND ... Tabel 4.9. Tabel Pengujian Gerbang NOT ...

xviii

Tabel 4.10. Tabel Perbandingan Keluaran Gerbang NOT yang Baik pada Papan Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.11. Tabel Hasil Pengujian Gerbang NOT yang Baik ... Tabel 4.12. Tabel Data Pengujian Gerbang NOT pada Gerbang NAND ... Tabel 4.13. Tabel Pengujian Enkoder 8 ke 3 ... Tabel 4.14. Tabel Perbandingan Keluaran Enkoder 8 ke 3 yang Baik pada Papan

Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.15. Tabel Hasil Pengujian Enkoder 8 ke 3 yang Baik ... Tabel 4.16. Tabel Data Pengujian Enkoder 8 ke 3 pada Penjumlah Biner 4-bit ... Tabel 4.17. Tabel Pengujian Penjumlah Biner 4-bit ... Tabel 4.18. Tabel Perbandingan Keluaran Penjumlah Biner 4-bit yang Baik pada

Papan Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.19. Tabel Hasil Pengujian Penjumlah Biner 4-bit yang Baik ... Tabel 4.20. Tabel Perbandingan Keluaran Penjumlah Biner 4-bit yang Rusak

pada Papan Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.21. Tabel Data Pengujian Penjumlah Biner 4-bit yang dalam Keadaan

Rusak ... Tabel 4.22. Tabel Pengujian JK Flip-Flop ... Tabel 4.23. Tabel Perbandingan Keluaran JK Flip-Flop yang Baik pada Papan

Untai dengan Keluaran Tabel Kebenaran ... Tabel 4.24. Tabel Hasil Pengujian JK Flip-Flop yang Baik ... Tabel 4.25. Tabel Data Pengujian JK Flip-Flop pada Penjumlah Biner 4-bit ...

1

BAB I

PENDAHULUAN

1.1

Latar Belakang

Kurikulum program pendidikan Strata-1 (S-1) di Program Studi Teknik Elektro Fakultas Sains dan Teknologi Universitas Sanata Dharma menitikberatkan pada konsentrasi teknik elektronika dengan peminatan kendali dan telekomunikasi. Selain teknik elektronika, dalam kurikulum ini juga diberikan materi matematika dasar serta materi lanjutan dan aplikasinya. Materi matematika dasar diberikan pada mata kuliah bidang kalkulus, sedangkan materi lanjutan dan aplikasinya diberikan pada mata kuliah lain, seperti sistem linear, mata kuliah bidang elektronika analog dan digital, mata kuliah kendali dasar, serta mata kuliah peminatan.

Mata kuliah bidang elektronika digital yang diberikan pada tahun pertama perkuliahan adalah teknik digital dan praktikum teknik digital. Materi pada mata kuliah teknik digital antara lain konsep digital, bilangan dan sandi, gerbang logika dasar, register, flip-flop, dan teknologi IC. Materi yang diberikan tersebut akan dipraktekkan di praktikum teknik digital. Praktikum dilakukan menggunakan sebuah alat yang disebut papan untai digital (Digital Logic Trainer).

Papan untai digital merupakan piranti elektronika yang memiliki berbagai fungsi logika digital, antara lain gerbang logika dasar, konverter, flip-flop, dan penjumlah biner. Papan untai digital juga dilengkapi dengan pin masukan dan pin keluaran, indikator LED, penampil 7-segment, dan tombol masukan. Setiap fungsi logika digital pada alat ini diimplementasikan menggunakan IC. Alat ini dioperasikan dengan cara menghubungkan pin masukan dan pin keluaran dengan pin masukan dan pin keluaran dari rangkaian yang dibutuhkan, menggunakan kabel penghubung.

Penelitian ini dilakukan berdasarkan kebutuhan akan sebuah alat pendeteksi yang dapat mendeteksi kondisi setiap gerbang logika dan rangkaian logika pada papan untai digital dengan tepat dan lebih cepat dibanding pengecekan secara manual. Alat pendeteksi ini dikendalikan oleh sebuah mikrokontroler. Gerbang logika atau rangkaian logika yang ingin dideteksi kondisinya dipilih dengan push button. Kemudian mikrokontroler akan melakukan pengujian terhadap gerbang logika atau rangkaian logika tersebut. Papan untai digital akan mendapat masukan dari mikrokontroler, dan keluaran dari papan untai digital menjadi masukan mikrokontroler. Keluaran dari papan untai digital ini kemudian dibandingkan dengan tabel pengujian yang sudah tersimpan dalam memori mikrokontroler. Hasil akhir dari perbandingan inilah yang nantinya akan menentukan kondisi dari gerbang logika atau rangkaian logika.

1.2

Tujuan dan Manfaat

Tujuan yang ingin dicapai melalui penelitian ini adalah menghasilkan sebuah alat yang ringkas dan mudah dipakai, untuk mendeteksi kondisi gerbang logika dan rangkaian logika yang terdapat pada papan untai digital dengan cepat dan tepat.

Penelitian ini diharapkan dapat bermanfaat sebagai alat bantu dalam mendeteksi kerusakan papan untai digital.

1.3

Batasan Masalah

Penelitian akan dibatasi pada pembuatan alat untuk menguji kebenaran gerbang logika NOT, NAND, dan NOR, serta enkoder 8 ke 3, penjumlah biner 4-bit, dan JK flip-flop pada papan untai digital di laboratorium Teknik Elektro Universitas Sanata Dharma, dengan menggunakan mikrokontroler ATmega8535. Spesifikasi alat yang akan dibuat adalah:

a. Menggunakan mikrokontroler ATmega8535.

b. Penampil LCD 2x16 sebagai penampil masukan ke papan untai digital, penampil keluaran dari papan untai digital, dan penampil hasil akhir pengujian.

1.4

Metodologi Penelitian

Metode yang akan diterapkan pada penelitian ini adalah sebagai berikut:

a. Studi pustaka. Pada tahap ini akan dilakukan pengumpulan dan pembelajaran bahan referensi berupa buku, jurnal, maupun internet yang mendukung penelitian.

b. Perancangan perangkat keras dan perancangan perangkat lunak. Perancangan dilakukan berdasarkan informasi yang didapat dari studi pustaka, dan dengan mempertimbangkan faktor permasalahan dan kebutuhan, sehingga menghasilkan model sistem yang optimal. Perancangan ini meliputi perancangan rangkaian dan pembuatan diagram alir perangkat lunak.

c. Persiapan alat dan bahan penelitian. Tahap ini bertujuan untuk mempersiapkan semua alat dan bahan yang dibutuhkan sesuai dengan perancangan.

d. Pembuatan perangkat keras dan pembuatan perangkat lunak. Proses pembuatan perangkat keras dan perangkat lunak berdasarkan perancangan, serta pengujian sistem keseluruhan.

e. Pengambilan data.

4

BAB II

DASAR TEORI

2.1

Sistem Bilangan Biner

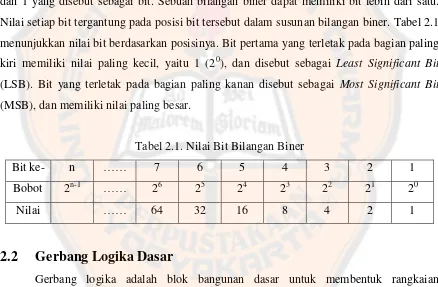

Elektronika digital dikembangkan dari prinsip bahwa transistor dapat dengan mudah dibuat dan dirancang untuk menghasilkan satu dari dua level tegangan pada keluarannya, berdasar level tegangan masukan [2]. Dua level tersebut (biasanya +5 volt dan 0 volt) adalah TINGGI dan RENDAH, juga dapat diwakili oleh 1 dan 0 [2]. Angka 1 dan 0 yang digunakan untuk mewakili dua level tegangan ini disebut sistem bilangan biner. Bilangan biner adalah sistem bilangan berbasis 2, memilliki 2 digit angka yaitu 0 dan 1 yang disebut sebagai bit. Sebuah bilangan biner dapat memiliki bit lebih dari satu. Nilai setiap bit tergantung pada posisi bit tersebut dalam susunan bilangan biner. Tabel 2.1 menunjukkan nilai bit berdasarkan posisinya. Bit pertama yang terletak pada bagian paling kiri memiliki nilai paling kecil, yaitu 1 (20), dan disebut sebagai Least Significant Bit

(LSB). Bit yang terletak pada bagian paling kanan disebut sebagai Most Significant Bit

(MSB), dan memiliki nilai paling besar.

Tabel 2.1. Nilai Bit Bilangan Biner

Bit ke- n …… 7 6 5 4 3 2 1

Bobot 2n-1 …… 26 25 24 23 22 21 20

Nilai …… 64 32 16 8 4 2 1

2.2

Gerbang Logika Dasar

Gerbang logika adalah blok bangunan dasar untuk membentuk rangkaian elektronika digital, yang digambarkan dengan simbol-simbol tertentu yang telah ditetapkan [1]. Gerbang logika memiliki satu atau lebih masukan, dan satu keluaran. Gerbang logika memiliki 2 keadaan keluaran, yaitu TINGGI (1) atau RENDAH (0), tergantung pada masukan yang diberikan.

Gerbang exclusive-OR (X-OR) dan exclusive-NOR (X-NOR) adalah gerbang logika hasil kombinasi dari gerbang AND, OR, dan NOT.

2.2.1

Gerbang NOT

Gerbang NOT yang sering disebut inverter (pembalik) memiliki satu masukan dan satu keluaran. Gerbang ini berfungsi untuk membalikkan sinyal digital. Jika masukan yang diberikan RENDAH (0), maka keluaran yang dihasilkan adalah TINGGI (1). Sebaliknya, jika masukannya TINGGI (1), maka keluarannya adalah RENDAH (0).

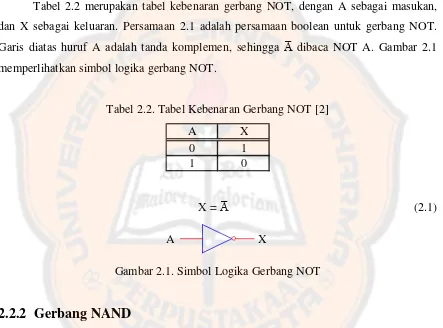

Tabel 2.2 merupakan tabel kebenaran gerbang NOT, dengan A sebagai masukan, dan X sebagai keluaran. Persamaan 2.1 adalah persamaan boolean untuk gerbang NOT. Garis diatas huruf A adalah tanda komplemen, sehingga dibaca NOT A. Gambar 2.1 memperlihatkan simbol logika gerbang NOT.

Tabel 2.2. Tabel Kebenaran Gerbang NOT [2]

A X

0 1

1 0

X = (2.1)

Gambar 2.1. Simbol Logika Gerbang NOT

2.2.2

Gerbang NAND

Gerbang NAND adalah gabungan gerbang AND dan NOT. Gerbang ini memiliki dua atau lebih masukan, dan satu keluaran. Keluaran gerbang NAND akan RENDAH (0) jika semua masukan yang diberikan TINGGI (1). Jika salah satu atau semua masukan gerbang NAND RENDAH (0), maka keluaran yang dihasilkan akan TINGGI (1).

Tabel kebenaran untuk gerbang NAND dengan dua masukan ditunjukkan tabel 2.3, dengan A dan B sebagai masukan, dan X sebagai keluaran. Persamaan 2.2 adalah persamaan boolean untuk gerbang NAND. Tanda dot (∙) pada ∙ di persamaan 2.2 menandakan fungsi AND, sehingga A∙B dibaca A AND B, dan ∙ dibaca NOT (A AND B). Gambar 2.2 memperlihatkan simbol logika gerbang NAND.

Tabel 2.3. Tabel Kebenaran Gerbang NAND [2]

A B X

0 0 1

0 1 1

1 0 1

1 1 0

X = ∙ (2.2)

Gambar 2.2. Simbol Logika Gerbang NAND

2.2.3

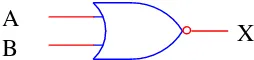

Gerbang NOR

Gerbang NOR adalah gabungan dari gerbang OR dan NOT. Gerbang NOR, sama seperti gerbang NAND, memiliki dua atau lebih masukan dan satu keluaran. Keluaran gerbang NOR merupakan komplemen dari keluaran gerbang OR. Jika salah satu dari masukan yang diberi TINGGI (1), maka keluaran gerbang NOR adalah RENDAH (0). Keluaran gerbang ini akan TINGGI (1) jika semua masukan yang diberikan RENDAH (0).

Tabel 2.4 merupakan tabel kebenaran gerbang NOR untuk dua masukan, dengan A dan B sebagai masukan, dan X sebagai keluaran. Persamaan 2.3 adalah persamaan boolean untuk gerbang NOR. Tanda plus (+) pada di persamaan 2.3 menandakan fungsi OR, sehingga A+B dibaca A OR B, dan dibaca NOT (A OR B). Gambar 2.3 memperlihatkan simbol logika gerbang NOR.

Tabel 2.4. Tabel Kebenaran Gerbang NOR [2]

A B X

0 0 1

0 1 0

1 0 0

1 1 0

X = (2.3)

A

Gambar 2.3. Simbol Logika Gerbang NOR

2.3

Konverter

Informasi atau data, yang digunakan oleh peralatan digital berasal dari banyak format [2]. Berbagai kode-kode khusus digunakan untuk mewakili angka, huruf, tanda baca, dan kontrol karakter [4]. Perangkat konversi khusus, yang disebut enkoder dan dekoder, berfungsi untuk mengubah sistem bilangan tertentu menjadi sistem bilangan lain [1].

Enkoder adalah perangkat konversi yang akan mengubah bilangan numerik pada masukan, menjadi bilangan tersandi pada bagian keluaran. Dekoder adalah perangkat konversi yang akan mengubah bilangan tersandi pada masukan, menjadi bilangan numerik sebagai keluaran. Enkoder dan dekoder memiliki masukan dan keluaran lebih dari satu, sesuai jumlah digit pada sistem bilangan yang akan diubah dan yang ingin dihasilkan. Enkoder hanya akan mengaktifkan satu jalur masukan pada waktu tertentu, sedangkan dekoder hanya akan mengaktifkan satu jalur keluaran pada waktu tertentu.

2.3.1

Enkoder 8 ke 3

Enkoder oktal ke biner, yang juga dikenal dengan sebutan enkoder 8 ke 3, adalah alat yang mengubah bilangan oktal ke biner. Enkoder ini memiliki 8 masukan, yang mewakili bilangan oktal, dan 3 keluaran yang mewakili 3-bit bilangan biner.

IC TTL untuk enkoder 8 ke 3 adalah 74148. Gambar 2.4 memperlihatkan konfigurasi pin IC 74148. Semua masukan dan keluaran IC 74148 adalah aktif RENDAH (0). Selain itu IC 74148 ini juga merupakan enkoder prioritas [2]. Jadi saat dua atau lebih masukan aktif pada saat yang bersamaan, hanya masukan dengan prioritas yang lebih tinggi yang akan diubah ke keluaran, dengan sebagai masukan dengan prioritas paling tinggi.

Pada pin masukan IC 74148 terdapat pin tambahan yang disebut masukan enable

( ). IC hanya dapat bekerja hanya jika pin ini dalam keadaan aktif (RENDAH). Jika pin dalam keadaan TINGGI (1), maka semua keluaran akan dalam keadaan tidak aktif (TINGGI). Tabel 2.5 adalah tabel fungsi dari IC enkoder 74148.

A

Gambar 2.4. Konfigurasi Pin IC 74148 [1]

Tabel 2.5. Tabel Fungsi IC 74148 [1]

Masukan Keluaran

H X X X X X X X X H H H H H

L H H H H H H H H H H H H L

L X X X X X X X L L L L L H

L X X X X X X L H L L H L H

L X X X X X L H H L H L L H

L X X X X L H H H L H H L H

L X X X L H H H H H L L L H

L X X L H H H H H H L H L H

L X L H H H H H H H H L L H

L L H H H H H H H H H H L H

2.4

Aritmatika Digital

Fungsi penting dari sistem digital dan komputer adalah penyelesaian operasi aritmatika [2]. Semua penyelesaian operasi aritmatika dilakukan secara binary

2.4.1

Penjumlahan Biner

Penjumlahan dalam bilangan biner pada dasarnya sama dengan penjumlahan bilangan desimal, hanya saja bilangan biner memiliki 2 digit angka, yaitu 0 dan 1. Hasil penjumlahan 0+0 dalam bilangan biner adalah 0, dan hasil penjumlahan 0+1 adalah 1. Hasil dari 1+1 Pada penjumlahan bilangan desimal adalah 2, yang dalam bilangan biner ditulis 10, sehingga hasil penjumlahan 1+1 dalam bilangan biner adalah 0 dengan carry 1. Gambar 2.5 menunjukkan penjumlahan biner 1-bit.

Gambar 2.5. Penjumlahan Biner 1-bit [4]

Penjumlahan biner lebih dari 1-bit memiliki cara kerja yang sama seperti penjumlahan biner 1-bit. Gambar 2.6 menunjukkan contoh penjumlahan biner 2-bit. A dan B adalah 2 bilangan biner yang ingin dijumlahkan. Cout adalah carry hasil penjumlahan,

dan menjadi Cin yang akan ikut dijumlahkan pada penjumlahan bit selanjutnya. ∑ adalah

hasil penjumlahan setiap bit.

Gambar 2.6. Penjumlahan Biner 2-bit [2]

Tabel 2.6. Tabel Penjumlahan LSB [2]

Masukan Keluaran

A0 B0 ∑0 Cout

0 0 0 0

0 1 1 0

1 0 1 0

1 1 1 1

Tabel 2.7. Tabel Penjumlahan MSB [2]

Masukan Keluaran

A1 B1 Cin ∑1 Cout

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Jika tabel penjumlahan LSB dan MSB digunakan sebagai tabel kebenaran, maka akan didapat rangkaian yang mewakili logika penjumlahan biner. Gambar 2.7 menunjukkan rangkaian logika penjumlahan LSB, yang disebut dengan rangkaian half

adder. Gambar 2.8 menunjukkan rangkaian logika penjumlahan MSB, yang disebut

dengan rangkaian full adder. Gambar 2.9 adalah diagram blok untuk rangkaian half adder

dan full adder. Pada penjumlahan biner lebih dari 2-bit, logika penjumlahan MSB juga digunakan untuk menjumlahkan bit kedua hingga MSB.

Gambar 2.7. Rangkaian Logika Half Adder [2]

A0

B0 ∑0 =

Gambar 2.8. Rangkaian Logika Full Adder [4]

Gambar 2.9. Diagram Blok (a) Half Adder (b) Full Adder [2]

2.4.2

Penjumlah Biner 4-bit

Pabrik IC memproduksi beberapa IC penjumlah. Salah satu IC aritmatika dasar yang diproduksi adalah IC TTL 7483, penjumlah biner 4-bit [4]. Simbol logika IC 7483 ditunjukkan gambar 2.10. Ground (GND) berada di pin 12, dan Vcc di pin 5.

Gambar 2.10. Simbol Logika IC 7483 [8]

IC TTL 7483 menjumlahkan dua buah bilangan biner 4-bit (A dan B) beserta masukan carry [8]. Penjumlahan bilangan biner ditampilkan pada keluaran penjumlahan

(S0 - S3) dan keluaran carry (C4) [8]. Persamaan untuk penjumlah biner 4-bit ini disajikan

pada persamaan 2.4 [8]. Tabel kebenaran IC TTL 7483 ditunjukkan oleh tabel 2.8.

C0 + (A0+B0) + 2(A1+B1) + 4(A2+B2) + 8(A3+B3) = S0 + 2S1 + 4S2 + 8S3 + 16S4 (2.4)

Tabel 2.8. Tabel Kebenaran IC 7483 [8]

Masukan Keluaran

C0 A0 A1 A2 A3 B0 B1 B2 B3 S0 S1 S2 S3 S4

Level Logika L L H L H H L L H H H L L H Aktif HIGH 0 0 1 0 1 1 0 0 1 1 1 0 0 1 Aktif LOW 1 1 0 1 0 0 1 1 0 0 0 1 1 0

2.5

Flip-Flop

Rangkaian logika kombinasioal dapat mengimplementasikan fungsi operasi aritmatika pada komputer. Namun, selain fungsi operasi aritmatika terdapat juga fungsi lain pada komputer yang membutuhkan memori, sehingga dibutuhkan rangkaian logika yang menggunakan memori.

Rangkaian logika diklasifikasikan menjadi 2 kelompok, yaitu rangkaian logika kombinasional dan rangkaian logika sequensial. Rangkaian logika sequensial adalah rangkaian logika digital yang dikontrol dan digunakan untuk mengontrol rangkaian lain pada keadaan tertentu berdasar pewaktu atau sinyal kontrol enable/disable [2]. Keluaran rangkaian logika sequensial tidak hanya tergantung pada masukan saat itu, tetapi juga tergantung pada keadaan keluaran sebelumnya. Blok rangkaian dasar untuk rangkaian logika sequensial adalah flip-flop (FF) [4].

Flip-flop merupakan perangkat bistable sinkron, karena keluaranflip-flop memiliki 2 keadaan stabil, yaitu TINGGI (1) dan RENDAH (0), yang berubah pada saat tertentu tergantung pada sebuah masukan pemicu yang disebut clock (CLK). Clock dibagi menjadi 4 jenis, yaitu:

1. Aktif tinggi. Clock aktif saat masukan clock dalam keadaan TINGGI (1). 2. Aktif rendah. Clock aktif saat masukan clock dalam keadaan RENDAH (0).

3. Pinggiran positif. Clock aktif saat masukan clock berubah dari keadaan RENDAH (0) ke keadaan TINGGI (1).

(1) ke keadaan RENDAH (0).

Gambar 2.11 menunjukkan simbol logika flip-flop untuk setiap jenis clock.

Gambar 2.11. (a) Clock Aktif Tinggi (b) Clock Aktif Rendah (c) Clock Pinggiran Positif (d) Clock Pinggiran Negatif [1]

Terdapat 4 jenis flip-flop, yaitu Set-Reset Flip-Flop (S-R FF), Data Flip-Flop (D FF), Toggle Flip-Flop (T FF), J-K Flip-Flop.

2.5.1

JK Flip-Flop

JK flip-flop adalah flip-flop yang paling serba guna, karena dapat bergungsi sebagai S-R flip-flop, D flip-flop, dan T flip-flop [1]. JK flip-flop memiliki 2 masukan data (J dan K), sebuah masukan clock (CLK), sebuah keluaran (Q) dan komplemen keluaran ( ). Simbol logika JK flip-flop, dengan clock aktif tinggi, ditunjukkan gambar 2.12.

Gambar 2.12. Simbol JK Flip-Flop [1]

Saat masukan J dan K yang diberikan adalah RENDAH (0), flip-flop akan dalam

masukan saat clock dalam keadaan aktif. Tabel kebenaran JK flip-flop dapat dilihat pada tabel

Tabel 2.9. Tabel Kebenaran JK Flip-Flop [4]

Toggle 1 1 Toggle Kebalikan dari keadaan sebelumnya

IC TTL untuk JK flop adalah 7476. Gambar 2.13 menunjukkan simbol JK flip-flop pada IC 7476. Jenis clock JK flip-flop pada gambar 2.13 adalah clock pinggiran negatif.

Gambar 2.13 Simbol JK Flip-Flop [1]

Selain masukan data dan masukan clock, gambar 2.13 juga menunjukkan 2 masukan tambahan, yaitu preset (PR) dan clear (CLR). Tidak seperti masukandata (J dan K) dan masukan clock (CLK), preset dan clear merupakan masukan asynchronous. Saat

preset atau clear aktif, maka keluaran Q akan berubah walaupun clock tidak dalam keadaan aktif, dan tanpa mengikuti masukan J dan K. Keluaran Q akan berubah menjadi TINGGI (1) saat preset aktif, dan berubah menjadi RENDAH (0) saat clear aktif. Berdasar gambar 2.13 preset dan clear merupakan aktif rendah. Tabel kebenaran untuk IC 7476 JK flip-flop dapat dilihat pada tabel 2.10.

Tabel 2.10. Tabel Kebenaran IC 7476 [4]

Tabel 2.10.(Lanjutan) Tabel Kebenaran IC 7476 [4]

Mikrokontroler AVR memiliki arsitektur RISC (Reduced Instruction Set

Computing) 8-bit, di mana semua instruksi dikemas dalam kode 16-bit dan sebagian besar

instruksi dieksekusi dalam 1 siklus clock. Secara umum, AVR dapat dikelompokkan menjadi 4 kelas, yaitu keluarga ATtiny, keluarga AT90Sxx, keluarga ATmega, dan AT86RFxx [5]. Masing-masing kelas pada dasarnya dibedakan oleh memori, pheripheral, dan fungsinya.

2.6.1

Arsitektur dan Konfigurasi Pin ATmega8535

ATmega8535 memiliki fasilitas yang cukup lengkap. Arsitektur ATmega8535 terdiri dari bagian-bagian sebagai berikut [5]:

1. Saluran I/O sebanyak 32 buah, yaitu Port A, Port B, Port C, dan Port D. 2. ADC 10-bit sebanyak 8 saluran.

3. Tiga buah Timer/Counter dengan kemampuan pembandingan. 4. CPU yang terdiri atas 32 buah register.

5. Watchdog Timer dengan osilator internal. 6. SRAM sebesar 512 byte.

7. Memori Flash sebesar 8 kb dengan kemampuan Read While Write.

8. Unit interupsi internal dan eksternal. 9. Port antarmuka SPI.

11.Antarmuka komparator analog.

12.Port USART untuk komunikasi serial.

Kapabilitas detail dari ATmega8535 adalah sebagai berikut [5]:

1. Sistem mikroprosesor 8-bit berbasis RISCdengan kecepatan maksimal 16 MHz. 2. Kapabilitas memori flash 8 KB, SRAM sebesar 512 byte, dan EEPROM

(Electrically Erasable Programmable Read Only Memory) sebesar 512 byte.

3. ADCinternal dengan fidelitas 10-bit sebanyak 8 saluran.

4. Portal komunikasi serial (USART) dengan kecepatan maksimal 2,5 Mbps. 5. Enam pilihan mode sleep menghemat penggunaan daya listrik.

Mikrokontroler ATmega8535 memiliki beberapa kemasan, yaitu PLCC, TQFP, QFN/MLF, dan PDIP. Selain kemasan PDIP yang memiliki 40 pin, kemasan mikrokontroler ATmega8535 yang lain memiliki 44 pin. Dalam penelitian ini akan digunakan mikrokontroler ATmega8535 dengan kemasan PDIP. Konfigurasi pin untuk mikrokontroler ATmega8535 kemasan PDIP ditunjukkan oleh gambar 2.14.

Gambar 2.14. Konfigurasi Pin ATmega8535 [6]

Fungsi dari setiap pin ATmega8535 adalah sebagai berikut [5]: 1. VCC merupakan pin yang berfungsi sebagai pin masukan catu daya. 2. GND merupakan pin ground.

3. Port A (PA0..PA7) merupakan pin I/O dua arah dan pin masukan ADC.

5. Port C (PC0..PC7) merupakan pin I/O dua arah dan pin fungsi khusus, yaitu TWI, komparator analog, dan Timer Oscilator.

6. Port D (PD0..PD7) merupakan pin I/O dua arah dan pin fungsi khusus, yaitu komparator analog, interupsi eksternal, dan komunikasi serial.

7. RESET merupakan pin yang digunakan untuk me-reset mikrokontroler. 8. XTAL1 dan XTAL2 merupakan pin masukan clock eksternal.

9. AVCC merupakan pin masukan tegangan untuk ADC. 10.AREF merupakan pin masukan tegangan referensi ADC.

2.6.2

Peta Memori

AVR memiliki 2 ruang memori utama, yaitu memori data dan memori program [6]. Memori data dibagi menjadi 3 bagian, yaitu:

1. 32 register umum, menempati alamat $00 sampai $1F.

2. 64 register I/O, merupakan register khusus untuk mengatur fungsi berbagai

pheripheral mikrokontroler. Register ini menempati alamat $20 sampai $5F.

3. 512 byte SRAM internal, menempati alamat $60 sampai $25F.

Memori program terletak dalam 4KByte x 16-bit Flash PEROM, dan tersusun dalam word

(2 byte). Flash PEROM menempati alamat $000 sampai $FFF. ATmega8535 memiliki

12-bit Program Counter (PC), sehingga mampu mengalamati isi Flash. Peta memori data dan

memori program ditunjukkan pada gambar 2.15.

Gambar 2.15. (a) Peta Memori Data (b) Peta Memori Program [5]

Selain itu, ATMega 8535 memiliki fitur memori EEPROM (Electrically Erasable

Programmable Read Only Memory) 8-bit sebanyak 512 byte, dengan alamat $000 sampai

$1FF. EEPROM dapat menyimpan data saat tidak dicatu dan juga dapat diubah saat program berjalan [5].

2.7

LCD M1632

LCD M1632 merupakan modul LCD dengan tampilan 16x2 baris dengan konsumsi daya rendah (2,7 volt sampai 5,5 volt). Setiap karakter dibentuk dari 5x8 atau 5x10 dot. Modul LCD ini dilengkapi dengan mikrokontroler HD44780 buatan Hitachi yang didesain khusus untuk mengendalikan LCD. Gambar 2.16 menunjukkan kofigurasi pin HD44780 pada LCD M1632.

Gambar 2.16 Konfigurasi Pin HD44780

Fungsi setiap pin HD44780 adalah sebagai berikut: 1. Pin 1 (GND): ground (0V).

2. Pin 2 (Vcc): masukan untuk catu daya LCD (+5V).

3. Pin 3 (VEE): tegangan pengatur kontras LCD, maksimum pada 0Volt.

4. Pin 4 (RS): Register Select, pin pemilih register yang akan diakses (1 = akses ke register data; 0 = akses ke register perintah).

5. Pin 5 (R/W): mode baca atau tulis pada LCD (1 = mode pembacaan; 0 = mode penulisan).

6. Pin 6 (E): pin untuk mengaktifkan clock LCD. 7. Pin 7-14 (D0-D7): jalur data bus.

8. Pin 15 (anoda): tegangan positif backlight modul LCD 9. Pin 16 (katoda): tegangan negative backlight modul LCD.

HD44780 memiliki dua 8-bit register yang aksesnya diatur oleh pin RS, yaitu register instruksi (IR) dan register data (DR). Saat RS berlogika 0, register yang diakses adalah register perintah, dan pada saat RS berlogika 1, register yang diakses adalah register data [5]. IR berfungsi untuk menyimpan kode perintah, seperti menghapus tampilan dan pergeseran cursor, serta informasi alamat untuk DDRAM (Display Data RAM) dan CGRAM (Character Generator RAM) [7]. DR adalah tempat penyimpan sementara data yang akan ditulis ke DDRAM atau CGRAM, dan data yang akan dibaca dari DDRAM atau CGRAM.

2.7.1

DDRAM (

Display Data

RAM), CGROM (

Character Generator

ROM), dan CGRAM (

Character Generator

RAM)

DDRAM (Display Data RAM) menyimpan data tampilan yang diwakili oleh 8-bit kode karakter [7]. Kapasitas tambahannya mencapai 80x8 bit, atau 80 karakter. Gambar 2.17 menunjukkan alamat DDRAM tempat karakter akan ditampilkan.

Gambar 2.17. Alamat DDRAM pada LCD 16x2 [7]

CGROM (Character Generator ROM) merupakan memori untuk menghasilkan pola karakter 5x8 dot atau 5x10 dot dari karakter yang sudah terdapat pada HD44780. Pola karakter yang dapat dihasilkan adalah 208 pola untuk 5x8 dot, dan 32 pola untuk 5x10 dot.

2.7.2

Register Perintah

Register perintah berfungsi untuk membaca perintah-perintah dari mikrokontroler ke HD44780 pada saat proses penulisan data atau tempat status dari HD44780 pada saat pembacaan data. Penulisan data ke register perintah dilakukan dengan tujuan mengatur tampilan LCD, inisialisasi, dan mengatur Address Counter maupun Address Data [5].

Proses penulisan data menggunakan mode 4-bit. Penulisan diawali dengan memberikan logika 0 pada pin RS yang menunjukkan akses ke register perintah, dan logika 0 pada R/W untuk mengaktifkan proses penulisan data. Data nibble high (bit 7 sampai bit 4) terlebih dahulu dikirimkan, diawali pulsa logika 1 pada pin E sebagai clock, dan kemudian diikuti dengan mengirimkan data nibble low (bit 4 sampai bit 0) yang juga diawali dengan pulsa 1 pada pin E.

Proses pembacaan data pada register perintah biasa digunakan untuk melihat status

busy dari LCD atau membaca Address Counter [5]. Proses pembacaan data dari register perintah sama seperti proses penulisan data ke register perintah, hanya saja pin R/W diatur pada logika 1 untuk mengaktifkan proses pembacaan data.

2.7.3

Register Data

Register data adalah register dimana mikrokontroler dapat menuliskan atau membaca data ke atau dari DDRAM [5]. Penulisan data pada register data dilakukan untuk menampilkan data yang akan ditampilkan pada LCD. Proses penampilan karakter pada LCD diawali dengan memberikan logika 1 pada pin RS yang menunjukkan akses ke register data, kondisi R/W diatur pada logika 0 yang menunjukkan proses penulisan data. Data nibble high dikirimkan diawali dengan pemberian logika 1 dan 0 pada pin E sebagai

clock, dan kemudian diikuti dengan mengirimkan data nibble low yang juga diawali dengan pemberian logika 1 dan 0 pada pin E.

21

BAB III

RANCANGAN PENELITIAN

3.1

Perancangan Perangkat Keras

Perancangan perangkat keras dibagi menjadi beberapa blok rangkaian, yaitu blok rangkaian mikrokontroler, blok rangkaian push button, blok rangkaian konektor ke papan untai digital dan dari papan untai digital, dan blok rangkaian penampil LCD. Diagram blok sistem keseluruhan ditunjukkan gambar 3.1.

Gambar 3.1. Diagram Blok Sistem Keseluruhan

Sistem ini digunakan untuk menguji kebenaran gerbang logika NAND, NOR dan NOT, serta enkoder 8 ke 3, penjumlah biner 4-bit, dan JK flip-flop yang terdapat pada papan untai digital. Pengujian dilakukan dengan membandingkan secara look-up table.

Setiap gerbang logika dan rangkaian logika yang akan diuji memiliki tabel pengujian yang telah disimpan dalam memori mikrokontroler, dan yang digunakan sebagai pembanding. Tabel pengujian merupakan tabel masukan dan keluaran berdasar tabel kebenaran masing-masing gerbang logika dan rangkaian logika yang diuji oleh sistem ini. Hasil akhir perbandingan merupakan hasil akhir dari pengujian yang menunjukkan keadaan baik atau keadaan rusak dari gerbang logika atau rangkaian logika yang diuji.

Cara kerja dari sistem penguji kebenaran ini adalah sebagai berikut:

1. Push button digunakan untuk memilih gerbang logika atau rangkaian logika yang akan diuji.

Mikrokontroler

ATmega8535 Papan Untai Digital

Penampil LCD Push

2. Mikrokontroler akan mengolah masukan dari push button. Papan untai digital akan menerima masukan dari mikrokontroler sesuai masukan pada tabel pengujian. 3. Keluaran dari papan untai digital dikirim kembali ke mikrokontroler.

Mikrokontroler akan membandingkan keluaran dari papan untai dengan keluaran pada tabel pengujian.

4. Masukan dan keluaran papan untai digital, dan hasil akhir pengujian ditampilkan pada LCD

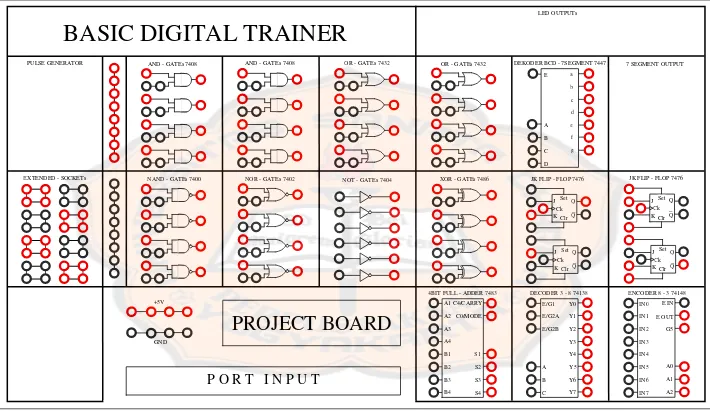

Papan untai digital yang akan digunakan pada penelitian ini adalah papan untai digital yang digunakan di laboratorium teknik digital. Layout papan untai digital ditunjukkan pada gambar 3.2. Berdasarkan gambar 3.2 masukan dan keluaran setiap gerbang logika dan rangkaian logika adalah sebagai berikut:

1. Gerbang NAND dan NOR, memiliki 2 masukan dan 1 keluaran. 2. Gerbang NOT, memiliki 1 masukan dan 1 keluaran.

3. Enkoder 8 ke 3, memiliki 9 masukan (IN0-IN7, dan E IN) dan 5 keluaran (A0-A3, G5, dan E OUT).

4. Penjumlah biner 4-bit, memiliki 9 masukan (A1-A4, B1-B4, dan C0/MODE) dan 5 keluaran (S1-S4, dan C4/CARRY).

5. JK filp-flop, memiliki 5 masukan (Set, Clr, J, K, dan Ck) dan 2 keluaran (Q dan ).

Jumlah masukan dan keluaran ditunjukkan pada tabel 3.1. Perancangan blok rangkaian mikrokontroler, blok rangkaian konektor ke papan untai digital dan dari papan untai digital akan mengacu pada tabel 3.1.

Tabel 3.1. Tabel Jumlah Masukan dan Keluaran Gerbang Logika dan Rangkaian Logika Jumlah Masukan Jumlah Keluaran

NAND 2 1

NOR 2 1

NOT 1 1

Enkoder 8 ke 3 9 5

Penjumlah biner 4-bit 9 5

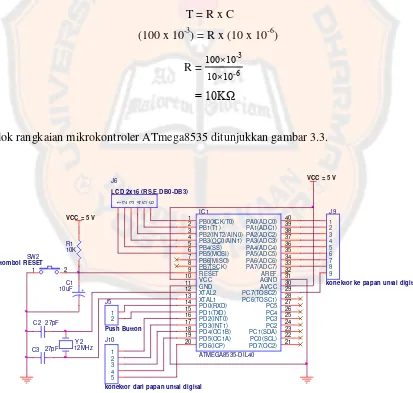

3.1.1

Mikrokontroler ATmega8535

Blok rangkaian mikrokontroler terdiri dari rangkaian tombol reset, rangkaian kristal osilator, beserta rangkaian konektor yang berfungsi untuk menghubungkan port I/O mikrokontroler dengan blok rangkaian lain.

Mikrokontroler ATmega8535 dilengkapi dengan osilator internal yang dapat digunakan sebagai sumber clock pada CPU. Agar osilator internal tersebut dapat digunakan, maka dibutuhkan sebuah kristal dan dua buah kapasitor yang dihubungkan ke XTAL1 dan XTAL2. Kristal yang digunakan dalam perancangan ini adalah kristal 12MHz, dengan kapasitor 27pF.

Pin reset digunakan untuk mereset mikrokontroler. Jika pin reset diberi logika RENDAH (0) lebih dari 1,5µs maka reset akan aktif, walaupun clock tidak dalam keadaan aktif [6]. Pada perancangan ini waktu reset yang diinginkan 100 ms, dengan menggunakan kapasitor 10 F, maka nilai resistor yang dibutuhkan dapat dihitung sebagai berikut:

T = R x C

Blok rangkaian mikrokontroler ATmega8535 ditunjukkan gambar 3.3.

Gambar 3.3. Blok Rangkaian Mikrokontroler ATmega8535

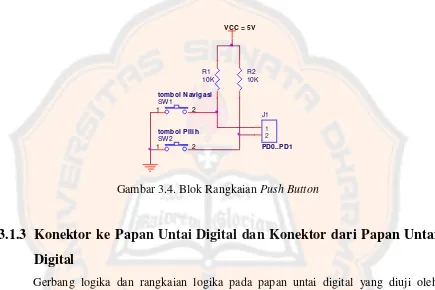

3.1.2

Push Button

Sistem penguji kebenaran ini menguji lebih dari satu gerbang logika dan rangkaian logika, sehingga digunakan push button agar sistem penguji hanya dapat menguji satu gerbang logika atau rangkaian logika dalam satu waktu. Ada 2 buah push button yang digunakan sebagai tombol navigasi dan tombol pilih. Pada penelitian ini push button

dirancang agar menjadi aktif rendah dan dihubungkan ke port D.0 dan D.1 (PD0 dan PD1) mikrokontroler. Blok rangkaian push button ditunjukkan gambar 3.4.

Gambar 3.4. Blok Rangkaian Push Button

3.1.3

Konektor ke Papan Untai Digital dan Konektor dari Papan Untai

Digital

Gerbang logika dan rangkaian logika pada papan untai digital yang diuji oleh sistem ini memiliki masukan dan keluaran yang bervariasi, sedangkan mikrokontroler memiliki jumlah port yang terbatas. Pada perancangan ini port mikrokontroler yang bertugas memberi masukan dan menerima keluaran dari gerbang logika dan rangkaian logika akan dihubungkan ke konektor, sehingga port tersebut dapat digunakan bersama.

Gambar 3.5. Blok Rangkaian Konektor (a) ke Papan Untai Digital (b) dari Papan Untai Digital

3.1.4

Penampil LCD

Perancangan ini menggunakan LCD M1632 yang memiliki 2 mode pengiriman data, yaitu mode 8-bit dan 4-bit. Jika menggunakan mode 4-bit, maka akan ada 6 jalur yang dihubungkan ke port I/O mikrokontroler (E, RS, dan 4 untuk jalur data). Jika menggunakan mode 8-bit, maka akan ada 10 jalur yang dihubungkan ke port I/O mikrokontroler (E, RS, dan 8 untuk jalur data).

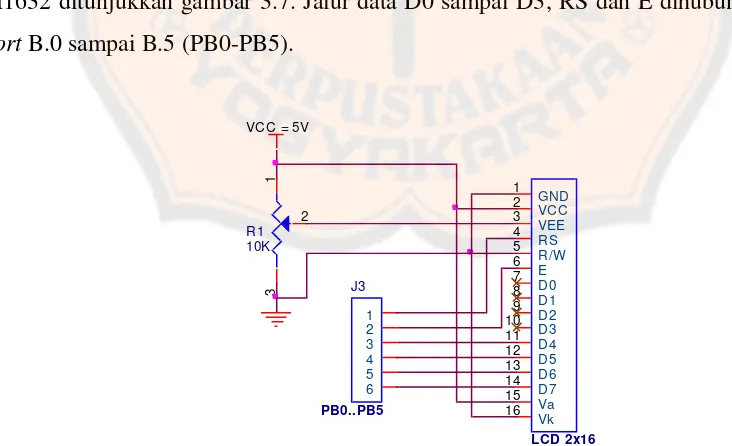

Pengiriman data menggunakan mode 8-bit lebih cepat dibanding pengiriman data mode 4-bit. Namun, karena kecepatan pengiriman data tidak begitu diutamakan, maka pada penelitian ini digunakan pengiriman data mode 4-bit. Blok rangkaian penampil LCD M1632 ditunjukkan gambar 3.7. Jalur data D0 sampai D3, RS dan E dihubungkan dengan

port B.0 sampai B.5 (PB0-PB5).

Gambar 3.7. Blok Rangkaian Penampil LCD

3.1

Perancangan Perangkat Lunak

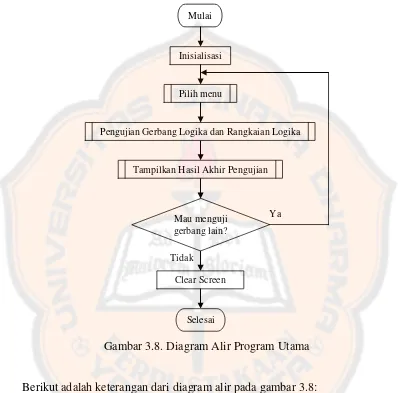

Perangkat keras sistem penguji kebenaran diatas, hanya dapat bekerja dengan baik jika mikrokontroler yang merupakan otak sistem telah diprogram. Diagram alir program utama penguji kebenaran ini ditunjukkan gambar 3.8.

Gambar 3.8. Diagram Alir Program Utama

Berikut adalah keterangan dari diagram alir pada gambar 3.8:

1. Semua port I/O pada mikrokontroler diinisialisasi di awal program sesuai dengan perancangan perangkat keras.

2. Pilih menu, adalah sub rutin untuk memilih gerbang logika atau rangkaian yang akan diuji. Pilihan ditampilkan di LCD, diubah dengan menggunakan tombol navigasi, dan untuk memilih digunakan tombol pilih.

3. Setelah gerbang logika atau rangkaian dipilih, maka mikrokontroler akan mulai melakukan pengujian. Mikrokontroler akan mengirimkan masukan ke papan untai digital, menerima keluaran dari papan untai digital, kemudian membandingkan keluaran tersebut dengan tabel pengujian yang tersimpan.

Selesai Clear Screen Mau menguji gerbang lain?

Ya Inisialisasi

Mulai

Pilih menu

Tampilkan Hasil Akhir Pengujian

Tidak

4. Jika pengujian telah selesai dilakukan, maka hasil akhinya akan ditampilkan di penampil LCD.

3.2.1

Pilih Menu

Pilih menu merupakan proses untuk menentukan tabel pengujian yang digunakan, agar sesuai dengan gerbang logika atau rangkaian logika yang ingin diuji saat itu. Pada sub rutin pilih menu, menu yang dipilih adalah gerbang logika atau rangkaian logika yang akan diuji, yaitu NAND, NOR, dan NOT, Enkoder 8 ke 3, Penjumlah biner 4-bit, dan JK flip-flop. Diagram alir sub rutin pilih menu ditunjukkan gambar 3.9.

A

gerbang/rangkaian yang diuji (R) = 1

Gambar 3.9. Diagram Alir Sub Rutin Pilih Menu

Proses dalam pilih menu ini dijelaskan sebagai berikut: 1. Menampilkan karakter “Pilih gerbang/rangkaian yang diuji”.

2. Menampilkan pilihan gerbang logika dan rangkaian logika yang dapat diuji pada baris pertama LCD. Baris kedua menampilkan keterangan push button yang digunakan untuk mengganti pilihan dan untuk memilih.

3. Pemilihan dilakukan menggunakan 2 tombol, yaitu tombol navigasi untuk mengganti pilihan gerbang logika atau rangkaian logika (PD.0), sedangkan untuk memilih menggunakan tombol pilih (PD.1).

4. Jika tombol navigasi ditekan (PD.0=1), maka LCD akan menampilkan pilihan gerbang atau rangkaian logika selanjutnya. Urutan gerbang dan rangkaian logika yang ditampilkan adalah NAND, NOR, NOT, Enkoder 8 ke 3, Penjumlah Biner 4-bit, JK flip-flop, kemudian kembali lagi ke NAND.

5. Jika tombol pilih ditekan (PD.1=1), maka mikrokontroler akan memulai proses pengujian.

3.2.2

Pengujian Gerbang Logika dan Rangkaian Logika

Pengujian gerbang logika dan rangkaian logika adalah proses inti pada sistem pengujian ini. Proses pengujian terdiri dari pengiriman data masukan ke papan untai digital, menerima data keluaran dari papan untai digital, dan perbandingan keluaran dari papan untai digital dengan keluaran pada tabel pengujian yang telah disimpan di mikrokontroler.

Diagram alir untuk sub rutin pengujian gerbang logika dan rangkaian logika ditunjukkan gambar 3.10. Berikut ini merupakan tabel pengujian dari setiap gerbang logika dan rangkaian logika yang akan digunakan dalam pengujian:

C

“Penjumlah Biner 4-bit” “JK flip-flop”

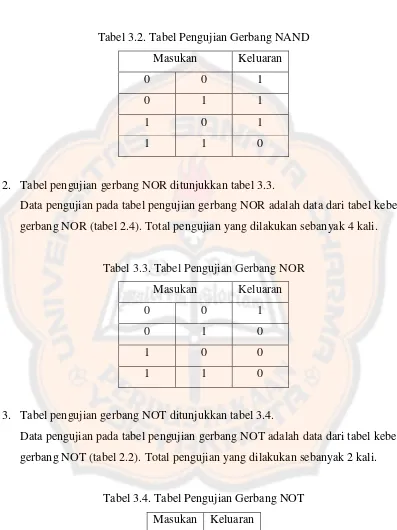

1. Tabel pengujian gerbang NAND ditunjukkan tabel 3.2.

Data pengujian pada tabel pengujian gerbang NAND adalah data dari tabel kebenaran gerbang NAND (tabel 2.3). Total pengujian yang dilakukan sebanyak 4 kali.

Tabel 3.2. Tabel Pengujian Gerbang NAND Masukan Keluaran

0 0 1

0 1 1

1 0 1

1 1 0

2. Tabel pengujian gerbang NOR ditunjukkan tabel 3.3.

Data pengujian pada tabel pengujian gerbang NOR adalah data dari tabel kebenaran gerbang NOR (tabel 2.4). Total pengujian yang dilakukan sebanyak 4 kali.

Tabel 3.3. Tabel Pengujian Gerbang NOR Masukan Keluaran

0 0 1

0 1 0

1 0 0

1 1 0

3. Tabel pengujian gerbang NOT ditunjukkan tabel 3.4.

Data pengujian pada tabel pengujian gerbang NOT adalah data dari tabel kebenaran gerbang NOT (tabel 2.2). Total pengujian yang dilakukan sebanyak 2 kali.

Tabel 3.4. Tabel Pengujian Gerbang NOT Masukan Keluaran

0 1

4. Tabel pengujian enkoder 8 ke 3 ditunjukkan tabel 3.5.

Data pengujian pada tabel pengujian enkoder 8 ke 3 ditentukan berdasar tabel kebenaran enkoder 8 ke 3 (tabel 2.5). Total pengujian yang dilakukan sebanyak 15 kali.

Tabel 3.5. Tabel Pengujian Enkoder 8 ke 3

Masukan Keluaran

4 A A A

1 0 0 0 0 0 0 0 0 1 1 1 1 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1

0 1 1 1 1 1 1 1 1 1 1 1 1 0

0 1 0 1 0 1 0 1 0 0 0 0 0 1

0 0 0 1 1 1 1 0 0 0 0 0 0 1

0 0 1 0 1 0 1 0 1 0 0 1 0 1

0 1 0 0 1 1 0 0 1 0 0 1 0 1

0 0 0 1 1 0 0 1 1 0 1 0 0 1

0 1 1 0 0 0 0 1 1 0 1 0 0 1

0 1 1 1 0 0 1 1 1 0 1 1 0 1

0 0 0 0 1 0 1 1 1 0 1 1 0 1

0 1 0 1 0 1 1 1 1 1 0 0 0 1

0 0 1 0 1 1 1 1 1 1 0 1 0 1

0 1 0 1 1 1 1 1 1 1 1 0 0 1

0 0 1 1 1 1 1 1 1 1 1 1 0 1

5. Tabel pengujian penjumlah biner 4-bit ditunjukkan tabel 3.6.

Data pengujian pada tabel pengujian penjumlah biner 4-bit ditentukan berdasar persamaan penjumlah biner 4-bit (persamaan 2.4). Total pengujian yang dilakukan sebanyak 10 kali.

Tabel 3.6. Tabel Pengujian Penjumlah Biner 4-bit

Masukan Keluaran

C0 A0 A1 A2 A3 B0 B1 B2 B3 S0 S1 S2 S3 S4

Tabel 3.6.(Lanjutan) Tabel Pengujian Penjumlah Biner 4-bit

Masukan Keluaran

C0 A0 A1 A2 A3 B0 B1 B2 B3 S0 S1 S2 S3 S4

0 0 1 0 0 0 0 1 1 0 1 1 1 0

0 0 0 1 0 0 1 1 1 0 1 0 0 1

0 0 1 1 0 1 1 0 1 1 0 0 0 1

0 0 0 0 1 1 1 1 1 1 1 1 0 1

1 1 0 0 0 0 1 0 1 0 0 1 1 0

1 1 1 0 0 0 1 1 1 0 1 0 0 1

1 1 0 1 0 1 1 0 1 1 0 0 0 1

1 1 1 1 0 1 0 1 1 1 0 1 0 1

1 1 0 0 1 0 0 1 1 0 1 1 0 1

6. Tabel pengujian JK flip-flop ditunjukkan tabel 3.7.

Data pengujian pada tabel pengujian JKflip-flop ditentukan berdasar tabel kebenaran JK flip-flop (tabel 2.10). Total pengujian yang dilakukan sebanyak 7 kali.

Tabel 3.7. Tabel Pengujian JK flip-flop

Masukan Keluaran

CLK PR CLR J K Q

1 0 1 1 1 1 0

1 1 0 1 1 0 1

1 1 1 0 0 0 1

1 1 1 0 1 0 1

1 1 1 1 0 1 0

1 1 1 1 1 0 1

Mulai

pengujian yang sudah dilakukan (c) = 0

keluaran papan untai digital (Y) = 0 keluaran pada tabel pengujian (Z) = 0

Gambar 3.10. Diagram Alir Sub Rutin Pengujian Gerbang Logika dan Rangkaian Logika

3.2.3

Menampilkan Hasil Akhir Pengujian

Proses akhir pengujian adalah dengan menampilkan hasil akhir pengujian pada LCD. LCD akan menampilkan karakter “Keadaan Baik”, jika hasil perbandingan (b) sama dengan total pengujian (a). Jika hasil perbandingan (b) tidak sama dengan total pengujian (a), maka LCD akan menampilkan karakter “Keadaan Rusak”. Gambar 3.11 menunjukkan diagram alir dari sub rutin tampilkan hasil akhir pengujian.

Gambar 3.11. Diagram Alir Sub Rutin Tampilkan Hasil Akhir Pengujian

Mulai

b = a?

Ya

Tidak

“Keadaan Baik” “Keadaan Rusak”

Selesai R=5?

Ya

Tidak

a = 10 A

B

C

R=6?

Ya

Tidak

a = 7

Kirim masukan preset, clear, J dan K

Kirim masukan clock

D

35

BAB IV

HASIL DAN PEMBAHASAN

4.1

PERANGKAT KERAS ALAT PENGUJI KEBENARAN

Rangkaian yang digunakan pada alat penguji kebenaran ini terdiri dari blok rangkaian mikrokontroler, blok rangkaian push button, blok rangkaian konektor ke papan untai digital dan dari papan untai digital, dan blok rangkaian penampil LCD. Gambar dari rangkaian keseluruhan dapat dilihat pada gambar 4.1. Pin LCD pada rangkaian akan dihubungkan ke penampil LCD. Pin masukan dan keluaran pada rangkaian akan dihubungkan ke banana socket yang berfungsi sebagai konektorke papan untai digital. Pin SW 1 dan 2 akan dihubungkan ke push button. Port mikrokontroler yang dihubungkan dengan konektor masukan adalah port A.0 (PA0) sampai port A.7 (PA7) dan port C.7 (PC7), sedangkan konektor keluaran dihubungkan dengan port D.2 (PD2) sampai port D.6 (PD6). Skema port mikrokontroler untuk konektor masukan dan konektor keluaran dapat dilihat pada gambar 4.2.

Gambar 4.1. Rangkaian Keseluruhan Alat Penguji Kebenaran

Pada perangkat keras penguji kebenaran, setiap konektor masukan dan keluaran diberi keterangan sesuai dengan masukan dan keluaran dari setiap gerbang logika dan rangkaian logika pada papan untai digital. Keterangan untuk push button ditampilkan pada

ke Penampil LCD

ke Konektor Keluaran

layar LCD. Layout perangkat keras alat penguji kebenaran ditunjukkan gambar 4.3. Cara menggunakan alat penguji kebenaran ini adalah:

1. Hubungkan konektor power yang ada disamping alat dengan konektor +5V dan 0V pada papan untai digital (atau sumber tegangan lainnya), kemudian tekan switch On-Off ke posisi On untuk menyalakan alat.

2. Tunggu hingga LCD menampilkan pilihan gerbang logika dan rangkaian logika. 3. Hubungkan konektor masukan dan keluaran pada alat penguji kebenaran dengan

konektor masukan dan keluaran pada papan untai digital, dengan keterangan yang sama, sesuai gerbang logika atau rangkaian logika yang ingin diuji menggunakan kabel jumper. Contoh: jika ingin menguji JK flip-flop, maka hubungkan konektor masukan dengan keterangan K pada alat penguji, dengan konektor masukan dengan keterangan K pada papan untai digital.

4. Pilih gerbang atau rangkaian logika yang ingin diuji dengan cara menekan tombol “lanjut” hingga nama gerbang logika atau rangkaian logika yang ingin diuji tertampil pada layar LCD.

5. Tekan tombol “pilih” untuk memulai pengujian.

6. Tunggu hingga proses pengujian selesai. Masukan dan keluaran saat pengujian dilakukan dapat dilihat pada layar LCD.

7. Setelah pengujian selesai dilakukan, hasil pengujian akan ditampilkan di LCD. 8. Tunggu hingga perintah untuk melakukan pengujian lagi tertampil di LCD.

9. Pilih “ya” untuk melakukan pengujian pada gerbang logika atau rangkaian logika yang lain, atau “tidak” untuk selesai.

Gambar 4.2. Skema Port Mikrokontroler untuk Konektor Masukan dan Konektor Keluaran

PC7 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0

Gambar 4.3. Layout Penguji Kebenaran Papan Untai Digital

4.2

PERANGKAT LUNAK ALAT PENGUJI KEBENARAN

Perangkat lunak pada alat penguji kebenaran ini menggunakan bahasa BASIC yang dibagi menjadi 4 bagian yaitu, program utama, sub rutin pilih menu, sub rutin pengujian gerbang logika dan rangkaian logika, dan sub rutin hasil akhir pengujian.

4.2.1

PROGRAM UTAMA

Perintah pada program untuk program utama, adalah:

Program untuk program utama di atas dapat dijelaskan sebagai berikut:

Program utama diawali dengan inisialisasi port mikrokontroler, pin LCD, dan variabel yang digunakan dalam program. Label “Mulai” setelah inisialisasi digunakan untuk perulangan saat user memilih untuk melakukan pengujian lagi. Nilai awal port A, C, dan D serta variabel Msk dan Klr diberikan setelah label “Mulai” agar saat pengujian ulang dilakukan nilai pengujian selanjutnya tidak tertumpuk dengan nilai pengujian sebelumnya. Nilai awal yang diberikan adalah 0. Perintah “Gosub Menu”, “Gosub Pengujian”, dan “Gosub

Hasil” pada program berfungsi agar eksekusi dari program utama dapat berpindah ke sub

rutin.

Setelah pengujian dilakukan dan hasil akhir ditampilkan (eksekusi sub rutin pilih menu, sub rutin pengujian gerbang logika dan rangkaian logika, dan sub rutin hasil akhir pengujian selesai) eksekusi dari sub rutin kembali ke program utama. Perintah “Locate 1 ,

1 : Lcd " Uji yang lain?"” untuk menampilkan perintah “Uji yang lain?” pada layar LCD dimulai pada baris pertama kolom pertama, sedangkan perintah “Locate 2 , 1 : Lcd

4.2.2

Pilih Menu

Perintah pada program untuk sub rutin pilih menu adalah:

Program untuk sub rutin pilih menu dapat dijelaskan sebagai berikut:

Perintah “Cls” berfungsi untuk membersihkan layar LCD dari tampilan

sebelumnya, sedangkan perintah ”Cursor Off” untuk mematikan cursor LCD. Variabel R

digunakan sebagai counter yang menentukan nama gerbang atau rangkaian logika yang ditampilkan. R=1 untuk menampilkan pilihan gerbang NAND, R=2 untuk menampilkan piihan gerbang NOR, R=3 untuk menampilkan pilihan gerbang NOT, tampilan pilihan ini dieksekusi pada perintah “Gosub Tampil”.

Pilih menu diawali dengan menampilkan perintah untuk memilih rangkaian yang akan diuji, dengan menggunakan perintah “Locate 1 , 1 : Lcd "Pilih rangkaian"

Locate 2 , 1 : Lcd "yang akan diuji"” pada program. Perintah ini ditampilkan selama 2 detik. Tampilan awal pilih menu dapat dilihat pada gambar 4.4.

Gambar 4.4. Tampilan Awal Pilih Menu

Setelah tampilan awal pilih menu LCD akan menampilkan pilihan gerbang logika dan rangkaian logika yang bisa diuji satu per satu sesuai nilai R saat itu. Baris pertama akan menampilkan nama gerbang logika atau rangkaian logika, sedangkan baris kedua menampilkan keterangan push button SW1 dan push button SW2. LCD akan terus menampilkan satu nama gerbang logika atau rangkaian logika secara terus menerus sampai salah satu push button ditekan. Setiap push button SW1 ditekan, maka nilai R akan menjadi R+1. Jika nilai R=7, maka nilai R akan kembali menjadi 1, karena gerbang logika dan rangkaian logika yang dapat diuji hanya berjumlah 6. Contoh tampilan pilih menu dapat dilihat pada gambar 4.5.

Gambar 4.5. Tampilan Pilih Menu

dilihat pada gambar 4.6. Proses eksekusi akan kembali ke program utama dan melanjutkan ke sub rutin pengujian gerbang logika dan rangkaian logika.

Gambar 4.6. Tampilan LCD setelah Pemilihan

4.2.3

Pengujian Gerbang Logika dan Rangkaian Logika

Program untuk sub rutin pengujian gerbang logika dan rangkaian logika dapat dijelaskan sebagai berikut:

Pengujian dilakukan dengan cara membandingkan secara look-up table, sehingga setiap gerbang logika dan rangkaian logika memiliki tabel pengujian yang berbeda. Program diawali dengan mengecek nilai R untuk memulai pengujian sesuai gerbang logika atau rangkaian logika yang telah dipilih. Jika nilai R saat ini adalah 1, perintah pada program adalah “If R = 1 Then Goto Gnand End If” (user memilih untuk menguji

gerbang NAND) maka eksekusi akan berpindah ke program di label “Gnand:”.

Pengujian tiap gerbang logika dan rangkaian logika diawali dengan memberikan nilai awal pada variabel I0 dan O. Variabel I0 berfungsi untuk menyimpan nilai yang memuat indeks data masukan dari tabel yang dituju. Variabel O berfungsi untuk menyimpan nilai yang memuat indeks data keluaran dari tabel yang dituju. Data masukan yang ditunjuk I0 kemudian disimpan dalam variabel Msk, sedangkan data keluaran yang ditunjuk O disimpan dalam variabel Klr. Pengujian dilakukan berulang sebanyak jumlah pengujian pada tabel pengujian. Perulangan pengujian pada program menggunakan perintah FOR-NEXT. Jumlah pengujian yang dilakukan disimpan dalam variabel A, sedangkan hasil perbandingan look-up table akan disimpan dalam variabel B.

Proses pengujian dimulai dengan memberi masukan ke papan untai digital, dan menyimpan keluaran dari tabel pengujian, perintah yang digunakan adalah “Msk =

Lookup(i0 , Tpnand) : Klr = Lookup(o , Tpnand) : Gosub Kesini”. Setelah memberikan

masukan, proses pengujian dilanjutkan dengan membaca nilai keluaran dari papan untai digital kemudian membandingkan keluaran tersebut dengan keluaran tabel pengujian yang disimpan di variabel Klr. Setiap hasil perbandingan yang sama akan dihitung dan disimpan

dalam variabel B. Proses ini dijalankan menggunakan perintah “If Pind.2 = Klr.2 Then

Incr B Else B = B End If”. Sebelum pengujian selanjutnya diproses, nilai variabel I0 dan

O diubah ke nilai yang berisi indeks data pengujian selanjutnya, perintah yang dijalankan adalah “I0 = I0 + 2 : O = O + 2”. I0 diberi nilai awal 0, dan O diberi nilai awal 1, karena

nilai yang memuat indeks data dimulai dari 0. Gambar 4.7 memperlihatkan tabel pengujian gerbang NAND untuk look-up table pada program.Proses pengujian yang dijalankan pada setiap gerbang logika dan rangkaian logika sama, kecuali pada pengujian JK flip-flop.

Masukan preset, clear, dan JK diberikan terlebih dahulu, kemudian clock diberi masukan.

Clock diberi masukan sebanyak dua kali, yaitu clock=1 kemudian clock=0. Perbandingan keluaran dilakukan setelah masukan clock.

Gambar 4.7. Tabel Pengujian Gerbang NAND untuk Look-Up Table Pada Program

Masukan dan keluaran papan untai digital selama proses pengujian ditampilkan pada layar LCD. Gambar 4.8 memperlihatkan tampilan LCD pada setiap proses pengujian gerbang logika dan rangkaian logika. Saat proses pengujian gerbang NAND, NOR, dan NOT, yang ditampilkan pada layar LCD adalah variabel A dan B, keterangan masukan dan keluaran, juga keadaan masukan dan keluaran saat itu. saat proses pengujian enkoder 8 ke 3, penjumlah biner 4-bit, dan JK flip-flop hanya keterangan masukan dan keluaran, serta keadaan masukan dan keluaran saat itu yang ditampilkan. Setelah proses eksekusi sub rutin pengujian gerbang logika dan rangkaian logika selesai, proses eksekusi akan kembali ke program utama dan melanjutkan ke sub rutin hasil akhir pengujian.

(a) (b) (c)

(d) (e) (f)

Gambar 4.8. Tampilan LCD pada Proses Pengujian (a) Gerbang NAND, (b) Gerbang NOR, (c) Gerbang NOT, (d) Enkoder 8 ke 3, (e) Penjumlah Biner 4-bit, (f) JK flip-flop

![Tabel 2.4. Tabel Kebenaran Gerbang NOR [2]](https://thumb-ap.123doks.com/thumbv2/123dok/1743601.2088902/23.595.93.529.493.728/tabel-tabel-kebenaran-gerbang-nor.webp)