MODtJLASI DELTA

Budihardja Murtianta

\JO])ll/,4SJ f)fT T4 Nudihurd;o Afurflal!ta

Program Studi Teknik Elektro, Fakultas Teknik Elektronika'& Komputer- UKSW

J Salati!.!.a ')( l I l

Email hudihardJ<WL'vahoo com

Intisari

Modulasi Delta merupakan salah satu dari beberapa macam modulasi digital yang memnakan Sll<ltll teknik knnversi sinval o11olo!! to di!!ital van!!. digunak;m untuk transmis1 informasi suara Modulasi Delta merupakan sebuah teknik modulasi dimana suatu sinyal analog dapat dikodekan dalam digit (bit) . Modulasi Delta merupakan salah satu sistem berbasis /}ulse ('ode Modulattoll (PCM). Prinsip kerja Modulasi Delta adalah pengmman deretan pulsa-pulsa dengan Iebar tetap, yang polaritasnya menunjukkan apakah keluaran

illfegralur harus naik atau turun pada masing-masing pulsa Keluaran dibuat naik atau tunm oleh suatu langkah yang tetap pada masing-masing pulsa. Modulator Delta membandingkan isyarat analog dan successiFe isyarat hasil Digttal to Aoalog Conl'erter

(DAC) dan mentransmisikannya dengan l bit saja. Rangkaian Modulator Delta terdiri atas beberapa blok rangkaian yaitu pembanding, encoder ( D-Flip tlop ), mtegrator

cliskret yang merupakan untai staircase generator dan pembangkit clock Agar dapat dipancarkan lev,at media udara keluaran Modulator Delta dimasukkan modulator FSK dan pemancar FM

Kata knnci : Modulas1 Delta, 1111egra1m· t'ilt 'hie I

1.

Pendahuluan

Modulasi Delta merupakan salah satu dari beberapa macam modulasi digital yang tujuannya untuk merubah isyarat intormasi yang berupa isyarat analog menjadi digitaL Sistem modulasi digital vang ada antara lain adalah

I --,: ; セ@ ' セ@ 1 .. , I l ' 'I

Modulasi kode-pulsa U'ulse ('ode Modukmon) digunakan untuk mengubab 1syarat analog menjadi hentuk digital Dalam sistem PCM, ke!ompok-ke!ompok pu!sa atau

kode yang dipancarkan merepresentasikan angka-angka

dengan tingkat-tingkat tegangan modulasi

.., . f)e/ta Afodululwtt (DM)

biner yang bersesuaian

uemodulator harus muk arau turun tergantung dari isyarat digital hasil Modulasi Delta

Pada PCN1, isyarat analog dicuplik pada i!lletTal yang reguler, clan amplitudo dari isyarat dikodekan menjadi dalam bentuk bit. Variasi dari teknik sejenis PCM adalah Modulasi

Delta V(l!l!l rnemhandlnukan isvarat analou dan Xli<H'\\'/l'C' isvarat hasil nt.!!ilul /1!

Analog Com·erler (DAC) dan mentransmisikannya dengan l bit saja Sistem modulas1 digital menggunakan teknik Modulasi Delta mempunyai dua bagian dasar, yaitu

bagian modulator dan demodulator. Pada tulisan ini akau uibahas tentang 1\lodulatm

Delta yang dipancarkan secara FM

2. Modulator Delta

Bagian modulator ini terdiri dari beberapa untai sebagai berikut •

Untai Pembanding

- Untai Encoder

- Untai Digital to Analog Converter (DAC)

Untai Generator Pulsa (Clock)

- t

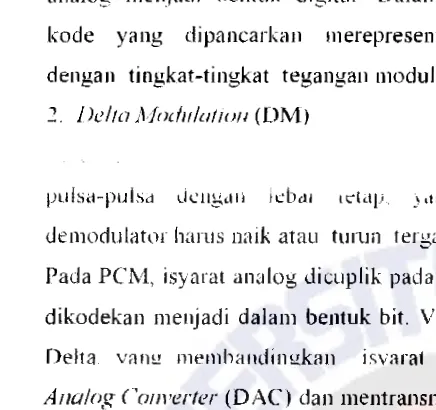

fntai Osilator Isyarat lnf(mnasiBagan Modulator Delta ditunjukkan pada Gambar 1.

;/

/

ClOCK

[image:2.1054.37.473.185.595.2]l -... I l \ 1 I\.\ t t

Gambar ! . Modulator Delta

2.1.

llntai Osilator lsyarat lnformasi

I

HOJ)l.i/,A.\1/JI:I lA

Uudilwrdtu A fllr!WIIhl

\ , \()

..

I \'lecJ•,,, '1•

Us!l,uu, J.:> yarat mtor mas I dli セ、mァ\QQ@ 1uasukau t::.y a1 al uJJ u1 DH1Sl <tkdli

menghasilkan isyarat sinus yang merupakan isyarat yang akan dimodulasi menjadi data

biner pada proses tnmsmisi 、ゥセゥエ。ャ@ lTnt<'li osil<'ltor ini mempunv<1i jangkauan frekuenc;i

keluaran dari 0 sampa1 I 0 kHz dengan menggunakan IC XR2206 yang difungsikan

sebagai penghasil isyarat sinus. VCO merupakan osilator terkendali tegangan, pada IC

XR1206 tegangan yang merupakan pengendali osilator pada blok VCO dihasilkan o!eh

arus pada blok nlt-rellf .\11'ifches sedangkan hambatannya yaitu 1imi11g rnistor R

terhubung pad a pin nomor 7. Sedangkan nilai frekuensi osilasi ( fo ) ditentukan olell

komponen luar yaitu tinnng cupositor C dan timing resistor R limiug copmitur C terhubung pada pin nomor 5 dan 6. Nilai frekuensi osilasi ( tb ) serta hubungan

dengan nilai kapasitor dan hambatan dapat dituliskan dengan rumus ·

./U

1rrRC

Dimana •

fo = frekuensi osilator (Hz)

C

=

kapasitor yang terhubung pada pin:\ dan 6 (FJR ""'· hambatan yang terhubung pada pin 7 dan ground (Ohm)

Untuk mcndapatkan th:kucnsi kduaran HエセャI@ mabmllllll セエZ「セZウ。イ@ 10 KrlL 111aka

I --,: ; セ@ ' セ@ 1 .. , I l ' 'I

Modulasi kode-pulsa U'ulse ('ode Modukmon) digunakan untuk mengubab 1syarat analog menjadi hentuk digital Dalam sistem PCM, ke!ompok-ke!ompok pu!sa atau

kode yang dipancarkan merepresentasikan angka-angka

dengan tingkat-tingkat tegangan modulasi

.., . f)e/ta Afodululwtt (DM)

biner yang bersesuaian

uemodulator harus muk arau turun tergantung dari isyarat digital hasil Modulasi Delta

Pada PCN1, isyarat analog dicuplik pada i!lletTal yang reguler, clan amplitudo dari isyarat dikodekan menjadi dalam bentuk bit. Variasi dari teknik sejenis PCM adalah Modulasi

Delta V(l!l!l rnemhandlnukan isvarat analou dan Xli<H'\\'/l'C' isvarat hasil nt.!!ilul /1!

Analog Com·erler (DAC) dan mentransmisikannya dengan l bit saja Sistem modulas1 digital menggunakan teknik Modulasi Delta mempunyai dua bagian dasar, yaitu

bagian modulator dan demodulator. Pada tulisan ini akau uibahas tentang 1\lodulatm

Delta yang dipancarkan secara FM

2. Modulator Delta

Bagian modulator ini terdiri dari beberapa untai sebagai berikut •

Untai Pembanding

- Untai Encoder

- Untai Digital to Analog Converter (DAC)

Untai Generator Pulsa (Clock)

- t

fntai Osilator Isyarat lnf(mnasiBagan Modulator Delta ditunjukkan pada Gambar 1.

;/

/

ClOCK

[image:3.1054.38.480.75.610.2]l -... I l \ 1 I\.\ t t

Gambar ! . Modulator Delta

2.1.

llntai Osilator lsyarat lnformasi

I

HOJ)l.i/,A.\1/JI:I lA

Uudilwrdtu A fllr!WIIhl

\ , \()

..

I \'lecJ•,,, '1•

Us!l,uu, J.:> yarat mtor mas I dli セ、mァ\QQ@ 1uasukau t::.y a1 al uJJ u1 DH1Sl <tkdli

menghasilkan isyarat sinus yang merupakan isyarat yang akan dimodulasi menjadi data

biner pada proses tnmsmisi 、ゥセゥエ。ャ@ lTnt<'li osil<'ltor ini mempunv<1i jangkauan frekuenc;i

keluaran dari 0 sampa1 I 0 kHz dengan menggunakan IC XR2206 yang difungsikan

sebagai penghasil isyarat sinus. VCO merupakan osilator terkendali tegangan, pada IC

XR1206 tegangan yang merupakan pengendali osilator pada blok VCO dihasilkan o!eh

arus pada blok nlt-rellf .\11'ifches sedangkan hambatannya yaitu 1imi11g rnistor R

terhubung pad a pin nomor 7. Sedangkan nilai frekuensi osilasi ( fo ) ditentukan olell

komponen luar yaitu tinnng cupositor C dan timing resistor R limiug copmitur C terhubung pada pin nomor 5 dan 6. Nilai frekuensi osilasi ( tb ) serta hubungan

dengan nilai kapasitor dan hambatan dapat dituliskan dengan rumus ·

./U

1rrRC

Dimana •

fo = frekuensi osilator (Hz)

C

=

kapasitor yang terhubung pada pin:\ dan 6 (FJR ""'· hambatan yang terhubung pada pin 7 dan ground (Ohm)

Untuk mcndapatkan th:kucnsi kduaran HエセャI@ mabmllllll セエZ「セZウ。イ@ 10 KrlL 111aka

rcchnc Jurnalllmwh LkhtrurckrJikd \\11 I \1 .',p I ,\pill·-'' i I t l.tl I . . .

nilai tahanan minimum R

=

1590 0 Sedangkan VR=

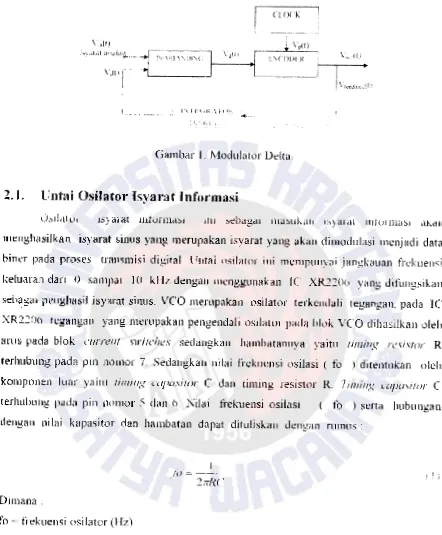

50 K terhubung pada pin 3 yang pada diagram hlok terhuhung ke sebuah blok penguat di!2.unakan untuk mengatur amplituda dari isvarat sinus yang dihasilkan. Amplituda maksimum yang dihasilkan sebesar 6 Vpp dihasilkan dari pembagian tegangan sumber (Vee) dengan dua buah hamhatan .;; I I< rbn VH - .;n K 11ntai ョウゥャ\セエョイ@ iw<1rat infnrmasi ditunjukkiln padaセ@ Jdllllldl

-1/1:

[image:4.1051.51.457.214.495.2]T

Gambar 2 Osilator lsyarat Informasi

2.2.

lJ

ntai

Offset

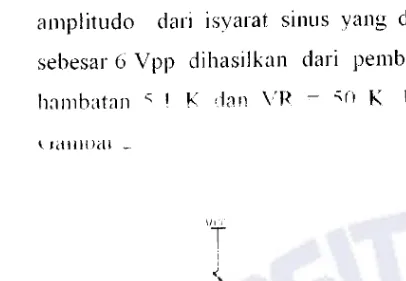

DCUntai ini berguna untuk memberikan tegangan DC pada isyarat informasi agar aras teg:mg:111 DC ー\セ、。@ isyarat informasi s<1ma clengan aras tegangan DC pada isyarat

s<11llpling kr kuantisasi sehmgga kedua 1syarat clapat dibandingkan oleh untni pemllilnding Untai ini direalisasikan sebagai penguat penjumlah tidak membalik

(uon-'"''crtillg) dengan komponen aktif IC Op-Amp LF.3)b Unta1 tersebut ditunjukkan

R1

V1n MセG|O|O|LMMMMMML@

! F ''lEi

::>UK

_l_

Gambar 3. lTntai HセェヲN|・エ@ DC

1 , out= (. I+-·-. + Rl) ( R1 J . de+ R2 J"in \

I

R1 HI+ 1<2 Rl

+

R2 ;2.3.

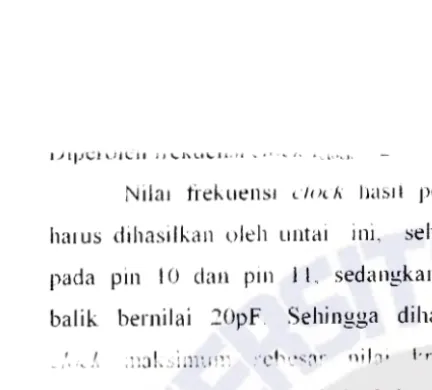

llntai Generator Pulsa

.\/OJ>ULt.\'1 DELT 4 HudilwrdJa Mnrttmlfo

(::

)Untai generator pulsa akan menghastlkan keluaran berupa isyarat clock yang berfimgsi sebagai isyarat peneuplik pada untai encoder dan sebagai clock untuk

up dmm co11nter pada untai staircuse generator. Untai ini direalisasikan menggunakan IC CD4060 Untuk menentukan nilai komponen pasif tersebut maka terlebih dahulu menghitung nilai frekuensi clock yang akan digunakan. Isyarat informasi berupa isvarat sinus rnempun'_,·ai frekuens'i nlaks'I.IllLIIll 4l,·Hz dar1 _ , illllj) rtu 1· d o maksimum SVpp Jumlah bit vang digunakan pada untai sltlltntsc gcncrmur adalah 4 maka nilai tegangan sh'JJ st::c' sesuai denga 11 pcrsamaart bcri ku t

I ; ' • !

rcchnc Jurnalllmwh LkhtrurckrJikd \\11 I \1 .',p I ,\pill·-'' i I t l.tl I . . .

nilai tahanan minimum R

=

1590 0 Sedangkan VR=

50 K terhubung pada pin 3 yang pada diagram hlok terhuhung ke sebuah blok penguat di!2.unakan untuk mengatur amplituda dari isvarat sinus yang dihasilkan. Amplituda maksimum yang dihasilkan sebesar 6 Vpp dihasilkan dari pembagian tegangan sumber (Vee) dengan dua buah hamhatan .;; I I< rbn VH - .;n K 11ntai ョウゥャ\セエョイ@ iw<1rat infnrmasi ditunjukkiln padaセ@ Jdllllldl

-1/1:

[image:5.1051.40.475.65.631.2]T

Gambar 2 Osilator lsyarat Informasi

2.2.

lJ

ntai

Offset

DCUntai ini berguna untuk memberikan tegangan DC pada isyarat informasi agar aras teg:mg:111 DC ー\セ、。@ isyarat informasi s<1ma clengan aras tegangan DC pada isyarat

s<11llpling kr kuantisasi sehmgga kedua 1syarat clapat dibandingkan oleh untni pemllilnding Untai ini direalisasikan sebagai penguat penjumlah tidak membalik

(uon-'"''crtillg) dengan komponen aktif IC Op-Amp LF.3)b Unta1 tersebut ditunjukkan

R1

V1n MセG|O|O|LMMMMMML@

! F ''lEi

::>UK

_l_

Gambar 3. lTntai HセェヲN|・エ@ DC

1 , out= (. I+-·-. + Rl) ( R1 J . de+ R2 J"in \

I

R1 HI+ 1<2 Rl

+

R2 ;2.3.

llntai Generator Pulsa

.\/OJ>ULt.\'1 DELT 4 HudilwrdJa Mnrttmlfo

(::

)Untai generator pulsa akan menghastlkan keluaran berupa isyarat clock yang berfimgsi sebagai isyarat peneuplik pada untai encoder dan sebagai clock untuk

up dmm co11nter pada untai staircuse generator. Untai ini direalisasikan menggunakan IC CD4060 Untuk menentukan nilai komponen pasif tersebut maka terlebih dahulu menghitung nilai frekuensi clock yang akan digunakan. Isyarat informasi berupa isvarat sinus rnempun'_,·ai frekuens'i nlaks'I.IllLIIll 4l,·Hz dar1 _ , illllj) rtu 1· d o maksimum SVpp Jumlah bit vang digunakan pada untai sltlltntsc gcncrmur adalah 4 maka nilai tegangan sh'JJ st::c' sesuai denga 11 pcrsamaart bcri ku t

I ; ' • !

t」」ィョセ@ Junnlllnuah eィZォャャッィZャ|ャャャセ。@ \iol 1•1 i'<u :\pnl ..:l•l 1 ii.u ' ',-,

Sedangkan nilai frek:uensi clock maksimum yang dibutuhkan sesuai dengan persamaan

berikut ·

hmus chhasllkan oleh untai 1111. sehingga digunakan k11stal 7 "'MFiz yang tt:rhubun:::;

pada p111 I 0 clan pm II .. sedangkan 2 buah kapasitoi sebagai perbandingan umpan

batik bernilai 20pF. Sehingga diharapkan untai ini akan rnenghasilkan frekuensi

percobaan deng,Rn mengubah frekuensi clock ini maka lC CD4060 juga berfungs1 sebagai pembagi frekuensi clock. Nilai frekuensi clock yang bisa dibagi menurut

persama<m sebagm berikut

LOセ@ 'Li 't •f..:_

( I

2"

Dim<llla ·

cセNLャM = frekuensi dock yang dihasilkan kristal 7,21-.fHz

n

=

pembag1 ke-n ( pembagi ke-n).lJOJ>L.LtSi IJIJ 1.-i /)11(/ilwrd;o 'lllntmtlu

セM iffiTO . セMᆳ

: :F'!K!'l ... ]セMMMNL⦅@ Mセ@

セ\OカGMMMMQ@

_L.,

cJ _LC.T'''"•

r.I.;;

r; [image:6.1054.53.485.211.600.2]_l_''"' I> _ , , , , ,

... .,..,..

Gambar 4. Untai Generator Pulsa

DengaH \

'-'-nilai puncak sebesar IOV pula. Agar keluaran clock sesuai dengan aras TTL yaitu 5V maka pad<l masing-masing pin dihubungkfln ke nntm pembag1 tegangan

2.4.

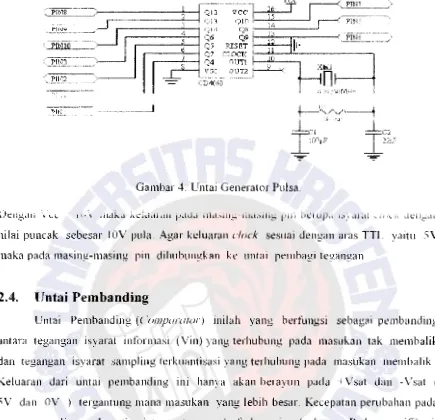

Untai Pembanding

Untai Pembanding ( Cumpwwor) inilah yang berfungsi sebagai pt:mbanding

antara tegangan isyarat informasi (Vin) yang terhubung pada masukan tak membalik

dan tegangan isyarat sampling terkuantisasi yang terhubung pada masukan membalik

Keluaran dari untai pembanding ini hanya akan berayun pada Vsat dan -Vsat ( 5V dan OV ) tergantung mana masukan yang lebih besar. Kecepatan perubahan pada isyarat sampling terkuantisasi tergantung pada tl·ekuensi c/uc/mya. Pada spesifikas1.

setelah melalu1 perhitungan frekuensi maksimum isyarat infonnasi -+kHz

dengan tegangau puncak 5V didapatkan t'h;kuensi clock \ang uibutuhkan 111111tmum sebesar 2fN,60kHz. Sehingga periode isyarat sampling terkuantisas1 maksimum sebesar

T .clock ]セ@ (I 209600) 4, 77 detik. Sehingga dari dasar perhitungan tersebut dapat menjadi acuan untuk memilih tipe Op-Amp yang mendukung spesifikasi dari sistem

modulasi delta Oleh karena keluaran yang diharapkan mempunvai nilai +Vsat

=

.:;y dan Vsat = OV maka tlpe Op-Amp yang dipilih harus mempunyai s/eH' raiL' atau laju lentingan minimum sebesar •t」」ィョセ@ Junnlllnuah eィZォャャッィZャ|ャャャセ。@ \iol 1•1 i'<u :\pnl ..:l•l 1 ii.u ' ',-,

Sedangkan nilai frek:uensi clock maksimum yang dibutuhkan sesuai dengan persamaan

berikut ·

hmus chhasllkan oleh untai 1111. sehingga digunakan k11stal 7 "'MFiz yang tt:rhubun:::;

pada p111 I 0 clan pm II .. sedangkan 2 buah kapasitoi sebagai perbandingan umpan

batik bernilai 20pF. Sehingga diharapkan untai ini akan rnenghasilkan frekuensi

percobaan deng,Rn mengubah frekuensi clock ini maka lC CD4060 juga berfungs1 sebagai pembagi frekuensi clock. Nilai frekuensi clock yang bisa dibagi menurut

persama<m sebagm berikut

LOセ@ 'Li 't •f..:_

( I

2"

Dim<llla ·

cセNLャM = frekuensi dock yang dihasilkan kristal 7,21-.fHz

n

=

pembag1 ke-n ( pembagi ke-n).lJOJ>L.LtSi IJIJ 1.-i /)11(/ilwrd;o 'lllntmtlu

セM iffiTO . セMᆳ

: :F'!K!'l ... ]セMMMNL⦅@ Mセ@

セ\OカGMMMMQ@

_L.,

cJ _LC.T'''"•

r.I.;;

r; [image:7.1054.41.476.78.498.2]_l_''"' I> _ , , , , ,

... .,..,..

Gambar 4. Untai Generator Pulsa

DengaH \

'-'-nilai puncak sebesar IOV pula. Agar keluaran clock sesuai dengan aras TTL yaitu 5V maka pad<l masing-masing pin dihubungkfln ke nntm pembag1 tegangan

2.4.

Untai Pembanding

Untai Pembanding ( Cumpwwor) inilah yang berfungsi sebagai pt:mbanding

antara tegangan isyarat informasi (Vin) yang terhubung pada masukan tak membalik

dan tegangan isyarat sampling terkuantisasi yang terhubung pada masukan membalik

Keluaran dari untai pembanding ini hanya akan berayun pada Vsat dan -Vsat ( 5V dan OV ) tergantung mana masukan yang lebih besar. Kecepatan perubahan pada isyarat sampling terkuantisasi tergantung pada tl·ekuensi c/uc/mya. Pada spesifikas1.

setelah melalu1 perhitungan frekuensi maksimum isyarat infonnasi -+kHz

dengan tegangau puncak 5V didapatkan t'h;kuensi clock \ang uibutuhkan 111111tmum sebesar 2fN,60kHz. Sehingga periode isyarat sampling terkuantisas1 maksimum sebesar

T .clock ]セ@ (I 209600) 4, 77 detik. Sehingga dari dasar perhitungan tersebut dapat menjadi acuan untuk memilih tipe Op-Amp yang mendukung spesifikasi dari sistem

modulasi delta Oleh karena keluaran yang diharapkan mempunvai nilai +Vsat

=

.:;y dan Vsat = OV maka tlpe Op-Amp yang dipilih harus mempunyai s/eH' raiL' atau laju lentingan minimum sebesar •I 81 'out( max)

s ewrate = - - - = 51' 1/ , /liS

81 4,77us

Untai pembanding ditunjukkan pada Gambar 5 berikut.

\.lCC

[image:8.1054.54.486.78.618.2]T

Gambar S. Untai Pembanding

2.5.

lfntai Encode•·

Untai Encoder 1m merupakan untai D-Fiipflop yang direalisasikan menggunakan

rc

74LS74, mempunyai satu masukan (D) dan satu keluaran (Q). UntaiEncoder dengan IC 74LS74 yang ditunjukkan pada Gambar 6

1

Gambar C). Untai Encoder

IC tersebut mempunyai tabel fungsi sebagai herikut ·

Tahel l Tabel Fu dari JC 741 S74

KlLl. \It\\

I'R CLR CLK () i)'

I! ll II II L

.\101JtJA.'il スjO[Qセ@ I A lllltlllwrdtu i\ lllrltafllu

Dari Tabel I dapat diiihat cara kerja D-t1iptlop vaitu nilai biner suatu masukan

(D) hasil perbandingan antara isyarat infnrmast dan isyarat sampling terkuantisasi akan

dikelwukan (()} apabila mendapat cluck Dengan memasukkan keluaran hasil

pcll.ktlldlllgcw .till<ua b)dlal llllOillld::,l \ \UIJ dan ISyatal ::><HtlplliJg lclkuantl::.d::.l i.e

dalam untai pencuplik maka keluaran modulasi akan mengisyaratkan nilai biner untuk

setiap clock ( keluaran abn sinkron dengan clock)

2.6. {Jntai Staircase Gene .. ator

Untai ,\'twrcasc c;enerator tnt tersusun atas 2 bagian yaitu up-doH'/1 cmmta

4 bit yang masukannya adalah hasil modulasi delta ( keluaran D-tliptlop) dan

Binm:1· We1g!Jred Resi.Hor (BWR) sebagai DAC. Keluaran dari untai pencuplik akan

dihubungkan pada up-dmm L'0/111/cr 4 bit, yang akan menentukan apakah penghituug akan naik (up) atau turun (down) Untuk menghasilkan unit ramp maka data biner

paralel 4 hit tadi dihubungkan ke sebuah DAC dengnn teknik Rmw:r f,fle1ghted Re\i'itnr

< 'onn;Ner rBHR C 'n11rcrten Cntai .\tu1rcmc ( icncrulur pada Gambar 7 mempuma1

keluaran sebagm berikut

I . 0 1 / f = - · · 1 4 + - '1.'+ 1<41'1 1?311 .. R'!.f'l. .,.6+ HI l't.7 · p ( )

R5 R5 RS RS

I 81 'out( max)

s ewrate = - - - = 51' 1/ , /liS

81 4,77us

Untai pembanding ditunjukkan pada Gambar 5 berikut.

\.lCC

T

Gambar S. Untai Pembanding

2.5.

lfntai Encode•·

Untai Encoder 1m merupakan untai D-Fiipflop yang direalisasikan menggunakan

rc

74LS74, mempunyai satu masukan (D) dan satu keluaran (Q). UntaiEncoder dengan IC 74LS74 yang ditunjukkan pada Gambar 6

1

Gambar C). Untai Encoder

IC tersebut mempunyai tabel fungsi sebagai herikut ·

Tahel l Tabel Fu dari JC 741 S74

KlLl. \It\\

I'R CLR CLK () i)'

I! ll II II L

.\101JtJA.'il スjO[Qセ@ I A lllltlllwrdtu i\ lllrltafllu

Dari Tabel I dapat diiihat cara kerja D-t1iptlop vaitu nilai biner suatu masukan

(D) hasil perbandingan antara isyarat infnrmast dan isyarat sampling terkuantisasi akan

dikelwukan (()} apabila mendapat cluck Dengan memasukkan keluaran hasil

pcll.ktlldlllgcw .till<ua b)dlal llllOillld::,l \ \UIJ dan ISyatal ::><HtlplliJg lclkuantl::.d::.l i.e

dalam untai pencuplik maka keluaran modulasi akan mengisyaratkan nilai biner untuk

setiap clock ( keluaran abn sinkron dengan clock)

2.6. {Jntai Staircase Gene .. ator

Untai ,\'twrcasc c;enerator tnt tersusun atas 2 bagian yaitu up-doH'/1 cmmta

4 bit yang masukannya adalah hasil modulasi delta ( keluaran D-tliptlop) dan

Binm:1· We1g!Jred Resi.Hor (BWR) sebagai DAC. Keluaran dari untai pencuplik akan

dihubungkan pada up-dmm L'0/111/cr 4 bit, yang akan menentukan apakah penghituug akan naik (up) atau turun (down) Untuk menghasilkan unit ramp maka data biner

paralel 4 hit tadi dihubungkan ke sebuah DAC dengnn teknik Rmw:r f,fle1ghted Re\i'itnr

< 'onn;Ner rBHR C 'n11rcrten Cntai .\tu1rcmc ( icncrulur pada Gambar 7 mempuma1

keluaran sebagm berikut

I . 0 1 / f = - · · 1 4 + - '1.'+ 1<41'1 1?311 .. R'!.f'l. .,.6+ HI l't.7 · p ( )

R5 R5 RS RS

セMMMMMMBGaBLMMセMM

(iambar 7 I Intai Staircase Generator

3.

lJntai 1\fodulator FSK

Modulatur FSK mengubah isyarat digital keluaran Modul<ltor Delta yang menjadi

isyarat analog sebagai masukan untai pemancar FM. Untuk isyarat digital basil modulasi

Delta dengan nilai lu).;h akan direpresentasikan menjadi isyarat sinus dengan frekuensi

fl dan isyarat digital hasil modulasi Delta dengan nilai loll' akan direpresentasikan

menjadi isyarat smus dengan frekuensi Modulas1 FSK 1111 direalisasikan

menggunakan /(' Afonolithic Fu11c1ion (ieneralor yaitu XR2206. IC XR2206 terdiri dari empat blok yang menyusunnya yaitu

r

rA!oge ( 'oll!rul Uvci/la!fW (VCO), saklar arus ( ( 'urre/11 Switches), pengali analog dan pembentuk sums dan sebuahpenyangga ( hufleo Blok VCO akan mendapat catu arus dari hlok saklar arus, jika arus berubah maka frekuensi _1uga \Zセォ。ョ@ berubah Besarnya arus ditentukan dengan

hambatan Rl pada pin 7 untuk masukan /11gh dan R2 pada pin 8 untuk masukan

low. Nilai frekuensi fl dan f2 ditentukan oleh nilai hambatan R l dan R2 se1ta nil at

kapasitor C yang terhubung pin 5 dan 6 Berikut persamaan untuk mendapatkan nilai

trekuensi fl tJan f2 ·

fl I , MMセ@ !

1n.RIC

l (}

Pada rancangan ini ditentukan nihti fl

i\JiJIJl:/.A,\1 IJt.LI..J NndilwrdJu A4urtwllf<l

1 I KHz dan f2 = l) KHz ser1a ( · i 0 nF

maka akan diperoleh nila Rl = 1447,6

.n

dan R2 1770.n

Masukan modulator FSK4.

ᄋjZセᄋZ@ セセMiセイNイMMMMQᄋ@

.. )_

-11')-J..t"

=:1/

Rl46'liS

::or·:

-'-<H. WAV:i.

WAVl ow

sセc@

EllA$

FSK

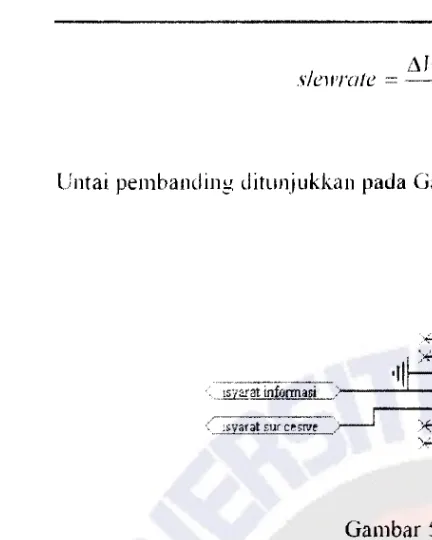

trntai Pemancar Fl\'1

(FrequellC.J' jセャッᆪOオャ。エゥッョI@Agar dapat dipancarkan melalw 11dara maka isyarat tennodulast FSK harus

cliubah menjadi gelombang Radio Frequency (RF) yang dalam hal im menggunakan

pemancar Fl\1 ) ang ャセイ、ゥイゥ@ dari 2 bagian yaitu l!XCIIL'I' FlVl dan l<adw

r

Fetjl!l.!/11.:1' Amplifier {RFA) Berikut diagram blok dari pemancar FM •セMMMMMMBGaBLMMセMM

(iambar 7 I Intai Staircase Generator

3.

lJntai 1\fodulator FSK

Modulatur FSK mengubah isyarat digital keluaran Modul<ltor Delta yang menjadi

isyarat analog sebagai masukan untai pemancar FM. Untuk isyarat digital basil modulasi

Delta dengan nilai lu).;h akan direpresentasikan menjadi isyarat sinus dengan frekuensi

fl dan isyarat digital hasil modulasi Delta dengan nilai loll' akan direpresentasikan

menjadi isyarat smus dengan frekuensi Modulas1 FSK 1111 direalisasikan

menggunakan /(' Afonolithic Fu11c1ion (ieneralor yaitu XR2206. IC XR2206 terdiri dari empat blok yang menyusunnya yaitu

r

rA!oge ( 'oll!rul Uvci/la!fW (VCO), saklar arus ( ( 'urre/11 Switches), pengali analog dan pembentuk sums dan sebuahpenyangga ( hufleo Blok VCO akan mendapat catu arus dari hlok saklar arus, jika arus berubah maka frekuensi _1uga \Zセォ。ョ@ berubah Besarnya arus ditentukan dengan

hambatan Rl pada pin 7 untuk masukan /11gh dan R2 pada pin 8 untuk masukan

low. Nilai frekuensi fl dan f2 ditentukan oleh nilai hambatan R l dan R2 se1ta nil at

kapasitor C yang terhubung pin 5 dan 6 Berikut persamaan untuk mendapatkan nilai

trekuensi fl tJan f2 ·

fl I , MMセ@ !

1n.RIC

l (}

Pada rancangan ini ditentukan nihti fl

i\JiJIJl:/.A,\1 IJt.LI..J NndilwrdJu A4urtwllf<l

1 I KHz dan f2 = l) KHz ser1a ( · i 0 nF

maka akan diperoleh nila Rl = 1447,6

.n

dan R2 1770.n

Masukan modulator FSK4.

ᄋjZセᄋZ@ セセMiセイNイMMMMQᄋ@

.. )_

-11')-J..t"

=:1/

Rl46'liS

::or·:

-'-<H. WAV:i.

WAVl ow

sセc@

EllA$

FSK

trntai Pemancar Fl\'1

(FrequellC.J' jセャッᆪOオャ。エゥッョI@Agar dapat dipancarkan melalw 11dara maka isyarat tennodulast FSK harus

cliubah menjadi gelombang Radio Frequency (RF) yang dalam hal im menggunakan

pemancar Fl\1 ) ang ャセイ、ゥイゥ@ dari 2 bagian yaitu l!XCIIL'I' FlVl dan l<adw

r

Fetjl!l.!/11.:1' Amplifier {RFA) Berikut diagram blok dari pemancar FM •I .:elm-.: Jmnallln11ah l•.kktrolekntka Vc•l 1' 1 i'<l) 1 \pnl _:(II I lldi i 1 ;,

' . -.. -·---.. -.. --... ---... -.. --- ---. -... セMM ---. -- - - --- ---セ@ --Mセ@

'

PENGL1AT OA\'A IU CIUT

lBOOSTflll!) ·-.- ..

Ciambar () Bagan Kotak Pemancar FT\f

Pada untai pemancar FM ini frekuensi kerjanya ditentukan oleh rangkaian tala

(induktor dan kapasitor) dalam lintasan umpan balik. Semua jenis osilator membutuhkan

dari pembebanan Pada perancangan ini penyangga adalah penguat kelas A dengan

kontigurasi tnmsistor conunon em iter menggunakan transistor C90 18. Osilator yang

dilengkapi dengan penyangga biasanya disebut sebagai cxctler (Gambar l 0.) ya11g sudah

bisa dipakai sebagai pemancar FM dengan daya yang masih lemah sekitar 1 mW.

_: HF _l!.I__ .---.!..f

....

.._:or

r

Mセ@ セMM\NB@ JFrerr--"

セjif@

[image:12.1051.49.474.240.641.2]r_r

J;

J'"

Gambar 10. Exciter FM.

"

Untuk mendapatkan day a yang Iebih besar dibutuhkan penguat day a

エィセォオ・ョウゥ@ radio N.udto Fn)LJIIL'I!cl· ,lll/fJitfh:r (RFA.l Dalam lwl ini RFA menggunakan

modul Pt>nnnc:1r !'vlini fセQ@ RR-1 ORl'vlH7 huatan RONlCA SC-I 07

12

5.

Pengukuran dan AnaJisa

Pengukman yang Jilakukan pada rancangan llll yaitu.

Isyarat informasi

/HOJJ£;/.A.\1 J;EL I A 811dihanftu ,\/uri wt lfu

1 Isyarat keluaran basil modulasi Hュッ、オャ\セウゥ@ delta, modulasi FSK modulasi .FM)

l Isyarat Silmpling terkuantis<1si pad<1 modulator

'-e(JangJ<.all pengukurannya mellputt parameter-para111ete1 setmga1 i)e!Ikut

Amplituda dan frekuensi dari isyarat informasi

1 frekuensi Pencuplik

QRャゥZjuTRセ@

3. Resolution ( ,\'leJJ .\·izc )

4. Jumlah bit pada DAC

Pada percobaan ini digunakan frekuensi pencuplik sebesar 125 KHz. Isyarat sinus ini

merupakan isyarat masukan dari Modulator Delta yang akan dibandingkan dengan

isyarat sampling terkuantisasi sehingga dari perbandingan tersebut akan clihasilkan

isyarat hasil Modulasi Delta, isyarat sinus yang dibandingkan dengan isyarat sampling

terkuantisasi ditunjukkan pada Gambar 11 lsyarat keluaran hasil Modulasi Delta ini

ditunjukkan pada Gambar 12. Pada gambar hasil percobaan terlihat bahwa isyarat

sampling terkuantisasi cukup baik untuk mengikuti laju perubahan isyarat informasi.

sehingga dihasilkan isyarat hasilmodulasi Delta yang sesuai dengan teori yaitu pada saat

isyarat sinus naik maka isyarat keluaran modulasi berupa isyarat digital dimana isyarat

digital bernilai high lebih banyak daripada isyarat digital bernilai low , sedangkan

pada saat isyarat sinus turun maka isyarat keluaran modulasi bempa isyarat digital

dimana isyarat digital bernila1 low lebih banyak daripada 1syarat digital bernJl,11

I .:elm-.: Jmnallln11ah l•.kktrolekntka Vc•l 1' 1 i'<l) 1 \pnl _:(II I lldi i 1 ;,

' . -.. -·---.. -.. --... ---... -.. --- ---. -... セMM ---. -- - - --- ---セ@ --Mセ@

'

PENGL1AT OA\'A IU CIUT

lBOOSTflll!) ·-.- ..

Ciambar () Bagan Kotak Pemancar FT\f

Pada untai pemancar FM ini frekuensi kerjanya ditentukan oleh rangkaian tala

(induktor dan kapasitor) dalam lintasan umpan balik. Semua jenis osilator membutuhkan

dari pembebanan Pada perancangan ini penyangga adalah penguat kelas A dengan

kontigurasi tnmsistor conunon em iter menggunakan transistor C90 18. Osilator yang

dilengkapi dengan penyangga biasanya disebut sebagai cxctler (Gambar l 0.) ya11g sudah

bisa dipakai sebagai pemancar FM dengan daya yang masih lemah sekitar 1 mW.

_: HF _l!.I__ .---.!..f

....

.._:or

r

Mセ@ セMM\NB@ JFrerr--"

セjif@

r_r

J;

J'"

Gambar 10. Exciter FM.

"

Untuk mendapatkan day a yang Iebih besar dibutuhkan penguat day a

エィセォオ・ョウゥ@ radio N.udto Fn)LJIIL'I!cl· ,lll/fJitfh:r (RFA.l Dalam lwl ini RFA menggunakan

modul Pt>nnnc:1r !'vlini fセQ@ RR-1 ORl'vlH7 huatan RONlCA SC-I 07

12

5.

Pengukuran dan AnaJisa

Pengukman yang Jilakukan pada rancangan llll yaitu.

Isyarat informasi

/HOJJ£;/.A.\1 J;EL I A 811dihanftu ,\/uri wt lfu

1 Isyarat keluaran basil modulasi Hュッ、オャ\セウゥ@ delta, modulasi FSK modulasi .FM)

l Isyarat Silmpling terkuantis<1si pad<1 modulator

'-e(JangJ<.all pengukurannya mellputt parameter-para111ete1 setmga1 i)e!Ikut

Amplituda dan frekuensi dari isyarat informasi

1 frekuensi Pencuplik

QRャゥZjuTRセ@

3. Resolution ( ,\'leJJ .\·izc )

4. Jumlah bit pada DAC

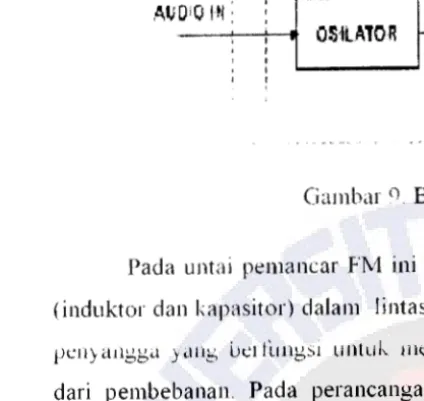

Pada percobaan ini digunakan frekuensi pencuplik sebesar 125 KHz. Isyarat sinus ini

merupakan isyarat masukan dari Modulator Delta yang akan dibandingkan dengan

isyarat sampling terkuantisasi sehingga dari perbandingan tersebut akan clihasilkan

isyarat hasil Modulasi Delta, isyarat sinus yang dibandingkan dengan isyarat sampling

terkuantisasi ditunjukkan pada Gambar 11 lsyarat keluaran hasil Modulasi Delta ini

ditunjukkan pada Gambar 12. Pada gambar hasil percobaan terlihat bahwa isyarat

sampling terkuantisasi cukup baik untuk mengikuti laju perubahan isyarat informasi.

sehingga dihasilkan isyarat hasilmodulasi Delta yang sesuai dengan teori yaitu pada saat

isyarat sinus naik maka isyarat keluaran modulasi berupa isyarat digital dimana isyarat

digital bernilai high lebih banyak daripada isyarat digital bernilai low , sedangkan

pada saat isyarat sinus turun maka isyarat keluaran modulasi bempa isyarat digital

dimana isyarat digital bernila1 low lebih banyak daripada 1syarat digital bernJl,11

「ョセ[@ Jurnallhmuh l:.luklwl ndw ol to u. I , pnl _Ill Hal I - I K

ambar 11. Isyarat Informa i dan Lsyarat

[image:14.1051.12.506.40.634.2]. ampling Terkuanti a i

Gambar 12. lsyarat Informasi dan Isyarat Keluaran ModulasiDelta ..

5.1. Pengaruh erubahan Frekoens1 encuplik

Jika frekuensi pencuplik diubah menjadi 4 KHz akan terjadi slope overload

( Gambar dan Gam bar 1-t)

yair

1 ke daan Ji mana i y rat ウ。ューhョセ@ terk.uantisasitidak dapa1 mengik."Uti laju dari perubahan isyarat sinus.

Sampling Terk.'Uauti asi .

G mbar J 4. Isyarat informa i dan Isyarat

Kel

aran Hastl

Modulasi.5.2. Pengaruh Frekuensi Isyarat Informasi

Fr kue i isyarat informasi diu ah le ih renda ari semula menjadi 500 Hz an

isyarat hasil m dulasi diperlihatkan pada Gambar 15 dan Gambar 16 yang menunj kkan

bahwa isyarat .w.unpling terkuantisasi dapat lebil1 banyak mencuplik isyarat intonnasi. fntuk erubahan frekuen i syarat informasi Lebib tinggi dari semula maka

W lJ£LTl

Httd!lwrdju A fun iallfa

akan mengakibatka n te1jadi slope overloa I seperti tela h ditu njukkan pada Gambar 13 dan

Gam ar 4

Sampling Terkuantisasi . Isyarat Hasil Modulasi .

.3

Penga rnh Resol usi (

Step Size

)

Untuk percobaan dengan me ngubah resolu si rnaka secara otomatis juga akan

mengubah tegangan step si::.e, hal itu dikar nakan tegangan step size merupakan tegangan terkecil dari isyarat intom1asi ケ。ョ セ@ dapat dijangkau oleh Analog to

Digital ( 'mm!rlt!r (ADC). Stairmse Generator diu bah dari proses kuantisasi 4 bit

menjadi 3 bit d n hosilnya ditunj uk.kan pada Ga mbar 17. D ri ha il tersebut dapat ilihat

bah a tegangan ウエ セー@ size pada isyarat cuplik terkuantisasi terlalu besar untuk meo)kuti laju peru ahan amplituda dari · yarat infonnasi. Hal tersebut dinam k n

grmmlur noise.

「ョセ[@ Jurnallhmuh l:.luklwl ndw ol to u. I , pnl _Ill Hal I - I K

ambar 11. Isyarat Informa i dan Lsyarat

[image:15.1051.6.493.120.774.2]. ampling Terkuanti a i

Gambar 12. lsyarat Informasi dan Isyarat Keluaran ModulasiDelta ..

5.1. Pengaruh erubahan Frekoens1 encuplik

Jika frekuensi pencuplik diubah menjadi 4 KHz akan terjadi slope overload

( Gambar dan Gam bar 1-t)

yair

1 ke daan Ji mana i y rat ウ。ューhョセ@ terk.uantisasitidak dapa1 mengik."Uti laju dari perubahan isyarat sinus.

Sampling Terk.'Uauti asi .

G mbar J 4. Isyarat informa i dan Isyarat

Kel

aran Hastl

Modulasi.5.2. Pengaruh Frekuensi Isyarat Informasi

Fr kue i isyarat informasi diu ah le ih renda ari semula menjadi 500 Hz an

isyarat hasil m dulasi diperlihatkan pada Gambar 15 dan Gambar 16 yang menunj kkan

bahwa isyarat .w.unpling terkuantisasi dapat lebil1 banyak mencuplik isyarat intonnasi. fntuk erubahan frekuen i syarat informasi Lebib tinggi dari semula maka

W lJ£LTl

Httd!lwrdju A fun iallfa

akan mengakibatka n te1jadi slope overloa I seperti tela h ditu njukkan pada Gambar 13 dan

Gam ar 4

Sampling Terkuantisasi . Isyarat Hasil Modulasi .

.3

Penga rnh Resol usi (

Step Size

)

Untuk percobaan dengan me ngubah resolu si rnaka secara otomatis juga akan

mengubah tegangan step si::.e, hal itu dikar nakan tegangan step size merupakan tegangan terkecil dari isyarat intom1asi ケ。ョ セ@ dapat dijangkau oleh Analog to

Digital ( 'mm!rlt!r (ADC). Stairmse Generator diu bah dari proses kuantisasi 4 bit

menjadi 3 bit d n hosilnya ditunj uk.kan pada Ga mbar 17. D ri ha il tersebut dapat ilihat

bah a tegangan ウエ セー@ size pada isyarat cuplik terkuantisasi terlalu besar untuk meo)kuti laju peru ahan amplituda dari · yarat infonnasi. Hal tersebut dinam k n

grmmlur noise.

ol. II N nl _ II ! 1 I - I X

a!

r セ@ r

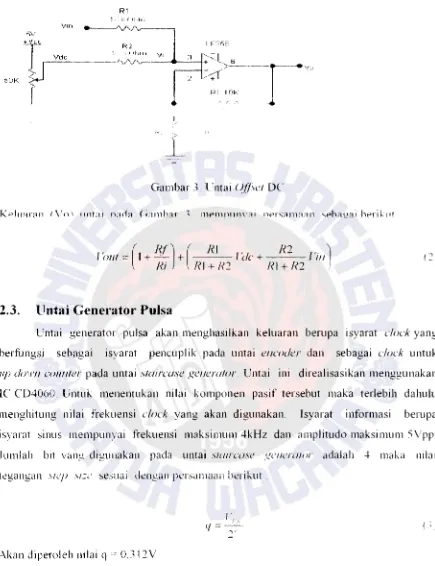

Isyarat analog bem pa si nus yang digunakan untu k mempresentasikan isyarat

pu lsa hasiJ Modulasi Delta digunakan frekuensi 1.1 KHz untuk mempresentasikan pulsa

high

dan.

frek.uensi 9 KHzuntuk

mempresentas·an

pul a low.K

luaranm

dulatorFS

.-pada Gambar J 8 terlihat bahwa .-pada saat isyarat hasil Modulasi Delta bernilai high pada keluarau Modulator FSK dihasilkan isyarat inu dengan frekuens i 11KHz

dan pada saat [image:16.1051.9.498.43.759.2]isyarat pul sa hasil Modulasi Delta bern ila i low pada keluaran Modulator FSK dihasilkan isyarat sinus dengan frekuens· 9KHz

Gambar 18. J;yarat HasiJ Modulasi Delta & Gambar 19 Isyarat Hasil Modulasi FM.

Jsyarat Ha il Mod Jl si FS

16

IOJ>UU. '/ /) LT.

Budtlwrdja Murtit1111a

5.5

Modula tor FM

Hasi modulasi F i itunju ' an

paua

Gam Pada unt i no ul tor FM y· ngte diri dari exciter FM an RFA. isyarat I asil modulasi FSK ditum angkan pada frekuensi pembawa 92 MHz ..

6.

I

e

im

uJ

n

1. Hasil keluaran inte "rator di krit 、・ョセ。ョ@ esaf frekue1 si 1 enct plik l erda rkan

perhitungan dan masukan berup is_yarat di itnl hasil Modulasi De ta cul'"Up untuk dapat mencuplik dan m ngikuti laju dari isyarat informasi .

.., Keluaran basi Modulasi Delta berupa isyarat digital . ang rnempun ai frekuen si

pt.:n k Jar,\11 b ru ah - ubi:l 1 I Jg.mtung Jt n amplltu lu ャsセエャイ ᄋ@ mt 1a , frekuensi isyarat informasi da n isya rat sampling.

Untuk. frekuensi .sampling !ebill keci dari per yaratan minimum akao tetj di

slope orerload yaitu keadaan dtmanc is arat cuplik terkuantisasi tidak dapat mengik""llti laju dari pembahan is arat siJ1us.

4 Pembahnn freh1 nsi isyarat informasi le ih kecil dari akan menghasilkan isy rat

pu lsa hasil Mod lasi Delta dengan nila i frekuensi pensakelaran yang semakin besar.

5. Dengat mengurangi jumlah bit k'Uantisasi pada D (' mak, kan mempengamhi besar tegangan step stze (q) yang merupakan tegangan terkecil dari isya rat informasi yang dapat dijangkau lei Digilul to A11alo ., Cum·erl ,,. (D C) menjadi

sem

kil b sar ehingg akan menimbulkat grun tlur noiseDaftar Pustaka

I. Ha kin, Simon, ") )igital Commtmicalioll" , McGraw-Hill, Series m Electrical Engjneering, 200

., Herbert L Krauss, harle セ ᄋ N@ Bostian. frederick H . Raa , "Teknik Radio

Benda Pad at" .. Jakarta Penerbit Universitas Indonesia. l · 90

:i Rappa o1t The dore. S. "W11· ' l'ss Communi ·ation

Sntem "

_nd Edition. p er addle i er, Prentice-Hall, 1001 .ol. II N nl _ II ! 1 I - I X

a!

r セ@ r

Isyarat analog bem pa si nus yang digunakan untu k mempresentasikan isyarat

pu lsa hasiJ Modulasi Delta digunakan frekuensi 1.1 KHz untuk mempresentasikan pulsa

high

dan.

frek.uensi 9 KHzuntuk

mempresentas·an

pul a low.K

luaranm

dulatorFS

.-pada Gambar J 8 terlihat bahwa .-pada saat isyarat hasil Modulasi Delta bernilai high pada keluarau Modulator FSK dihasilkan isyarat inu dengan frekuens i 11KHz

dan pada saatisyarat pul sa hasil Modulasi Delta bern ila i low pada keluaran Modulator FSK dihasilkan isyarat sinus dengan frekuens· 9KHz

Gambar 18. J;yarat HasiJ Modulasi Delta & Gambar 19 Isyarat Hasil Modulasi FM.

Jsyarat Ha il Mod Jl si FS

16

IOJ>UU. '/ /) LT.

Budtlwrdja Murtit1111a

5.5

Modula tor FM

Hasi modulasi F i itunju ' an

paua

Gam Pada unt i no ul tor FM y· ngte diri dari exciter FM an RFA. isyarat I asil modulasi FSK ditum angkan pada frekuensi pembawa 92 MHz ..

6.

I

e

im

uJ

n

1. Hasil keluaran inte "rator di krit 、・ョセ。ョ@ esaf frekue1 si 1 enct plik l erda rkan

perhitungan dan masukan berup is_yarat di itnl hasil Modulasi De ta cul'"Up untuk dapat mencuplik dan m ngikuti laju dari isyarat informasi .

.., Keluaran basi Modulasi Delta berupa isyarat digital . ang rnempun ai frekuen si

pt.:n k Jar,\11 b ru ah - ubi:l 1 I Jg.mtung Jt n amplltu lu ャsセエャイ ᄋ@ mt 1a , frekuensi isyarat informasi da n isya rat sampling.

Untuk. frekuensi .sampling !ebill keci dari per yaratan minimum akao tetj di

slope orerload yaitu keadaan dtmanc is arat cuplik terkuantisasi tidak dapat mengik""llti laju dari pembahan is arat siJ1us.

4 Pembahnn freh1 nsi isyarat informasi le ih kecil dari akan menghasilkan isy rat

pu lsa hasil Mod lasi Delta dengan nila i frekuensi pensakelaran yang semakin besar.

5. Dengat mengurangi jumlah bit k'Uantisasi pada D (' mak, kan mempengamhi besar tegangan step stze (q) yang merupakan tegangan terkecil dari isya rat informasi yang dapat dijangkau lei Digilul to A11alo ., Cum·erl ,,. (D C) menjadi

sem

kil b sar ehingg akan menimbulkat grun tlur noiseDaftar Pustaka

I. Ha kin, Simon, ") )igital Commtmicalioll" , McGraw-Hill, Series m Electrical Engjneering, 200

., Herbert L Krauss, harle セ ᄋ N@ Bostian. frederick H . Raa , "Teknik Radio

Benda Pad at" .. Jakarta Penerbit Universitas Indonesia. l · 90

:i Rappa o1t The dore. S. "W11· ' l'ss Communi ·ation

Sntem "

_nd Edition. p er addle i er, Prentice-Hall, 1001 . [image:17.1051.5.486.174.784.2]Techne Jurnnlllmiah eエ・ォエイッエセォュォ。@ Vol Ill No i Apnl セQQQ@ 1 Hal 1 . 111

4. Tocci, Ronald J, ''Digital .):vstem, Principle, and Applicatiou" , 5th Edition, Englev,ood Clitl Prentice HalL 1991

5 Tomasi, Wayne, "Advauced Electronic ( 'ommunl(:ation Svstem ·· , 2nd Edition.

Englewood Cliff. Prentice Hall International, I 092.

h Young. P:tul H "/·}cctronic ( 'nmni!I!Jicotinn l'ei'llllilfiW" "'th Edition New

j・イセ・カN@ J'e<HSD!i neliiH;e naH. _uu-;