BAB II

SIMULATOR XILINX PADA

RANGKAIAN DIGITAL SEDERHANA

OBYEKTIF :

- Memahami perangkat lunak Xilinx

- Mampu menggambarkan gerbang digital dasar pada schematic editor - Mampu mensimulasikan gerbang dasar digital

- Mampu menyederhanakan rangkaian digital dan mensimulasikannya

2.1 Disain Rangkaian Digital dengan Xilinx

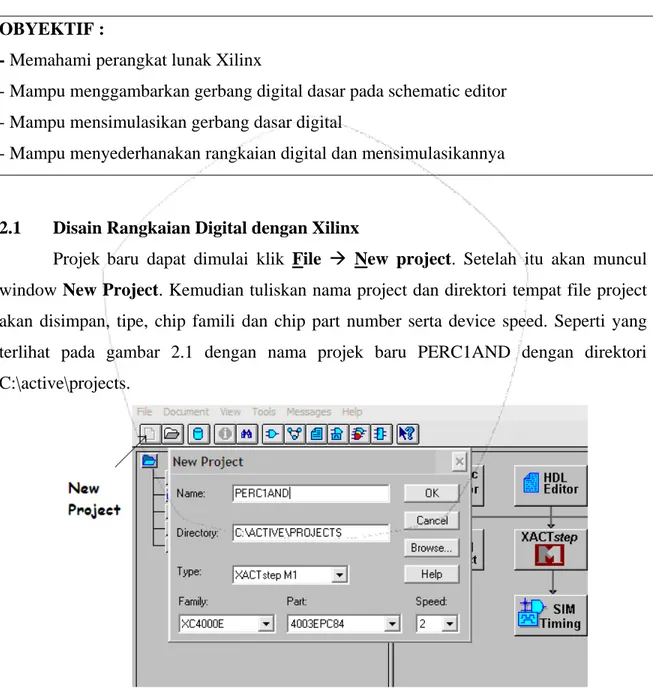

Projek baru dapat dimulai klik File Æ New project. Setelah itu akan muncul window New Project. Kemudian tuliskan nama project dan direktori tempat file project akan disimpan, tipe, chip famili dan chip part number serta device speed. Seperti yang terlihat pada gambar 2.1 dengan nama projek baru PERC1AND dengan direktori C:\active\projects.

Gambar 2.1 : New Project

Membuka window New Project juga dapat dilakukan dengan klik ikon new

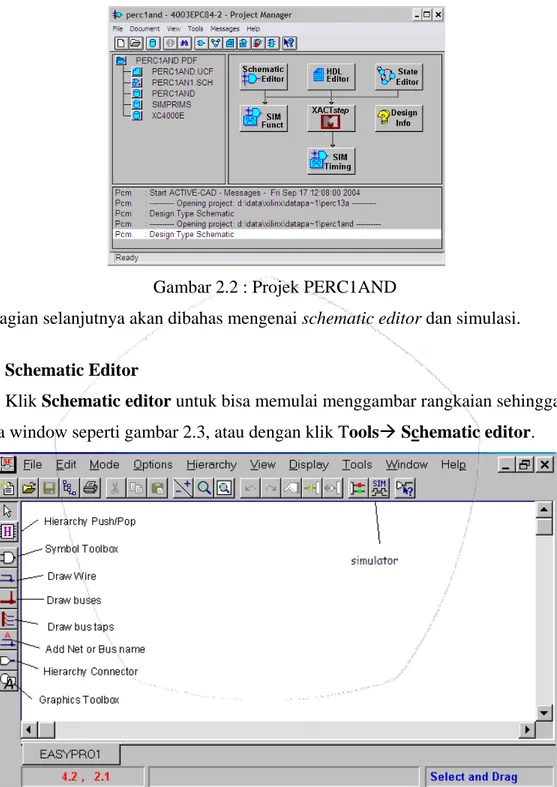

project seperti yang terlihat pada gambar 2.1. Setelah klik OK, tampilan Project Manager akan terlihat seperti pada gambar 2.2.

Gambar 2.2 : Projek PERC1AND

Pada bagian selanjutnya akan dibahas mengenai schematic editor dan simulasi.

2.2 Schematic Editor

Klik Schematic editor untuk bisa memulai menggambar rangkaian sehingga akan

terbuka window seperti gambar 2.3, atau dengan klik ToolsÆ Schematic editor.

Gambar 2.3 : Schematic editor

Pada gambar 2.3 dapat dilihat beberapa ikon disamping sebelah kiri gambar. Untuk mulai menyusun rangkaian kita pilih Mode Æ Symbols atau dengan klik ikon

symbol toolbox, sehingga akan muncul SC Symbols window seperti yang terlihat pada

gambar 2.4. Di dalam SC Symbol window ini kita memilih komponen yang akan kita rangkai.

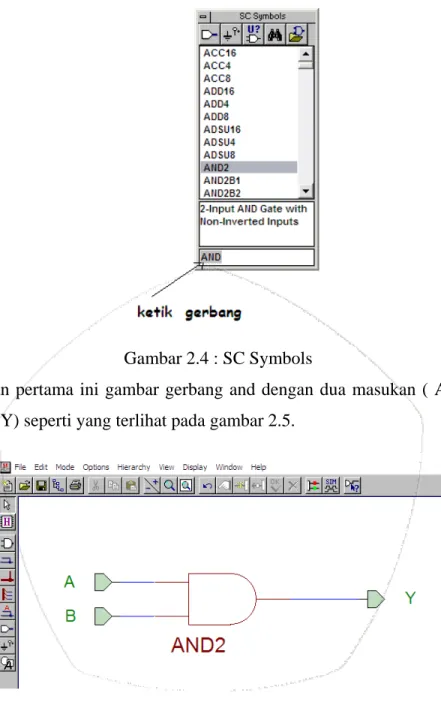

Gambar 2.4 : SC Symbols

Pada percobaan pertama ini gambar gerbang and dengan dua masukan ( A dan B ) dan satu keluaran (Y) seperti yang terlihat pada gambar 2.5.

Gambar 2.5 : Gambar Schematic Editor Gerbang AND

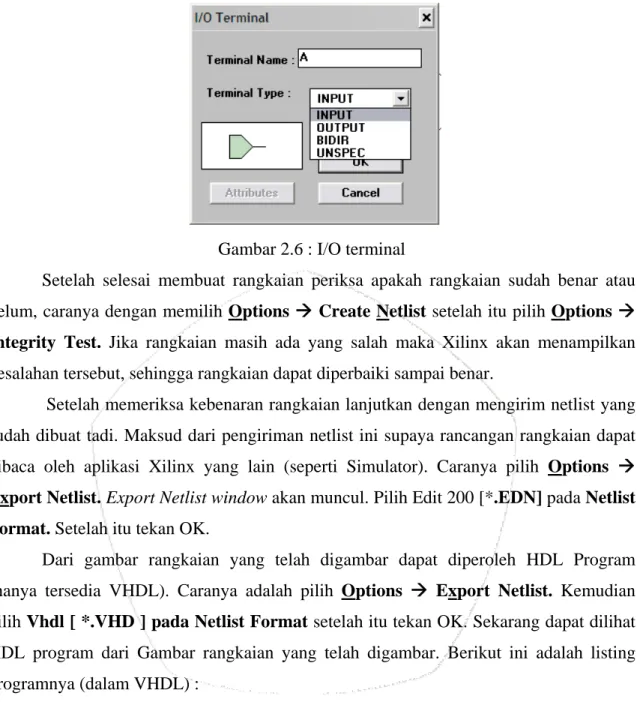

Input dan output (A, B dan Y) digambar dengan klik hierarchy connector atau I/O Terminal kemudian ketik terminal name dan type terminal, seperti yang terlihat pada gambar 2.6. Setelah itu gambar wire dengan klik draw wire. Hubungkan input A dan B serta keluaran Y dengan gerbang AND seperti yang terlihat pada gambar 2.5.

Gambar 2.6 : I/O terminal

Setelah selesai membuat rangkaian periksa apakah rangkaian sudah benar atau belum, caranya dengan memilih Options Æ Create Netlist setelah itu pilih Options Æ

Integrity Test. Jika rangkaian masih ada yang salah maka Xilinx akan menampilkan

kesalahan tersebut, sehingga rangkaian dapat diperbaiki sampai benar.

Setelah memeriksa kebenaran rangkaian lanjutkan dengan mengirim netlist yang sudah dibuat tadi. Maksud dari pengiriman netlist ini supaya rancangan rangkaian dapat dibaca oleh aplikasi Xilinx yang lain (seperti Simulator). Caranya pilih Options Æ

Export Netlist. Export Netlist window akan muncul. Pilih Edit 200 [*.EDN] pada Netlist Format. Setelah itu tekan OK.

Dari gambar rangkaian yang telah digambar dapat diperoleh HDL Program (hanya tersedia VHDL). Caranya adalah pilih Options Æ Export Netlist. Kemudian pilih Vhdl [ *.VHD ] pada Netlist Format setelah itu tekan OK. Sekarang dapat dilihat HDL program dari Gambar rangkaian yang telah digambar. Berikut ini adalah listing programnya (dalam VHDL) :

-- ACTIVE-CAD-2-VHDL, 2.5.4.34, Fri Nov 26 02:34:02 2004

LIBRARY IEEE; USE IEEE.std_logic_1164.all; library x1; use x1.GLOBAL_SIGNALS.all; entity X1 is port ( A : in std_logic; B : in std_logic;

Y : out std_logic ); end X1;

architecture STRUCTURE of X1 is --COMPONENTS

component AND2 port ( I0 : in std_logic; I1 : in std_logic; O : out std_logic ); end component; --SIGNALS begin --SIGNAL ASSIGNMENTS --COMPONENT INSTANCES X36_I1 : AND2 port map(

I0 => B, I1 => A, O => Y ); end STRUCTURE; 2.3 Functional Simulation

Setelah selesai membuat rancangan Schematic sekarang dapat dilihat simulasi Timing Diagram yang dihasilkan oleh rangkaian yang telah dibuat. Caranya adalah meng-klik simulator pada Project Window. Kemudian akan tampak Logic-Simulator Foundation window dan Waveform Viewer Window yang masih kosong. Seperti yang terlihat pada gambar 2.7.

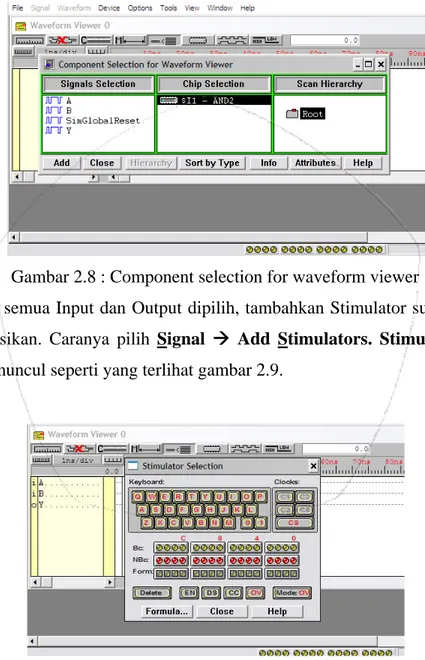

Yang pertama harus lakukan adalah menambahkan input dan output pada Waveform Viewer supaya dapat melakukan simulasi. Caranya adalah pilih Signal Æ Add

Signals. Component Selection for Waveform Viewer window akan muncul seperti yang

terlihat pada gambar 2.8. Kemudian pilihlah Input dan Output yang akan disimulasikan. Setelah selesai pilih Close.

Gambar 2.8 : Component selection for waveform viewer

Setelah semua Input dan Output dipilih, tambahkan Stimulator supaya rangkaian dapat disimulasikan. Caranya pilih Signal Æ Add Stimulators. Stimulator Selection window akan muncul seperti yang terlihat gambar 2.9.

Gambar 2.9 : Stimulator selection

Sekarang rangkaian siap untuk disimulasikan. Untuk itu pilih View Æ Main

Toolbox untuk menampilkan Simulator window. Klik step atau long maka Timing

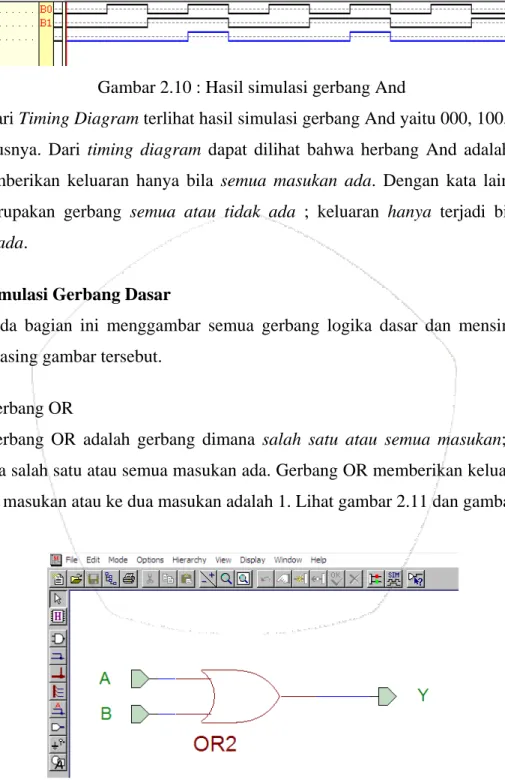

Gambar 2.10 : Hasil simulasi gerbang And

Dari Timing Diagram terlihat hasil simulasi gerbang And yaitu 000, 100, 010, 111 dan seterusnya. Dari timing diagram dapat dilihat bahwa herbang And adalah gerbang yang memberikan keluaran hanya bila semua masukan ada. Dengan kata lain gerbang AND merupakan gerbang semua atau tidak ada ; keluaran hanya terjadi bila semua masukan ada.

2.4 Simulasi Gerbang Dasar

Pada bagian ini menggambar semua gerbang logika dasar dan mensimulasikan masing-masing gambar tersebut.

2.4.1 Gerbang OR

Gerbang OR adalah gerbang dimana salah satu atau semua masukan; keluaran terjadi bila salah satu atau semua masukan ada. Gerbang OR memberikan keluaran 1 bila salah satu masukan atau ke dua masukan adalah 1. Lihat gambar 2.11 dan gambar 2.12.

Gambar 2.12 : Simulasi gerbang OR

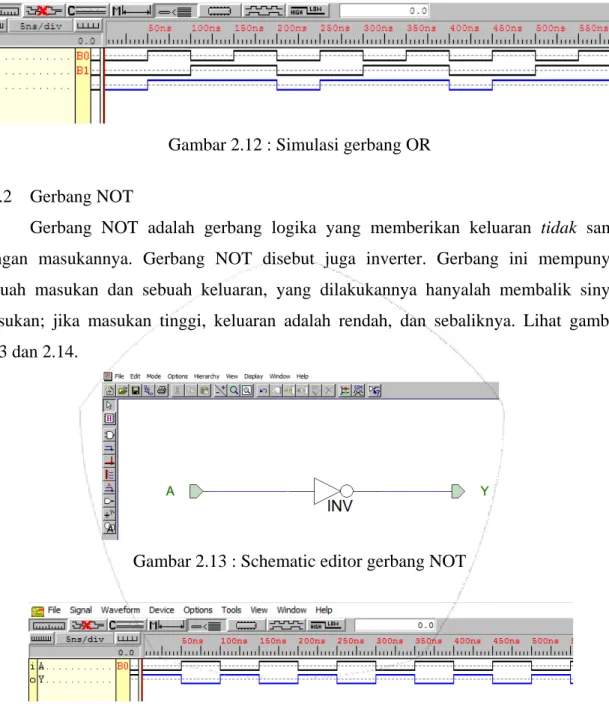

2.4.2 Gerbang NOT

Gerbang NOT adalah gerbang logika yang memberikan keluaran tidak sama dengan masukannya. Gerbang NOT disebut juga inverter. Gerbang ini mempunyai sebuah masukan dan sebuah keluaran, yang dilakukannya hanyalah membalik sinyal masukan; jika masukan tinggi, keluaran adalah rendah, dan sebaliknya. Lihat gambar 2.13 dan 2.14.

Gambar 2.13 : Schematic editor gerbang NOT

Gambar 2.14 : Simulasi gerbang NOT

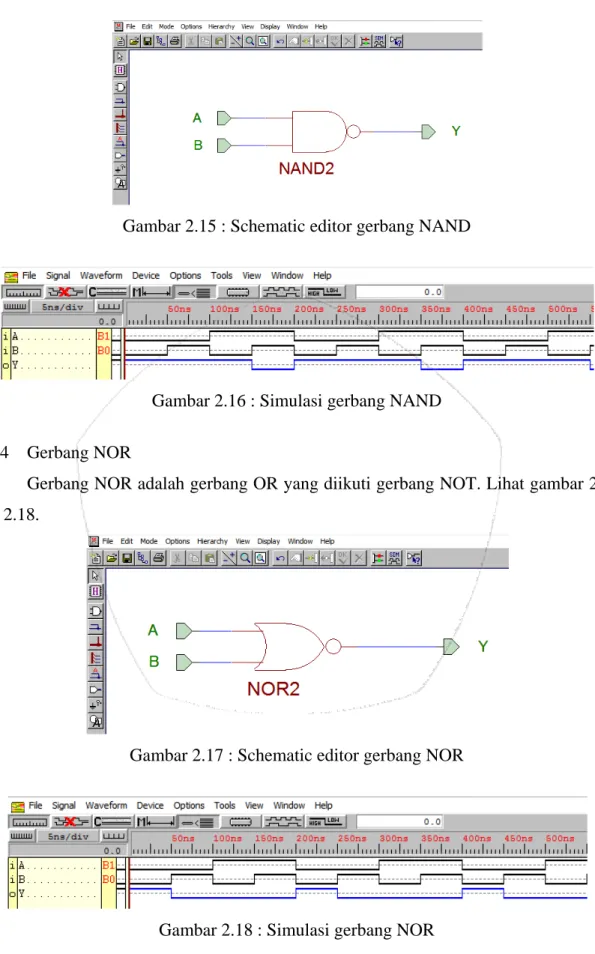

2.4.3 Gerbang NAND (NOT-AND)

Gerbang NAND adalah gerbang AND yang diikuti gerbang NOT dengan simbol seperti pada gambar 2.15 dan simulasi gerbang NAND dapat dilihat pada gambar 2.16.

Gambar 2.15 : Schematic editor gerbang NAND

Gambar 2.16 : Simulasi gerbang NAND

2.4.4 Gerbang NOR

Gerbang NOR adalah gerbang OR yang diikuti gerbang NOT. Lihat gambar 2.17 dan 2.18.

Gambar 2.17 : Schematic editor gerbang NOR

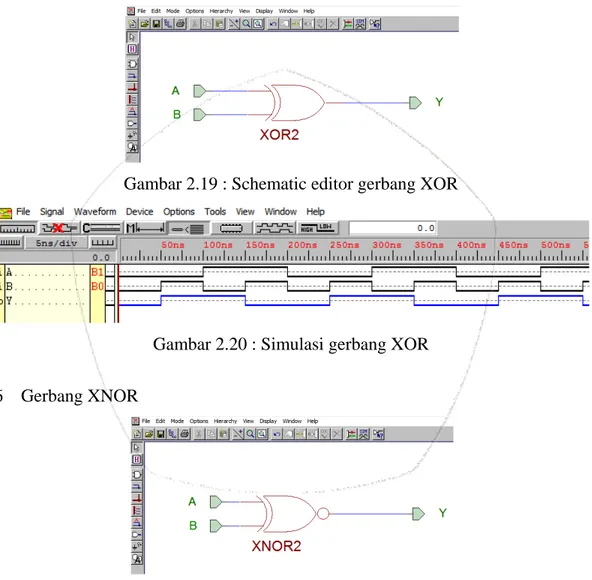

2.4.5 Gerbang XOR

Gerbang ini mempunyai dua masukan dan satu keluaran. XOR adalah nama lain dari Oreksklusif, disebut demikian karena gerbang XOR memberikan keluaran 1 bila masukan pertama atau masukan kedua adalah 1, namun tidak kedua-duanya. Dengan kata lain, gerbang XOR mempunyai keluaran 1 hanya bila ke dua masukannya berbeda dan keluarannya 0 apabila ke dua masukannya sama. Lihat gambar 2.19 dan 2.20.

Gambar 2.19 : Schematic editor gerbang XOR

Gambar 2.20 : Simulasi gerbang XOR 2.4.6 Gerbang XNOR

Gambar 2.21 : Schematic editor gerbang XNOR

2.5 Penyederhanaan Rangkaian

Penyederhanaan rangkaian logika dapat dilakukan dengan beberapa metode seperti metode Peta Karnaugh, metode Maksterm/Minterm, metode Aljabar Boolean dan lain sebagainya. Pada sub bagian ini dengan menggunakan simulator Xilinx dapat di ketahui kebenaren hasil penyederhanaan rangkaian dengan mensimulasikan rangkaian sebelum disederhanakan dan yang setelah disederhanakan, dan kemudian membandingkan apakah timing diagram kedua rangkaian tersebut sama atau tidak.

2.5.1 Menyederhanakan rangkaian Y=ABC+ABC+ABC+ABC:

Untuk menyederhanakan rangkaian Y=ABC+ABC+ABC+ABCdapat dilakukan dengan langkah-langkah sebagai berikut :

Langkah -1 : gambar rangkaian Y=ABC+ABC+ABC+ABC pada schematic editor, seperti yang terlihat pada gambar 2.23.

Gambar 2.23 : schematic editor Y=ABC+ABC+ABC+ABC

Langkah -2 : simulasikan rangkaian Y=ABC+ABC+ABC+ABC, seperti yang terlihat pada gambar 2.24.

Gambar 2.24 : hasil simulasi Y=ABC+ABC+ABC+ABC

Langkah -3 : sederhanakan rangkaian Y=ABC+ABC+ABC+ABC, pada gambar 2.25 penyederhanaan rangkaian menggunakan peta karnaugh.

AB C 00 01 11 10 0 1 0 0 1 1 1 0 0 1

Gambar 2.25 : Peta Karnaugh rangkaian Y=ABC+ABC+ABC+ABC

Langkah -4 : gambar rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.26.

Gambar 2.26 : Schematic editor Y = B

Langkah -5 : simulasikan rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.27.

Gambar 2.27 : simulasi

Langkah -6 : bandingkan hasil simulasi rangkaian sebelum disederhanakan (langkah-2) dengan hasil simulasi rangkaian yang telah disederhanakan (langkah-5).

Dari timing diagram gambar 2.27 sama dengan timing diagram gambar 2.24 sehingga dapat disimpulkan bahwa penyederhanaan rangkaian yang dilakukan benar.

2.5.2 Simulasikan X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD dan sederhanakan persamaan serta buktikan hasil penyederhanaan yang dilakukan benar dengan mensimulasikan hasil penyederhanaan persamaan yang diperoleh!

Langkah 1 :

gambar rangkaian X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD pada schematic editor, seperti yang terlihat pada gambar 2.28.

Langkah -2 : simulasikan rangkaianX=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD, seperti yang terlihat pada gambar 2.29.

Langkah -3 :

sederhanakan rangkaianX=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD , pada gambar 2.30 penyederhanaan rangkaian menggunakan peta karnaugh.

Gambar 2.28 : schematic editor X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

Gambar 2.29 : hasil simulasi X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

AB CD 00 01 11 10 00 0 1 0 1 01 0 1 0 1 11 1 1 0 1 10 0 1 0 1

Gambar 2.30 : Peta Karnaugh

Langkah -4 : gambar rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.31.

Gambar 2.31 : Schematic editor X= A B + A B C + A C D

Langkah -5 : simulasikan rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.32.

Gambar 2.32 : simulasi X= A B + A B C + A C D

Langkah -6 : bandingkan hasil simulasi rangkaian sebelum disederhanakan (langkah-2) dengan hasil simulasi rangkaian yang telah disederhanakan (langkah-5).

Dari timing diagram gambar 2.32 sama dengan timing diagram gambar 2.29 sehingga dapat disimpulkan bahwa penyederhanaan rangkaian yang dilakukan benar.

2.5.3 Simulasikan persamaan berikut ini dan sederhanakanlah persamaan tersebut, buktikanlah bahwa hasil penyederhanaan yang dilakukan benar!

ABCD D ABC CD B A D C B A D C B A BCD A CD B A D C B A D C B A D C B A Y= + + + + + + + + +

Lakukan seperti pada bagian 2.51 dan 2.5.2. Langkah 1 : buat Schematic editor rangkaian

ABCD D ABC CD B A D C B A D C B A BCD A CD B A D C B A D C B A D C B A Y= + + + + + + + + + :

Gambar 2.33 : Schematic editor

Langkah 2 : simulasikan sehingga diperoleh timing diagramnya (gambar 2.34)

Gambar 2.34 : Hasil simulasi

AB CD 00 01 11 10 00 1 0 0 1 01 1 0 0 1 11 1 1 1 1 10 1 0 0 0 Gambar 2.35 : peta karnaugh

Langkah 4 : gambar hasil rangkaian yang telah disederhanakan (Y = AB+CD+BC+ABC)

Gambar 2.36 : peta karnaugh

Langkah 5 : simulasikan rangkaian yang telah disederhanakan sehingga diperoleh timing diagramnya

Gambar 2.37 : Hasil simulasi

Langkah 6 : bandingkan timing diagram sebelum disederhanakan dengan yang setelah disederhanakan.

Dari kedua hasil simulasi rangkaian sebelum disederhanakan (gambar 2.34) dan yang setelah disederhanakan (gambar 2.37) sama, sehingga proses penyederhanaan yang dilakukan benar.

2.5.4 Simulasikan persamaan berikut ini dan sederhanakanlah persamaan tersebut, buktikanlah bahwa hasil penyederhanaan yang dilakukan benar!

ABCD D ABC D C AB D C AB D C B A D C B A BCD A D C B A D C B A D C B A D C B A X= + + + + + + + + + +

Langkah 1 : gambar rangkaian diatas pada schematic editor! Langkah 2 : simulasikan sehingga diperoleh timing diagramnya! Langkah 3 : Sederhanakan rangkaian tersebut!

Langkah 4 : gambar hasil rangkaian yang telah disederhanakan !

Langkah 5 : simulasikan rangkaian yang telah disederhanakan sehingga diperoleh timing diagramnya !

Langkah 6 : bandingkan timing diagram sebelum disederhanakan dengan yang setelah disederhanakan!

2.5.5 Simulasikan persamaan berikut ini dan sederhanakanlah persamaan tersebut, buktikanlah bahwa hasil penyederhanaan yang dilakukan benar!

D C AB D C AB D C B A D C B A BCD A D BC A D C B A D C B A D C B A D C B A Y= + + + + + + + + + +ABCD+ABCD

Langkah 1 : gambar rangkaian di atas pada schematic editor! Langkah 2 : simulasikan sehingga diperoleh timing diagramnya! Langkah 3 : Sederhanakan rangkaian tersebut !

Langkah 4 : gambar hasil rangkaian yang telah disederhanakan !

Langkah 5 : simulasikan rangkaian yang telah disederhanakan sehingga diperoleh timing diagramnya!

Langkah 6 : bandingkan timing diagram sebelum disederhanakan dengan yang setelah disederhanakan!