6

LANDASAN TEORI

2.1 Programmable Logic Device (PLD)

Dalam rangkaian digital, terdapat tiga macam elemen yang digunakan, antara lain: Memory, Microprocessor, dan perangkat logika. Memory merupakan perangkat penyimpanan informasi yang dapat berupa isi dari spreadsheet dan database. Microprocessor merupakan otak dari perangkat elektronik yang memproses program. Perangkat logika merupakan penyedia fungsi-fungsi yang spesifik, seperti interface dari satu perangkat ke perangkat lain, komunikasi data, pemrosesan sinyal, display data, waktu dan pengontrolan operasi, dan hampir seluruh fungsi lain yang harus dijalankan.

PLD merupakan komponen elektronik yang dapat digunakan untuk membangun rangkaian digital sesuai dengan keinginan perancang. PLD menghubungkan beberapa gerbang logika yang diatur oleh perancang hardware. Pemrograman logika berarti bahwa design chip baru dapat dicoba dan dapat dengan mudah diubah tanpa membutuhkan biaya untuk penyelesaian chip dalam pabrik semikonduktor. Dengan demikian, memory yang berdasarkan PLD bisa diprogram berkali-kali, yang memungkinkan produk dapat dikembangkan oleh pengguna, bukan hanya oleh pabrik saja.

Berdasarkan jumlah gerbang logika yang dimiliki, PLD dapat dibagi atas tiga tipe, yaitu Simple Programmable Logic Device (SPLD), Complex Programmable Logic Device (CPLD), dan Field Programmable Gate Array (FPGA).

2.1.1 Simple Programmable Logic Device (SPLD)

SPLD merupakan alat dengan gerbang AND yang dihubungkan dengan gerbang OR atau gerbang lain yang sejenis. Gerbang-gerbang ini dapat diatur sedemikian rupa oleh pemakai. SPLD dapat diprogram dengan fusible link, antifuse, EPROM, EEPROM, atau flash.

• Fusible link merupakan bagian dari Overcurrent Protection Device (OCPD) yang terdiri dari kawat logam yang akan meleleh ketika dipanaskan oleh suatu arus elektrik.

• Antifuse merupakan kebalikan dari fusible link.

• Erasable Programmable Read-Only Memory (EPROM) merupakan suatu jenis chip memory komputer yang dapat mempertahankan data ketika tegangan terputus dan data hanya dapat dihapus menggunakan sinar ultraviolet.

• Electrically Erasable Programmable Read-Only Memory (EEPROM) merupakan chip memory komputer yang dapat mempertahankan data ketika tegangan terputus dan data dapat dihapus secara elektrik.

• Flash merupakan memory komputer yang dapat mempertahankan data ketika tegangan terputus serta dapat menghapus dan menyimpan data secara elektrik.

2.1.2 Complex Programmable Logic Device (CPLD)

CPLD dibuat pertama kali oleh Ross Freeman pada pertengahan tahun 1980 dan Field Programmable Gate Array (FPGA) dibuat pertama kali pada tahun 1984. CPLD adalah gabungan dari beberapa SPLD yang dihubungkan oleh Programmable Switching Matrix. Jadi, CPLD merupakan sebuah programmable logic device dengan kompleksitas antara Programmable Array Logic (PAL) dan FPGA.

2.1.2.1 Karakteristik CPLD

CPLD memiliki sifat non-volatile yang diadopsi dari PAL, dan memiliki banyak gerbang yang diadopsi dari FPGA, meskipun gerbang PAL tidak sebanyak FPGA. Jumlah gerbang yang terdapat pada IC CPLD berkisar antara ribuan sampai ratusan ribu gerbang logika.

2.1.2.2 Arsitektur CPLD

CPLD disusun atas Logic Block, I/O Block, dan Pragrammable Interconnect. Logic Block memiliki macrocell yang terdiri dari sebuah SPLD dan sebuah flip-flop. I/O Block merupakan bagian pada CPLD yang digunakan sebagai interface data yang akan masuk dan keluar pada CPLD, Programmable Interconnect digunakan sebagai penghubung antar macrocell atau antara macrocell dengan I/O Block.

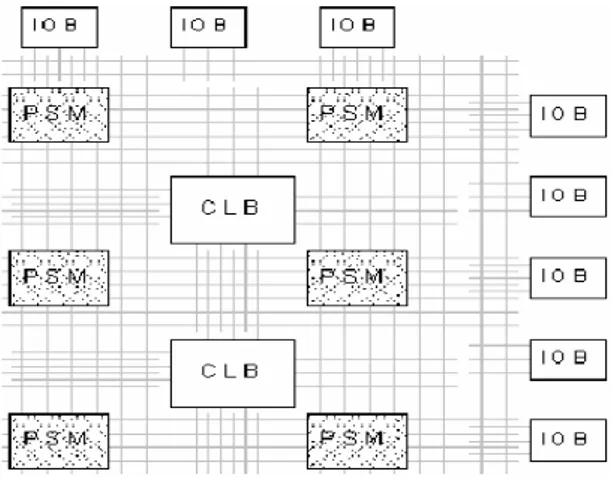

Macrocell Macrocell Macrocell Logic Block Macrocell Macrocell Macrocell Logic Block I/O Block Macrocell Macrocell Macrocell Logic Block Pr og ram m able Inte rco n n e ct Gambar 2.1 Arsitektur CPLD

2.1.3 Field Programmable Gate Array (FPGA)

FPGA merupakan rangkaian combinational dan sequential yang dikombinasikan sedemikian rupa untuk bisa diimplementasikan langsung pada silicon. Merupakan salah satu bagian dari application-specific integrated circuit (ASIC) yang memiliki performance tinggi tetapi memiliki fungsi yang spesifik (special purpose). Fungsi yang spesifik berarti hasil rangkaian yang dibuat hanya dapat melakukan satu proses khusus, contoh : jika user membuat rangkaian Full Adder, maka rangkaian ini hanya dapat melakukan penjumlahan saja.

Jadi FPGA merupakan hardware yang dapat diprogram dengan mengganti instruksi. Perancangan hardware FPGA dilakukan dengan cara mengatur koneksi antara ratusan ribu transistor yang tersedia pada chip sehingga terbentuk sebuah fungsi baru dalam suatu aplikasi baru.

2.1.3.1 Karakteristik FPGA

Karakteristik FPGA yang tidak dimiliki oleh PLD lain adalah gerbang logika yang berjumlah antara puluhan ribu sampai jutaan gerbang logika. Sifat pemrograman pada FPGA ada dua jenis yaitu :

• Non-volatile

Pada jenis non-volatile data tidak akan hilang jika tegangan terputus, tetapi jumlah pemrograman yang bisa ditangani lebih sedikit, dan pemrograman relatif lebih lambat dibandingkan dengan jenis volatile. Contoh : ROM.

• Volatile

Pada jenis volatile, data akan hilang jika tegangan terputus, tetapi jumlah pemrograman yang bisa ditangani lebih banyak, dan pemrograman relatif lebih cepat dibandingkan dengan jenis non-volatile. Oleh karena itu, untuk menyimpan data pada FPGA jenis ini, digunakan external memory. Contoh : RAM.

2.1.3.2 Arsitektur FPGA

FPGA terdiri dari Configurable Logic Blocks (CLB), Input / Output Blocks (IOB), dan Programmable Switch Matrix (PSM). CLB merupakan blok untuk membangun komponen-komponen combinational / sequential. Untuk dapat membentuk CLB dibutuhkan truth table dalam membangun jalur logika. IOB

merupakan blok yang digunakan untuk mengirimkan sinyal keluar dari chip dan sekaligus membaca sinyal yang masuk ke dalam chip. PSM merupakan penghubung yang bisa diatur sedemikian rupa untuk menghubungkan antar CLB dan CLB dengan IOB secara horizontal maupun secara vertikal, serta dapat mengeluarkan fan out (kemampuan untuk mengirimkan data ke banyak sumber untuk dijadikan input sekaligus) untuk multiple output. Jadi, output dari CLB yang satu dapat dihubungkan ke input CLB yang lain melalui multiple PSM.

Meskipun pada dasar arsitektur FPGA ditunjukkan seperti gambar 2.2, tetapi masing-masing vendor memiliki cara tersendiri dalam mengatur isi dari struktur masing-masing blok.

Proses pemrograman pada FPGA dapat dilihat pada gambar 2.3.

Gambar 2.3 Flowchart pemrograman pada FPGA

Berikut penjelasan dari masing-masing bagian flowchart diatas :

• Design Entry

Pada bagian ini, user memulai proses perancangan rangkaian logika yang akan diimplementasikan dalam programable logic device. Proses perancangan ini dapat dikerjakan dalam dua cara yang berbeda, yaitu text entry dan schematic entry.

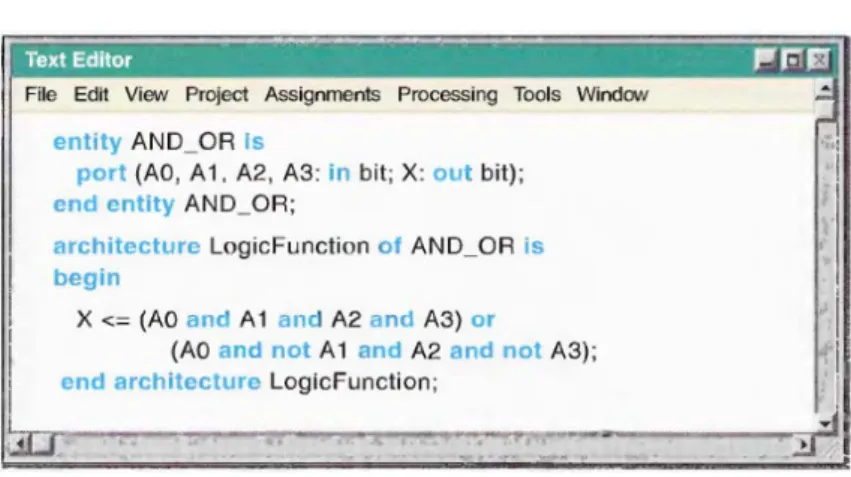

Text entry, user harus mengerti bahasa pemrograman Hardware Definiton Language (HDL) seperti VHDL atau Verilog.

Gambar 2.4 Text Entry yang menggunakan VHDL

Schematic entry merupakan cara mendesain rangkaian logika berdasarkan rancangan schematic.

Gambar 2.5 Schematic Entry

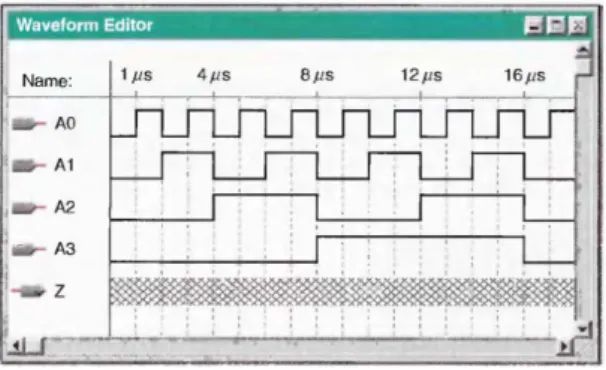

• Functional Simulation

Tujuan dari functional simulation dalam design flow adalah memastikan bahwa desain rangkaian logika yang dibuat bekerja sesuai dengan keinginan user. Proses ini disimulasikan dengan memberikan input waveforms dan mengecek output untuk semua kemungkinan kombinasi input menggunakan waveform editor.

Gambar 2.6 Contoh Functional Simulation

• Synthesis

Pada proses ini, rangkaian logika yang dibuat akan dioptimasi dengan meminimalkan jumlah penggunaan gerbang, mengganti elemen logika dengan elemen logika lain yang mempunyai fungsi sama, tetapi lebih efisien dalam penggunaan gerbang, serta mengeliminasi logika yang tidak diperlukan.

Hasil terakhir dari proses synthesis adalah netlist yang mendeskripsikan rangkaian logika yang sudah dioptimasi. Netlist adalah daftar connection yang mendeskripsikan komponen dan bagaimana komponen tersebut saling tersambung.

• Implementation

Proses ini meliputi mapping, placing, and routing desain sehingga desain tersebut dapat diimplementasikan ke IC FPGA sesuai dengan arsitektur dan konfigurasi pin IC FPGA tersebut.

• Timing Simulation

Proses ini memverifikasi rangkaian tersebut bekerja dengan frekuensi yang diinginkan dan tidak ada propagation delay atau permasalahan waktu lain yang akan berpengaruh kepada sistem secara keseluruhan

• Device Programming

Proses ini akan membuat bitstream yang merepresen-tasikan desain akhir dan akan dikirim ke target device.

2.1.4 Perbandingan antara SPLD, CPLD dan FPGA

Gambar 2.7 Grafik Perbandingan SPLD, CPLD dan FPGA

2.2 VHDL

VHDL merupakan kepanjangan dari VHSIC Hardware Description Language. VHSIC berarti Very High Speed Integrated Circuit program. Program ini telah dikembangkan oleh departemen pertahanan dengan tujuan untuk mengembangkan suatu generasi baru IC dengan kecepatan tinggi. Sebuah tim dari departemen pertahanan telah ditugaskan untuk mengembangkan bahasa ini

dan versi pertama diluncurkan pada tahun 1985. Setelah itu bahasa ini disahkan pada tahun 1987 oleh Institute of Electrical and Electronics Engineers (IEEE) dan menjadi standar IEEE 1076-1987. (Yalamanchili, 2001, p1).

VHDL dapat digunakan sebagai dokumentasi, pembuktian, dan sintesa pada perancangan digital berukuran besar. VHDL menggunakan tiga pendekatan untuk mendeskripsikan hardware, antara lain :

• Metode structural

• Data flow

• Behaviour

(http://www.gmvhdl.com/introduc.htm , 2007)

Metode Structural membagi rancangan ke dalam beberapa blok agar mudah dimengerti dan diatur, blok-blok tersebut kemudian dihubungkan hingga membentuk rancangan yang utuh. Setiap blok yang berdiri sendiri pada VHDL disebut “entity”.

Entity juga digunakan sebagai antar muka dari komponen. Komponen tersebut akan digunakan sebagai sebuah instance (sub block). Component instance merupakan salinan dari sebuah komponen yang dihubungkan ke bagian dan sinyal lain.

Data Flow merupakan jalur yang digambarkan dengan menyatakan bagaimana input dan output dalam komponen primitive (seperti gerbang logika AND) terhubung.

Behaviour berbeda dengan metode structural dan data flow, Behaviour tidak benar-benar menggambarkan bagaimana rancangan diimplementasikan. Dasar dari behaviour adalah adalah pendekatan kotak hitam (black box) dalam melakukan pemodelan, tidak peduli apa isi kotak hitam tersebut dan bagaimana cara kerja dari isi kotak hitam tersebut. Penjabaran behaviour didukung oleh proses statement yang muncul dalam badan architecture declaration seperti pada saat sequential statement yang ditemukan dalam bahasa pemrograman.

2.3 Keyboard

Keyboard merupakan suatu alat yang berfungsi untuk memberikan input data ke PC. Keyboard standard memiliki 104 tombol, yaitu: tombol ketik (57 tombol), tombol sistem (2 tombol), tombol aplikasi (1 tombol), tombol fungsi (12 tombol), tombol angka (16 tombol), tombol arah (4 tombol) , tombol enter (2 tombol) dan tombol lain-lain (10 tombol) seperti yang terlihat pada gambar 2.8.

Gambar 2.8 Tombol-tombol keyboard

Cara kerja suatu keyboard adalah dengan the key matrix, microprocessor dan circuit controller. Key matrix adalah jalur yang saling menghubungkan antar

tombol satu dengan tombol yang lain, sehingga apabila ada input dari user, microprosesor dan circuit controller dapat mengenali input tersebut. Sedangkan microprosesor dan circuit controller adalah tempat mengolah data yang diberikan oleh key matrix, seperti yang terdapat pada gambar 2.9 dan gambar 2.10.

Gambar 2.9 Key matrix Gambar 2.10 Microprosesor dan Circuit Controller

Port keyboard terdiri dari 6 pin yang terlihat seperti gambar 2.8 yang terdiri dari pin data, pin gnd, pin vcc, pin clock dan 2 pin yang tidak dipakai.

Gambar 2.11 PS/2 Port

Komunikasi keyboard adalah komunikasi serial dengan cara kerja ketika keyboard ditekan maka sinyal PS/2CLK dari kondisi idle (Logic High) akan berubah ke logic low dan berubah lagi ke logic high pada setiap bit data yang dikirimkan keyboard hingga data selesai dikirimkan. PS/2Data dikirim bersamaan dengan PS/2CLK. Ketika PS/2CLK berjalan PS/2Data akan berubah ke logic low yang bearti kondisi start setelah itu dikirimkan 8 bit data, satu parity bit (pengecekan kesalahan memakai odd parity ), dan bit terakhir adalah stop bit

(penanda bahwa data sudah selesai dikirimkan). Timing diagram keyboard dapat dilihat pada gambar 2.12. Contoh jika menekan tombol ”A” maka paket data yang dikirim adalah ”0”, ”0”, ”0”, ”0”, ”1”, ”1”, ”1”, ”0”, ”0”, ”0”, ”0”.

Gambar 2.12 Timing diagram keyboard

2.4 Monitor

Monitor merupakan suatu alat yang berfungsi untuk menampilkan data berupa tulisan atau gambar dari sebuah komputer.

2.4.1 Monitor Cathode Ray Tube (CRT)

CRT merupakan salah satu dari tipe monitor. CRT menggunakan sebuah electron gun untuk menembakkan sinar elektron pada sebuah metal grille / mask yang berada didalam layar kaca monitor. Layar dilapisi dengan phosphor yang berwarna merah, hijau, atau biru untuk membuat warna dan memproduksi gambar. Dengan menembakkan electron gun pada warna yang tepat dengan intensitas yang berbeda dapat memproduksi seluruh spectrum warna.

2.4.1.1 Tipe layar monitor CRT

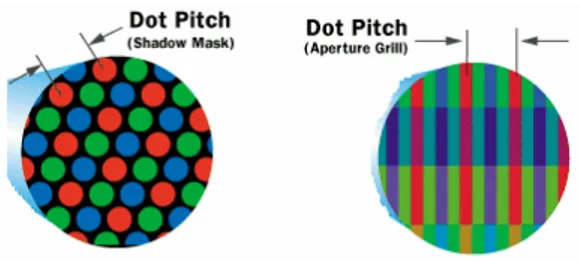

Ada 3 tipe grilles yaitu aperture grille, shadow mask, dan slot mask. Setiap tipe memiliki karakteristik masing-masing.

2.4.1.1.1 Shadow Mask

Layar Shadow Mask adalah sebuah layar metal dengan lubang kecil-kecil. Cara kerja dari shadow mask adalah tiga electron beam melewati lubang-lubang untuk fokus pada satu titik permukaan phoshor tampilan CRT. Tugas shadow mask adalah mengatur electron beam agar dapat tampil sesuai yang diharapkan. Gambar dari shadow mask seperti yang terlihat pada gambar 2.13 dan gambar 2.14.

Gambar 2.13 Shadow Mask Gambar 2.14 Tampilan pointer

2.4.1.1.2 Aperture Grille

Tabung Aperture Grille mengirimkan sinar elektron pada sebuah array dari kabel vertical tipis. Grille didukung oleh satu atau dua kabel horizontal yang bisa menyebabkan garis yang tidak kelihatan yang muncul pada layar putih. Kebanyakan pemakai tidak menyadari

efek ini jika tidak benar-benar dilihat. Contoh dapat dilihat pada gambar 2.15 dan 2.16.

Gambar 2.15 Aperture Grille Gambar 2.16 Tampilan huruf e

2.4.1.1.3 Slot Mask

Layar Slot Mask merupakan gabungan dari Aperture Grille dan teknologi Shadow Mask. Dalam rangka untuk meningkatkan jumlah elektron pada Mask.

Gambar 2.17 Tampilan pada Slot Mask

2.4.2 Resolusi

Sebuah layar monitor dibuat berdasarkan titik warna tersendiri (disebut: pixel). Resolusi monitor merupakan jumlah pixel yang terkandung dalam sebuah layar. Secara garis besar resolusi ditunjukkan dengan memberikan jumlah pixel yang berada pada sumbu horizontal dan

jumlah pixel yang berada pada sumbu vertical. Contoh seperti 1024 x 768, berarti ada 1024 pixel pada sumbu horizontal dan 768 pixel pada sumbu vertical. Semakin besar resolusi akan menghasilkan grafik yang lebih halus dan bisa meletakkan lebih banyak informasi sekaligus.

2.4.3 Kedalaman Warna

Kedalaman Warna (color depth) mengidentikasikan berapa banyak warna yang bisa ditampilkan pada layar monitor.

2.4.4 Refresh Rate

Refresh Rate merupakan berapa kali dalam 1 detik gambar pada layar CRT ditampilkan ulang.

2.4.5 Dot pitch

Dot pitch mengindikasikan berapa ketajaman dari gambar tersebut. Ukuran dot pitch dihitung dalam millimeter (mm) yang bearti semakin kecil angka semakin tajam gambar tersebut.

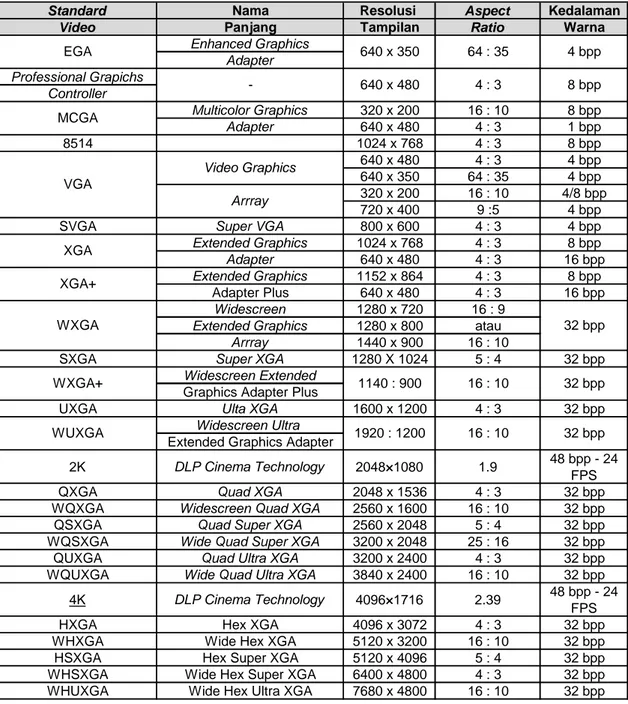

2.4.6 Standar tampilan computer

Tabel 2.1 Standar tampilan komputer

Standard Nama Resolusi Aspect Kedalaman

Video Panjang Tampilan Ratio Warna

Enhanced Graphics Adapter Professional Grapichs Controller Multicolor Graphics 320 x 200 16 : 10 8 bpp Adapter 640 x 480 4 : 3 1 bpp 8514 1024 x 768 4 : 3 8 bpp 640 x 480 4 : 3 4 bpp 640 x 350 64 : 35 4 bpp 320 x 200 16 : 10 4/8 bpp 720 x 400 9 :5 4 bpp

SVGA Super VGA 800 x 600 4 : 3 4 bpp

Extended Graphics 1024 x 768 4 : 3 8 bpp

Adapter 640 x 480 4 : 3 16 bpp

Extended Graphics 1152 x 864 4 : 3 8 bpp

Adapter Plus 640 x 480 4 : 3 16 bpp

Widescreen 1280 x 720 16 : 9

Extended Graphics 1280 x 800 atau

Arrray 1440 x 900 16 : 10

SXGA Super XGA 1280 X 1024 5 : 4 32 bpp

Widescreen Extended

Graphics Adapter Plus

UXGA Ulta XGA 1600 x 1200 4 : 3 32 bpp

Widescreen Ultra

Extended Graphics Adapter

2K DLP Cinema Technology 2048×1080 1.9 48 bpp - 24

FPS

QXGA Quad XGA 2048 x 1536 4 : 3 32 bpp

WQXGA Widescreen Quad XGA 2560 x 1600 16 : 10 32 bpp

QSXGA Quad Super XGA 2560 x 2048 5 : 4 32 bpp

WQSXGA Wide Quad Super XGA 3200 x 2048 25 : 16 32 bpp

QUXGA Quad Ultra XGA 3200 x 2400 4 : 3 32 bpp

WQUXGA Wide Quad Ultra XGA 3840 x 2400 16 : 10 32 bpp

4K DLP Cinema Technology 4096×1716 2.39 48 bpp - 24

FPS

HXGA Hex XGA 4096 x 3072 4 : 3 32 bpp

WHXGA Wide Hex XGA 5120 x 3200 16 : 10 32 bpp

HSXGA Hex Super XGA 5120 x 4096 5 : 4 32 bpp

WHSXGA Wide Hex Super XGA 6400 x 4800 4 : 3 32 bpp

WHUXGA Wide Hex Ultra XGA 7680 x 4800 16 : 10 32 bpp

WUXGA 1920 : 1200 16 : 10 32 bpp WXGA+ 1140 : 900 16 : 10 32 bpp WXGA 32 bpp XGA+ EGA 640 x 350 64 : 35 4 bpp - 640 x 480 4 : 3 8 bpp MCGA VGA Video Graphics Arrray XGA 2.4.7 Monitor Protocol

Monitor protocol merupakan suatu standar susunan data yang akan dikirimkan ke monitor agar monitor dapat mengenal data apa yang

dikirim ke monitor. Beberapa tipe monitor protocol yang dibahas adalah Digital Video Interface (DVI), dan Video Graphic Array (VGA).

2.4.7.1 Digital Video Inteface (DVI)

Merupakan standard video interface yang didesain untuk memaksimalkan kualitas tampilan dari layar digital seperti flat panel CRT layar komputer dan proyektor digital. DVI didesain terutama untuk membawa data digital video yang belum di-compress manjadi sebuah tampilan. Secara terpisah DVI compatible dengan standard High Definition Multimedia Interface (HDMI) dalam digital mode (DVI-D).

Gambar 2.19 Konektor DVI

2.4.7.2 Video Graphic Array (VGA)

Merupakan standar tampilan komputer analog, pertama dipasarkan pada tahun 1987 oleh IBM. Layar terbentuk dari sebuah pixel matrix yang berukuran 640 pixel mendatar dan 480 pixel menurun (jumlah pixel pada mendatar dan menurun bisa

lebih besar atau lebih kecil). Suatu berkas elektron mewarnai masing-masing pixel dari kiri ke kanan dan dari atas ke bawah.

Gambar 2.20 Pixel koordinat

Gambar 2.21 Konektor VGA

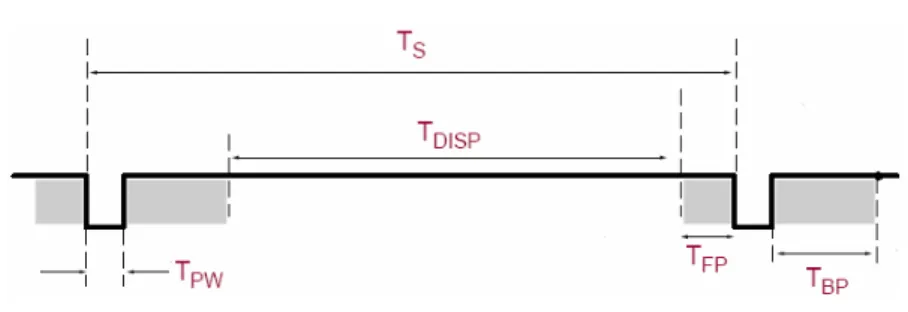

2.4.7.2.1 Horizontal Timing dan Vertical Timing VGA Monitor

Gambar 2.22 Timing diagram monitor

• Sync pulse time (Ts) adalah waktu penjumlahan antara

• Display time (TDISP) adalah waktu dimana menampilkan

gambar pada monitor.

• Pulse width (TPW) adalah waktu sesudah back porch. • Front porch (TFP) adalah waktu sesudah TDISP. • Back porch (TBP) adalah waktu sebelum TDISP.

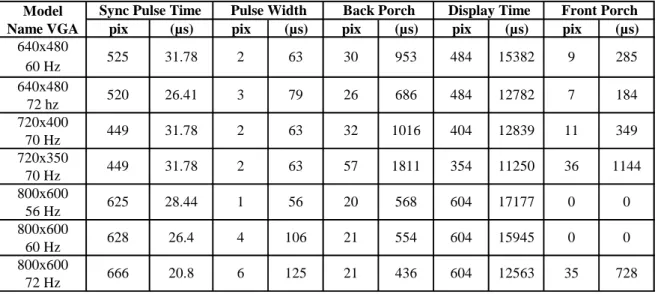

Tabel 2.2 Vertical timing Model

Name VGA pix (µs) pix (µs) pix (µs) pix (µs) pix (µs)

640x480 60 Hz 640x480 72 hz 720x400 70 Hz 720x350 70 Hz 800x600 56 Hz 800x600 60 Hz 800x600 72 Hz 1016 404 12839 11 349 449 31.78 2 63 32 525 31.78 2 63 30

Sync Pulse Time Pulse Width Back Porch Display Time Front Porch

520 26.41 3 79 26 953 484 15382 9 285 686 484 12782 7 184 449 625 628 666 31.78 28.44 26.4 20.8 63 2 1 4 6 56 106 125 21 21 20 57 1811 568 554 436 604 604 604 354 11250 17177 15945 12563 35 0 0 36 1144 0 0 728 ( http://www.epanorama.net/documents/pc/vga_timing.html )

Tabel 2.3 Horizontal timing

Mode Sync pulse time Pulse width Back porch Display time Front porch

Name VGA (pix) (pix) (pix) (pix) (pix)

640x480 60Hz 800 96 45 646 13 640x480 72Hz 832 40 125 646 21 720x400 70Hz 900 108 51 726 15 720x350 70Hz 900 108 51 726 15 800x600 56Hz 1024 72 125 806 21 800x600 60Hz 1056 128 85 806 37 800x600 72Hz 1040 120 61 806 53 ( http://www.epanorama.net/documents/pc/vga_timing.html )

Perhitungan timing untuk monitor tidak ada yang baku. Setiap user dapat merancang sendiri timing untuk monitor.

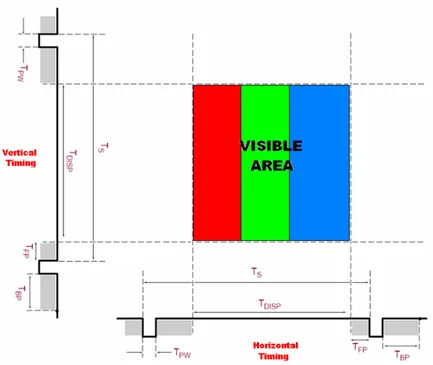

2.4.7.2.2 Penggabungan Horizontal Timing dan Vertical Timing

Gambar 2.23 Penggabungan horizontal timing dan vertical timing

Visible area merupakan daerah yang akan ditampilkan pada monitor, selain daerah visible area tidak dapat dilihat pada monitor.