BAB 1.

KONSEP DASAR DIGITAL

Materi :

1. Representasi Bentuk Digital dan Analog

2. Bentuk Sinyal Digital

3. Transmisi Serial & Paralel

4. Switch dalam Rangkaian Elektronika

5. Gerbang Logika Dasar

6. Tabel Kebenaran

Pendekatan

Æ

Representasi Numerik

Representasi ANALOG :

Besarannya dinyatakan dalam tegangan, arus atau

gerakan meter yang proporsional dengan nilai dari

besaran itu sendiri.

Contoh :

Speedometer

sepedamotor (kecepatan sepeda

motor ditunjukkan oleh gerakan jarum)

Thermostat

ruangan (temperatur ruangan ditunjukkan

oleh gerakan strip metalnya)

Representasi DIGITAL

Besarannya tidak hanya ditunjukkan dalam nilai

yang proporsional saja, tetapi juga dalam simbol

yang dinamakan digit.

Contoh :

-

Jam digital

-

Kalkulator

Beda sistim Analog dan Digital

Sistim DIGITAL

Kombinasi dari sejumlah peralatan yang didisain untuk

memanipulasi informasi logika atau besaran fisik yang

dinyatakan dalam bentuk digital; nilainya berupa nilai-nilai diskrit.

Sebagian besar berupa peralatan elektronik, juga bisa mekanik,

magnetik atau pneumatik.

Contoh : komputer, kalkulator, audio dan video digital, sistim

telepon.

Sistim ANALOG

Terdiri dari sejumlah peralatan untuk memanipulasi besaran fisik

yang dinyatakan dalam bentuk analog. Besarannya bisa

bervariasi dalam rentang nilai yang kontinyu.

Keunggulan Sistem Digital

1. Mudah dalam mendisain

2. Mudah dalam penyimpanan informasi

3. Ketepatan dan akurasi tinggi

4. Pengoperasiannya dapat diprogram

5. Lebih tahan terhadap noise

Bagaimana mem-proses sistim analog

menggunakan teknik digital ?

Ada 3 langkah :

1. Ubah input analog menjadi bentuk digital

2. Lakukan pemrosesan informasi digital

3. Ubah kembali output digital ke dalam bentuk analog

Peralatan

Ukur

A/D

Converter

Digital

Processing

D/A

Converter

Controller

Analog

Analog

Digital

Digital

Analog

temperatur

Pengaturan

temperatur

Bentuk Sinyal Digital

0 V

0,8 V

2 V

5 V

Biner ‘0’

Biner ‘1’

Tidak digunakan

t

0t

1t

2t

3t

40

0

0

1

1

4 V

t

Vo(t)

Rangkaian Digital

Didisain untuk menghasilkan output digital yang

bervariasi, yaitu ‘0’ atau ‘1’

0 V

4 V

v

iv

o5 V

0 V

t

Case 1

0,5 V

4 V

v

iv

o3,7 V

0 V

t

Case 2

Rangkaian

Digital

v

iv

oTransmisi SERIAL dan PARALEL

Salah satu aspek penting dalam sistim digital adalah

memindahkan data / informasi digital dari satu tempat ke

tempat lainnya

Æ

Transmisi

Berdasarkan jumlah circuit/kabel yang menghubungkan

kedua tempat tersebut, ada 2 jenis transmisi :

a. Transmisi

Paralel

Æ

jumlah circuit yang terhubung lebih dari 1

b. Transmisi

Serial

Æ

jumlah circuit yang terhubung hanya 1

Kelebihan/kekurangan :

Transmisi Paralel

Æ

waktu pengiriman cepat, cost mahal

Contoh : DB-25 (printer)

Transmisi Serial

Æ

waktu pengiriman lambat, cost murah

Contoh : internet (RJ-45), USB, DB 9

A

4A

3A

2A

1A

0MSB

LSB

Circuit

A

B

4B

3B

2B

1B

0Circuit

B

1

0

0

1

1

Transmisi Paralel

A

OUTCircuit

A

B

INCircuit

B

Transmisi Serial

T

0T

1T

2T

3T

40

0

1

1

1

SWITCH DALAM RANGKAIAN ELEKTRONIKA

Transisi antara level digital ‘1’ dan ‘0’ dapat dibuat dengan

men-switch dari level tegangan satu ke level tegangan

yang lain (biasanya 0V dan +5V).

Komponen-komponen yang bisa dijadikan switch :

-Dioda

-Transistor

Dioda sebagai switch

5V

Dioda

K

A

5V

arus I

Dioda

A

K

Transistor sebagai switch

RB RC 5 V 2 VV

out= 0 V

Transistor ON

Sinyal

input

RB RC 5 V 0 VV

out= 5 V

Transistor OFF

GERBANG LOGIKA DASAR

Gerbang Logika

Æ

blok dasar untuk membentuk rangkaian

elektronika digital

¾

Sebuah gerbang logika mempunyai satu terminal output

dan satu atau lebih terminal input

¾

Output-outputnya bisa bernilai HIGH (1) atau LOW (0)

tergantung dari level-level digital pada terminal inputnya.

¾

Ada 7 gerbang logika dasar : AND, OR, NOT, NAND,

NOR, Ex-OR, Ex-NOR

input

output

Gerbang

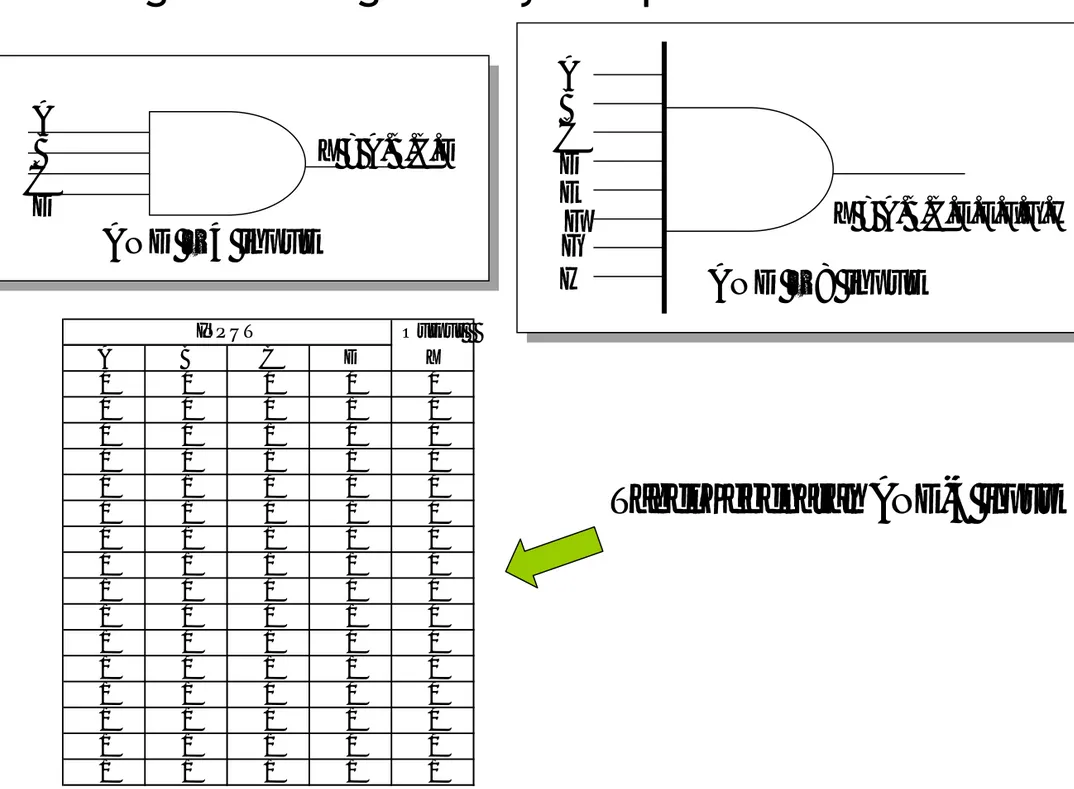

Gerbang AND

Input A

Input B

Output X

Simbol gerbang logika AND

Operasi AND :

• Jika Input A AND B keduanya

HIGH

, maka output X akan

HIGH

• Jika Input A atau B salah satu atau keduanya

LOW

maka output X

akan

LOW

A B 0 0 0 0 1 0 1 0 0 INPUT Output XTabel Kebenaran

gerbang AND – 2 input

Cara kerja Gerbang AND :

1

1

0

0

A

B

X = A.B

5 V

Analogi elektrikal gerbang AND

X=A.B

+5V

A

B

Konfigurasi Pin

QUAD 2-Input AND Gate

(7408)

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

Quad Æ

Ada 4 gerbang AND

2 input AND gate Æ

gerbang AND 2 input

7408 Æ

(74 = TTL), (08 = nomor urut)

Gerbang AND dengan banyak Input

A

X = A.B.C.D

B

C

D

AND – 4 input

X = A.B.C.D.E.F.G.H

A

B

C

D

F

E

H

G

AND – 8 input

A B C D 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 Output X INPUTKonfigurasi Pin

DUAL 4-Input AND Gate

(7421)

TRIPLE 3-Input AND Gate

(7411)

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

Gerbang OR

Input A

Input B

Output X

Simbol gerbang logika OR

Operasi OR :

• Jika Input A OR B atau keduanya

HIGH

, maka output X akan

HIGH

• Jika Input A dan B keduanya

LOW

maka output X akan

LOW

Konfigurasi Pin

Tabel Kebenaran

gerbang OR – 2 input

QUAD 2-Input OR Gate

(7432)

A

B

0

0

0

0

1

1

1

0

1

1

1

1

INPUT

Output

X

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

Cara kerja Gerbang OR :

1

0

A

X = A+B

5 V

1

0

B

Analogi elektrikal gerbang OR

X=A+B

+5V

A

B

Gerbang OR dengan banyak Input

X = A+B+C+D+E+F+G+H

A

B

C

D

F

E

H

G

OR – 8 input

A

X = A+B+C

B

C

OR – 3 input

Tabel Kebenaran OR-3 input

A B C 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 Output X INPUT

Gerbang NOT / INVERTER

Input A

Output X

Simbol gerbang logika NOT

Operasi NOT :

• Jika Input A

HIGH

, maka output X akan

LOW

• Jika Input A

LOW,

maka output X akan

HIGH

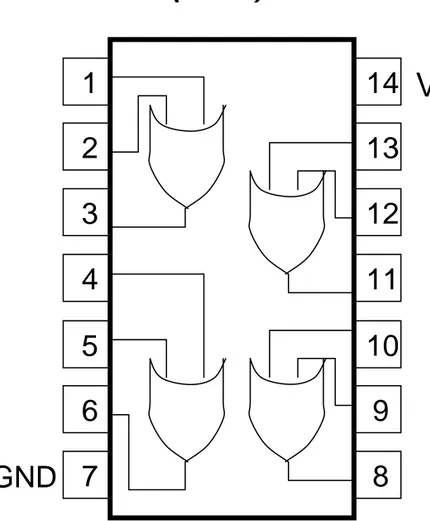

Konfigurasi Pin

Tabel Kebenaran

gerbang NOT / INVERTER

HEX Inverting Gate

(7404)

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

0

1

1

0

INPUT

A

Output

X

Gerbang NAND

Simbol gerbang logika NAND

Input A

Input B

Output X

Input A

Input B

Output X

ATAU

Operasi NAND :

• Merupakan Inversi (kebalikan) dari operasi AND

• Jika Input A AND B keduanya

HIGH,

maka output X akan

LOW

• Jika Input A atau B atau keduanya

LOW

, maka output X akan

HIGH

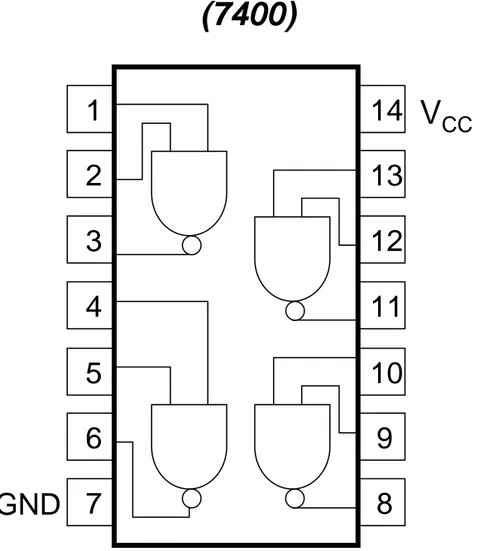

Konfigurasi Pin

Tabel Kebenaran

gerbang NAND

QUAD 2-input NAND Gate

(7400)

A B 0 0 1 0 1 1 1 0 1 1 1 0 INPUT Output X1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

Gerbang NAND dengan banyak Input

A

X = A.B.C

B

C

NAND – 3 input

X = A.B.C.D.E.F.G.H

A

B

C

D

F

E

H

G

NAND – 8 input

Tabel Kebenaran NAND-3 input

A B C 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 Output X INPUT

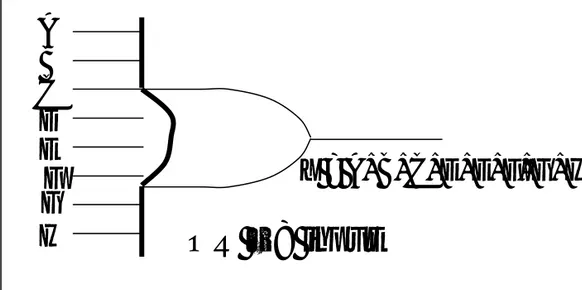

Gerbang NOR

Input A

Input B

Output X

Input A

Input B

Output X

ATAU

Simbol gerbang logika NOR

Operasi NOR :

• Merupakan Inversi (kebalikan) dari operasi OR

• Jika Input A dan B keduanya

LOW,

maka output X akan

HIGH

• Jika Input A OR B salah satu atau keduanya

HIGH

, maka

output X akan

LOW

Konfigurasi Pin

QUAD 2-Input NOR Gate

(7402)

Tabel Kebenaran

gerbang NOR

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

A B 0 0 1 0 1 0 1 0 0 1 1 0 INPUT Output XGerbang Ex-OR

Input A

Input B

Output X

Simbol gerbang logika Ex-OR

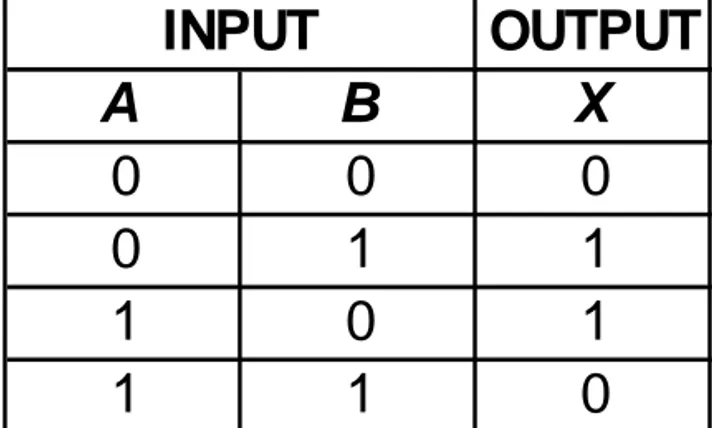

Operasi Ex-OR :

• Ex-OR adalah kependekan dari Exclusive OR

• Jika salah satu dari kedua inputnya HIGH (bukan kedua-duanya),

maka output X akan HIGH

• Jika kedua inputnya bernilai LOW semua atau HIGH semua,

maka output X akan LOW

Tabel Kebenaran Gerbang Ex-OR

OUTPUT A B X 0 0 0 0 1 1 1 0 1 1 1 0 INPUTPersamaan Logika Ex-OR

X = A + B

Berdasarkan Tabel Kebenaran di atas (yang bernilai output = 1),

Ex-OR dapat disusun dari gerbang dasar : AND, OR dan NOT

Persamaan EX-OR (dari AND, OR dan NOT) :

X = AB + AB

A

B

X

A

B

X

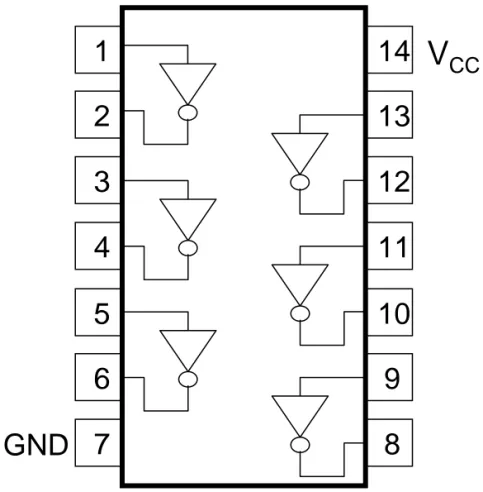

Konfigurasi Pin

QUAD 2-Input Exclusive OR Gate

(7486)

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CCGND

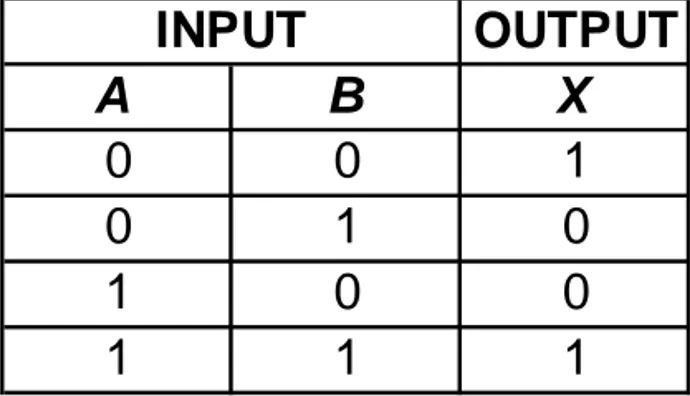

Gerbang Ex-NOR

Input A

Input B

Output X

Simbol gerbang logika Ex-NOR

Operasi Ex-NOR :

• Ex-NOR merupakan kebalikan dari Ex-OR

• Jika salah satu dari kedua inputnya HIGH (bukan kedua-duanya),

maka output X akan LOW

• Jika kedua inputnya bernilai LOW semua atau HIGH semua,

maka output X akan HIGH

Tabel Kebenaran Gerbang Ex-NOR

OUTPUT A B X 0 0 1 0 1 0 1 0 0 1 1 1 INPUTPersamaan Logika Ex-NOR

X = A + B

Berdasarkan Tabel Kebenaran di atas (yang bernilai output = 1),

Ex-NOR dapat disusun dari gerbang dasar : AND, OR dan NOT

Persamaan EX-NOR (dari AND, OR dan NOT) :

X = AB + AB

A

B

X

A

B

X

RINGKASAN JENIS GERBANG LOGIKA

No NAMA

TIPE IC

Simbol Logika

Persamaan

Tabel Kebenaran

A B 0 0 0 0 1 0 1 0 0 1 1 1 INPUT Output X

A

B

X

AND

7408

1

X=A.B

4

3 NOT

NAND 7400

7404

2

OR

7432

A

B

X

X=A+B

A B 0 0 0 0 1 1 1 0 1 1 1 1 INPUT Output XA

X

0 1 1 0 INPUT A Output XX=A

A B 0 0 1 0 1 1 1 0 1 1 1 0 INPUT Output XA

B

X

X=A.B

RINGKASAN JENIS GERBANG LOGIKA……

cont

No NAMA

TIPE IC

Simbol Logika

Persamaan

Tabel Kebenaran

5 NOR

7402

A

B

X

X=A+B

A B 0 0 1 0 1 0 1 0 0 1 1 0 INPUT Output X7

6 Ex-OR

Ex-NOR

7486

OUTPUT A B X 0 0 0 0 1 1 1 0 1 1 1 0 INPUTA

B

X

X=A + B

X=A + B

A

B

X

OUTPUT A B X 0 0 1 0 1 0 1 0 0 1 1 1 INPUTTABEL KEBENARAN

•

Sebuah Tabel yang digunakan untuk menganalisa respons output

dari gerbang / rangkaian logika berdasarkan kombinasi

input-inputnya

Terdiri dari 2 bagian : Input dan Output

Bagian input bisa terdiri dua atau lebih variabel, baik variabel input

gerbang maupun variabel kontrol (mis : enable, strobe, clock)

Bagian output juga bisa terdiri dari satu atau lebih variabel

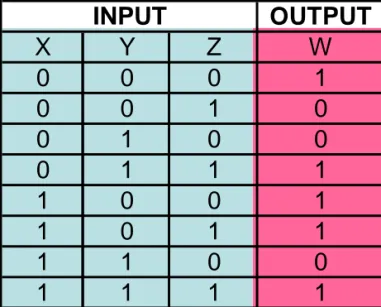

OUTPUT X Y Z W 0 0 0 1 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 1 INPUT

Ada 3 var. input

(n=3, yaitu X,Y,Z)

Jumlah data = 8 (=2

n)

(masing-masing 3 bit)

Ada 1 var. output, dimana

masing-masing data

ANALISA PE-WAKTU-AN

Cara penganalisaan response output terhadap kombinasi input-inputnya

pada periode waktu tertentu,

Cara penganalisaaan yang lain adalah dengan Tabel Kebenaran

Peralatan yang digunakan disebut : Timing Diagram (Diagram pe-waktu-an).

Bentuk Timing Diagram :

A

B

1

0

X

1

0

1

0

t1

t2

t3

t4

t5

t0

INPUT

OUTPUT

Contoh :

1. Buatlah timing diagram untuk mendapatkan output dari gerbang AND

berikut ini :

A

B

X

Jawab :

A

B

1

0

X

1

0

1

0

2. Buatlah timing diagram untuk mendapatkan output dari gerbang Ex-OR

berikut ini :

A

B

X

Jawab :

A

B

1

0

X

1

0

1

0

Soal Latihan :

1. Sebuah input data mempunyai urutan : 101110010. Gambarkan bentuk

gelombang dari data input tersebut dalam representasi sinyal digital.

2. Sebutkan 3 jenis aplikasi yang menggunakan teknologi digital.

3. Buat Tabel Kebenaran untuk gerbang AND-3 input berikut ini :

A

B

C

4. Buat Tabel Kebenaran untuk gerbang NOR-4 input berikut ini :

5. Buat Timing Diagram untuk output X dari gerbang OR-3 input berikut ini :

A

B

C

D

X

A

B

C

X

A

B

1

0

C

1

0

1

0

I. DASAR RANGKAIAN SEKUENSIAL

Tujuan :

1. Memahami perbedaan antara rangkaian kombinasional dan

sekuensial

2. Mengerti State Diagram

3. Mengerti maksud dan tujuan Elemen Penyimpan Biner

4. Dapat membuat SR Flip-flop dari gerbang NOR

5. Dapat membuat SR Flip-flop dari gerbang NAND

6. Mengerti Elemen Penyimpan dengan Clock

7. Dapat melakukan Analisa Rangkaian Sekuensial

8. Dapat melakukan Sintesa Rangkaian Sekuensial

RANGKAIAN

KOMBINASIONAL

INPUT

OUTPUT

a) Blok Diagram Rangkaian Kombinasional

RANGKAIAN

KOMBINASIONAL

OUTPUT

INPUT

Elemen

Penyimpan

Present

State

Next

State

Fungsi Delay pada Elemen Penyimpan

t

PD 1 0 0 1 1 0 1 0 1 0 1 0 2 7 12 3 8 13 X A B 1 2 3 3 8 1 0 1 0 4 5 13 4 9 14 5 2 3 4 1 X A B)

,

,

(

A

B

X

F

X

B

AB

XA

X

B

A

f

(

,

,

)

=

.

.

B A C D G 1 0 1 0 1 0 1 0 1 0 5 19 6 9 12 15 18 20 7 10 13 16 19 21 8 11 14 17 20 22 9 12 15 18 21 23 G A B C D

A

B

C

Z

X

Y

)

(

).

(

)

(

)

(

).

(

)

(

t

C

t

B

t

Y

t

B

t

A

t

X

=

∆

+

=

∆

+

)

(

)

(

)

2

(

t

+

∆

=

X

t

+

∆

+

Y

t

+

∆

Z

[

(

)

(

)

]

)

(

)

(

)

(

)

(

)

(

t

B

t

B

t

C

t

B

t

A

t

C

t

A

+

=

+

=

0

0

0

0

1

1

1

1

5

4

7

12

10

12

15

18

20 23

23

21

A

B

C

Z

A

B

Z

nX

Y

)

(

)

(

)

2

(

t

+

∆

=

X

t

+

∆

+

Y

t

+

∆

Z

[

(

)

(

)

]

)

(

t

A

t

Z

t

B

+

=

0

0

0

1

1

1

5

4

7

14

10

12

18 21

A

B

Zn

STATE DIAGRAM

• Menggambarkan perubahan kondisi sebuah variabel (output) dari

kondisi sekarang (Present State) ke kondisi berikutnya (Next State).

• Kondisi tersebut berubah karena adanya pengaruh input dari luar

State diagram terdiri dari

a.

Lingkaran (node) yang jumlahnya satu untuk tiap-tiap keadaan.

b.

Anak panah transisi, yang meninggalkan tiap-tiap keadaan

A

B

A = Present input B = Present output

A

B

Rangkaian sekuensial

gerbang NAND

0

1

1

0

0

1

State Diagram untuk

rangkaian NAND di atas

A

B

X

Y

Z

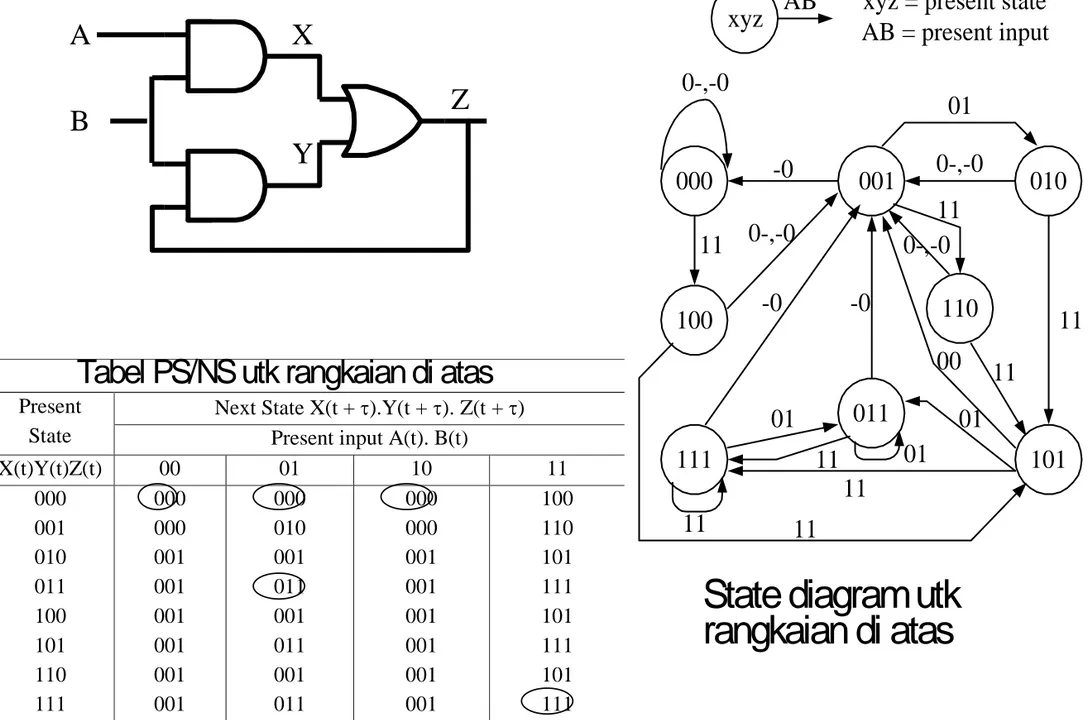

000 001 010 100 110 111 011 101 0-,-0 -0 01 0-,-0 11 0-,-0 11 11 00 01 01 11 11 11 11 01 11 0-,-0 -0 -0xyz AB xyz = present state AB = present input

Tabel 8-1 Tabel Present state/next state untuk rangkaian gambar 8-9 Next State X(t + τ).Y(t + τ). Z(t + τ)

Present

State Present input A(t). B(t)

X(t)Y(t)Z(t) 00 01 10 11 000 001 010 011 100 101 110 111 000 000 001 001 001 001 001 001 000 010 001 011 001 011 001 011 000 000 001 001 001 001 001 001 100 110 101 111 101 111 101 111

Tabel PS/NS utk rangkaian di atas

State diagram utk

rangkaian di atas

ELEMEN PENYIMPAN BINER

Bentuk sederhana dari elemen penyimpan biner adalah sebuah

rangkaian yang dapat mengingat sebuah sinyal biner sebelumnya,

terutama nilai logika.

τ

1

S

Y

Z

τ

2

Z(t) = 0 , t

S(t) = 0 , t

≤

≤

0

0

Y(t) = 0, t

≤

0

1

0

1

0

1

2

t

4

t

3

t

2

t

1

t

1 +

τ1

t

1 +

τ1

+

τ2

S

Y

Z

NOR SR FLIP-FLOP

τ

1τ

2S

Y

R

Z

S(t) = 0

Y(t) =1

R(t) = 0

Z(t) = 0, t

≤

0

τ

1=

τ

2= 1 unit

1 0 0 1 1 0 1 0 5 10 15 20 7 6 17 16S

R

Y

Z

(

)

)

(

)

(

)

(

*

)

(

)

(

2 1t

R

t

Y

t

Z

t

S

t

Z

t

Y

+

=

+

+

=

+

τ

τ

)

(

)

(

)

(

t

+

τ

1+

τ

2=

Y

t

+

τ

1+

R

t

+

τ

1Z

)

(

)

(

)

(

+

+

+

τ

1=

Z

t

S

t

R

t

[

(

)

(

)

]

)

(

t

1Z

t

S

t

R

+

+

=

τ

Z Z 1 0

S

R

S R 1 0Z

Simbol Logika NOR SR Flip-flop

S

R

Z*

Z

Kondisi

0

0

Zn

Zn

Hold

0

1

0

1

Reset

1

0

1

0

Set

1

1

0

0

Not used

NAND SR FLIP-FLOP

S(t) = 1

R(t) = 1

Z*(t) = 1

Z(t) = 1

S R Z* Z 5 10 15 20 6 17 7 16 1 0 1 0 1 0 1 0 S R Z* ZS

R

Z

Z

S R 1 0 Z *Simbol Logika NAND SR Flip-flop

S

R

Z*

Z

Kondisi

0

0

Zn

Zn

Hold

0

1

0

1

Reset

1

0

1

0

Set

1

1

1

1

Not used

Rangk. Sekuensial 15

ELEMEN PENYIMPAN DENGAN CLOCK

Di dalam sistem digital sering terjadi beberapa buah SR flip flop yang

bekerja secara bersamaan (

synchron)

. Untuk mengatasi hal itu,

maka diperlukan suatu alat pengontrol yang bekerja untuk mengatur

proses dari rangkaian tersebut.

Clock SR flip flop

yaitu menambahkan sinyal enable pada gerbang SR.

Tujuan dari suatu sinyal clock adalah agar user dapat

menahan

dan

mengembalikan

SR flip flop untuk berhenti sejenak (

rest state

)

selama perubahan terjadi pada input SR.

S C R Z Z* b R C S Z Z* a S R 1 0 C

Simbol Logika SR-FF dengan Clock

NAND SR-FF dengan Clock

Persamaan output untuk gerbang NOR :

Z(t +

∆

) = [R(t) + C(t)][S(t)C(t) + Z(t)]

Z(t +

∆

) = [S(t) + C(t)][R(t)C(t) +Z(t)]

Jika C(t) = 0

Z(t +

∆

) = Z(t),

Z

*(t +

∆

) = Z

*(t)

Jika C(t) = 1

Z(t +

∆

) = R(t)[S(t) + Z(t)],

Z(t +

∆

) = S(t)[R(t) + Z

*(t)]

Rangk. Sekuensial 17

ANALISA RANGKAIAN SEKUENSIAL

Digunakan untuk mendapatkan hasil keluaran dari sebuah

rangkaian sekuensial yang diketahui

Langkah-langkah melakukan analisa :

a. Tentukan persamaan logika kombinasional untuk input S dan R,

serta anggap gerbangnya dalam keadaan ideal.

b. Tentukan apakah S.R = 0

Catatan : Jika S.R

≠

0, prosedur harus dihentikan.

c. Gunakan persamaan gerbang NAND atau NOR untuk

menentukan persamaan next state.

Z(t +

∆

) = S(t) + (t)Z(t)

NAND

Z(t +

∆

) = (t)[S(t) + Z(t)]

NOR

Catatan : Jika S.R = 0, kedua persamaan ini adalah ekivalen.

R

R

Contoh 1 :

Tentukan persamaan next state dan tabel present state/next state

untuk clock SR flip flop di bawah ini.

S

R

1

0

X

C

A

B

clockJawab :

1. S(t) = A(t) , R(t) =

2. S(t) . R(t) = A(t) .

3. X(t +

∆

) = S(t) + (t)X(t)

=

A(t) + [A(t) + B(t)] X(t)

=

A(t) + B(t)X(t)

B(t)

A(t)

B(t)

A(t)

+

=

⋅

0

B(t)

A(t)

=

R

Tabel 8-8

Tabel PS/NS untuk gambar 8-20

Present Input

Present

State

Next State

A(t) B(t) X(t) X (t +

∆

)

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

1

1

1

1

Tabel Present State / Next State untuk soal contoh 1 :

0 1

X

AB

0- 1-

1-,1-00

SINTESA RANGKAIAN SEKUENSIAL

Digunakan untuk mendisain sebuah rangkaian logika sekuensial,

jika diberikan deskripsi dari fungsi rangkaian tersebut

Prosedur sintesa dengan menggunakan clock SR flip flop :

1. Dengan menggunakan persamaan next state yang diketahui,

buatlah tabel present state/next state untuk rangkaian yang

akan dibangun.

2. Tambahkan kolom pasangan eksitasi S

Xi(t) dan R

Xi(t) untuk setiap

variabel keadaan. Masukkan ke dalam kolom ini, dengan

menggunakan pasangan : [X

i(t), X

i(t +

∆

)

3. Tuliskan persamaan logika untuk kolom eksitasi S

Qi(t) dan R

Qi(t).

4. Buatlah tabel eksitasi dan persamaan outputnya.

5. Periksa kembali dan analisa setiap flip flop dengan

menggunakan persamaan umum next state, yaitu :

Q

i(t +

∆

) = S

Qi(t) +

Qi(t)Q

i(t)

Kemudian : S

(t) .

(t) = 0

R

R

Rangk. Sekuensial 21

Contoh 2 :

Rancanglah rangkaian sekuensial dengan menggunakan clock

SR flip flop dimana persamaan next statenya adalah :

X(t +

∆

) = A(t)X(t) + B(t)

Jawab :

Dengan menggunakan persamaan next state, maka dapat

dibangun tabel present state/next statenya

Tabel 8-12 Tabel present state/next state contoh 8-4 Present Input Present

State

Next

State Nilai eksitasi A(t) B(t) X(t) X(t + ∆) Sx(t) Rx(t) 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 1 1 0 1 1 1 0 0 1 d 0 d 1 d d 1 0 0 d 0 0 0

Mencari persamaan logika menggunakan K-Map :

X X A B A B A B A B 1 1 d d d X X A B A B A B A B 1 d d Untuk Sx Untuk RxS

x(t) = B(t)

R

x(t) =

A

(t).

B

(t)

=

A(t)

+

B(t)

Bentuk rangkaian adalah sbb :

S

R

1

0

X

C

B

A

clockALJABAR BOOLEAN

(1)

Pokok Bahasan :

1. Postulat Boolean

2. Teorema Aljabar Boolean

Tujuan Instruksional Khusus :

1.Mahasiswa dapat menjelaskan dan mengerti

Postulat dan Teorema Aljabar Boolean.

2.Mahasiswa dapat mengimplementasikan Aljabar Boolean

untuk penyederhanaan rangkaian.

3.Mahasiswa dapat menuliskan persamaan Boolean

untuk setiap gerbang logika dan rangkaian logika.

DASAR ALJABAR BOOLEAN

Dalam mengembangkan sistem Aljabar Boolean

Perlu memulainya dengan asumsi – asumsi

yakni Postulat Boolean dan Teorema Aljabar Boolean.

Postulat Boolean :

1.

0 . 0 = 0

2.

0 . 1 = 0

di turunkan dari fungsi AND

3.

1 . 0 = 0

4.

1 . 1 = 1

5.

0 + 0 = 0

6.

0 + 1 = 1

di turunkan dari fungsi OR

7.

1 + 0 = 1

8.

1 + 1 = 1

9.

0 = 1

diturunkan dari fungsi NOT

10.

1 = 0

TEOREMA ALJABAR BOOLEAN

T1. COMMUTATIVE LAW :

a. A + B = B + A

b. A . B = B . A

T2. ASSOCIATIVE LAW :

a. ( A + B ) + C = A + ( B + C )

b. ( A . B) . C = A . ( B . C )

T3. DISTRIBUTIVE LAW :

a. A. ( B + C ) = A . B + A . C

b. A + ( B . C ) = ( A+B ) . ( A+C )

T4. IDENTITY LAW:

a. A + A = A

b. A . A = A

T5. NEGATION LAW:

a.( A’ ) = A’

b. ( A’’ ) = A

T6. REDUNDANCE LAW :

a. A + A. B = A

b. A .( A + B) = A

T8. :

a. A’ + A = 1

b. A’ . A = 0

T9. :

a. A + A’ . B = A + B

b. A.( A’ + B ) = A . B

T7. :

a. 0 + A = A

b. 1 . A = A

c. 1 + A = 1

d. 0 . A = 0

10. DE MORGAN’S THEOREM:

a. (A + B ) = A . B

b. (A . B ) = A + B

PEMBUKTIAN TEOREMA T6(a)

TABEL KEBENARAN UNTUK A + A . B = A

A B

A . B

A + A.B

0 0

0 1

1 0

1 1

0

0

0

1

0

0

1

1

PEMBUKTIAN TEOREMA T9(a)

TABEL KEBENARAN UNTUK A + A’ B = A+B

A B

A’ . B A + A’B A + B

0 0

0 1

1 0

1 1

0

1

0

0

0

1

1

1

0

1

1

1

Aplikasi soal Aljabar Boole

Dari Postulat dan Teorema Aljabar Boolean diatas

tujuan utamanya adalah untuk penyederhanaan :

- Ekspresi Logika

- Persamaan Logika

- Persamaan Boolean (Fungsi Boolean)

yang inti-intinya adalah untuk mendapatkan

Rangkaian Logika(Logic Diagram) yang paling sederhana.

Contoh 1

Sederhanakan A . (A . B + C)

Penyelesaian

A . (A . B + C)

= A . A . B + A . C

(T3a)

= A . B + A . C

(T4b)

Contoh 2

Sederhanakan A’. B + A . B + A’ . B’

Penyelesaian

A’ . B + A . B + A’ . B’ = (A’ + A) . B + A’ . B’

(T3a)

= 1 . B + A’ . B’

(T8a)

= B + A’ . B’

(T7b)

= B + A’

(T9a)

Contoh 3

Sederhanakan A + A . B’ + A’ . B

Penyelesaian

A + A . B’ + A’ . B = (A + A . B’ ) + A’ . B

= A + A’ . B

(T6a)

Contoh 2

Sederhanakan A’. B + A . B + A’ . B’

Penyelesaian

A’ . B + A . B + A’ . B’ = (A’ + A) . B + A’ . B’

(T3a)

= 1 . B + A’ . B’

(T8a)

= B + A’ . B’

(T7b)

= B + A’

(T9a)

Contoh 3

Sederhanakan A + A . B’ + A’ . B

Penyelesaian

A + A . B’ + A’ . B = (A + A . B’ ) + A’ . B

= A + A’ . B

(T6a)

Soal Latihan I :

Sederhanakan ekspresi logika dibawah dengan

Aljabar Boolean :

1. AB’ + BC + C’A

2. A’(BC + AB + BA’)

3. ABC + AB +A

4. (A’ + AB ) (A’B)

Soal Latihan II :

BUATLAH TABEL KEBENARAN DARI PERSAMAAN

LOGIKA DIBAWAH:

(a) X . Y + X’ . Y + X’ . Y’ = X’ + Y

(b) A . B . C + A . C + B . C = A + B + C

(c) ( X’ . Y + Y’ . X ) + X . Y = ( X . Y’ )

FUNGSI CANNONICAL

Pokok Bahasan :

1. Komplemen, Duality, Lateral dan Term

2. Maxterm dan Minterm

3. Bentuk SOP dan POS

Tujuan Instruksional Khusus :

1.Mahasiswa dapat menjelaskan tentang komplemen,

maxterm dan minterm serta bentuk SOP dan POS

2.Mahasiswa dapat mengimplementasikan ke dalam bentuk

rangkaian.

3.Mahasiswa dapat menuliskan persamaan dan membuat

diagram logika dalam bentuk SOP dan POS.

FUNGSI BOOLEAN

PERSAMAAN ( EKSPRESI ) ALJABAR YANG DIBENTUK DARI VARIABEL

- VARIABEL BINER, OPERATOR BINER (OR DAN AND) , OPERATOR UNARY (NOT) , DAN TANDA SAMA DENGAN ( = ).

Contoh :

F = AB’C

F : fungsi Boolean

F : bernilai 1 jika A , B dan C = 1 ,

dan F=0 pada A , B’dan C yang

lain.

DUALITY :

METODE YANG BISA DILAKUKAN PADA PERSAMAAN BOOLEAN, DENGAN MENGGANTI NILAI ATAU OPERATOR :

‘0’ MENJADI ‘1’ ATAU ‘1’ MENJADI ‘0’

‘AND’ MENJADI ‘OR’ ATAU ‘OR’ MENJADI ‘AND’

CONTOH :

X . 1 = X duality-nya X + 0 = X

LATERAL & TERM

Lateral

= menyatakan input – input sebuah gerbang logika

Term

= menyatakan operasi yang dilakukan dalam sebuah gerbang

Contoh :

F = ABC’ + A’DE

Persamaan Boolean di atas mempunyai 5 input (ada 5 lateral :

A, B, C,D dan E)

Ada 5 Term ( AND untuk ABC’, AND untuk A’DE, NOT untuk C,

NOT untuk A dan OR untuk F), berarti ada 5 gerbang yang

diperlukan.

Komplemen dari sebuah fungsi didasarkan pada aturan De

Morgan dan prinsip Duality, dimana Fungsi NAND mempunyai

nilai yang sama dengan fungsi OR dari komplemen variabel

-variabelnya, dan Fungsi NOR mempunyai nilai yang sama

dengan fungsi AND dari komplemen variabel – variabelnya.

contoh :

F = (A+B+C)

maka

F’ = (A+B+C)’ = A’ . B’. C’

( A + B + C + D + ….. + Z )’ = A’ . B’ . C’ . D’… .Z’

( A . B . C . D…Z )’

= A’ + B’ + C’ + D’… +Z’

KOMPLEMEN

MINTERM DAN MAXTERM

n variabel yang membentuk operasi AND menghasilkan

suatu bentuk persamaan yang disebut

MINTERM

atau

standart product

contoh :

XYZ

A’BC

Minterm (dgn 3 variabel)

n variabel yang membentuk operasi OR menghasilkan

suatu bentuk persamaan yang disebut

MAXTERM

atau

standart sum

contoh :

X + Y + Z’

A’ + B’ + C’

1

1

1

1

7

0

0

1

1

6

1

1

0

1

5

0

0

0

1

4

0

1

1

0

3

0

0

1

0

2

1

1

0

0

1

1

0

0

0

0

Y

C

B

A

Map ValueA’B’C’

A’B’C

AB’C

ABC

(A+B’+C)

(A+B’+C’)

(A’+B+C)

(A’+B’+C)

MINTERM

MAXTERM

Tabel Kebenaran

MINTERM DAN MAXTERM

Bentuk SOP (Sum of Product) dari Tabel diatas adalah :

A’B’C’

A’B’C

AB’C

ABC

Y

(A,B,C)=

+

+

+

atau

Y

(A,B,C)=

Σ

( 0, 1, 5, 7)

B’

A

C’

A’

C

B’

B’

A

C

A

C

B

Y

Rangkaian

Bentuk SOP

Persamaan

Bentuk SOP

Bentuk POS (Product of Sum) dari Tabel diatas adalah :

Y

(A,B,C)= (A+B’+C) . (A+B’+C’) . (A’+B+C) . (A’+B’+C)

atau

Y

(A,B,C)=

π

( 2, 3, 4, 6)

A

B’

C’

A’

B

C

A’

B’

C

A

B’

C

Y

Rangkaian

Bentuk POS

Persamaan

Bentuk SOP

Buat Tabel Kebenaran dari fungsi di bawah ini dan ekspresikan setiap fungsi menjadi SOP dan POS : F = ( xy + z ).( y + xz ) Jawab : F = Σ ( 3, 5, 6, 7 ) F = π ( 0, 1, 2, 4 ) atau atau

F = x’yz + xy’z + xyz’ + xyz F = (x+y+z)(x+y+z’)(x+y’+z)(x’+y+z) ` SOP POS x y z F 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 1 0 0 0 0 0 1 1 0 0 1 1 0 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 1 1 1 0 1 1 1 1 0 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 1 (xy + z) (y + xz)

Ekspresikan persamaan dibawah ini menjadi Sum of Product ( SOP ) dan Product of Sum ( POS )

F(A, B, C, D ) = B’D + A’D + BD

Jawab :

Persamaan diatas bernilai ‘1’ untuk nilai BD = 01, AD = 01, BD = 11. Berdasarkan Tabel Kebenaran 4 variabel ( A, B, C, D ) maka output ‘1’

berlaku untuk minterm-minterm :

A’B’C’D, A’B’CD, A’BC’D, A’BCD, AB’C’D, AB’CD, ABC’D, ABCD SOP : F ( A, B, C, D ) = Σ( 1, 3, 5, 7, 9, 11, 13, 15 )

= A’B’C’D + A’B’CD + A’BC’D + A’BCD + AB’C’D + AB’CD + ABC’D + ABCD

POS : F ( A, B, C, D ) = π( 0, 2, 4, 6, 8, 10, 12, 14 )

= ( A+B+C+D)(A+B+C’+D)(A+B’+C+D)(A+B’+C+D’) (A’+B+C+D)(A’+B+C’+D)(A’+B’+C’+D)

LANGKAH - LANGKAH DI DALAM PROSES DISAIN :

f = u’xy + ux’y + uxy’ + uxy

f = u’xy + ux’y + uxy’ + uxy

= u’xy + uxy + ux’y + uxy + uxy’ + uxy = xy(u’ + u) + uy(x’ + x) + ux(y’ + y) = xy + uy + ux

y

x

u f

1. Buat Tabel Kebenarannya

2. Tulis minterm-minterm pada output yang bernilai ‘1’ 3. Tulis persamaan SOP untuk output

4. Sederhanakan persamaan output

5. Implementasikan dalam bentuk rangkaian

Latihan Soal I :

Buat ekspresi logika dibawah kedalam bentuk SOP dan

bentuk POS, serta gambar rangkaian logikanya :

(a)

F

(a, b, c, d )= AC’ + C’D + B’D’

(b)

F

(x, y, z )= X (Y’ +Z’) + Y+ Y’Z

Latihan Soal II :

Buat Tabel Kebenaran dari fungsi di bawah ini dan ekspresikan

setiap fungsi menjadi SOP dan POS , serta rangkaian

logikanya:

F1=A(C’D+BD’).D(A’C+BD’)

F2=(AC’+CD’).B(C’+AD)

BAB 5. MULTIVIBRATOR

Materi :

1. Dasar rangkaian Clock / Multivibrator

2. Jenis-jenis multivibrator

3. Laju Pengisian dan Pengosongan Kapasitor

4. Multivibrator Astabil dari IC 555

5. Multivibrator Monostabil dari IC 555

6. IC Multivibrator Monostabil 74121

7. Crystal Oscillator

1. PRINSIP DASAR MULTIVIBRATOR

1. Multivibrator merupakan osilator.

2. Sedangkan osilator adalah rangkaian elektronika yang menghasilkan perubahan keadaan

pada sinyal output.

3. Osilator dapat menghasilkan clock / sinyal pewaktuan untuk sistem digital seperti komputer.

4. Osilator juga bisa menghasilkan frekuensi dari pemancar dan penerima pada radio.

Pada dasarnya ada 3 tipe dari multivibrator, yaitu :

1. Multivibrator astabil

2. Multivibrator monostabil

3. Multivibrator bistabil

2. LAJU PENGISIAN DAN PENGOSONGAN KAPASITOR

Prinsip kerja dari sebuah rangkaian multivibrator dapat dijelaskan dengan

model pengisian dan pengosongan kapasitor yang berulang-ulang

E + _ 1 2 3 +_ R C VC SW Saat pengisian Saat pengosongan a VC Waktu b VC Waktu c

a. Rangkaian dasar RC saat pengisian

dan pengosongan tegangan kapasitor

b. Kurva saat pengisian

(

1

e

t/RC)

E

Δ

v

=

−

−Diketahui :

dimana :

Δ

v = perubahan tegangan kapasitor.

E = perbedaan tegangan antara tegangan kapasitor yang pertama dan tegangan total.

e = ketetapan yang bernilai log (2,718)

t = waktu saat pengisian kapasitor

R = resistansi , ohm

C = kapasitansi , farad

Dari penurunan persamaan di atas, akan didapatkan nilai waktu pengisian kapasitor,

t

, yaitu :

⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ − = E Δv 1 1 ln RC t

Contoh soal :

5 V + _ 1 2 3 R C 10 ΚΩ 0,047 μF1. Berdasarkan gambar di atas, anggap bahwa mulanya tegangan pada kapasitor berisi sebesar 1 V. Berapa lama waktu yang dibutuhkan setelah saklar dirubah dari posisi 2 ke posisi 1 dan

tegangan kapasitor menuju 3 V. Jawab : Δv = 3 V − 1 V = 2 V

E = 5 V − 1 V = 4 V,

kemudian gunakan persamaan t:

⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ − = E Δv 1 1 ln RC t

(

) (

)

⎟⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ − ⋅ = 4 2 1 1 ln F 0,047 10KΩ t μBentuk grafik dari tegangan kapasitor tersebut adalah:

t = 0,326 ms 0 0.2 0.4 0.6 0.8 1.0 1.0 2.0 3.0 4.0 5.0 0 Toward +5 V t = 0.326 ms E = 4.0 V v kap (V) v = 2.0 V

2. Berdasarkan gambar yang sama, anggap bahwa mulanya tegangan kapasitor berisi sebesar 4,2 V. Berapa lama waktu yang dibutuhkan jika saklar dirubah dari posisi 2 ke posisi 3 dan menyebabkan tegangan pada kapasitor drop menjadi 1,5 V.

Jawab : soal ini merupakan prinsip dari laju pengosongan tegangan pada kapasitor.

Δv = 4,2 V − 1,5 V = 2,7 V E = 4,2 V − 0 V = 4,2 V, gunakan persamaan t: ⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ − = E Δv 1 1 ln RC t

(

) (

)

⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎝ ⎛ − ⋅ = 4,2 2,7 1 1 ln F 0,047 10KΩ t μBentuk grafik dari tegangan kapasitor tersebut adalah :

t = 0,484 ms 0 0.2 0.4 0.6 0.8 1.0 1.0 2.0 3.0 4.0 0 Toward 0 V t = 0.484 ms E = 4.2 V v kap (V) Waktu (ms) v = 2.7 V 5.0

9 Multivibrator astabil adalah suatu rangkaian yang mempunyai dua state dan yang berosilasi secara

kontinu guna menghasilkan bentuk gelombang persegi atau pulsa di outputnya.

9 Pada multivibrator astabil, outputnya tidak stabil pada setiap state, tapi akan berubah secara kontinu dari 0 ke 1 dan dari 1 ke 0.

9 Prinsip ini sama dengan rangkaian osilator dan kondisi ini sering disebut dengan free running.

3. JENIS MULTIVIBRATOR

3a. MULTIVIBRATOR ASTABIL

Saat

pengisian Saat pengosongan

Vout = 5 V/ 0 V R

C 74HC14

multivibrator 8 Operasi dari osilator seperti pada gambar Rangkaian Multivibrator Astabil Schmitt Trigger adalah : 1. Tegangan supply IC dalam keadaan hidup / ON, sehingga Vkap adalah 0 V dan Vout akan tinggi /

sama dengan tegangan IC ≈ 5 V.

2. Kapasitor akan mulai mengisi yang sama dengan tegangan Vout.

3. Ketika Vkap menuju tegangan positif (VT+) dari schmitt trigger yaitu sebesar 5 V, maka output

dari Schmitt akan berubah menjadi rendah (≈ 0 V).

4. Karena Vout≈ 0 V, maka akan terjadi pengosongan kapasitor terhadap 0 V.

5. Ketika Vkap drop menuju tegangan negatif (VT-), maka output Schmitt akan kembali menjadi tinggi.

6. Kejadian seperti ini akan terus berulang, dimana saat pengisian tegangan kapasitor menjadi VT+ dan saat pengosongan tegangan kapasitor turun menjadi VT-.

Bentuk gelombang dari Vout dan Vkap dapat dilihat pada gambar di bawah.

0 V VT -VT + VO H V Vout Vkap VC C

multivibrator 9

Contoh Soal :

a. Buatlah bentuk gelombang dari rangkaian multivibrator astabil Schmitt trigger berdasarkan rangkaian Scmitt Trigger yang mempunyai spesifikasi CMOS 74HC14 (VCC = 5 V).

VOH = 5 V, VOL = 0 V

VT+ = 2,75 V, VT- = 1,67 V

b.Hitunglah waktu yang dibutuhkan saat pengisian tegangan kapasitor (tHI), pengosongan tegangan kapasitor (tLO), duty cycle dan rekuensi jika R = 10 KΩ dan C = 0,022 μF. Jawab:

a.Bentuk gelombang dari rangkaian Schmitt Trigger Multivibrator Astabil adalah :

0 V 1,67 V 2,75 V 5 V 5 V 0 V Vout Vkap

b. Untuk mencari tHI adalah :

ΔV = VT+ −

VT-ΔV = 2,75 V − 1,67 V = 1,08 V E = 5 V − 1,67 V = 3,33 V

tHI = RC ln = (10 KΩ).(0,022 μF) ln = 86,2 μs Untuk mencari tLO adalah :

ΔV = 2,75 V − 1,67 V = 1,08 V E = 2,75 V − 0 V = 2,75 V

tLO = RC ln = (10 KΩ).(0,022 μF) ln = 110 μs

Untuk mencari duty cycle (perbandingan antara lebar waktu saat kondisi high/tinggi dengan

total perioda suatu gelombang) adalah :

D = = = 0,439 = 43,9 %

Untuk mencari frekuensi adalah :

f = = = 5,10 KHz ⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ −ΔvE 1 1 ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎝ ⎛ −1,08V3,33V 1 1 ⎟⎟ ⎟ ⎠ ⎞ ⎜⎜ ⎜ ⎝ ⎛ −ΔvE 1 1 ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎝ ⎛ −1,08V2,75V 1 1 LO HI HI t t t + 86,286,2+110 LO HI t t 1 + 86,2 110 1 +

9 Multivibrator monostabil ini sering disebut dengan one shot.

9 Multivibrator monostabil adalah suatu rangkaian yang banyak dipakai untuk membangkitkan pulsa output yang lebarnya dan amplitudonya tetap.

9 Pulsa pada outputnya akan dihasilkan jika diberikan sebuah trigger pada inputnya.

9 Multivibrator monostabil ini dapat dibuat dengan menggunakan komponen-komponen tersendiri atau dapat diperoleh dalam paket terintegrasi.

3b. MULTIVIBRATOR MONOSTABIL

1 2 Q Q C R Vcc Pt. D 74HC00 A (Input trigger)Multivibrator monostabil yang dibangun dari gerbang NAND

Cara kerja rangkaian tersebut adalah :

1. Ketika tegangan diberikan, anggaplah bahwa dalam keadaan tinggi, Q = rendah, = tinggi dan pada C terjadi pengosongan tegangan, sehingga titik D = tinggi.

2. Jika diberikan pulsa negatif pada , maka Q menjadi tinggi dan = rendah.

3. Tegangan kapasitor akan berubah dengan segera dan titik D akan drop menjadi 0 V.

4. Karena pada titik d = 0 V, maka akan menyebabkan salah satu input pada gerbang 1 menjadi rendah, meskipun ditrigger menjadi tinggi. Oleh karena itu Q tetap dalam keadaan tinggi dan = rendah. 5. Beberapa lama kemudian akan terjadi pengisian kapasitor terhadap VCC. Ketika tegangan kapasitor

pada titik D menuju level tegangan input (VIH) dari gerbang 1 dalam keadaan tinggi, maka Q akan menjadi rendah dan menjadi tinggi.

6. Rangkaian kembali pada state yang stabil, sampai munculnya sinyal trigger dari . dan pada kapasitor terjadi lagi pengosongan tegangan ≈ 0 V.

Bentuk gelombang pada gambar dibawah menunjukkan karakteristik input/output dari rangkaian dan akan digunakan untuk membangun suatu persamaan untuk menentukan tw.

Pada kondisi state stabil ( = tinggi ), tegangan pada titik D akan sama dengan VCC.

A Q A Q A Q Q A Q

0 V VCC A VCC VCC V1H 0 V 0 V tw tw 2 1 3 4 5 Q D

3c. MULTIVIBRATOR BISTABIL

9 Multivibrator ini disebut juga dengan flip flop atau latch (penahan) yang mempunyai dua state.

9 Flip flop merupakan elemen dasar dari rangkaian logika sekuensial.

9 Output dari flip flop tergantung dari keadaan rangkaian sebelumnya.

9 Output dari flip flop terdiri dari Q dan . Dimana keadaan berlawanan dengan Q.

9 Salah satu contoh dari triggered flip flop adalah RS flip flop. Q

1 2 3 1 2 3

Flip flop

Diagram menunjukkan trigger pulsa 3 buah

input.Sesudah pulsa ke tiga outputnya tetap tinggi

4. MULTIVIBRATOR ASTABIL DARI IC 555

+ -+ Comp. 1 Comp. 2 RA RB 5 k 5 k 5 k 0.01 µF R S Q Output Output buffer (IOL=IOH=200ma) Discharge Transistor Reset GND VCC (4.8 V to 18 V) C Discharge Path Charging Path VCC FF Treshold Control Voltage Trigger Discharge 555 (7) (6) (5) (2) (8) (1) (4) (3)¾IC pewaktu 555 sudah banyak dikenal sebagai suatu IC pewaktu yang general purpose.

¾555 berasal dari tiga buah resistor yang terdapat pada rangkaian tersebut yang masing-masing nilainya adalah 5 KΩ.

¾Resistor ini akan membentuk rantai pembagi tegangan dari VCC ke ground.

¾Ada tegangan sebesar 1/3 VCC pada komparator 1 yang melewati resistor 5 KΩ yang pertama. dan tegangan 2/3 VCC pada komparator 2 yang melewati resistor 5 KΩ yang kedua.

¾Komparator disini berfungsi untuk menunjukkan tinggi atau rendahnya output berdasarkan perbandingan level tegangan analog pada input.

¾Jika input positif lebih besar dari input negatif maka outputnya akan bernilai tinggi.

¾Sebaliknya jika input positif lebih kecil dari input negatif maka outputnya akan bernilai rendah.

VC C - 1 .5 V Vo u t 0 .1 V 0 VC C 1 /3 VC C VC 2 /3 VC C tL O tH I VC trig g e r k o m p a ra to r 2 VC tr ig g e r k o m p a ra to r 1 τD= RB .C τ = ( R A + RB) .C C

Untuk menentukan

t

LO:

t

LO= 0,693 . R

B.C

Untuk menentukan

t

HI:

t

HI=

0,693 . (R

A+ R

B)C

Untuk menentukan Duty Cycle (D) dan frekuensi :

D =

f =

LO HI HI t t t + LO HI t t 1 +Contoh Soal :

Tentukan tHI, tLO, duty cycle dan frekuensi untuk rangkaian multivibrator 555 berdasarkan gambar di bawah ini :

R A RB 4.7 k 10 k 680 pF C VCC = 6 V 1 5 3 2 7 6 8 4 555 VOUT 0.01 µF Jawab : a. tLO = 0,693 . RBC = 0,693 . (10 KΩ) . 680 pF = 4,71 μs b. tHI = 0,693 .(RA+ RB)C = 0,693 . (4,7 KΩ + 10 KΩ) . 680 pF = 6,93 μs c. duty cycle = = = 59,5 % d. frekuensi = = = 85,9 KHz LO HI HI t t t + s s μ μ μ 71 , 4 93 , 6 s 6,93 + LO HI t t 1 + 71 , 4 93 , 6 1 +

RA 10 k Trigger C VCC 1 5 6 2 4 8 555 (Thres.) 3 7 (Disch.) 0.01µF

5. MULTIVIBRATOR MONOSTABIL DARI IC 555

Hubungan pin IC pewaktu 555 dengan

6. IC MULTIVIBRATOR MONOSTABIL 74121

T Q Q A1 A2 B Rint 2 kΩ Rext Cext 1 5 4 3 11 10 9 6 Blok Diagram IC 74121 A1 A2 B Q Q L X H L H X L H L H X X L L H H H X L H H H H H H L X X L Tabel FungsiLebar pulsa output :

2

ln

ext ext wR

C

t

=

Contoh Soal :

Disain sebuah rangkaian menggunakan 74121 yang mengubah sebuah gelombang kotak 50 kHz, 80 % duty cycle, ke gelombang kotak 50 kHz, 50 % duty cycle.

Jawab :

Pertama kali, gambarkan gelombang kotak asal :

kHz t 50 1 = = 20 μs, t HI = 80 % x 20 μs = 16 μs 16 μs 20 μs 4 μs T Q Q A1 A2 B OUT Rext Cext 1 1 IN VCC 14,4 kΩ 0,01 μF 16 μs 4 μs IN (A1) 10 μs 10 μs OUT (Q) ) 2 ln( ext ext w R C t = ) 693 , 0 ( 10μs = RextCext s C Rext ext =14,4μ F s Rext μ μ 001 , 0 4 , 14 =

Anggap Cext = 0,001 μF, maka :

1

Karnaugh MAP (K-Map)

Pokok Bahasan :

1. K-map 2 variabel

2. K-map 3 variabel

3. K-map 4 variabel

4. Penyederhanaan rangkaian dengan k-map

Tujuan Instruksional Khusus :

1.Mahasiswa dapat menerangkan dan memahami cara

membuat k-map 2, 3, 4 variabel.

2.Mahasiswa dapat menerangkan dan memahami cara

peng-cover-an minterm dalam sebuah k-map..

3.Mahasiswa dapat menyederhanakan persamaan logika

melalui metode k-map.

Karnaugh Map (K-Map)

•Suatu peralatan grafis yang digunakan untuk menyederhanakan

persamaan logika atau mengkonversikan sebuah tabel kebenaran

menjadi sebuah rangkaian logika.

•Salah satu metode yang paling mudah untuk penyederhanaan

Rangkaian Logika.

3 Map Value

A

B

Y

0

0

0

A’B’

1

0

1

A’B

2

1

0

AB’

3

1

1

AB

Karnaugh Map 2 Variabel :

( A dan B )

Tabel Kebenaran

A

AB

3A’B

1AB’

2A’B’

00

1

0

1

B

Model II

AB

3AB’

2A’B

1A’B’

00

1

0

1

A

B

Model I

Map Value

Desain Pemetaan K- Map 2

Variabel

0

1

0

1

A

B

A’

A

B’

B

5