PEMBALIK KOMPLEKS 8-BIT BERBASIS

PENGALI DAN PEMBAGI SEKUENSIAL

MENGGUNAKAN FPGA XILINX

SPARTAN 3E UNTUK PENYAMAAN

KANAL OFDM

Nicolas Arya Kuntawijaya

1, Budi Setiyanto

2, Addin Suwastono

3Abstract— OFDM receiver needs a channel equalizer

(CE) to gain similarity between received signals and transmitted signals. CE multiplies received signal with a weighting factor which results a signal similar with transmitted signal. Weighting factor is reciprocal of the channel estimator output, which become the multiplier factor in CE.

This research offered a reciprocal circuit to process the output from estimator and interpolator blocks yield OFDM CE weighting factor. There are two reciprocal circuit designs in this final assignment. They are reciprocal without internal bit scaling (system A), and reciprocal with internal bit scaling (system B). Reciprocal circuits in this research is four sub-channels circuit, with sequential multiplier and sequential divider. The circuits are designed with VHDL (Very high speed integrated circuit Hardware Description Language) and Xilinx ISE 12i sofware.

Design result and simulation show that system A and system B work properly, although there are few errors as result of binary number and internal bit scaling used in both systems. Both systems successfully implemented on FPGA Xilinx Spartan 3E XCS3S500E. System B uses fewer resources than system A, but less accurate.

Intisari— Sistem penerima OFDM membutuhkan

penyama kanal (channel equalizer, CE) agar memperoleh isyarat terima yang mirip dengan isyarat kirim. CE bekerja dengan cara mengalikan isyarat terima dengan suatu faktor pembobot yang menghasilkan isyarat mirip isyarat kirim. Faktor pembobot adalah kebalikan (resiprokal) keluaran estimator dan interpolator OFDM, yang menjadi faktor pengali pada CE.

Dalam penelitian ini dirancang pembalik kompleks (blok resiprokal) untuk mengolah keluaran estimator dan interpolator, sehingga menghasilkan faktor pembobot pada CE OFDM. Terdapat dua jenis pembalik kompleks yang dirancang, yakni pembalik kompleks tanpa penyekala internal (sistem A) dan pembalik kompleks dengan penyekala internal (sistem B). Rangkaian yang dirancang merupakan rangkaian empat subkanal, dengan komponen penguadrat dan pembagi yang bekerja secara sekuensial. Perancangan pembalik kompleks menggunakan VHDL (Very high speed

integrated circuit Hardware Description Language), dengan perangkat lunak Xilinx ISE 12i.

Hasil perancangan dan simulasi menunjukkan bahwa sistem A dan sistem B dapat bekerja dengan baik, walaupun terdapat sedikit galat perhitungan yang disebabkan penggunaan bilangan biner dan penggunaan penyekala internal. Kedua sistem rancangan dapat diimplementasi pada FPGA Xilinx Spartan 3E XC3S500E. Rancangan sistem B terbukti lebih hemat daripada sistem A, namun tidak lebih akurat daripada sistem A.

Kata Kunci— OFDM, Pembalik kompleks.

I. PENDAHULUAN

Kebutuhan manusia terhadap komunikasi yang bersifat pita luas (broadband) yang semakin meningkat

menyebabkan munculnya teknologi komunikasi

ganerasi keempat, yaitu WIMAX (Worldwide

Interoperability for Microwave Access) dan LTE (Long Term Evolution). Keduanya menggunakan teknologi OFDM (Orthogonal Frequency Division Multiplexing) yang dalam aplikasinya unggul karena dapat menghemat penggunaan lebar pita frekuensi.

Pada skripsi sebelumnya sudah dirancang pembalik kompleks, namun berupa untai kombinatorial [1].

Skripsi ini memaparkan hasil penelitian tentang perancangan untai pembalik (resiprokal) kompleks dengan komponen penguadrat dan pembagi berupa untai sekuensial. Keluaran untai pembalik kompleks merupakan masukan dari CE, namun tentang CE tidak dibahas dalam skripsi ini. Keluaran untai pembalik kompleks merupakan faktor pembobot (weighting factor, WF) untuk CE.

II. DASAR TEORI

Selain efisiensi penggunaan spektrum yang baik, OFDM juga memiliki keunggulan diantaranya tahan terhadap pudaran lintasan jamak (multipath fading) dan tahan terhadap interferensi pengguna jamak (multiuser interference) [2]. Ortogonalitas membuat transmisi dapat dipancarkan secara simultan pada subpembawa dalam jarak antar subkanal yang sangat rapat tanpa menimbulkan interferensi satu sama lain. Dengan kata lain aliran data yang besar dibagi-bagi

1Mahasiswa, Jurusan Teknik Elektro dan Teknologi

Informasi Fakultas Teknik Universitas Gadjah Mada, Dadapan, Godean, Sleman,Yogyakarta 55564

2, 3Dosen Jurusan Teknik Elektro dan Teknologi

menjadi aliran data yang lebih rendah, kemudian aliran data ini memodulasi subpembawa yang saling ortogonal [3].

OFDM diimplementasikan menggunakan pemetaan

Quadrature Amplitude Modulation (QAM) di setiap subkanal. Simbol QAM kemudian diubah menjadi simbol OFDM. Dalam proses pemetaan QAM, bit-bit dibagi menjadi dua bagian yaitu Inphase dan

Quadrature. Isyarat pembawa untuk komponen I dan Q berbeda fase 90o [1].

Isyarat yang diterima pada umumnya berbeda dengan isyarat yang dikirim, karena propagasi isyarat dari pengirim ke penerima melewati kanal yang memiliki watak yang tidak ideal. Oleh karena itu diperlukan penerapan CE untuk memulihkan isyarat terima. Penerapan CE juga dapat memulihkan isyarat yang terkena pudaran selektif frekuensi. Subkanal yang bersifat pita sempit memungkinkan hal ini, karena sub kanal pita sempit jika terkena pudaran selektif frekuensi hanya mengakibatkan pudaran yang bersifat datar (flat fading). Pudaran yang bersifat datar yang terjadi pada subkanal dapat diatasi dengan mengatur faktor pembobot pada CE. Pengaturan faktor pembobot dilakukan dengan proses estimasi kanal yang bersangkutan, lalu mencari nilai resiprokal dari nilai estimasi kanal. Nilai resiprokal dari keluaran estimator merupakan faktor pembobot pada CE. Berikut merupakan persamaan untuk menghitung nilai resiprokal.

Gambar 1. Pembalik satu subkanal

(1)

FPGA yang dipakai adalah seri XCS500E yang terdapat pada modul Spartan 3E starter kit. Seri ini memiliki 4.656 buah slice. Perancangan menggunakan bahasa VHDL dan menggunakan perangkat lunak Xilinx ISE 12i.

III. HASIL DAN PEMBAHASAN A. Prinsip Perancangan

Blok pembalik kompleks 8-bit atau blok resiprokal dirancang secara modular berjenjang, sehingga blok resiprokal tersusun atas blok – blok yang lebih kecil. Blok – blok penyusun blok resiprokal diantaranya adalah penguadrat, penjumlah kuadrat, penegatif, dan pembagi. Jika semua blok ini dirangkai, maka akan terbentuk blok resiprokal satu subkanal. Blok resiprokal sebagai satu kesatuan tersusun atas blok resiprokal satu subkanal yang dirangkai secara paralel sehingga membentuk blok resiprokal empat subkanal.

Masukan dan keluaran sistem merupakan bilangan real dan imajiner dengan format bilangan magnitude bertanda (sign magnitude). Sistem yang dirancang bekerja seperti sebuah konverter yang keluarannya sebanding dengan persamaan (1), yang secara numeris memungkinkan keluaran yang tidak sesuai dengan persamaan.

Terdapat dua buah sistem yang dirancang, yakni blok resiprokal tanpa penyekala internal (sistem A), dan blok resiprokal dengan penyekala internal. Penyekala internal adalah sebuah pemangkas bit keluaran blok penguadrat. Penggunaan penyekala internal bertujuan mengurangi jumlah bit yang harus

diproses oleh sistem, dengan harapan dapat

menghemat sumber daya yang digunakan dan mengurangi tunda waktu sistem.

B. Blok Resiprokal tanpa Penyekala Internal (Sistem A)

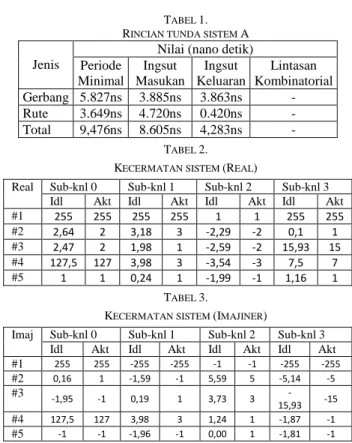

Blok resiprokal sistem A sebagai satu kesatuan merupakan blok resiprokal empat subkanal yang disajikan dalam diagram kotak Gambar 2, yang membutuhkan 2.279 slice (1.544 flip – flop dan 4.382 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 1. Satu siklus operasi dirancang membutuhkan 63 detak, sehingga tunda sekuensial yang dibutuhkan sebesar 63 × 9,476 ns = 596,988 ns. Sehingga, latensi satu siklus perhitungan adalah (596,988 ns + 8.605 ns + 4,283 ns) ns = 609,876 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (Akt) terhadap keluaran ideal (Idl), yang tersaji pada Tabel 2 dan Tabel 3.

Gambar 2. Diagram kotak blok resiprokal sistem A TABEL 1.

RINCIAN TUNDA SISTEM A

Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 5.827ns 3.885ns 3.863ns - Rute 3.649ns 4.720ns 0.420ns - Total 9,476ns 8.605ns 4,283ns - TABEL 2.

KECERMATAN SISTEM (REAL)

Real Sub-knl 0 Sub-knl 1 Sub-knl 2 Sub-knl 3 Idl Akt Idl Akt Idl Akt Idl Akt

#1 255 255 255 255 1 1 255 255 #2 2,64 2 3,18 3 -2,29 -2 0,1 1 #3 2,47 2 1,98 1 -2,59 -2 15,93 15 #4 127,5 127 3,98 3 -3,54 -3 7,5 7 #5 1 1 0,24 1 -1,99 -1 1,16 1 TABEL 3.

KECERMATAN SISTEM (IMAJINER)

Imaj Sub-knl 0 Sub-knl 1 Sub-knl 2 Sub-knl 3 Idl Akt Idl Akt Idl Akt Idl Akt

#1 255 255 -255 -255 -1 -1 -255 -255 #2 0,16 1 -1,59 -1 5,59 5 -5,14 -5 #3 -1,95 -1 0,19 1 3,73 3 -15,93 -15 #4 127,5 127 3,98 3 1,24 1 -1,87 -1 #5 -1 -1 -1,96 -1 0,00 1 -1,81 -1

C. Sistem A Satu Subkanal

Blok resiprokal sistem A satu subkanal memiliki diagram kotak seperti yang ditunjukkan oleh Gambar 3.

Gambar 3. Diagram kotak sistem A satu subkanal

Sistem A satu subkanal menggunakan 571 slice

(386 flip – flop dan 1.097 LUT empat masukan). Rincian estimasi waktu tunda disajikan pada Tabel 4. Satu siklus operasi dirancang membutuhkan 63 detak, sehingga total tunda sekuensial yang dibutuhkan sebesar 63 × 9,476 ns = 596,988 ns. Sehingga, latensi satu siklus perhitungan adalah (596,988 ns + 7.462 ns + 4,283 ns) ns = 608,733 ns.

Pembalik sistem A satu subkanal tersusun atas beberapa komponen penyusun seperti yang disajikan oleh Gambar 4.

Gambar 4. Komponen penyusun sistem A TABEL 4.

RINCIAN TUNDA SISTEM Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerba ng 5.827ns 4.663ns 3.863ns - Rute 3.649ns 2.799ns 0.420ns - Total 9.476ns 7.462ns 4.283ns -

1) Blok Penguadrat: Blok penguadrat memiliki diagram kotak yang disajikan oleh Gambar 5.

Gambar 5. Diagram kotak penguadrat real

Blok penguadrat membutuhkan 90 slice (50 flip – flop dan 168 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 5. Satu siklus operasi dirancang membutuhkan 9 detak, sehingag total tunda sekuensial yang dibutuhkan sebesar 9 × 6.517 ns = 58,653 ns. Sehingga, latensi satu siklus perhitungan adalah (58,653 ns + 7,004 ns + 4,283 ns) ns = 69,94 ns. Kecermatan ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel 6.

TABEL 5. RINCIAN TUNDA SISTEM Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 3.750ns 4.663ns 3.863ns - Rute 2.767ns 2.341ns 0.420ns - Total 6.517ns 7.004ns 4.283ns - TABEL 6. KECERMATAN SISTEM Kombinasi Penguadrat Ideal Sebenarnya 255 65025 65025 128 16384 16384 64 4096 4096 32 1024 1024 2 4 4 1 1 1 -255 65025 65025 -100 10000 10000

2) Blok penegatif: Blok penegatif memiliki diagram kotak yang disajikan oleh Gambar 6.

Gambar 6. Diagram kotak penegatif

Blok penegatif membutuhkan 1 slice (1 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 7. Penegatif bekerja secara kombinatorial, sehingga tunda yang ditemukan merupakan tunda kombinatorial yakni sebesar 6,034 ns.

TABEL 7. RINCIAN TUNDA WAKTU Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang - - - 5.194ns Rute - - - 0.840ns Total - - - 6.034ns

3) Blok penjumlah kuadrat: Blok penegatif memiliki diagram kotak yang disajikan oleh Gambar 7.

Gambar 7. Diagram kotak penjumlah kuadrat

Blok penguadrat membutuhkan 22 slice (39 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 8. Blok penjumlah kuadrat bekerja secara kombinatorial, sehingga tunda yang ditemukan merupakan tunda kombinatorial yakni sebesar 28,339 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel 9.

TABEL 8. RINCIAN TUNDA WAKTU Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang - - - 17.866ns Rute - - - 10.473ns Total - - - 28.339ns

TABEL 9. KECERMATAN SISTEM Masukan Keluaran 𝑥2 𝑦2 Ideal Aktual 100 100 200 200 144 400 544 544 22500 30625 53125 53125 39601 1 39602 39602 20736 52900 73636 73636 255 255 510 510

4) Blok pembagi: Blok pembagi memiliki diagram kotak yang disajikan oleh Gambar 8.

Gambar 8. Diagram kotak blok pembagi

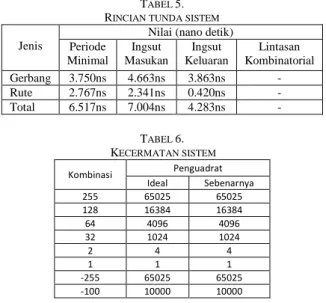

Blok pembagi membutuhkan 213 slice (147 flip – flop dan 415 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 10. Satu siklus operasi dirancang membutuhkan 36 detak, sehingga total tunda sekuensial yang dibutuhkan sebesar 36 × 7.784 ns = 280,224 ns. Sehingga, latensi satu siklus perhitungan adalah (280,224 ns + 5.790 ns + 4.283 ns) ns = 290,297 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel 11.

TABEL 10. RINCIAN TUNDA SISTEM

Jenis

Nilai (nano detik)

Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 5.352ns 3.181ns 3.863ns - Rute 2.432ns 2.609ns 0.420ns - Total 7.784ns 5.790ns 4.283ns - TABEL 11. KECERMATAN SISTEM Masukan Keluaran

Pembilang Penyebut Ideal Aktual

1 2 255 255 192 37.008 2,645874 2 127 26.129 2,47467 2 2 8 127,5 127 255 130.050 0,996094 1 1 2 255 255

Diagram kotak penyusun blok pembagi yakni

komponen pembagi dan penyekala pembagi

ditunjukkan secara berurutan oleh Gambar 9 dan Gambar 10.

Gambar 9. Diagram kotak komponen pembagi

Gambar 10. Diagram kotak penyekala pembagi

D. Blok Resiprokal dengan Penyekala Internal (Sistem B)

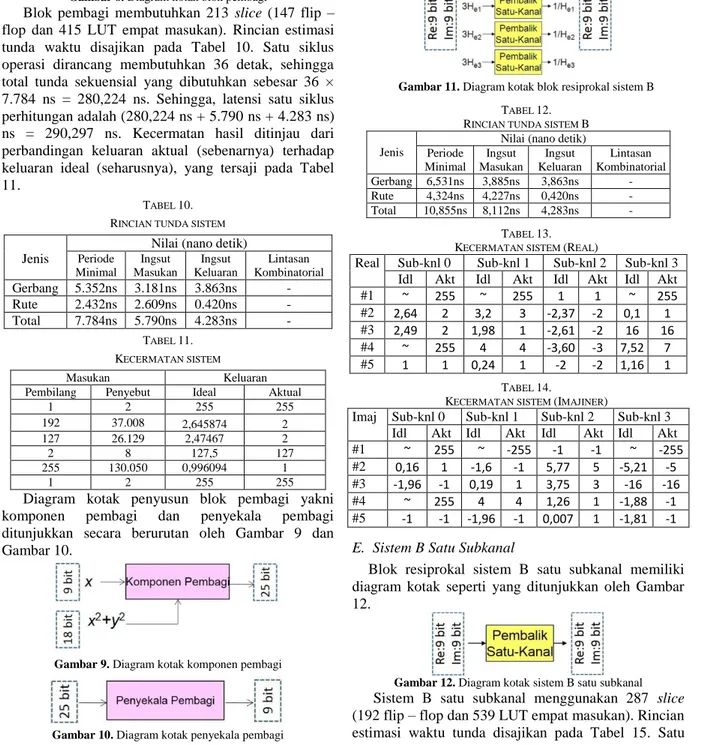

Blok resiprokal sistem B sebagai satu kesatuan merupakan blok resiprokal empat subkanal yang disajikan dalam diagram kotak Gambar 11, yang membutuhkan 1.136 slice (784 flip – flop dan 2.133 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 12. Satu siklus operasi dirancang membutuhkan tunda 23 detak, sehingga total tunda sekuensial yang dibutuhkan sebesar 23 × 10,855 ns = 249,665 ns. Sehingga, latensi satu siklus perhitungan adalah (249,665 ns + 8,112 ns + 4,283 ns) ns = 262,06 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel 13 dan Tabel 14.

Gambar 11. Diagram kotak blok resiprokal sistem B TABEL 12.

RINCIAN TUNDA SISTEM B Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 6,531ns 3,885ns 3,863ns - Rute 4,324ns 4,227ns 0,420ns - Total 10,855ns 8,112ns 4,283ns - TABEL 13. KECERMATAN SISTEM (REAL)

Real Sub-knl 0 Sub-knl 1 Sub-knl 2 Sub-knl 3 Idl Akt Idl Akt Idl Akt Idl Akt

#1 ~ 255 ~ 255 1 1 ~ 255 #2 2,64 2 3,2 3 -2,37 -2 0,1 1 #3 2,49 2 1,98 1 -2,61 -2 16 16 #4 ~ 255 4 4 -3,60 -3 7,52 7 #5 1 1 0,24 1 -2 -2 1,16 1 TABEL 14.

KECERMATAN SISTEM (IMAJINER)

Imaj Sub-knl 0 Sub-knl 1 Sub-knl 2 Sub-knl 3 Idl Akt Idl Akt Idl Akt Idl Akt

#1 ~ 255 ~ -255 -1 -1 ~ -255

#2 0,16 1 -1,6 -1 5,77 5 -5,21 -5

#3 -1,96 -1 0,19 1 3,75 3 -16 -16

#4 ~ 255 4 4 1,26 1 -1,88 -1

#5 -1 -1 -1,96 -1 0,007 1 -1,81 -1

E. Sistem B Satu Subkanal

Blok resiprokal sistem B satu subkanal memiliki diagram kotak seperti yang ditunjukkan oleh Gambar 12.

Gambar 12. Diagram kotak sistem B satu subkanal

Sistem B satu subkanal menggunakan 287 slice

(192 flip – flop dan 539 LUT empat masukan). Rincian estimasi waktu tunda disajikan pada Tabel 15. Satu

siklus operasi dirancang membutuhkan 23 detak, sehingga total tunda sekuensial yang dibutuhkan sebesar 23 × 10,748 ns = 247,204 ns. Sehingga, latensi satu siklus perhitungan adalah (247,204 ns + 7,515 ns + 4,283 ns) ns = 259,002 ns.

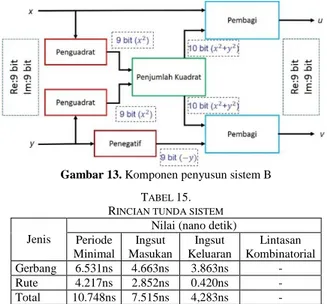

Pembalik sistem B satu subkanal tersusun atas beberapa komponen penyusun seperti ayng disajikan oleh Gambar 13.

Gambar 13. Komponen penyusun sistem B TABEL 15.

RINCIAN TUNDA SISTEM Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 6.531ns 4.663ns 3.863ns - Rute 4.217ns 2.852ns 0.420ns - Total 10.748ns 7.515ns 4,283ns -

1) Blok Penguadrat: Blok penguadrat memiliki diagram kotak yang disajikan oleh Gambar 14.

Gambar 14. Diagram kotak penguadrat real

Blok penguadrat membutuhkan 100 slice (54 flip – flop dan 185 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 16. Satu siklus operasi dirancang membutuhkan 9 detak, sehingga total tunda sekuensial yang dibutuhkan sebesar 9 × 7.649 ns = 68,841 ns. Sehingga, tunda satu siklus perhitungan adalah (68,841 ns + 6.704ns + 14.193ns) ns = 89,738 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel 17.

TABEL 16. RINCIAN TUNDA SISTEM Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 4.419ns 4.663ns 9.565ns - Rute 3.230ns 2.041ns 4.628ns - Total 7.649ns 6.704ns 14.193ns - TABEL 17. KECERMATAN SISTEM Kombinasi Penguadrat Ideal Sebenarnya 255 255 255 128 64 64 64 16 16 32 4 4 2 0 0 1 0 0 -100 39 39

Blok penguadrat tersusun atas blok pengali dan blok penyekala internal yang ditunjukkan oleh Gambar 15 dan 16 Penyekala internal bekerja dengan cara memangkas panjang bit dari 17 bit menjadi 9 bit, sehingga menyebabkan galat penyekalaan yang menghasilkan galat pada hasil akhir. Ketidakakuratan hasil akhir akibat galat penyekalaan ditunjukkan oleh Tabel 18.

Gambar 15. Diagram kotak pengali

Gambar 16. Diagram kotak penyekala kuadrat

TABEL 18. GALAT HASIL AKHIR

Masukan Keluaran Akt (Sistem B) Keluaran Akt (Sistem A) Real Imajiner Real Imajiner Real Imajiner

2 -2 255 255 127 127

64 -64 4 4 3 3

-255 -1 -2 1 -1 1

16 16 16 -16 15 -15

2) Blok penegatif: Blok penegatif memiliki diagram kotak yang disajikan oleh Gambar 17.

Gambar 17. Diagram kotak penegatif

Blok penegatif membutuhkan 1 slice (1 LUT empat masukan). Rincian estimasi tunda disajikan pada Tabel 19. Blok penegatif bekerja secara kombinatorial, sehingga tunda yang ditemukan merupakan tunda kombinatorial yakni sebesar 6,034 ns.

TABEL 19. RINCIAN TUNDA WAKTU Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang - - - 5.194ns Rute - - - 0.840ns Total - - - 6.034ns

3) Blok penjumlah kuadrat: Blok penegatif memiliki diagram kotak yang disajikan oleh Gambar 18.

Gambar 18. Diagram kotak penjumlah kuadrat

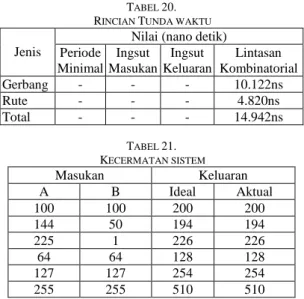

Blok penguadrat membutuhkan 9 slice (16 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 20. Blok penjumlah kuadrat bekerja secara kombinatorial, sehingga tunda yang ditemukan merupakan tunda kombinatorial yakni sebesar 14,942 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel 21.

TABEL 20. RINCIAN TUNDA WAKTU

Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang - - - 10.122ns Rute - - - 4.820ns Total - - - 14.942ns TABEL 21. KECERMATAN SISTEM Masukan Keluaran A B Ideal Aktual 100 100 200 200 144 50 194 194 225 1 226 226 64 64 128 128 127 127 254 254 255 255 510 510

4) Blok pembagi: Blok pembagi memiliki diagram kotak yang disajikan oleh Gambar 19.

Gambar 19. Diagram kotak blok pembagi

Blok pembagi membutuhkan 46 slice (48 flip – flop dan 75 LUT empat masukan). Rincian estimasi tunda waktu disajikan pada Tabel 22. Satu siklus operasi dirancang membutuhkan 11 detak, sehingga total tunda sekuensial yang dibutuhkan sebesar 11 × 5,428 ns = 59,708 ns. Sehingga, latensi satu siklus perhitungan adalah (59,708 ns + 7,163 ns + 4,283 ns) ns = 71,154 ns. Kecermatan hasil ditinjau dari perbandingan keluaran aktual (sebenarnya) terhadap keluaran ideal (seharusnya), yang tersaji pada Tabel23

TABEL 22. RINCIAN TUNDA SISTEM

Jenis

Nilai (nano detik) Periode Minimal Ingsut Masukan Ingsut Keluaran Lintasan Kombinatorial Gerbang 3.011ns 3.885ns 3.863ns - Rute 2.417ns 3.278ns 0.420ns - Total 5.428ns 7.163ns 4.283ns - TABEL 23. KECERMATAN SISTEM Kombinasi Masukan Keluaran Presisi Keluaran Modifikasi Pembilang Penyebut Ideal Ideal Sebenarnya

1 192 145 1,324 2,6482 2 2 128 80 1,6 3,2 3 3 64 17 3,7647 7,5294 7 4 16 2 8 16 16 5 255 510 0,5 1 1 IV. KESIMPULAN

Tabel-tabel kecermatan sistem menunjukkan seluruh blok yang ada dalam blok resiprokal sistem A dan sistem B telah bekerja dengan baik. Perbedaan hasil perhitungan aktual dan ideal disebabkan oleh

ketidakmampuan bilangan biner dalam representasi bilangan pecahan, serta penggunaan penyekala internal yang menyebabkan hilangnya sebagian porsi bilangan. Rancangan pembalik kompleks sistem A dan sistem B menggunakan sumber daya FPGA yang lebih sedikit dari kapasitas sumber daya total FPGA Xilinx Spartan 3E XC3S500E, sehingga dapat diimplementasikan kedalam FPGA Xilinx Spartan 3E starter kit.

Rancangan blok resiprokal dengan pengali dan pembagi yang bekerja secara sekuensial membutuhkan sumber daya yang lebih sedikit yakni 2.279 slice,

dibanding blok resiprokal yang seluruh komponennya bekerja secara kombinatorial milik Hendra sebesar 33.272 slice [2]. Namun memiliki waktu tunda yang lebih lama yakni 609,876 ns yang tersusun atas tunda 63 clock, offset in dan offset out, dibanding rancangan Hendra yang hanya membutuhkan waktu tunda sebesar 83,430 ns yang tersusun atas tunda kombinatorial saja.

Rancangan pembalik kompleks sistem B (blok resiprokal sistem B) berhasil mengurangi tunda waktu yang dimiliki oleh sistem A, menjadi hanya 240,350 ns. Sumber daya yang digunakan juga lebih sedikit dibanding yang digunakan oleh sistem A, yakni hanya 1.136 slice.

Penggunaan penyekala internal (penyekala keluaran penguadrat) mengakibatkan galat penyekalaan yang disebabkan karena proses pemotongan bit yang menyebabkan sebagian porsi bilangan hilang.

REFERENSI

[1] Hendra, F., 2012, Perancangan Untai Kombinatorial Berbasis VHDL Dengan FPGA Xilinx Spartan-3E Atas Model Interpolasi Linear Untuk Estimasi Kanal OFDM. Skripsi S1, JTETI FT UGM. Tidak dipublikasikan.

[2] Jiang, T., Song, L., Zhang, Y.,2010, Orthogonal Frequency Division Multiple Access Fundamentals and Applications, USA : CRC Press.

[3] R. W. Chang, Synthesis of band-limited orthogonal signals for multichannel data transmission, Bell System Technical Journal, 45, 1775–1796, 1966.