BAB I

Rangkaian Sekuensial (2) Deskripsi

Pada bab ini akan dibahas tentang aplikasi elemen flip-flop pada counter dan register serta clock mode, pulse mode, dan level mode.

Manfaat

Memberikan kompetensi tentang rangkaian sekuensial yakni counter dan elemen flip-flop dan pemilihan clock mode, pulse mode, dan level mode.

Relevansi

Counter dan register merupakan rangkaian yang banyak digunakan dalam dunia elektronika sebagai elemen penyimpan memori

Learning Outcome

Mampu memahami aplikasi rangkaian sekuensial pada elemen elektronika seperti : Counter, Register Geser

Mampu menjelaskan Clock mode, pulse mode dan level mode

Materi I. Counter

Counter (Pencacah) adalah rangkaian yang mencacah pulsa tegangan, counter adalah rangkaian sekuensial yang dibentuk dari gabungan rangkaian kombinasional dan flip-flop. Pencacah dibangun menggunakan flip-flop, dimana N buah flip-flop yang dibangun menghasilkan 2 ^ N keadaan yang berbeda. Secara umum dapat dikemukakan bahwa dengan N buah FF yang disusun secara serial akan menghasilkan frekuensi keluaran pada FF terakhir sebesar FN yang dapat dituliskan sebagai berikut :

adalah frekuensi detak masukan mula-mula, sehingga membentuk rangkaian

pembagi frekuensi. Secara umum, ada 2 jenis pencacah yaitu : a. Pencacah Sinkron

Perubahan semua output FF terjadi secara serempak sesaat setelah terjadi pulsa input. Pulsa input dimasukkan pada input clock dari setiap FF. Perubahan

output dari flip-flop terjadi secara bersamaan sesaat setelah pulsa input dimasukkan. Flip-flop paling depan berkedudukan sebagai LSB, yang dikenai J dan K = 1 secara permanen. Saluran J dan K pada FF yang lain dikendalikan melalui kombinasi output FF yang sesuai. Pencacah sinkron lebih cepat karena dapat menghitung frekuensi detak yang lebih tinggi untuk selang waktu yang sama. Untuk merancang pencacah sinkron langkah-langkahnya adalah sebagai berikut :

1. Digunakan tabel transisi siklus pencacahan dan tabel eksitasi FF yang digunakan.

2. Dari kedua tabel tersebut, dibentuk tabel kebenaran untuk menentukan fungsi saluran masukan terhadap keluarannya.

3. Dibuat peta karnaughnya untuk menghasilkan Fungsi Logikanya. 4. Dari persamaan logika tersebut dapat dibuat rangkaian pencacah

sinkron menggunakan flip-flop.

Tabel Eksitasi JKFF terlihat pada tabel 1.18. Tabel ini digunakan untuk menentukan persamaan input dan output bagi counter.

Tabel 1.18. Tabel Eksitasi JKFF Qn Qn+1 J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Berikut ini cara merancang pencacah sinkron modulo 8 menggunakan 3 buah Flip-flop JK. Tabel Representasi saluran masukan (J dan K) terhadap saluran output (Q), setiap Flip-flop terlihat pada table 1.19

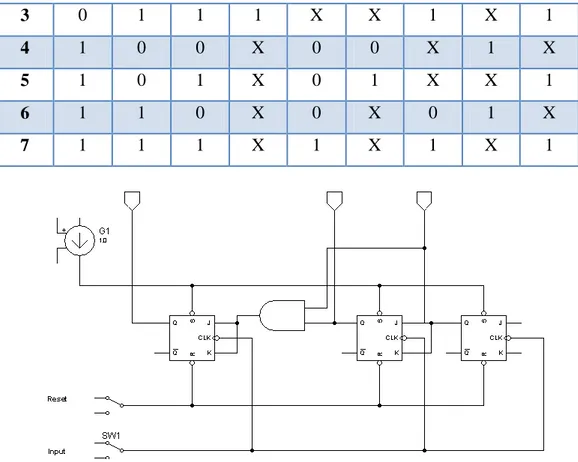

Tabel 1.19. Tabel Representasi Input dan Output Flip-Flop No. Baris QA QB QC JA KA JB KB JC KC 0 0 0 0 0 X 0 X 1 X 1 0 0 1 0 X 1 X X 1 2 0 1 0 0 X X 0 1 X

3 0 1 1 1 X X 1 X 1

4 1 0 0 X 0 0 X 1 X

5 1 0 1 X 0 1 X X 1

6 1 1 0 X 0 X 0 1 X

7 1 1 1 X 1 X 1 X 1

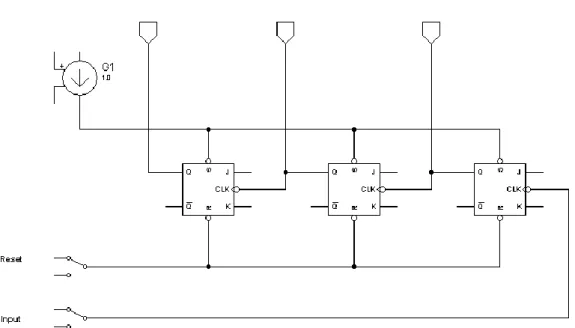

Gambar 1.27. Rangkaian Pencacah Sinkron modulo 8

Untuk menentukan JA, KA, , JB , KB , JC, KC sebagai fungsi dari variable keluaran (QA, QB, QC) dibuat berdasarkan table eksitasi JKFF. Peta karnaugh untuk masing-masing variable disajikan pada table 1.20 dan 1.21 berikut ini :

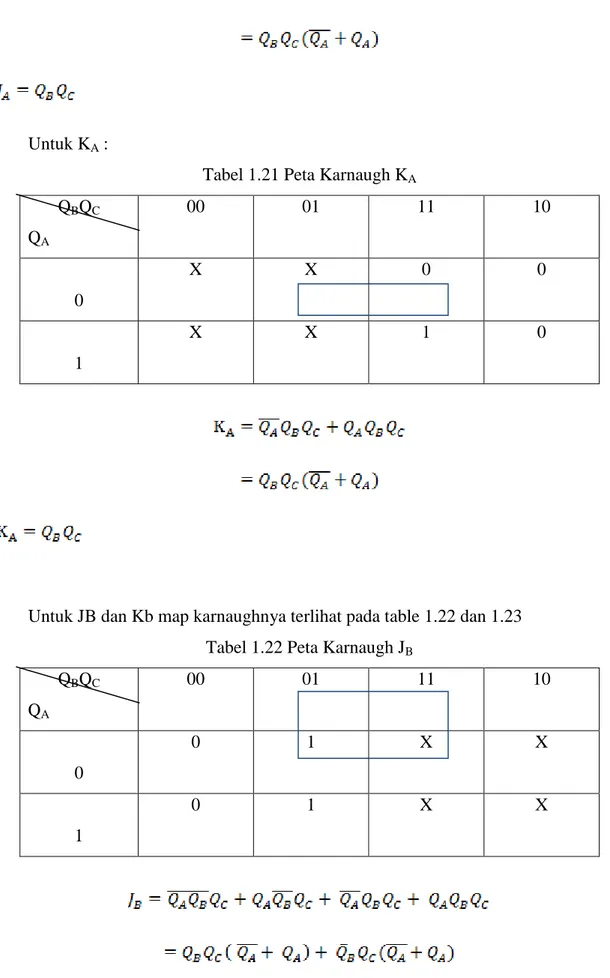

Untuk JA :

Tabel 1.20 Peta Karnaugh JA QBQC QA 00 01 11 10 0 0 0 X X 1 0 1 X X

Untuk KA :

Tabel 1.21 Peta Karnaugh KA QBQC QA 00 01 11 10 0 X X 0 0 1 X X 1 0

Untuk JB dan Kb map karnaughnya terlihat pada table 1.22 dan 1.23 Tabel 1.22 Peta Karnaugh JB

QBQC QA 00 01 11 10 0 0 1 X X 1 0 1 X X

=

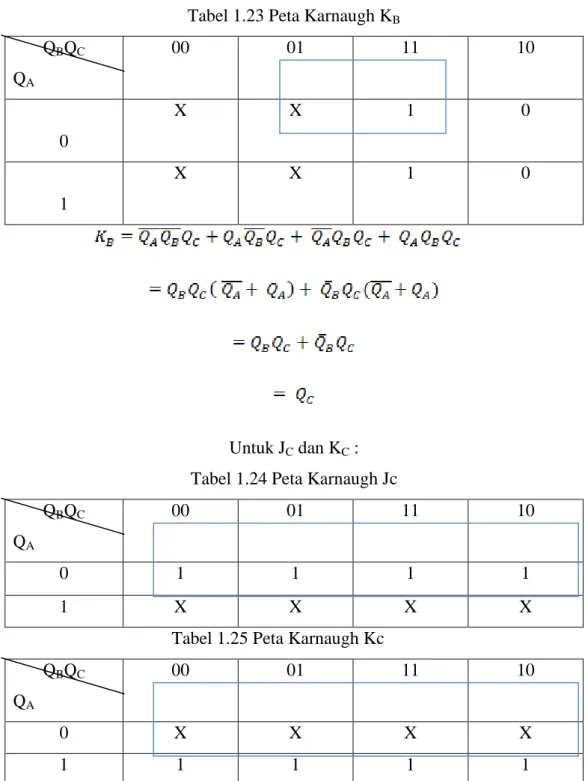

Untuk KB map karnaughnya terlihat pada table 1.23. Tabel 1.23 Peta Karnaugh KB

QBQC QA 00 01 11 10 0 X X 1 0 1 X X 1 0 Untuk JC dan KC : Tabel 1.24 Peta Karnaugh Jc QBQC

QA

00 01 11 10

0 1 1 1 1

1 X X X X

Tabel 1.25 Peta Karnaugh Kc QBQC

QA

00 01 11 10

0 X X X X

1 1 1 1 1

= 1 ( masukan LSB, karena seluruh nilainya biasanya bernilai 1 atau X don’t care dapat di sederhanakan menjadi satu pada map karnaugh)

Dari persamaan dan map karnaugh tersebut, dapat dibuat rangakaiannya sesuai dengan persamaan tersebut seperti terlihat pada gambar 1.27.

Pencacah Sinkron dengan T Flip-Flop

Pencacah sinkron memiliki 3 buah output yaitu Q2, Q1, dan Q0. Bit pada Q0 berubah setiap terjadi clock. Bit Q1 berubah hanya jika q0 = 1. Bit Q2 berubah hanya jika Q1 dan Q2 bernilai 1. Gambar 1.28. menunjukkan (a) rangkaian pencacah sinkron dengan T Flip-flop dan (b) timing diagram rangkaian pencacah sinkron.

(a)

Gambar 1.28. (a) Circuit Pencacah Sinkron dengan T Flip-Flop (b) Timing Diagram

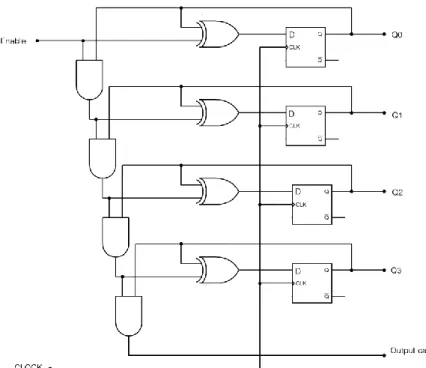

Pencacah Sinkron dengan D Flip-Flop

Sebuah pencacah sinkron 4 bit, dengan output Q3,Q2, Q1, Q0. Jika diasumsikan Enable = 1, saat input D dari flip-flop didefinisikan dengan persamaan beikut ini :

Untuk pencacah yang besar dengan kondisi ke-i, dapat didefinisikan dengan :

Sinyal dikontrol oleh enable sehingga counter dapat menghitung saat pulsa clock jika Enable = 1. Persamaan diatas dapat dimodifikasi untuk diimplementasikan pada rangkaian dengan persamaan berikut :

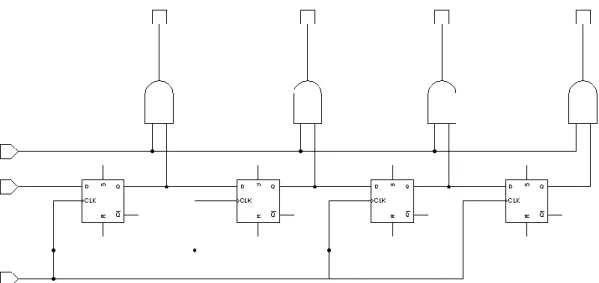

Gambar 1.29 menunjukkan rangkaian 4 bit pencacah dengan D flip-flop. Output dari gerbang XOR menghasilkan . Gerbang AND digunakan sebagai

Gambar 1.29. Rangkaian 4 bit Pencacah Sinkron dengan D Flip-Flop b. Pencacah Tak Sinkron

Pencacah tak sinkron disebut juga pencacah serial atau pencacah riak (ripple), dimana setiap keluaran FF bertindak sebagai sinyal masukkan bagi Clock pada FF berikutnya. Output setiap FF berubah secara tak sinkron terhadap pulsa detak. Hanya FF ke 0 yang dikenai pulsa detak, output FF-1 menunggu dipicu dari FF-0. Pulsa input clock hanya dimasukkan pada FF yang terdepan (Least Sighificant Bit = LSB). Perubahan FF-1 menunggu hingga dipicu oleh FF-0. Output FF-2 menunggu dipicu oleh FF-1, demikian seterusnya. Misalkan kombinasi dari , pada akhir pulsa ke delapan ketiga FF kembali pada keadaan 000 dan

serial biner terulang dengan sendirinya untuk pulsa yang berurutan. Pencacah tersebutmengitung nilai tertinggi 111 = 7 (8 keadaan) dan selanjutnya kembali ke 0. Pencacah ini memiliki 23=8 keadaan yang berbeda (dari 000 s/d 111) dan dikenal sebagai pencacah modulo 8. Pencacah modulo 2N akan mampu menghitung dari nol hingga 2N – 1 sebelum kembali ke keadaan nol. Berikut ini cara merancang pencacah sinkron modulo 8 menggunakan 3 buah Flip-flop JK. Tabel Representasi saluran masukan (J dan K) terhadap saluran output (Q), setiap Flip-flop terlihat pada table 1.26.

No. Baris QA QB QC JA KA JB KB 0 0 0 0 X X X X 1 0 0 1 X X 1 X 2 0 1 0 X X X X 3 0 1 1 1 X X 1 4 1 0 0 X X X X 5 1 0 1 X X 1 X 6 1 1 0 X X X X 7 1 1 1 X 1 X 1

Dari tabel diatas dapat dilihat kalau dipilih semua X = 1, maka :

JB= KB=1 dan JA= KA=1

Dari tabel ini terlihat bahwa FFC yang input clock-nya dihubungkan dengan pulsa input akan mengakibatkan QC selalu berubah setiap ada pulsa masuk. Hal ini akan terjadi kalau diatur JC=KC=1. Untuk FFB yang diharapkan sebagai pulsa clock adalah QC dan ini mungkin karena QB berubah (dari 0 ke 1 atau 1 ke 0) selalu bersamaan dengan perubahan dari QC dari 1 ke 0 (pulsa clock efektif). Sehingga input clock FFB dihubungkan dengan QC. Untuk mengatur harga JB dan KB, dari tabel 1.26dapat terlihat pada cacah ke 0,2,4, dan 6, QC berubah dari 0 ke 1 yang merupakan pulsa clock tidak efektif, maka JB dan KB pada keadaan tersebut dapat diisi X.

Sedang untuk keadaan yang lain harga JB dan KB diatur sesuai dengan perubahan QB. Untuk FFB yang diharapkan sebagai pulsa clock adalah QB dan QC, dan keduanya mungkin karena setiap QA berubah (dari 0 ke 1 atau 1 ke 0) selalu bersamaan dengan perubahan QB dan QC dari 1 ke 0. Hanya saja karena perubahan QB dari 1 ke 0 lebih sedikit daripada QC, maka dengan memlilih QB sebagai pulsa clock FFA, harga X untuk JA dan KA akan lebih banyak. Rangakaian pencacah tak sinkron modulo 8 terlihat pada gambar 1.30.

Gambar 1.30. Pencacah Tak Sinkron Modulo 8

Up Counter dengan T Flip-Flop

Input T flip-flop terkoneksi dengan nilai konstanta = 1, yang artinya outputnya akan bernilai bergantian. Clock input hanya dimasukkan pada FF yang pertama, sedangkan flip-flop selanjutnya terhubung dengan . Flip-flop kedua

diclock oleh demikian seterusnya hingga flip-flop ke-2. Gambar 1.31. (a)

(a)

(b)

Gambar 1.31. Rangkaian Up Counter (a) Timing diagram (b)

Down Counter dengan T Flip-Flop

Clock pada down counter dengan T flip-flop dihubungkan ke bagian output Q sehingga menghasilkan counting secara berurutan dari 0,7,6,5,4,3,2,1,0,7 sebagai down counter. Pada gambar 1.32 menunjukkan (a) Rangkaian Up Counter dan (b) timing diagram dari Down Counter dengan T Flip-Flop.

(b)

Gambar 1.32. (a) Rangkaian Down Counter dengan T Flip-Flop (b) Timing Diagram

Latihan:

1. Buatlah Counter Asinkron dan Sinkron yang dapat menghitung secara Up/Down Counter? (Modulo berapa pun bebas)

2. Buatlah Counter sinkron modulo 5 dengan FF Jk naik dan modulo 5 turun ? 3. Buatlah Counter Asinkron modulo 5 dengan FF Jk naik dan modulo 5 turun? 4. Rancanglah pencacah biner sinkron / pararel naik modulo 6 menggunakan

flip-flop JK yang dapat di reset (di nol kan) dengan hanya menekan satu tombol?

II. Register Geser

Register adalah kumpulan flip-flop, dimana tiap flip-flop terhubung pada clock dan mampu menyimpan informasi 1 bit. Register geser adalah n-bit register dengan kemampuan untuk menggeser dan memasukkan data dengan posisi satu bit akan bergeser dengan masukan satu clock. Register digunakan untuk menyimpan data sementara, untuk kemudian diproses atau diganti dengan data yang baru. Jenis register dapat pula diklasifikasikan berdasarkan cara data masuk ke dalam suatu register untuk disimpan dan cara data dikeluarkan dari register tersebut. Gambar 1.33menggambarkan 4 bit shift register yang digunakan untuk menggeser posisi bit data ke kanan. Bit data dimasukkan dalam shift register secara serial melalui In input. Isi dari masing-masing flop ditransfer ke flip-flop selanjutnya melalui positive edge clock. Ilustrasi dari transfer bit data terlihat

pada tabel 2.9, dimana nilai input yang dimasukkan adalah 1,0,1,1,1,0,0,dan 0 yang mengasumsikan bahwa inisial state dari seluruh flip-flop = 0.

Gambar 1.33. Shift Register dengan D Flip-flop

Tabel 1.27 Ilustrasi Shift Register

In 1 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 0 1 0 1 1 1 0 1 0 1 1 1 0 0 0 1 1 1 0 0 0 1 1

Untuk memasukkan dan mengeluarkan data masing-masing dapat dilakukan secara serial atau pararel. Serial berarti data dimasukkan atau dikeluarkan ke atau dari register secara beruntun bit demi bit. Sedangkan cara pararel berarti data yang terdiri dari beberapa bit dimasukkan atau dikeluarkan ke atau dari register secara serempak.

Berdasarkan hal itu maka terdapat 4 jenis register : a. Serial In Pararel Out (SIPO)

Pada register SIPO data input dimasukkan secara serial, maka output dari FF yang satu dihubungkan ke input FF berikutnya. Kemudian Output dikeluarkan secara pararel. Gambar 1.34 menunjukkan rangkaian register serial in dan pararel out.

Gambar 1.34. Rangkaian Register SIPO b. Serial In Serial Out (SISO)

Pada register SISO data input dimasukkan secara serial, dan output dari FF yang satu dihubungkan ke input FF berikutnya. Kemudian Output dikeluarkan secara serial. Gambar 1.35 menunjukkan rangkaian register serial in dan serial out.

Gambar 1.35. Rangkaian Register SIPO c. Pararel In Serial Out (PISO)

Pada register PISO data input dimasukkan secara pararel, dan output dari FF yang satu dihubungkan ke input FF berikutnya. Kemudian Output dikeluarkan secara serial. Gambar 1.36 menunjukkan rangkaian register pararel in dan serial out.

Gambar 1.36. Rangkaian Register Pararel In dan Serial Out

d. Pararel In Pararel Out (PIPO)

Register 4 bit PIPO dapat dibentuk dengan 4 buah DFF, dan beberapa gerbang logika, seperti pada gambar 1.37. Sehingga jika data 4 bit dimasukkan secara bersama-sama pada (ABCD)in dan kemudian memberikan

pulsa clock, maka .

Gambar 1.37. Rangkaian Pararel In dan Pararel Out Shift Register

TUGAS BAB REGISTER

1. Rancanglah register geser 4 bit untuk jenis PISO menggunakan flip-flop JK?

2. Rancanglah sebuah pengendali lampu lalu lintas (traffic Light) dengan urutan kejadian :

Nyala hijau selama 20 detik, nyala kuning selama 10 detik, dan nyala merah selama 20 detik. Selain itu, pada malam hari hanya terjadi nyala kuning yang berkedip setiap 1 detik secara terus menerus.

III. Clock Mode, Pulse Mode dan Level Mode

Clock merupakan pembangkit pulsa atau pemicu agar suatu rangkaian sekuensial sehingga terjadi perubahan keadaan output. Ada 2 jenis model pembangkit sinyal, yaitu

a. Pulse Triggering

Pada mode ini pulsa clock dibangkitkan selama terjadi pulsa naik atau pulsa turun. Ada 2 jenis pembangkit pulsa yakni positive pulse triggering dan negative pulse triggering. IIlustrasinya terlihat pada gambar 1.38.

positive pulse triggering

negative pulse triggering

Gambar 1.38 ilustrasi Pulse Triggering

b. Edge Triggering

Pada mode ini pulsa clock dibangkitkan pada saat pulsa tepi naik atau pulsa tepi turun. Ada 2 jenis pembangkit pulsa yakni positive edge dan negative edge triggering. IIlustrasinya terlihat pada gambar 1.39

Edge Triggering (rising)

Edge Triggering (falling)

Gambar 1.39. Ilustrasi Edge Triggering

ck

ck

ck

Sinyal clock dikatakan active high jika perubahan keadaan terjadi pada rising edge (untuk edge triggered device) ataupada keadaan logic 1 (untuk I pulse triggered devices). Sinyal clock dikatakan active low jika perubahan terjadi pada falling edge atau keadaan logicnya = 0. Ilustrasi active high dan active low disajikan pada gambar 1.40.

(a) (b) Gambar 1.40. (a) Timing Diagram Active high dan Active low ; (b) Flip-flop

timing

Periode Clock adalah waktu yang dibutuhkan untuk transisi pada arah yang sama. Frekuensi clock adalah periode clock yang berulang. Clock Tick adalah tepi pertama, atau pulsa pada periode clock. Duty Cycle adalah presentase waktu pada sebuah clock pada level assertion. Flip-flop timing dapat dikategorikan dalam beberapa tipe :

a. Combinational

tpd, min : minimum propagation delay, input to output tpd, max : maximum propagation delay, input to output b. Latch

tpd, min : minimum propagation delay, input to output tpd, max : maximum propagation delay, input to output tw : maximum pulse width, input to input c. Flip-Flop

tpd, min : minimum propagation delay, CLK to output tpd, max : maximum propagation delay, CLK to output

tsetup : waktu stabil, yang dibutuhkan input sebelum CLK, dari input sebelum CLK.

thold : waktu stabil, yang dibutuhkan input setelah CLK, dari input setelah CLK.

Soal Latihan

1. Buatlah suatu rangkaian dengan 2 input, dimana masing-masing input memiliki karakteristik sendiri-sendiri, yaitu:

0 : counter berjalan dari bilangan 0 sampai dengan 7 1 : counter akan berjalan dari bilangan 15 turun ke 8

2. Buatlah simulasi dari robot yang dapat berhitung apabila tangannya diputar, maka robot akan berhitung : 2,3,5,7 dan terus berulang, jika kepalanya diputar dia menghitung dari : 0,1,4,6 dan terus berulang. Jika kakinya diputar maka dia akan berhitung mundur 7,6,5,4,3,2,1 dan seterusnya.

3. Buatlah timer countdown yang terdapat pada traffic light 30 hitungan. 4. Buatlah sebuah detektor setiap counter 40 pada kelipatan 5 akan menyala! 5. Anak-anak bermain menyebutkan bilangan 1-15. Budi tidak ikut

menyebutkan bilangan dan akan bermain sebagai komando. Pada saat Budi berkata: “TETOT!” anak-anak lain disuruh menentukan apakah bilangan itu ganjil dan genap. Buatlah simulasi dalam rangkaian untuk menggambarkan proses di atas. {petunjuk: gunakan 2 buah lampu indikator untuk bilangan ganjil dan genap!, semakin sederhana rangkaian nilai semakin bagus}

Petunjuk Penilaian dan Umpan Balik

Penilaian dilaksanakan dari keaktifan mahasiswa dikelas untuk berdiskusi dan bertanya. Tes formatif dilaksanakan pada akhir sesi, penilaian diberikan dengan rentang nilai 0 – 100. Bobot keaktifan dan tes formatif adalah 10 % dari nilai akhir keseluruhan. Umpan balik diberikan oleh dosen sebagai fasilitator, dan sebagai mahasiswa umpan balik dilakukan dengan memberikan pertanyaan atau tanggapan terhadap pertanyaan dari dosen.

Tindak Lanjut

Studi lanjut tentang verilog akan disampaikan pada pertemuan selanjutnya tentang perancangan rangkaian sekuensial menggunakan verilog. Tindak lanjut dari hasil test Formatif adalah meningkatkan pemahaman mahasiswa melalui latihan dan pengaplikasian ilmu pada hardware sesungguhnya pada mata kuliah penunjang praktikum.