TAPIS PELEWAT JALUR MENGGUNAKAN

KAPASITOR TERSAKLAR

TUGAS AKHIR

Diajukan untuk memenuhi salah satu syarat Memperoleh gelar Sarjana Teknik

Program Studi Teknik Elektro

Disusun oleh :

Noviyanti Maya Dewi Kia

NIM : 995114071

JURUSAN TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

2007

Halaman Persembahan

YESUS………..

DIA tidak pernah berjanji….

langit cerah tanpa hujan,

Hidup suka tanpa duka,

Bunga mekar tanpa layu,

Wajah tersenyum tanpa air mata,

Tapi DIA berjanji,

Akan menyertai mu hingga akhir jaman……

Seperti Ia telah menyertaiku,dalam setiap denyut nadiku

Trmakasih YESUS……

Papi & Mami…….

.trmakasih tuk segalanya

BUBY……buby………

THX dah nemenin selama di jogja………..

LOVE U BUBY……….huk….huk…huk…

TAPIS PELEWAT JALUR MENGGUNAKAN KAPASITOR

TERSAKLAR

NAMA : NOVIYANTI MAYA DEWI KIA

NIM : 995114071

INTISARI

Berawal dari semakin berkembangnya teknologi khususnya teknologi telekomunikasi, antara lain telepon, radio, dan berbagai alat elektronika yang semuanya menggunakan penepis (filter) untuk membatasi arus listrik dengan frekuensi-frekuensi tertentu, sesuai dengan yang dibutuhkan, maka dibuatlah sebuah penepis aktif dengan menggunakan kapasitor tersaklar

Penelitian ini bertujuan untuk lebih memahami dasar-dasar tapis pelewat jalur, system ordo frekuensi cutoff, tanggapan frekuensi, dan kapasitor tersaklar. Frekuensi tengah yang digunakan adalah 4000 Hz dengan frekeunsi clock-nya adalah 150 KHz.

BANDPASS SWITCHED CAPACITOR FILTER

NAME : NOVIYANTI MAYA DEWI KIA

NIM : 995114071

ABSTRACT

Early from progressively expand technological on specially telecommunication technology, for example telephone, radio, and various all electronic appliance, filter is used to limit the electrics current with the certain frequency that is required. So that is needed to design an active filter using switch capacitor.

The objective of this research is to get deeper understanding about the bandpass filter, system order, cutoff frequency, frequency response, and switch capacitor.Cutoff frequency for bandpass filter is design about 4000 Hz with clock frequency is used is 150 KHz.

KATA PENGANTAR

Puji kehadirat Tuhan yang Maha Esa, Tuhanku Yesus Kristus yang telah

memberikan rahmat dan berkat-NYA, sehingga penyususn dapat menyelesaikan tugas

akhir ini.

Atas tersusunnya tugas akhir ini, penyususn mengucapkan banyak terima kasih

kepada:

1. Bapak Agustinus Bayu Prinawan,S.T., M.Eng, selaku Ketua Jurusan Teknik

Elektro Fakultas Teknik Universitas Sanata Dharma Yogyakarta.

2. Bapak Martanto, S.T, M.T, selaku Dosen Pembimbing I yang telah meluangkan

waktu guna memberikan bimbingan,saran dan kritik.

3. Orang tuaku tercinta, papi dan mami,yang telah memberikan do’a, kasih sayang,

pengertian, dan semangat.

4. Pak Pur dan Mama Irna, terima kasih untuk do’a, dan kasih sayangnya.

5. Kakakku Tony, adek Yola, my lovely Rio, terima kasih atas bantuan dan

dorongannya, ‘n BUBY……(thx dah nemenin selama di jogja, dan menghibur

dengan gonggongan-mu….huk…huk…)

6. Mas Wawan, terima kasih atas doa, perhatian, dan sayangnya ,hingga tugas akhir

ini selesai. ( you best I ever had).

7. Semua temen kos, Sitha.Ira, Mbk Ayu,(kalian teman yang menggilakan, tapi juga

menyenangkan) ‘n rekan mahasiswa Santi, Roy, Dagul, Tutus, Ari Inyonk, Anci’,

DAFTAR ISI

Halaman

HALAMAN JUDUL……….. i

LEMBAR PENGESAHAN PEMBIMBING………. iii

LEMBAR PENGESAHAN PENGUJI……….. iv

LEMBAR PERNYATAAN KEASLIAN KARYA……….. v

HALAMAN PERSEMBAHAN……….. vi

INTISARI……….. vii

ABSTRACT……… viii

KATA PENGANTAR……… ix

DAFTAR ISI………. xi

DAFTAR GAMBAR………. xiii

DAFTAR TABEL………. xiv

BAB I PENDAHULUAN……… 1

1.1. Latar Belakang………. 1

1.2. Tujuan Penelitian……… 2

1.3. Manfaat Penelitian……… 3

1.4. Perumusan Masalah………. 3

1.5. Batasan Masalah………. 4

1.6. Metodologi Penelitian……….. 5

1.7. Sistematika Penulisan……… 6

BAB II DASAR TEORI……….. 8

2.1. Pengertian Tapis……… 8

2.2. Klasifikasi Tapis………. 9

2.2.1. Watak Tapis Nyata……….. 12

2.2.2. Realisasi Tapis Nyata………. 14

2.2.3. Untai Realisasi Tapis………. 14

2.2.3.1. Tapis Pasif Dengan R,L dan C…… 14

2.2.3.2. Tapis RC aktif………. 15

2.2.3.3. Kapasitor Tersaklar………. 17

2.2.3.4. Dasar Kapasitor Tersaklar…………..18

2.3. Penapis Lolos Pita………. 20

2.3.1. Untai Tapis Analo pelewat Jalur……….. 22

BAB III PERANCANGAN KAPASITOR TERSAKLAR……… 25

3.1. Pembangkit Detak dua Fase……….. 25

3.2. Untai Tapis Pelewat jalur……… 26

BAB IV DATA PENGAMATAN……….. 29

4.1. Nilai-nilai Perancangan Tapis Pelewat jalur………... 29

4.2. Pengamatan Tanggapan Frekuensi……… 31

4.2.1. Tapis Pelewat Jalur………... 32

4.3. Karakteristik Tapis Pelewat Jalur ………. 33

4.3.1. Hubungan Frekuensi Penyaklaran……… 34

BAB V PENUTUP………. 35

DAFTAR PUSTAKA……….. 36

LAMPIRAN

8. Dan semua pihak yang telah membantuku, yang tidak bias disebutkan satu

persatu.

Akhir kata, penulis menyadari bahwa tugas akhir ini masih jauh dari sempurna,

karena itu hati terbuka penulis mengharapkan kritik dan saran yang sifatnya membangun

demi kesempurnaan tugas ini. Penulis berharap semoga tugas akhir ini dapat bermanfaat

bagi yang memerlukan dan dapat menambah Ilmu Pengetahuan.

Yogyakarta, 30 Januari 2007

DAFTAR GAMBAR

Gambar Halaman

2.1. Tanggapan Tapis Ideal……….. 9

2.2. Tanggapan Tapis Nyata……… 11

2.3. Watak Pelemahan Tapis……… 12

2.4. Dasar Kapasitor Tersaklar……… 17

2.5. Untai Dasar Kapasitor Tersaklar……… 18

2.6. Kurva Umum Karakteristik Penapis Lolos Pita……… 20

2.7. Q Pada Penapis Lolos Pita……… 22

2.8. Untai Tapis Pelewat Jalur Dengan untai Biquad………. 23

3.1. Pembangkit detak Dua Fasa………. 26

3.2. BPF dengan Kapasitor Tersaklar………. 27

DAFTAR TABEL

Tabel Halaman

4.1. Tabel Penguatan Tapis Pelewat Jalur……….. 32

1

BAB I

PENDAHULUAN

1.1. Latar Belakang

Perkembangan ilmu pengetahuan dan teknologi elektronika saat ini

sangatlah pesat. Berbagai kemajuan di bidang teknologi elektronika tersebut

akan sangat membantu manusia di dalam kehidupannya. Salah satu bentuk

kemajuan teknologi elektronika yang dapat dirasakan manfaatnya adalah

penapis aktif. Banyak peralatan yang digunakan manusia menggunakan

penapis aktif dalam salah satu komponennya, contohnya: radio, telephone,

televisi, dan modem.Peran suatu penapis aktif yang begitu besar bagi

peralatan-peralatan elektronik terkadang tidak disadari atau bahkan tidak

diketahui. Memang bagi orang awam penapis aktif tidaklah terlalu penting

karena yang tepenting bagi mereka adalah bagaimana suatu peralatan atau

suatu system elektronik dapat bekerja dengan baik. Bagi orang elektro,

penapis aktif adalah sesuatu hal yang harus diketahui, namun belum semua

orang elektro mengetahuinya dengan baik. Pengetahuan mahasiswa elektro

mengenai penapis aktif pun terkadang tidaklah begitu baik. Dalam hal ini,

pemehaman tentang penapis aktif dapat menjadi maksimal apabila mahasiswa

juga melakukan praktek langsung, baik melalui praktikum maupun melalui

2

perancangansuatu alat yang menggunakan aktif sebagai salah satu

komponennya.

Berawal dari keadaan tersebut penulis mencoba untuk membuat

suatu filter pelewat jalur dengan menggunakan kapasitor tersaklar sebagai

salah satu cara untuk lebih memahami tentang penapis aktif.

Setelah belajar kembali tentang penapis aktif pelewat jalur

menggunakan kapasitor tersaklar ini, pemahaman terhadap penapis aktif dapat

menjadi lebih baik. Sejalan dengan hal tersebut, diharapkan akan

menumbuhkan dorongan untuk menciptakan sesuatu hal baru yang

menggunakan teknologi penapis aktif.

1.2. Tujuan Penelitian

Tujuan dari penelitian Filter Pelewat Jalur Menggunakan Kapasitor

Tersaklar ini adalah:

1.2.1. Membuat suatu filter pelewat jalur dengan menggunakan

kapsitor tersaklar dengan menerapkan pengetahuan tentang

panapis aktif.

1.2.2. Dengan membuat tapis pelewat jalur menggunakan kasitor

tersaklar ini dapat diharapkan pemahaman mahhasiswa

mengenai penapis aktif dan kapasitor tersaklar menjadi lebih

baik.

3

1.2.3. Membuat penapis pelewat jalur dengan menggunakan

kapasitor tersaklar, jauh lebih mudah dibandingkan harus

menghitung elemen per elemen dari tapis aktif RC tidak bisa

memuaskan dalam hal keakuratan dan kestabilan yang

dikehendaki.

1.3. Manfaat Penelitian

Manfaat dari penelitian Tapis Pelewat Jalur Menggunakan Kapasitor

Tersaklar ini adalah:

1.3.1 Terciptanya pemahaman yang lebih baik tentang berbagai hal

di dalam penapis aktif.

1.3.2 Tumbuhnya minat untuk menciptakan sesuatu hal baru yang

menggunakan kapasitor tersaklar untuk membuat penapis

pelewat jalur, sebagai komponennya.

1.4. Perumusan Masalah

Permasalahan yang diajukan dalam penelitian ini adalah :

1.4.1 Bagaimana merancang suatu piranti sebuah tapis pelewat

jalur menggunakan kapasitor tersaklar ?

1.4.2 Bagaimana menentukan banyaknya orde suatu penapis aktif ?

1.4.3 Bagaimana tenggapan penaksiaran Butterworth diterapkan

pada penapis aktif ?

4

1.4.4 Bagaimana menghitung tanggapan frekuensinya bila

frekuensi cutoff 4 kHz, dan frekuensi clock 150 kHz ?

1.5. Batasan Masalah

Dalam mengimplementasikan tapis yang memiliki tanggapan butterworth dengan menggunakan kapasitor tersaklar akan dibatasi dalam hal

orde tapis yang di pergunakan. Untai tapis yang dipakai untuk

mengimplementasikan tapis dengan menggunakan kapasitor tersaklar adalah

didasarkan pada untai Biquad.

Penelitian pada Bandpass Filter With Use Switch Capacitor ini

dibatasi pada masalah-masalah sebagai berikut :

1.5.1. Filter pelewat jalur menggunakan kapasitor tersaklar tersusun

atas rangkaian-rangkaian switch capacitor yang mana bahwa

pensaklaran kapasitor digunakan sebagai pengganti suatu

resistor pada untai analog.

1.5.2. Penapis aktif tersebut menggunakan tanggapan panaksiaran

Butterworth.

1.5.3. Untuk orde bandpassfilter yang dibuat adalah orde kedua.

1.5.4. Pembuatan orde kedua bandpass filter didasarkan pada untai

RC analog Biquad.

5

1.5.5. Masukan (input) frekuensi menggunakan AFG (Audio

Function Generator)

Kemudian hasil perancangan tapis diimplementasikan kedalam untai

yang nyata, dengan menggunakan komponen yang sifatnya diskret yaitu

dengan penggunaan kapasitor, penguat operasi, dan saklar CMOS. Nilai-nilai

kapasitor yang dipakai untuk merealisasikan tapis dengan kapasitor tersaklar

menggunakan kapasitor yang tersedia di pasaran, yang nilainya diambil yang

paling dekat dengan nilai perhitungan.

Pengamatan terhadap tapis yang telah diimplementasikan dibatasi

pada tanggapan frekuensi dan bentuk gelombang masukan dan keluaran tapis

untuk masukan berupa gelombang sinus.

1.6. Metodologi Penelitian

Dalam perancangan piranti Bandpass Filter With Use Switch

Capasitor malalui beberapa tahap penelitian yang akan mendukung

suksesnya perancangan ini. Tahap-tahap penelitian tersebut adalah:

1.6.1. Mengumpulkan bahan literature pendukung : paper,

buku-buku, data sheet.

1.6.2. Perancangan layout alat : membuat PCB dan switch

capacitor.

1.6.3. Pengujian dan perbaikan alat : pengukuran tegangan masukan

dan tegangan keluaran pada masing-masing penapis aktif

6

dengan menggunakan osiloskop, pembuatan grafik tanggapan

frekuensi.

1.6.4. Pembuatan laporan.

1.7. Sistematika

Penulisan

Sistematika penulisan dalam penyusunan laporan penelitian ini

tersusun sebagai berikut :

BAB I PENDAHULUAN

Pada bab ini berisi tentang : latar belakang yang mendasari

dipilihnya topik dalam tugas ini, tujuan penelitian, menfaat

penelitian, perumusan masalah, batasan masalah, metodologi

penelitian, dan sistematika penulisan.

BAB II DASAR TEORI

Pada bab berisi tentang teori yang berkaitan dengan penapis aktif,

dan penjelasan tentang kapasitor tersaklar.

BAB III PERANCANGAN PERANGKAT KERAS

Pada bab ini berisi tentang dasar-dasar kapasitor tersaklar dengan

operasi analog yang dapat dipakai dengan kapasitor tersaklar. Serta

perancangan dari masing-masing hardware.

7

BAB IV PENGAMATAN DATA

Pada bab ini berisi tentang data hasil pengamatan, beserta analisa

data.

BAB V PENUTUP

Pada bab ini berisi tentang kesimpulan serta kritik dan saran.

BAB II

DASAR TEORI

2.1.

Pengertian Tapis

Sebuah penapis adalah sebuah alat atau rangkaian atau subtanst yang

meneruskan atau meloloskan arus listrik pada frekuensi-frekuensi atau jangkauan

frekuensi tertentu serta menahan (menghalangi ) frekuensi-frekuensi lainnya.

Secara khusus, sebuah penapis aktif adalah suatu rangkaian penapis yang

tersusun atas resistor-resistor dan kapasitor-kapasitor disertai dengan suatu rangkain

penguat, biasanya berupa penguat operasional. Sedangkan panapis aktif hanya terdiri

dari resistor, inductor dan kapasitor.

Sebuah penapis aktif memiliki beberapa kelabihan sebagai berikut:

¾ Tidak ada sinyal hilang – Hal ini disebabkan karena penguat operasional

mampu menyediakan penguat atau gain, sehinggan sinyal masukan tidak akan

segera mengalami pelemahan (atenuasi) selama rangkain meneruskan

sinyal-sinyal dengan frekuensi yang dikehendaki;

¾ Biaya dan kemudahan – Sebenarnya rangkaian penapis aktif ongkos

pembuatanya rata-rata lebih murah dibandingkan dengan penapis pasif, hal ini

disebabkan karena pada rangkain pasif menggunakan komponen inductor yang

harganya jauh lebih mahal dan tidak selalu tersedia di pasaran;

¾ Penyetelan – Penapis aktif mudah disetel ( tune ) untuk jangkauan frekuensi

yang lebar tanpa mempengaruhi tanggap rangkaian yang telah ditentukan (

¾ Isolasi – Sebagai akibat dari penggunaan penguat operasional, penapis aktif

akan memiliki impedansi masukan yang tinggi dan keluaran yang rendah, hal

ini sebenarnya hampir menjamin tidak adanya interaksi antara penapis dengan

sumber atau beban sinyal

2.2.

Klasifikasi Tapis

Tapis diklasifikasikan menurut fungsi yang dibentuk dalam hal jangkauan

frekuensi jalur lewat (passband) dan jalur henti (stop band). Dalam keadaan ideal,

perbandingan besar tegangan keluaran dengan tegangan masukan pada jalur pelewat

sama dengan 1, sedang pada jalur henti sama dengan 0. Pola dari jalur lewat dan

jalur henti , memberikan empat macam tapis yang sangat umum, yang ditunjukan

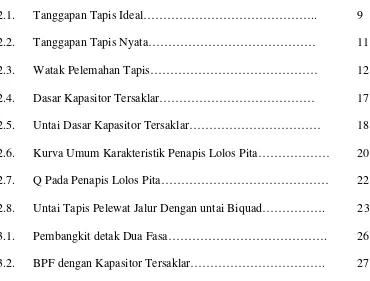

pada Gambar 2-1.

| T | | T |

1 1 JALUR JALUR

JALUR JALUR HENTI PELEWAT

PELEWAT HENTI

O ωο ω O ωο ω

(a) (b)

| | T |

JALUR JALUR JALUR JALUR JALUR

HENTI PELEWAT HENTI HENTI PELEWAT

JALUR PELE WAT

O ω₁ ω₂ ω

Gambar 2-1. Tanggapan Tapis ideal. (a) Tapis Pelewat Rendah, (b) Tapis Pelewat

Atas, ( c) Tapis Pelewat Jalur dan (d) Tapis Penolak Jalur

Empat macam tapis dapat dijelaskan sebagai berikut :

1. Tapis Pelewat Rendah (Low Pass Filter) adalah tapis yang memiliki jalur

pelewat dari ω=0 sampai ω=ωo, dengan ωo disebut sebagai frekuensi pancung

(cut off frequency).

2. Tapis Pelewat Tinggi (High Pass Filter) merupakan komplomen dari tapis

pelewat rendah, dengan frekuensi dari 0 sampai ωo merupakan jalur henti (stop

band), sedangkan jalur pelewat adalah dari frekuensi ωo sampai tak hingga.

3. Tapis Pelewat Jalur (Band Pass Filter) adalah tapis yang melewatkan frekuensi

antara ω1 sampai ω2, selain frekuensi ini tidak dilewatkan.

4. Tapis Jalur Henti (Band Elimination Filtar) merupakan komplemen dari Tapis

Pelewat Jalur dengan frekuensi dari ω1 sampai ω2 dihentikan dan lainnya

dilewatkan. Tapis ini sering dinamakan ‘notch filter’.

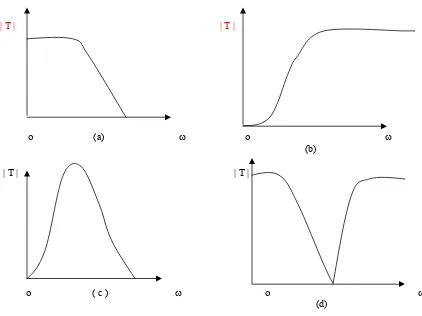

Watak tapis yang nyata yang berhubungan dengan keempat macam tapis

ditunjukan pada Gambar 2-2. Watak pelemahan yang berhubungan dengan Gambar

2-2 ditunjukkan pada Gambar 2-3. Hubungan kedua besaran ini ditunjukkan pada

| T | | T |

(b)

ο (a) ω ο ω

| T | | T |

ο ( c ) ω ο ω (d)

Gambar 2-2. Tanggapan tapis nyata. (a) Tapis Pelewat Rendah,(b) Tapis Pelewat

α α

ο (a) ω ο (b) ω

α

α

ο (c) ω ο (d) ω

Gambar 2-3. Watak pelemahan tapis yang berhubungan dengan gambar 2-2. (a)

Tapis Pelewat Rendah, (b) Tapis Pelewat Atas,(c) Tapis Pelewat

Jalur dan (d) Tapis Penolak Jalur.

2.2.1. Watak Tapis Nyata

Dalam praktisnya, penapisan dikehendaki untuk menolak komponen

isyarat dengan merancang tapis yang menghasilkan pelemahan (atenuasi) pada

daerah frekuensi tertentu, dan diinginkan komponen-komponen dari isyarat yang

lewat tanpa adanya pelemahan, atau mungkin bahkan dengan suatu penguatan isyarat.

Dalam hal ini perlu adanya pengukuran atenuasi dan perolehan (gain).Pelemahan atau

α = - 20 log [T] dB , | T | < 1……. ( 2 – 1 )

dengan T adalah perbandingan antara besaran output dengan besaran input. Satuan

pelemahan adalah decibel (dB), dan tanda minus menjelaskan bahwa positif bila

rangkaian menghasilkan rugi – rugi, seperti dijelaskan dengan

| T |≤1 . Bila T ≥ 1 di pakai symbol yang berlainan, yang menyatakan

suatu perolehan (gain), dengan :

A = 20 log [ T ] dB ……….( 2 – 2 )

Penyelesaian untuk [T] apabila α sudah diketahui, adalah dengan persamaan

[T] = 10 ̄ª⁄₂₀ ……… ( 2 ‐ 3 )

Sedangkan bila diketahui A , [ T ] dapat dicari dengan persamaan :

[T] = ( 10 ⁰∙⁰⁵ )A …. ……… ...( 2 - 4 )

Oleh karena tidak mungkin merealisasikan tapis ideal dengan perubahan

yang tajam dari jalur pelewat dan jalur henti, maka tapis ideal harus didekati dengan

tapis yang nyata. Watak yang dikehendaki ditentukan dengan mendefinisikan

perbedaan antara jalur pelewat dengan jalur henti, sebagai berikut ;

1. Jalur pelewat adalah suatu tanggapan yang memiliki pelemahan kurang

dari suatu nilai perancangan, yakni αmak.

2. Jalur henti adalah tanggapan yang selalu memiliki pelemahan lebih

besar dari nilai perancangan, yakni αmin.

3. Jalur frekuensi antara jalur henti dan jalir pelewat didefinisikan sebagai

Pada tapis pelewat rendah jalur, pelewat berada pada ω = 0 sampai ω = ωp,

jalur peralihan adalah dari ωp sampai ωs, dan jalur henti adalah semua frekuensi di

atas ωs sampai tak berhingga. Huruf s dan p pada ω menandakan tepi dari jalur

pelewat dan jalur henti. Konsep yang sama diterapkan pada pelewat atas,pelewat jalur

dan penolak jalur.

2.2.2. Realisasi Tapis Nyata

Untuk meralisasikan tapis dengan watak yang ideal tidaklah mungkin dicapai,

dengan adanya keterbatasan komponen yang digunakan.

Ada beberapa realisasi tapis sebagai pendekatan tapis ideal antar lain Tapis

Butterworth. Watak tapis Butterworth ialah pada jalur pelewat memiliki tanggapan

yang datar maksimum ( maximally flat ). Sifat-sifat tapis Butterworth akan diuraikan

dalam bab-bab selanjutnya.

2.2.3. Untai Realisasi Tapis

2.2.3.1Tapis pasif dengan R,L,dan C

Secara historisnya, tapis mula-mula direalisasikan seebagai tapis pasif yang

dibangun dari komponen Resistor, Indukator dan Kapasitor ( R,L dan C ). Dalam

realisasi tapis pasif, komponen induktor memiliki beberapa sifat seperti berikut :

1. Induktor biasanya memiliki rugi-rugi. Pada frekuensi rendah rugi-rugi dapat

digambarkan sebagai untai seri antara L murni dengan R ( hambatan dalam

inductor ). Dengan mendefinisikan factor kualitas dari induktor oleh

hubungan

L

Q

R

2. Untuk frekuensi rendah ( misalnya dibawah 100 Hz ) ukuran dan berat

induktor menjadi lebih besar.

3. Induktor kadang-kadang memerlukan bahan feromagnetik sebagai intinya,

sehingga biasa tidak linear dan membangkitkan harmonis yang tidak

diinginkan.

4. Radiasi dari induktor seperti halnya gelombang elektromagnetik. Oleh karena

itu induktor cenderung menghasilkan derau pada rangkaian.

5. Faktor kualitas sebanding dengan kuadrat dimensi induktor. Oleh karena

itu ukuran induktor tidak bisa direduksi tanpa penurunan

L

Q

.

L

Q

Sebaliknya pada kapasitor yang memiliki rugi-rugi, pada frekuensi rendah untai

paralel antara kapasitor C dan admitansi G. Faktor kualitas kapasitor adalah Qc = ω C

/ G. , yang dapat ditunjukan bahwa Qc tidak tergantung pada dimensi fisik. Oleh

karenanya factor kualitas Qc yang tinggi dari kapasitor bias dibangun. Qc dapat

dibuat sebesar 10 ribu untuk kapasitor praktis.

2.2.3.2 Tapis RC Aktif ( tapis analog )

Dengan sifat-sifat tersebut di atas, terlihat bahwa penggunaan komponen

induktor untuk tapis pasif ( terutama untuk frekuensi yang rendah ) kurang efektif,

setelah adanya penguat operasi ( Op – Amp ) yang harganya relatif murah, dengan

kelebihan yang telah dibuat untuk perancangan dan membuat tapis dari penguat

operasi, resistor dan kapasitor saja disebut dengan tapis analog. Tapis aktif RC ini

memainkan peranan yang penting dalam bidang komunikasi dan sistem kendali.

dan keping kapasitor yang disolderkan pada papan yang mengandung resistor film

tipis. Oleh karena itu fabrikasi tapis RC aktif dapat dibuat sangat lebih kecil

dibanding dengan untai tapis pasif RLC setaranya, khususnya untuk frekuensi rendah.

Langkah penalaran selanjutnya adalah merealisasikan tapis aktif RC ke dalam

struktur yang terpadu seluruhnya. Fabrikasinya dipilih antara teknologi bipolar dan

teknologi MOS, dan dalam banyak hal dipilih menggunakan tekhnologi MOS. Alasan

utamanya adalah ketersediaan kapasitor dengan kualitas yang tinggi pada untai

terpadu MOS, kemampuan penyimpanan mutan pada suatu simpul untuk waktu yang

cukup lama, arus MOS dapat lebih kecil dari satu pico ampere, dan kebocoran ke

substarte bahkan lebih kecil. Tetapi keterbatasan fisik yang nyata mencegah

pengurangan ukuran dalam bentuk hibrid yang benar-benar membentuk dimensi yang

sub miniatur.

Dengan teknologi MOS dimungkinkan pembuatan kapasitor dengan kualitas

tinggi. Namun kapasitor yang besar kapasitasnya memerlukan daerah yang luas pula

( Zmil² sekitar 200 µm² per pF ). Oleh karena itu kapasitor yang lebih

besar dari 100 pF jarang digunakan.

Karena kapasitor dibuat dalam langkah fabrikasi yang berbeda dengan

resistor, kesalahannya tidak dapat dilacak dengan resistor-resistor pada keping yang

sama. Kesalahan kapasitor sama tingkatnya dengan kesalahan resistor yakni sekitar

10%, sedangkan kesalahan anatara kapasitor yang sama dalam satu keping sekitar

3%, sehingga konstanta waktu RC bisa mencapai 20%. Kesalahan seperti ini

temperatur dan tegangan dari resistor dan kapasitor tidak terkolerasi, sehingga

konstanta waktu juga akan berubah terhadap temperatur dan arus isyarat.

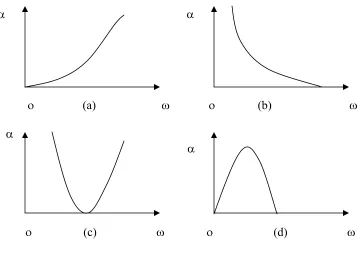

2.2.3.3. Kapasitor Tersaklar

Dari bahasan di atas dapat diketahui bahwa pemaduan elemen per elemen dari

tapis aktif RC tidak bisa memuaskan dalam hal keakuratan dan kestabilan yang

dikehendaki. Oleh karena itu diperlukan strategi lain. Ide kunci adalah dengan adanya

kapasitor tersaklar. Penemuan ini didasarkan atas kenyataan bahwa sebuah resistor

dapat disimulasikan dengan menggunakan saklar MOS yang dioperasikan secara

periodis dan sebuah kapasitor. Konstanta waktu dari rangkaian bukan lagi perkalian

RC tetapi merupakan perbandingan kapasitor. Sedangkan nilai resistansi setara

resistor berbanding lurus dengan perioda penyaklaran, atau berbanding terbalik

dengan frekuensi penyaklaran. Hubungan ini dapat dituliskan sebagai Req = 1 / ( C.

Fclok ).

Req C

2.2.3.4. Dasar Kapasitor Tersaklar

Banyak fungsi penapisan analog dibentuk oleh tapis aktif dengan Op-Amp

dapat ditiru dengan penggunaan untai kapasitor tersaklar. Untai kapasitor tersaklar

dibangun oleh Op-Amp, saklar MOS dan kapasitor-kapasitor yang nilai

kapasitansinya kecil. Bila Op-Amp terbuat dari MOS-FET, seluruh jaringan kapasitor

tersaklar tak mengandung resistor yang dapat dibangun pada untai terintegrasi

tunggal. Frekuensi kutub dan frekuensi nol dari untai kapasitor tersaklar dapat

dikendalikan dari luar melalui frekuensi clock. Kanampakan ini mengundang suatu

keuntungan yang prinsip disbanding tapis analog yang memakai resistor.

Gambar 2 – 5 Untai dasar kapasitor tersaklar

Dasar dari untai kapasitor tersaklar sebagai pengganti resistor terdapat pada

untai sederhana Gambar 2-5.a. Saklar sinkronisasi S1 dan S2 membuka dan menutup

setiap setengah siklus dari interval clock Tc dan secara periodic memuati dan

melucuti muatan pada kapasitor. Untuk susunan ini akan berfungsi sebagai resistor,

maka anggapan berikut ini harus dipenuhi.

1. Pada suatu saat tertentu hanya ada satu saklar yang tertutup; kedua

2. Selang waktu selama kedua saklar tidak tertutup sangat singkat

dibandingkan dengan periode detak Tc.

3. Apabila S1 tertutup, kapasitor memuati secara cepat tegangan isyarat

masukan vs.

4. Jika S2 tertutup, kapasitor segera melucuti muatan ke ground.

Selama interval S1 tertutup, muatan kapasitor mencapai nilai

………(2 – 5)

C q= vs

Muatan ini secara lengkap dilucuti ke ground ketika S2 tertutup. Dalam satu interval

clock Tc, muatan keseluruhan akibat tegangan vs adalah sama dengan :

Tc Cv t

q = s

∆ ∆

………(2 – 6)

Muatan ini harus secara terus menerus disuplai ke kapasitor dengan sumber vs,

karena muatan dilucuti ke ground setelah setiap siklus clock. Setelah beberapa siklus

clock, aliran muatan yang kontinyu dari vs arus tunak (steady) yang memiliki rerata

sama dengan :

Tc v C dt t q Tc

i 1 Tc . s )

(

0

1 =

∆ ∆

=

∫

……….(2 – 7)Perbandingan antara Tc dengan C mempunyai satuan resistansi (sec/Coulomb/Volt =

Ohm), oleh karena itu persamaan tersebut mempunyai bentuk hukum Ohm :

R v

i ) s /

( 1 = ………(2 – 8)

Mekanisme rugi-rugi dari untai kapasitor tersaklar Gambar 2 – 5.a dapat dimodelkan

2.3. Penapis lolos pita

(Bandpass Filter)

Sebagaimana tampak pada Gambar 2– 6, penapis lolos pita akan meneruskan

sinyal-sinyal dengan frekuensi antara (median frequency) dan menahan frekuensi di

bawah dan di atas median tersebut.

Untuk penapis lolos pita ini dikenal istilah frekuensi tengah (center

frequency) dan lebar pita (bandwidth), dengan pengertian sebagai berikut :

- Frekuensi tengah ( ) merupakan titik munculnya penguatan tegangan paling

besar (maksimum).

o

f

- Lebar pita (bandwidth) dari suatu penapis lolos pita adalah perbedaan antara

frekuensi atas dan bawah dibawah penguatan tegangannya (volt gain) yaitu

0,707 kali dari nilai maksimum atau 3 dB lebih rendah dari penguatan tegangan

frekuensi tengah, atau lebar pita

(BW) = fh − fl ……….( 2 – 9)

Karena semua tanggapan penapis digambar dengan skala log, maka terlihat

bahwa penapis lolos pita seakan-akan simetris pada frekuensi tengah. Bila

menganggap bahwa adalah ditengah-tengah dan maka hal tersebut tidak

benar. Ternyata frekuensi tengah sama dengan rata-rata geometri, atau dapat

dituliskan sebagai berikut :

o

f fh fl

l h o f f

f = . ………..(2 – 10)

jika dikatahui lebar pita dan frekuensi tengahnya maka :

2 / 1 2 2

2

] ) 2 ( )

[( o

l

f BW

BW

f = − + + ………(2 – 11)

BW f

fh = l + ……….(2 – 12)

Lebar pita (BW) dan frekuensi tengah ( ) memiliki hubungan satu sama lainnya

dengan factor kualitas atau Q :

o

f

BW f

Q= o

atau

l h

o

f f

f Q

−

= ………(2 – 14)

l h

l h

f f

f f Q

−

=( . )1/2 ………(2 – 15)

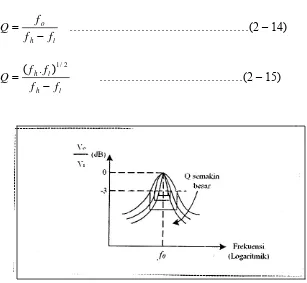

Gambar 2 – 7 Q pada penapis lolos pita

Sebagaimana terlihat pada Gambar 2 – 7, Q merupakan indeks “ketajaman

lengkungan” tanggapan amplitudo dari frekuensi tengah. Penyempitan lebar pita

mengakibatkan naiknya nilai Q (lihat persamaan 2 – 13).

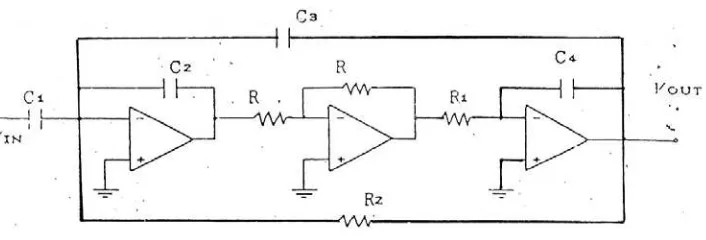

2.3.1. Untai Tapis Analog Pelewat Jalur

Untuk merealisasikan tapis pelewat jalur ke dalam untai yang nyata, dapat

dipakai untai RC yang disebut dengan Biquad. Untai Biquad ini dapat dilihat pada

Gambar 2 – 8. Pada untai ini mengandung tiga buah penguat operasi yang

untai integrator dengan isyarat masukan dari dan tegangan keluaran penguat

operasi ketiga. Penguat operasi yang kedua berfungsi sebagai penguat pembalik.

Sedangkan penguat operasi ketiga berfungsi sebagai pengintegral isyarat keluaran

penguat operasi yang kedua yang kemudian dimpankan kemasukan penguat operasi

pertama melalui dan . Terminal keluaran untai diambil pada keluaran penguat

operasi ketiga.

in

V

2

R C3

Gambar 2 – 8 Untai Tapis Pelewat Jalur menggunakan untai Biquad

Watak alih atau perbandingan besar isyarat keluaran dengan insyarat

masukan pada untai Biquad tersebut di atas dapat dituliskan sebagai berikut :

) / 1 ( )] /( [ )] /( [ 4 2 1 2 4 2 3 2 4 2 1 ) ( C C R R s R C C C s s R C C C T i i s + + −

= ………(2 – 12)

Watak alih tapis pelewat jalur standar dapat dituliskan sebagai :

2 2 ) ( ) / ( ) / ( o o o s s Q s s Q T ω ω ω + +

Dengan membandingkan watak alih di atas dengan persamaan Tapis pelewat jalur

standar, maka akan didapatkan besaran-besaran ωo, Q dan factor perolehan (H)

sebagai berikut :

) (

1

4 2 2 1R C C R

o = ω

Q = ( C2 / C1 ) (R1/R2) ………(2 – 14)

Apabila watak alih untai Biquad ini dinormalisasikan, dengan kata lain

membuat ωo = 1, dan ditentukan perolehan dibuat sama dengan satu, serta memilih

kapasitor sama dengan C, dan membuat nilai = 1, maka akan

diperoleh nilai komponen-komponen sebagai barikut : 4

3 2

1 C C C

C = = = R1

o

ω = 1

C C C C

C1 = 2 = 3 = 4 =

1 1 = R

2

R = 1 / Q2 ……… (2 – 15)

Pemilihan komponen yang lainnya bisa dilaksanakan, tetapi nilai-nilai

tersebut perlu disesuaikan dengan watak yang akan diharapkan. Serta perlu diketahui

bahwa nilai-nilai ternormalisasi ini akan diskala untuk memperoleh komponen yang

sesuai. Dengan menggunakan untai Biquad ini, untai tapis pelewat jalur mudah

dipahami.

Dimana dalam perancangan ditentukan,frekuensi pusat (fo) yang digunakan

filter yang dirancang adalah 2, maka dapat dicari bandwidth adalah dengan

menggunakan persamaan (2-13).

Q =

BW fo

BW =

2 4000

BW = 2000 Hz

Besarnya frekuensi bawah (lower frequency = ) dapat dihitung dengan

menggunakan persamaan (2-11).

l

f

2 / 1 2 2

2

] ) 2 ( )

[( o

l

f BW

BW

f = − + +

2 / 1 2 2

2

] ) 4000 2 ( ) 2000 [(

2000 x

fl = − + + = 3123,1056 Hz

Besarnya frekuensi atas (upper frequency = f ) dapat dihitung dengan menggunakan

persamaan 2 – 12

h

BW f

fh = l + = 3123.1056 Hz + 2000 Hz = 5123.1056 Hz

Besarnya ωo dapat di cari juga dengan menggunakan

o

ω = 2 . π . f 0 ………( 2 – 16)

Sehingga

o

ω = 2 . π . 4000 Hz

BAB III

PERANCANGAN TAPIS KAPASITOR TERSAKLAR

Di dalam merancang untai tapis dengan kapasitor tersaklar perlu diperhatikan

adanya frekuensi detak yang akan mengaktifkan saklar-saklar MOS yang dipergunakan,

frekuensi detak ini yang menentukan watak tapis dengan kapasitor tersaklar. Hal ini

merupakan salah satu cara untuk mengubah tapis dengan kapasitor tersaklar.

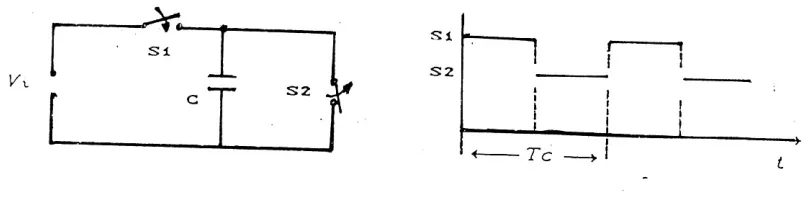

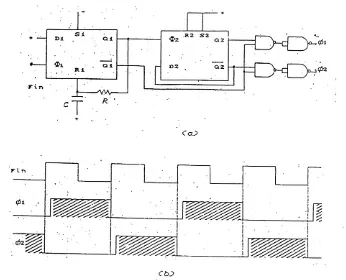

3.1 Pembangkit detak dua fase non overlap

Untai frekuensi detak untuk penyaklaran saklar MOS berupa pembangkit detak

dua fase yang tidak saling tumpang tindih (non-overlap). Untuk mendapatkan detak yang

–overlap digunakan rangkaian seperti yang ditunjukkan pada Gambar 3 – 1.

Keluaran rangkaian ini berupa φ1 dan φ2, yang keduanya tidak saling tumpang

tindih. Besarnya frekuensi isyarat keluaran detak adalah setengah dari frekuensi masukan.

Sedangkan lebar sela antara φ1 dan φ2, ditentukan oleh konstanta waktu RC yang

Gambar 3 – 1 (a). Untai pembangkit detak dua fase non-overlap, (b). bentuk gelombang penyaklaran.

Frekuensi masukan pembangkit detak dua fase non-overlap dihasilkan dari

pembangkit detak yang dapat dikendalikan tegangan.

3.2. Untai Tapis Pelewat Jalur

Realisasi untai tapis pelewat jalur dengan menggunakan kapasitor tersaklar, dalam

hal ini didasarkan pada untai tapis analog pelewat jalur dengan untai Biquad.

Dengan menggantikan resistor pada untai analog Biquad dengan kapasitor

tersaklar bias menghasilkan untai tapis dengan kapasitor tersaklar. Namun dalam hal ini

perlu memperhatikan posisi saklar agar didapatkan kombinasi yang tepat. Dalam untai

dengan (pada untai analog). Sehingga untuk merealisasikan ke untai kapasitor

tersaklar untai pembalik ini bisa digantikan dengan kombinasi saklar. Kemudian seluruh

nilai kapasitor, sampai dengan , dibuat mempunyai nilai kapasitansi yang sama.

Sehingga hanya dua buah kapasitor tersaklar yang dipakai untuk membentuk tapis

pelewat jalur orde pertama. Dengan demikian didapatkan penyederhanaan susunan

saklar pada untai ini. Untai kapasitor tersaklar pelewat jalur dapat dilihat pada Gambar 3

– 2.

2

R

1

C C4

.

.

+

-. .

3 2

1 4

5

.

.

. C

+

-.

3 2

1 4

5

CR1 . .

. .

.

CR2

Gambar 3 – 2. BPF dengan kapasitor tersaklar.

Watak alih tapis pelewat jalur dengan kapasitor tersaklar ini dapat dilihat pada

tapis analog, dengan menggantikan resistor menggunakan kapasitor tersaklar setaranya.

Frekuensi pusat tapis ini ditentukan oleh nilai-nilai kapasitor yang terdapat pada umpan

balik integrator dan kapasitor-kapasitor tersaklar pengganti resistor dapat dituliskan

seperti pada persamaan 3 – 1. Sedangkan factor kualitas dari untai ini, yang diturunkan

2 1. R R clk

o C C

C F

=

ω ………(3 – 1)

1 2

R R

C C

Q = ……….(3 – 2)

Untuk perancangan untai pelewat jalur dengan kapasitor tersaklar, selain

spesifikasi tapis, perlu diketahui terlebih dahulu frekuensi penyaklaran tapis, serta salah

satu dari : kapasitor-kapasitor tersaklar atau kapasitor pada umpan balik negativ

integrator. Jadi bila telah diketahui ω0, Q, Fclock, dan nilai-nilai kapasitor utama, maka

langkah perancangan tinggal mencari nilai-nilai kapasitor tersaklar. Pada tapis analog

diketahui bahwa saat normalisasi didapatkan

1 R

C = ω0 C / (Q Fclk). ………...(3 – 3)

2 R

C = ω0 C Q / Fclk ………...(3 – 4)

Dalam perancangan didapat nilai-nilai untukCR1 dan CR2,adalah :

Ditentukan nilai C = 1 nF, Fclk = 150 KHz, dan ω0 = 25.132741 rad/sec

Untuk merealisasikan tapis pelewat jalur dengan kapasitor tersaklar dengan orde

pola dasar lebih dari satu diperlukan untai yang harus dikaskade. Untuk mengkaskade

29

BAB IV

DATA PENGAMATAN

Realisasi kapasitor tersaklar menggunakan komponen-komponen utama berupa

kapasitor dan saklar. Nilai –nilai kapasitor dicari dengan menggunakan perumusan yang

telah dijelaskan pada bab sebelumnya. Hasil perhitungan nilai-nilai kapasitor yang

dipakai untuk membuat,dicantumkan pada bab ini. Untai realisasi tapis dengan

menggunakan kapasitor tersaklar secara lengkap terdapat pada bagian ini.

Salah satu watak tapis yang diamati adalah tenggapan frekuensi tapis. Tanggapan

frekuensi tapis dinyatakan dalam besaran yang merupakan perbandingan tegangan isyarat

keluaran tapis, dengan tegangan isyarat masukan tapis sebagai fungsi dari frekuensi

isyarat.

Setelah didapatkan tenggapan frekuensi tapis, maka perlu diketahui beberapa hala

dari tapis pelewat jalur, yaitu frekuensi pusat dan lebar jalur (BW).

4.1 Nilai-nilai Perancangan Tapis Pelewat Jalur

Nilai-nilai komponen yang dipakai untuk membangun untai kapasitor dan untai

tapis diberikan pada bagian ini.

Spesifikasi tapis pelewat jalur dan nilai-nilai komponen yang dipakai untuk

merealisasikan tapis dengan kapasitor tersaklar adalah sebagai berikut :

n = 2

30

Fo = 4 KHz

Fclk = 150 KHz

Q = 2

BW = 2000 Hz

0

ω = 2 . π f0

= 25,132741 rad/sec

oi

ω = ωo / BW

= 12,566371 rad/sec

2 o

ω = ωo . BW

= 50,26548 rad/sec

Pada perancangan, dibuat untuk semua nilai C = 1 nF

Untuk ωoi = 12,566371 rad/sec dan ω 02 = 50,26548 rad/sec.

=

11 R

C ωoi C / ( Q . Fclk )

= 40 pF

= 20 + 20 = 40 pF

CR21 = ωoi C / Fclk

= 80 pF

= 20pF + 20 pF + 20 pF + 20 pF

CR12 = ωoi C / ( Q . Fclk )

` = 0,17 µF

31

CR22 = ω 02 C / Fclk

= 0,33 µF

4.2

Pengamatan Tanggapan Frekuensi

Untuk mendapatkan perbandingan besar isyarat keluaran dengan isyarat masukan,

dilakukan pengamatan dengan cara memberikan isyarat pada masukan yang telah

diketahui frekuensinya dan dengan mengukur amplitudonya, kemudian melihat besar

amplitudo isyarat keluaran tapis. Hal ini dilakukan untuk beberapa macam frekuensi

dalam jangkauan frekuensi-frekuensi audio yakni sekitar 800 Hz sampai 20 Khz.

Kemudian dari nilai-nilai yang diperoleh, dilakukan perbandingan antara nilai amplitudo

keluaran dengan amplitudo masukan. Tanggapan frekuensi tapis biasanya dinyatakan

dalam deci Bell (dB). Oleh karenanya, nilai perbandingan amplitudo tersebut perlu dicari

nilai logaritmisnya, lalu dikalikan dengan faktor 20. Bila dinyatakan dalam persamaan

menjadi :

A(f) = 20 log (Vout / Vin) dalam dB

A(f) menyatakan besar tanggapan sebagai fungsi frekuensi. Tanggapan akan bernilai

positif bila amplitude keluaran lebih besar dari amplitude masukan, bernilai nol bila

masukan sama dengan keluaran, dan bernilai negative bila keluaran lebih kecil dari

masukan.

Setelah mendapatkan besarnya tanggapan untuk tiap-tiap frekuensi tertentu, agar

dapat mengetahui juga kurva tanggapan tapis maka perlu digambarkan grafik hubungan

32

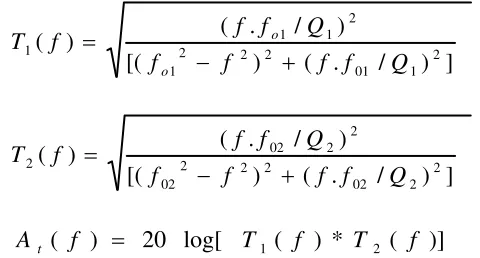

4.2.1 Tapis Pelewat Jalur

Tanggapan tapis pelewat jalur dengan menggunakan kapasiyor tersaklar dapat

dilihat pada tebel 4 – 1, dan dengan gambar 4 – 1. Sedangkan untuk tanggapan tapis

secara perhitungan terdapat pada table 4 – 1. Tanggapan secara teoritis dari pelewat jalur

orde ke-2 dengan fo = 4 KHz, qc = 2, dapat dicari dengan memakai persamaan

sebagai berikut. ] ) / . ( ) [( ) / . ( ) ( 2 1 01 2 2 2 1 2 1 1 1 Q f f f f Q f f f T o o + − = ] ) / . ( ) [( ) / . ( ) ( 2 2 02 2 2 2 02 2 2 02 2 Q f f f f Q f f f T + − = )] ( * ) ( log[ 20 )

( f T1 f T2 f

At =

dengan dan merupakan fungsi alih tegangan untuk tiap orde, sedangkan

tanggapan tapis keseluruhan dinyatakan dalam A(f), dengan nilai = = 3123,1056

Hz dan = = 5123,1036 Hz, dan )

(

1 f

T T2(f )

01

f fl

02

f fh Q1 =Q2= 2.

Tabel 4 – 1.

BPF N = 2, Fclk = 150 KHz, Vi = 3Vpp

Frekuensi (Hz) Vo (V) A (dB) At (dB)

800 0,010 - 49,5439 - 40,9829

1000 0,020 - 43,5227 - 37,1119

1200 0,045 - 36,4782 - 33,8629

1500 0,060 - 33,9794 - 29,6746

1700 0,080 - 31,4804 - 25,4342

2000 0,100 - 29,5433 - 23,6288

2200 0,400 - 17,5033 - 21,3363

3000 0,900 - 10,4575 - 11,5187

3200 1,150 - 8,3360 - 8,5147

3400 1,250 - 7,6056 - 4,9713

3600 1,480 - 6,1377 - 0,4136

3800 1,500 - 6,0206 2,1492

33

4000 1,480 - 6,1377 -1,478 x 10−7

4200 1,430 - 6,4369 -2,7444

4400 1,375 - 6,7764 -1,5592

4600 1,300 - 7,2702 -1,1881

4800 1,100 - 8,7303 -1,0267

5000 1,000 - 9,5425 -0,9559

5500 0,600 -13,9794 -1,0076

6000 0,450 - 16,4781 -1,5193

7000 0,250 - 21,5839 1,4352

8000 0,150 - 26,0206 0,3552

10000 0,075 - 32,0412 0,1555

15000 0,030 - 40 0,02926

20000 0,005 - 55,5034 0,01381

A (f) = 20 log (Vo / Vi)

At (f) = 20 log [T1 (f) * T2(f)]

4.3

Karakteristik Tapis Pelewat Jalur dengan Kapasitor Tersaklar

Untuk mengetahui kebenaran dari tapis pelewat jalur yang telah dibuat yang

dibandingkan dengan watak tapis pelewat jalur perancangan, maka dari watak yang telah

digambarkan perlu diketahui beberapa hal antara lain, dicari lebar pita pelewat dan

frekuensi pusat pelewat.

Frekuensi pusat pada tapis pelewat jalur merupakan frekuensi dengan penguatan

yang paling besar atau penguatan pada puncak kurva tanggapan frekuensi tapis pelewat

jalur. Dalam hasil pengamatan, penguatan maksimal sebesar -6,0206 dB yang terdapat

pada frekuensi 3900 Hz.

Lebar jalur pelewat pada BPF dapat ditentukan dengan mencari frekuensi

setengah daya (frekeunsi 3 – dB) pada kedua sisi peralihan tapis. Bila frekensi 3 – dB

yang berada di atas frekuensi pusat dinyatakan dengan f02 = fh dan frekuensi 3 – dB yang berada di bawah frekuensi pusat dinyatakan dengan f01 = fl, maka lebar pelewat

34

BW = f02 − f01

4.3.1. Hubungan Frekuensi penyaklaran dengan tanggapan frekuensi

Untuk mengetahui pengaruh frekuensi penyaklar terhadap tanggapan frekuensi

dari Butterworth dengan kapasitor tersaklar, dilakukan pengamatan terhadap frekuensi

pusat.

Besar frekuensi pusat pada tapis pelewat jalur dinyatakan sebagai :

o

ϖ =

C Fclk

(CR1.CR2)

dengan

o

ω = 2πFo, maka

Fo =

C Fclk

.

2π (CR1.CR2)

Dengan nilai kapasitor-kapasitor C, , dan yang sudah tertentu, maka hubungan

Fo terhadap Fclk adalah linier. Dari sini terlihat bahwa bila Fclk naik maka Fo akan naik

dan sebaliknya.

1 R

BAB V

PENUTUP

Tapis dalam pengolahan isyarat listrik memiliki arti mengambil suatu komponen

frekuensi tertentu dari suatu isyarat dan menolak komponen frekuensi lain.

Tapis Butterwoth adalah tapis yang memiliki tanggapan datar secara meksimal

pada jalur pelewat. Sebuah hambatan dapat diganti dengan menggunakan kapasitor

tersaklar yang dinyatakan dengan Req =

R clkC

F

1

dengan adalah frekuensi clock dan

adalah kapasitor tersaklar dan Req adalah resistansi.

clk

f

R

C

Perancangan tapis Butterworth dengan menggunakan kapasitor tersaklar bias

dilakukan dengan terlebih dulu merancang untai analognya dan kemudian merealisasikan

kedalam untai yang memakai kapasitor tersaklar, dengan menggantikan resistor dengan

kapasitor tersaklar.

Untai keempat jenis tapis Butterworth dengan menggunakan kapasitor tersaklar

yang telah direalisasikan dengan frekuensi penyaklar 150 KHz. Untuk BPF fo = 400 Hz,

f = 3123,1056 Hz, f01 02 = 5123,1056 Hz, dan BW = 2 KHz.

Beberapa hal yang dapat menyebabkan kesalahan watak tapis hasil perancangan

jika dibandingkan dengan perhitungan antara lain : sifat-sifat dari komponen pembangun

DAFTAR PUSTAKA

• Eko Putranto, Afgianto, Penapis Aktif Elektronika : teori dan Praktek,

C.V. Gava Media Yogyakarta

• Franco, S., Design with Operational Amplifier and Analog Integrated

Circuit, Mc Graww Hill Book Co., Singapore, 1988.

• Parker, S P., Mc Graw Hill Concise Encyclopedia of Science and

Technology, Mc Graw Hill, Inc., New York, 1984.

• Http://www.yahoo.com

• Http://www.Panorama.net

U1C

CD4093B

8

9

10

995114071 Pembangkit Detak dua f ase

A

1 1

Sunday , January 28, 2007 Title

Size Document Number Rev

Date: Sheet of

Vin

U3B

CD4093B

5

6

4

R1

1k5

Q-1

+ VCC

U5B

CD4013B

8

9

11 13

12

10

SET

D CLK

Q Q

R

ESE

T

Q-2

200pF C

U2D

CD4093B

13

12

11

U4A

CD4093B

1

2

3

U6A

CD4013B

6

5

3 1

2

4

SET

D CLK

Q Q

RE

S

E

T

R2

Q2 + -LF353N 8 1 2 4 3 Q2 C C C EN1 1 1 > > < < U5A 4016 2 1 13 EN1 1 1 > > < < U2B 4016 10 11 12 CR11 Q1 EN1 1 1 > > < < U6B 4016 10 11 12 Q1 + -LF353N 8 1 2 4 3 Q1 Q2 Q2 Q1 C Q2 Voi Vin EN1 1 1 > > < < U1A 4016 2 1 Q1 + -LF353N 8 7 6 4 5 Q1 C CR21 EN1 1 1 > > < < U1A 4016 2 1 Q1 CR22 + -LF353N 8 7 6 4 5 EN1 1 1 > > < < U6B 4016 10 11 12 EN1

1 1 > > < < U7D 4016 9 8 6 Vout C Q2 EN1 1 1 > > < < U3C 4016 3 4 5 EN1

1 1 > > < < U2B 4016 10 11 12 CR12 C 995114071

BPF N=2 DENGAN KAPASITOR TERSAKLAR

A

1 1

Sunday , February 04, 2007 Title

Size Document Number Rev

Date: Sheet of

Voi

LF353

Wide Bandwidth Dual JFET Input Operational Amplifier

General DescriptionThese devices are low cost, high speed, dual JFET input operational amplifiers with an internally trimmed input offset voltage (BI-FET II™ technology). They require low supply current yet maintain a large gain bandwidth product and fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The LF353 is pin compatible with the standard LM1558 allowing designers to immediately upgrade the overall performance of existing LM1558 and LM358 designs.

These amplifiers may be used in applications such as high speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low input offset voltage, low input bias current, high input impedance, high slew rate and wide bandwidth. The devices also exhibit low noise and offset voltage drift.

Features

n Internally trimmed offset voltage: 10 mV

n Low input bias current: 50pA

n Low input noise voltage: 25 nV/√Hz

n Low input noise current: 0.01 pA/√Hz

n Wide gain bandwidth: 4 MHz

n High slew rate: 13 V/µs

n Low supply current: 3.6 mA

n High input impedance: 1012Ω n Low total harmonic distortion : ≤0.02%

n Low 1/f noise corner: 50 Hz

n Fast settling time to 0.01%: 2 µs

Typical Connection

00564914

Simplified Schematic

1/2 Dual

00564916

Connection Diagram

Dual-In-Line Package

00564917 Top View

Order Number LF353M, LF353MX or LF353N See NS Package Number M08A or N08E

BI-FET II™is a trademark of National Semiconductor Corporation.

December 2003

LF353

W

ide

Bandwidth

Dual

JFET

Input

Operational

Amplifier

Absolute Maximum Ratings(Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ±18V

Power Dissipation (Note 2) Operating Temperature Range 0˚C to +70˚C

Tj(MAX) 150˚C

Differential Input Voltage ±30V Input Voltage Range (Note 3) ±15V Output Short Circuit Duration Continuous Storage Temperature Range −65˚C to +150˚C Lead Temp. (Soldering, 10 sec.) 260˚C Soldering Information

Dual-In-Line Package

Soldering (10 sec.) 260˚C

Small Outline Package

Vapor Phase (60 sec.) 215˚C Infrared (15 sec.) 220˚C See AN-450 “Surface Mounting Methods and Their Effect on Product Reliability” for other methods of soldering surface mount devices.

ESD Tolerance (Note 8) 1000V

θJAM Package TBD

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Elec-trical Characteristics state DC and AC elecElec-trical specifications under particu-lar test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guar-anteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

DC Electrical Characteristics

(Note 5)

Symbol Parameter Conditions LF353 Units

MIn Typ Max

VOS Input Offset Voltage RS=10kΩ, TA=25˚C 5 10 mV

Over Temperature 13 mV

∆VOS/∆T Average TC of Input Offset Voltage RS=10 kΩ 10 µV/˚C

IOS Input Offset Current Tj=25˚C, (Notes 5, 6) 25 100 pA

Tj≤70˚C 4 nA

IB Input Bias Current Tj=25˚C, (Notes 5, 6) 50 200 pA

Tj≤70˚C 8 nA

RIN Input Resistance Tj=25˚C 1012 Ω

AVOL Large Signal Voltage Gain VS=±15V, TA=25˚C 25 100 V/mV

VO=±10V, RL=2 kΩ

Over Temperature 15 V/mV

VO Output Voltage Swing VS=±15V, RL=10kΩ ±12 ±13.5 V

VCM Input Common-Mode Voltage VS=±15V ±11 +15 V

Range −12 V

CMRR Common-Mode Rejection Ratio RS≤10kΩ 70 100 dB

PSRR Supply Voltage Rejection Ratio (Note 7) 70 100 dB

IS Supply Current 3.6 6.5 mA

AC Electrical Characteristics

(Note 5)

Symbol Parameter Conditions LF353 Units

Min Typ Max

Amplifier to Amplifier Coupling TA=25˚C, f=1 Hz−20 kHz −120 dB

(Input Referred)

SR Slew Rate VS=±15V, TA=25˚C 8.0 13 V/µs

GBW Gain Bandwidth Product VS=±15V, TA=25˚C 2.7 4 MHz

en Equivalent Input Noise Voltage TA=25˚C, RS=100Ω, 16

f=1000 Hz

in Equivalent Input Noise Current Tj=25˚C, f=1000 Hz 0.01

LF353

AC Electrical Characteristics (Continued) (Note 5)

Symbol Parameter Conditions LF353 Units

Min Typ Max

THD Total Harmonic Distortion AV=+10, RL=10k,

VO=20Vp−p,

BW=20 Hz-20 kHz

<0.02 %

Note 2: For operating at elevated temperatures, the device must be derated based on a thermal resistance of 115˚C/W typ junction to ambient for the N package, and 158˚C/W typ junction to ambient for the H package.

Note 3: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

Note 4: The power dissipation limit, however, cannot be exceeded.

Note 5: These specifications apply for VS=±15V and 0˚C≤TA≤+70˚C. VOS, IBand IOSare measured at VCM=0.

Note 6: The input bias currents are junction leakage currents which approximately double for every 10˚C increase in the junction temperature, Tj. Due to the limited

production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, PD. Tj=TA+θjAPDwhereθjAis the thermal resistance from junction to ambient. Use of a heat sink is

recommended if input bias current is to be kept to a minimum.

Note 7: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice. VS

=±6V to±15V.

Note 8: Human body model, 1.5 kΩin series with 100 pF.

Typical Performance Characteristics

Input Bias Current Input Bias Current

00564918

00564919

Supply Current Positive Common-Mode Input Voltage Limit

00564920

00564921

LF353

Typical Performance Characteristics (Continued)

Negative Common-Mode Input Voltage Limit Positive Current Limit

00564922 00564923

Negative Current Limit Voltage Swing

00564924 00564925

Output Voltage Swing Gain Bandwidth

00564926 00564927

LF353

Typical Performance Characteristics (Continued)

Bode Plot Slew Rate

00564928 00564929

Distortion vs. Frequency Undistorted Output Voltage Swing

00564930 00564931

Open Loop Frequency Response Common-Mode Rejection Ratio

00564932 00564933

LF353

Typical Performance Characteristics (Continued)

Power Supply Rejection Ratio Equivalent Input Noise Voltage

00564934 00564935

Open Loop Voltage Gain (V/V) Output Impedance

00564936 00564937

Inverter Settling Time

00564938

LF353

Pulse Response

Small Signaling Inverting

00564904

Large Signal Inverting

00564906

Small Signal Non-Inverting

00564905

Large Signal Non-Inverting

00564907

Current Limit (RL= 100Ω)

00564908

Application Hints

These devices are op amps with an internally trimmed input offset voltage and JFET input devices (BI-FET II). These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore, large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the

supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.

Exceeding the negative common-mode limit on either input will force the output to a high state, potentially causing a reversal of phase to the output. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur

LF353

Application Hints (Continued)

since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode.

Exceeding the positive common-mode limit on a single input will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

The amplifiers will operate with a common-mode input volt-age equal to the positive supply; however, the gain band-width and slew rate may be decreased in this condition. When the negative common-mode voltage swings to within 3V of the negative supply, an increase in input offset voltage may occur.

Each amplifier is individually biased by a zener reference which allows normal circuit operation on ±6V power sup-plies. Supply voltages less than these may result in lower gain bandwidth and slew rate.

The amplifiers will drive a 2 kΩload resistance to±10V over the full temperature range of 0˚C to +70˚C. If the amplifier is forced to drive heavier load currents, however, an increase in input offset voltage may occur on the negative voltage swing and finally reach an active current limit on both posi-tive and negaposi-tive swings.

Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity

or that the unit is not inadvertently installed backwards in a socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.

As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize “pick-up” and maximize the frequency of the feed-back pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feed-back pole is less than approximately 6 times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

Detailed Schematic

00564909

LF353

Typical Applications

Three-Band Active Tone Control

00564939

00564940

Note 1:All controls flat.

Note 2:Bass and treble boost, mid flat.

Note 3:Bass and treble cut, mid flat.

Note 4:Mid boost, bass and treble flat.

Note 5:Mid cut, bass and treble flat.

• All potentiometers are linear taper

• Use the LF347 Quad for stereo applications

LF353

Typical Applications (Continued)

Improved CMRR Instrumentation Amplifier

00564941

Fourth Order Low Pass Butterworth Filter

00564942

LF353

Typical Applications (Continued)

Fourth Order High Pass Butterworth Filter

00564943

LF353

Typical Applications (Continued)

Ohms to Volts Converter

00564944

LF353

Physical Dimensions inches (millimeters) unless otherwise noted

Order Number LF353M or LF353MX NS Package Number M08A

Molded Dual-In-Line Package Order Number LF353N

NS Package N08E

LF353

Notes

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no ‘‘Banned Substances’’ as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Customer Support Center

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center

Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center

Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

www.national.com

LF353

W

ide

Bandwidth

Dual

JFET

Input

Operational

Amplifier

JFET Input

Operational Amplifiers

These low cost JFET input operational amplifiers combine two state–of–the–art analog technologies on a single monolithic integrated circuit. Each internally compensated operational amplifier has well matched high voltage JFET input devices for low input offset voltage. The JFET technology provides wide bandwidths and fast slew rates with low input bias currents, input offset currents, and supply currents.

These devices are available in single, dual and quad operational amplifiers which are pin–compatible with the industry standard MC1741, MC1458, and the MC3403/LM324 bipolar devices.

• Input Offset Voltage of 5.0 mV Max (LF347B)

• Low Input Bias Current: 50 pA

• Low Input Noise Voltage: 16 nV/ Hzv

• Wide Gain Bandwidth: 4.0 MHz

• High Slew Rate: 13V/µs

• Low Supply Current: 1.8 mA per Amplifier

• High Input Impedance: 1012 Ω

• High Common Mode and Supply Voltage Rejection Ratios: 100 dB

MAXIMUM RATINGS

Rating Symbol Value Unit

Supply Voltage VCC +18 V

VEE –18

Differential Input Voltage VID ±30 V

Input Voltage Range (Note 1) VIDR ±15 V

Output Short Circuit Duration (Note 2) tSC Continuous

Power Dissipation at TA = +25°C PD 900 mW

Derate above TA =+25°C 1/θJA 10 mW/°C

Operating Ambient Temperature Range TA 0 to +70 °C

Operating Junction Temperature Range TJ 115 °C

Storage Temperature Range Tstg – 65 to

+150

°C

NOTES:1. Unless otherwise specified, the absolute maximum negative input voltage is limited to the negative power supply.

2. Any amplifier output can be shorted to ground indefinitely. However, if more than one amplifier output is shorted simultaneously, maximum junction temperature rating may be exceeded.

ON Semiconductort

Semiconductor Components Industries, LLC, 2002

March, 2002 – Rev. 1

1 Publication Order Number:

LF347/D

LF347, B

LF351

LF353

FAMILY OF JFET OPERATIONAL AMPLIFIERS D SUFFIX PLASTIC PACKAGE CASE 751 (SO–8) N SUFFIX PLASTIC PACKAGE CASE 626 1 1 8 8 Output A Inputs A VEE VCC Output B Inputs B LF351 (Top View) LF353 (Top View) Offset Null Invt Input Noninvt Input VEE NC VCC Output Offset Null 1 2 3 4 8 7 6 5 + -+ + A B 1 2 3 4 8 7 6 5 PIN CONNECTIONS N SUFFIX PLASTIC PACKAGE CASE 646 14 1 (Top View) Out 1 Inputs 1 VCC Inputs 2 Out 2 Out 4 Inputs 4 VEE Inputs 3 Out 3 1 2 3 4 5 6 7 8 9 10 11 12 13 14 4 2 3 + + + + 1 - -- -PIN CONNECTIONS ORDERING INFORMATION Function Device Package Operating Temperature Range LF351D LF351N Single Single

TA = 0° to +70°C

LF347, B LF351 LF353

http://onsemi.com

2

ELECTRICAL CHARACTERISTICS (VCC = +15 VEE = –15 V, TA = 25°C, unless otherwise noted.)

LF347B LF347, LF351, LF353

Characteristic Symbol Min Typ Max Min Typ Max<