Sistem Pengaturan dan Pemantauan Kecepatan Putar Motor DC

berbasis FPGA dan VHDL

Agfianto Eko Putra

1, Rahadian Mu’alif

2

1,2

Program Studi Elektronika dan Instumentasi, Jurusan Ilmu Komputer dan Elektronika, Fakultas MIPA Universitas Gadjah Mada - Yogyakarta 55281

1

[email protected], [email protected]

Abstrak - Telah diimplementasikan sebuah rangkaian digital untuk pengaturan dan pemantauan kecepatan putar motor DC ke dalam FPGA Altera EPF10K10 menggunakan VHSIC Hardware Description Language (VHDL). Sistem terdiri dari rangkaian penggerak dan rangkaian pembaca kecepatan putar motor DC. Sistem ini dapat menggerakkan motor DC dengan 10 variasi kecepatan dan besarnya kecepatan putar tersebut ditampilkan melalui 7-Segmen. FPGA menghasilkan luaran Pulse Width Modulation (PWM) untuk menggerakkan motor DC. Besarnya kecepatan putar motor DC dibaca oleh sensor optokopler kemudian diteruskan ke FPGA untuk ditampilkan nilainya melalui 7-segmen dalam satuan Rotasi per Detik (RPD). Hasil pengujian luaran PWM pada FPGA menggunakan metode regresi linier, diperoleh ralat sebesar 0,04. Hasil pengujian kecepatan putar motor DC untuk arah putaran searah jarum jam yaitu dengan ralat sebesar 0,70. Sedangkan untuk yang berlawanan jarum jam diperoleh ralat sebesar 0,75. Jumlah LE dalam FPGA yang digunakan adalah 262 atau 45% dari kapasitas total LE yang dimiki FPGA Altera EPF10K10.

Kata kunci: FPGA, VHDL, PWM, Motor DC 1.PENDAHULUAN

Kendali PWM adalah suatu teknik pengendalian rangkaian analog dengan suatu keluaran pengolah digital [1]. Keluaran pengolah digital ini berupa pulsa dengan periode tertentu, dimana lebar pulsa high-nya divariasikan. PWM ini biasanya digunakan dalam pengiriman data digital, regulasi tegangan, efek suara, dan penguatan.

Motor DC bisa diatur kecepatan putarnya melalui

Pulse Width Modulation atau PWM, dengan

memanfaatkan chip FPGA sebagai inti rangkaian pengendalinya. Besarnya kecepatan putar motor DC (Rotasi per Detik atau RPD) dibaca oleh sensor dan ditampilkan melalui 7-Segmen juga menggunakan FPGA. Penggunaan FPGA ini diharapkan dapat menjadi sebuah alternatif terobosan baru dalam mengatur kecepatan putar motor DC selain menggunakan mikrokontroler, mikroprosesor maupun

chip lainnya.

2.RANCANGAN SISTEM DIGITAL

Sistem pengontrolan kecepatan motor DC ini

menggunakan luaran PWM yang dihasilkan melalui rangkaian digital yang diimplementasikan ke dalam FPGA Altera EPF10K10 dengan 10 macam variasi PWM (sekaligus 10 macam kecepatan putar).

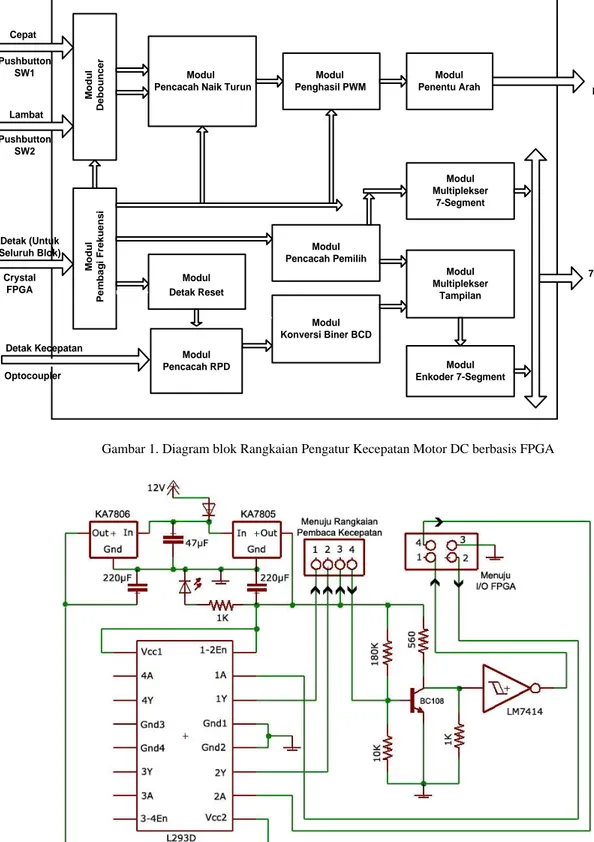

Sebagaimana ditunjukkan pada Gambar 1, digunakan dua buah tombol (SW1 dan SW2) yang masing-masing digunakan untuk melebarkan pulsa high PWM dan menyempitkan lebar pulsa high PWM. Dengan melebarnya pulsa high PWM maka motor DC berputar makin cepat, sebaliknya dengan menyempitnya pulsa

high PWM maka motor berputar makin lambat. Saklar

geser atau dipswitch digunakan untuk mengatur arah perputaran motor DC yaitu searah atau berlawanan jarum jam. Luaran FPGA yang berupa sinyal PWM dihubungkan dengan rangkaian penggerak motor DC. Selanjutnya, kecepatan putar motor DC dibaca oleh sensor rotary plate yang luarannya berupa pulsa yang kemudian diumpankan ke FPGA untuk proses pembacaan, hasilnya ditampilkan dalam ratusan (tiga digit) melalui 7-segmen.

2.1. Modul Pembagi Frekuensi

Modul ini digunakan untuk membagi frekuensi yang dihasilkan oleh osilator agar sesuai dengan kebutuhan detak modul rangkaian yang lain. Dalam hal ini osilator detak pada papan perancangan memiliki frekuensi sebesar 9,6 MHz. Berikut kode VHDL-nya:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY Pembagi_Frekuensi IS PORT ( Clk : in std_logic; Clock1 : out std_logic; Clock2 : out std_logic); END Pembagi_Frekuensi;

ARCHITECTURE Behavioral OF Pembagi_Frekuensi IS

SIGNAL Counter : std_logic_vector (23 downto 0);

BEGIN

PROCESS (Clk) BEGIN

if (Clk'event and Clk='1') then Counter <= Counter + 1; end if;

Clock1 <= Counter(9); Clock2 <= Counter(15); END PROCESS;

END Behavioral;

2.2. Modul Debouncer

Modul ini digunakan untuk mengurangi efek bouncing yang biasa terjadi jika pushbutton pada papan pengembangan wizard FLEX-A01 ditekan. Berikut kode VHDL-nya:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Debouncer IS PORT( Input1, Input2 : in std_logic; Output1, Output2 : out std_logic); END Debouncer;

ARCHITECTURE structural OF Debouncer IS COMPONENT D_flipflop IS PORT(

D, Clock: in std_logic; Q: out std_logic); END COMPONENT;

SIGNAL SQ1, SQ2: std_logic;

SIGNAL Sin, Sout, Sout2: std_logic; BEGIN

Sin<=not(Input1);

A0: D_flipflop port map(Sin, Input2, SQ1); A1: D_flipflop port map(SQ1, Input2, SQ2); Sout<=(not(SQ2) and SQ1);

Sout2<=(not(Sout)); Output1<=Sout; Output2<=Sout2; END structural;

2.3. Modul Pencacah Naik Turun

Modul ini digunakan sebagai pencacah naik dan turun, mulai dari 1 sampai dengan 10, yang kemudian diumpankan luarannya ke modul penghasil PWM.

2.4. Modul Penghasil PWM

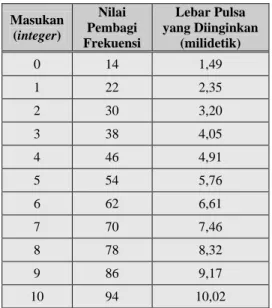

Pengaturan kecepatan putaran dilakukan dengan menggunakan menggunakan Pulse Width Modulation atau biasa disingkat sebagai PWM. Teknik PWM adalah cara pengalihan daya menggunakan sistem lebar pulsa untuk mengemudikan kecepatan motor. Pengaturan lebar pulsa ini menentukan kecepatan putar motor. Hubungan antara masukan terhadap luaran PWM ditunjukkan pada Tabel 1.

Berikut kode VHDL untuk modul yang menghasilkan sinyal PWM:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY Penghasil_PWM IS PORT( Clock: in std_logic;

Input: in std_logic_vector (3 downto 0); PWM : out std_logic);

END Penghasil_PWM;

ARCHITECTURE Behavioral OF Penghasil_PWM IS

SIGNAL counter : integer;

SIGNAL penentu_putaran : integer; SIGNAL PWMi : std_logic;

SIGNAL faktor : integer; BEGIN

PROCESS(Clock) BEGIN

faktor <= conv_integer (input); penentu_putaran <= 14 + (8 * faktor); if (Clock'event and Clock='1') then if (counter = 94) then

counter <= 0;

else counter <= counter + 1; end if;

end if;

if rising_edge(Clock) then

if (counter <= penentu_putaran ) then PWMi <= '1'; else PWMi <= '0'; end if; end if; END PROCESS; PWM <= PWMi; END Behavioral;

Tabel 1. Hubungan Masukan dan Luaran PWM Masukan (integer) Nilai Pembagi Frekuensi Lebar Pulsa yang Diinginkan (milidetik) 0 14 1,49 1 22 2,35 2 30 3,20 3 38 4,05 4 46 4,91 5 54 5,76 6 62 6,61 7 70 7,46 8 78 8,32 9 86 9,17 10 94 10,02

2.5. Modul Penentu Arah

Modul ini digunakan menentukan arah berputarnya motor DC apakah searah jarum jam atau berlawanan. Berikut kode VHDL-nya:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Penentu_arah IS PORT( InputPWM : in std_logic; Output1 : out std_logic; Output2 : out std_logic; InputArah : in std_logic); END Penentu_arah;

ARCHITECTURE Behavioral OF Penentu_arah IS BEGIN

PROCESS (InputArah, InputPWM) BEGIN

output1 <= inputPWM; output2 <= '0'; else output1 <= '0'; output2 <= inputpwm; end if; END PROCESS; END Behavioral;

2.6. Modul Detak Reset

Modul ini untuk menghasilkan luaran detak (clock) sebesar ±1 Hz. Luaran detak ini akan dihubungkan dengan masukan pada modul pencacah RPD.

2.7. Modul Pencacah RPD

Modul ini digunakan untuk menghitung banyaknya rotasi perputaran motor tiap detik. Berikut kode VHDL-nya:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY Pencacah_RPD IS PORT( Clock : in std_logic; Reset : in std_logic;

Q : out std_logic_vector (7 downto 0)); END Pencacah_RPD;

ARCHITECTURE Behavioral OF Pencacah_RPD IS SIGNAL qi : std_logic_vector (7 downto 0); BEGIN

PROCESS (clock, reset) BEGIN

if (reset='1') then qi <= "00000000"; else

if (clock'event and clock='1') then qi <= qi + 1;

end if; end if;

if (reset'event and reset='1') then q <= qi;

end if; END PROCESS; END Behavioral;

2.8. Modul Konversi Biner BCD

Modul ini merupakan modul pengkonversian bilangan dalam format biner ke Binary Coded Decimal (BCD) untuk keperluan tampilan 3x7-segmen. Berikut VHDL-nya:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY Konversi_Bin_BCD IS PORT(

Biner: in STD_LOGIC_VECTOR (7 downto 0); BCD: out STD_LOGIC_VECTOR (15 downto 0)); END Konversi_Bin_BCD;

ARCHITECTURE Behavioral OF Konversi_Bin_BCD IS

BEGIN

BCD1 : PROCESS(Biner)

VARIABLE z: STD_LOGIC_VECTOR (17 downto 0); BEGIN for i in 0 to 17 loop z(i) := '0'; end loop; z(10 downto 3) := Biner; for i in 0 to 4 loop if z(11 downto 8) > 4 then z(11 downto 8) := z(11 downto 8)+3; end if; if z(15 downto 12) > 4 then z(15 downto 12) := z(15 downto 12)+3; end if; z(17 downto 1) := z(16 downto 0); end loop; BCD <= z(17 downto 8); END PROCESS BCD1; END Behavioral;

2.9. Modul Pencacah Pemilih

Modul ini digunakan sebagai pemilih dalam menentukan data dan 7-Segmen mana yang digunakan untuk menampilkan data tersebut.

2.10. Modul Multiplekser Tampilan

Modul ini merupakan modul multiplekser atau dapat dikatakan sebagai pemilih dari 3 data yang akan ditampilkan melalui 7-Segmen. Data tersebut berupa sebuah bilangan biner 16 bit dimana 12 bit terendah merepresentasikan 3 data yang dimaksud.

2.11. Modul Multiplekser 7-Segment

Modul ini diperlukan karena karakteristik tampilan 3x7-Segmen yang digunakan merupakan rangkaian multipleks. Walaupun agak rumit mengoperasikannya namun rangkaiannya menjadi lebih sederhana.

2.12. Modul Enkoder 7-Segmen

Modul ini digunakan untuk mengkonversikan kode dalam bentuk BCD ke led-led yang sesuai dalam 7-segmen.

3.RANCANGAN SISTEM ANALOG

3.1. Rangkaian Penggerak Motor DC

Rangkaian ini berfungsi sebagai penggerak (driver) berputarnya motor DC dan pengkondisi sinyal luaran optokopler menjadi gelombang kotak sempurna. Rangkaian ini terdiri dari rangkaian catudaya, penggerak motor DC dan Pemicu Schmitt, sebagaimana ditunjukkan pada Gambar 2.

3.2. Rangkaian Optokopler

Optokopler adalah bagian penting dari sensor kecepatan putar motor DC. Rotary plate yang digunakan yaitu sebuah piringan dengan satu buah lobang dipinggirnya. Optokopler sebagai penghasil pulsa yang nantinya dikirim ke FPGA, sebagaimana ditunjukkan pada Gambar 3.

Gambar 3. Rangkaian optokopler

4.HASIL SINTESIS DAN PEMBAHASAN

Hasil penggunaan sumber daya Logic Element (LE) dan flip-flop per-modul dan sistem lengkap yang diimplementasikan ke dalam FPGA Altera EPF10K10 ditunjukkan pada Tabel 2.

Tabel 2. Rangkuman penggunaan LE dan Flip-flop

No Modul LE/Flip-flop

1 Pembagi Frekuensi 26 / 20

2 Debouncer 4 / 2

3 Pencacah Naik Turun 14 / 4 4 Penghasil PWM 69 / 33 5 Penentu Arah 2 / 0 6 Detak Reset 63 / 33 7 Pencacah RPD 18 / 16 8 Pencacah Pemilih 6 / 6 9 Konversi Biner BCD 33 / 0 10 Multiplekser Tampilan 18 / 0 11 Multiplekser 7-Segment 4 / 0 12 Enkoder 7-Segment 7 / 0 13 Modulgabung 262 / 116 Penggunaan LE dan flip-flop pada perancangan ini cukup banyak. Hal ini disebabkan oleh banyaknya modul yang digunakan dan pembuatan deskripsi VHDL masing-masing modul yang belum teroptimasi, fokus pada fungsinya saja.

5.PENGUJIAN ALAT DAN RANGKAIAN

5.1. Pengujian Luaran PWM

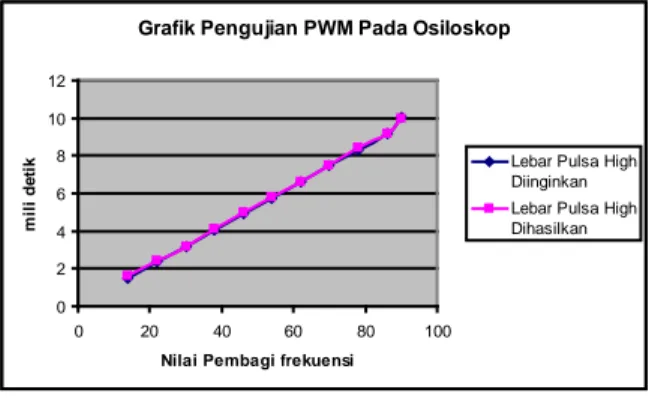

Luaran PWM yang dihasilkan oleh FPGA diuji dengan menggunakan osiloskop. Grafik hasil pengujiannya ditunjukkan pada Gambar 4.

Berdasarkan data grafik yang ditunjukkan pada Gambar 4, besarnya lebar pulsa high PWM yang diinginkan dengan yang dihasilkan saling mendekati. Menggunakan metode regresi linier, persamaan yang diperoleh yaitu 0,99x + 0,08 dengan ralat sebesar 0,04. Ralat dihasilkan akibat tundaan rambatan yang terjadi dalam FPGA.

Grafik Pengujian PWM Pada Osiloskop

0 2 4 6 8 10 12 0 20 40 60 80 100

Nilai Pembagi frekuensi

m

ili d

e

tik Lebar Pulsa High

Diinginkan Lebar Pulsa High Dihasilkan

Gambar 4. Grafik pengujian PWM pada osiloskop

5.2. Pengujian Kecepatan Putar Motor DC

Hasil pengujian RPD pada 7-Segmen (luaran sistem) ditunjukkan pada Gambar 5 dan 6, masing-masing untuk searah dan berlawanan arah jarum .

Grafik Perhitungan dan Pembacaan Kecepatan Putar Motor DC 0 10 20 30 40 50 60 70 0 5 10 15

Lebar Pulsa High PWM (ms)

RP

D

RPD Hasil Perhitungan

RPD Hasil Pembacaan 7-Segment

Gambar 5. Grafik RPD hasil perhitungan dan hasil sistem motor searah jarum jam.

Berdasarkan grafik pada Gambar 5 dan 6, besarnya RPD hasil perhitungan dan tampilan 7-Segmen saling mendekati. Persamaan yang diperoleh pada pengujian RPD searah jarum jam yang ditunjukkan pada Gambar 5, yaitu 1,03x - 0,71 dengan ralat sebesar ±0,70. Sedangkan untuk yang berlawanan jarum jam, sebagaimana ditunjukkan pada Gambar 6, diperoleh persamaan 1,02x + 0,40 dengan ralat sebesar ±0,75. Ralat dihasilkan akibat tundaan rambatan atau

propagation delay yang terjadi pada FPGA.

Terjadinya glitch pada modul-modul pendukung juga cukup berpengaruh terhadap luaran PWM-nya.

Kecepatan putar motor DC searah jarum jam dan berlawanan jarum jam terdapat sedikit perbedaan. Hal ini disebabkan oleh beban yang dipasang pada shaft motor DC yaitu berupa kipas. Kipas ini ketika berputar menghasilkan gaya sentripetal yang berbeda untuk perputaran searah dan berlawanan jarum jam. Sehingga dengan semakin cepat motor berputar maka gaya sentripetal yang dihasilkan makin besar dan gaya sentrifugal-nya mengecil.

Grafik Perhitungan dan Pembacaan Kecepatan Putar Motor DC 0 10 20 30 40 50 60 70 80 0 5 10 15

Lebar Pulsa High PWM (ms)

RP

D

RPD Hasil Perhitungan

RPD Hasil Pembacaan 7-Segment

Gambar 6. Grafik RPD hasil perhitungan dan hasil sistem motor berlawanan arah jarum jam.

5.3. Pengujian masukan PWM dengan Kecepatan putar Motor DC

Pada Gambar 7 dan 8 ditunjukkan grafik perbandingan antara RPD hasil perhitungan dan yang tampil pada 7-segmen untuk beberapa masukan nilai PWM ke motor DC melalui rangkaian penggerak menggunakan IC L293D.

Grafik RPD Hasil Perhitungan dan RPD Pada 7-Segment 0 20 40 60 80 100 0 50 100 150 Duty Cycle (%) RP D RPD Hasil Perhitungan RPD Pada 7-Segment

Gambar 7. Grafik perbandingan RPD hasil perhitungan dan sistem untuk motor dengan gerak searah jarum jam.

Grafik RPD Hasil Perhitungan dan RPD Pada 7-Segment 0 20 40 60 80 100 0 50 100 150 Duty Cycle (%) RP D RPD Hasil Perhitungan RPD Pada 7-Segment

Gambar 8. Grafik perbandingan RPD hasil perhitungan dan sistem untuk motor dengan gerak berlawanan arah jarum

jam.

Berdasarkan grafik pada Gambar 7 dan 8, besarnya nilai RPD hasil perhitungan dan sistem menunjukkan perbedaan yang cukup signifikan. Hal ini disebabkan karena ketidakmampuan IC penggerak motor DC L293D dalam mengolah masukan PWM. Frekuensi

PWM yang diberikan pada IC L293D ini yaitu 10 kHz. Sedangkan frekuensi maksimum dari L293D dalam mengolah aplikasi PWM yaitu 5 kHz [2]. Dengan begitu cepatnya masukan PWM berosilasi, maka ruang tundaan propagasi pada IC L293D menjadi sempit. Hal ini menyebabkan tidak sempurnanya luaran PWM IC L93D yang diumpankan ke motor DC, sehingga motor tidak berputar pada kecepatan yang diinginkan. Oleh karena itu, IC L293D ini dapat bekerja baik untuk aplikasi PWM apabila frekuensi masukannya kurang dari 5 kHz. Sistem pengaturan dan pemantauan kecepatan putar motor DC berbasis FPGA ditunjukkan pada Gambar 9.

Gambar 9. Sistem pengontrolan kecepatan Motor DC berbasis FPGA

6.KESIMPULAN

Hasil pengujian keluaran PWM pada FPGA, dengan menggunakan metode regresi linier, diperoleh persamaan yaitu 0,99x + 0,08 dengan ralat sebesar ±0,04.

Hasil pengujian kecepatan putar motor DC, dengan menggunakan metode regresi linier, persamaan yang diperoleh pada pembacaan RPD searah jarum jam (DS = “OFF”) yaitu 1,03x - 0,71 dengan ralat sebesar ±0,70. Sedangkan untuk yang berlawanan jarum jam (DS = ”ON”) diperoleh persamaan 1,02x + 0,40 dengan ralat sebesar ±0,75.

Jumlah LE dalam FPGA yang digunakan adalah 262 atau 45% dari kapasitas total LE yang dimiki FPGA Altera EPF10K10.

DAFTAR PUSTAKA

[1] Barr, M., 2001, Introduction to Pulse Width

Modulation (PWM), diakses November 20071

[2] SGS Thomson Microelectronics, 1996, L293D

L293DD Push-pull Four Channel Driver with Diodes, SGS Thomson Microelecronics

.

1

M o d u l P e m b a g i F re k u e n s i M o d u l D e b o u n c e r Modul Pencacah Naik Turun

Modul Penghasil PWM Modul Penentu Arah Modul Detak Reset Modul Konversi Biner BCD Modul Pencacah Pemilih Modul Multiplekser Tampilan Modul Enkoder 7-Segment Modul Multiplekser 7-Segment Cepat Lambat ) Detak Kecepatan Rangkaian Pengendali Motor 7- Segment Modul Pencacah RPD Detak (Untuk Seluruh Blok) Crystal FPGA Pushbutton SW1 Pushbutton SW2 Optocoupler

Gambar 1. Diagram blok Rangkaian Pengatur Kecepatan Motor DC berbasis FPGA