KEGIATAN BELAJAR 4:

FLIP-FLOP

a. Tujuan Pemelajaran

1. Mampu mengaplikasikan konsep-konsep sistem digital menjadi rangkaian flip-flop

2. Menjelaskan prinsip kerja macam-macam rangkaian flip-flop

dengan benar

3. Menjelaskan fungsi rangkaian flip-flop

b. Uraian Materi

Flip-flop adalah keluarga Multivibrator yang mempunyai dua keadaaan stabil atau disebut Bistobil Multivibrator. Rangkaian

flip-flop mempunyai sifat sekuensial karena sistem kerjanya diatur dengan jam atau pulsa, yaitu sistem-sistem tersebut bekerja secara sinkron dengan deretan pulsa berperiode T yang disebut jam sistem (System Clock atau disingkat menjadi CK). Seperti yang ditunjukkan dalam gambar 1:

Gambar1: Keluaran dari pembangkit pulsa yang digunakan sebagai deretan pulsa untuk sinkronisasi suatu sistem digital sekuensial Lebor pulsa tp diandaikan kecil terhadap T

Sedangkan fungsi rangkaian flip-flop yang utama adalah sebagai memori (menyimpan informasi) 1 bit atau suatu sel penyimpan 1 bit.

Selain itu flip-flop juga dapat digunakan pada Rangkaian Shift

Register, rangkaian Counter dan lain sebagainya.

Macam - macam Flip-Flop:

1. RS Flip-Flop 2. CRS Flip-Flop 3. D Flip-Flop 4. T Flip-Flop 5. J-K Flip-Flop

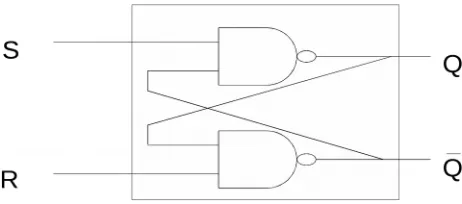

ad 1.RS Flip-Flop

RS Flip-Flop yaitu rangkaian Flip-Flop yang mempunyai 2

jalan keluar Q dan Q (atasnya digaris). Simbol-simbol yang ada pada jalan keluar selalu berlawanan satu dengan yang lain. RS-FF adalah flip-flop dasar yang memiliki dua masukan yaitu R (Reset) dan S (Set). Bila S diberi logika 1 dan R diberi logika 0, maka output Q akan berada pada logika 0 dan Q not pada logika 1. Bila R diberi logika 1 dan S diberi logika 0 maka keadaan output akan berubah menjadi Q berada pada logik 1 dan Q not

pada logika 0.

Gambar 2. RS-FF yang disusun dari gerbang NAND

Tabel Kebenaran:

S B Q Q Keterangan 0 0 1 1 Terlarang

0 1 1 0 Set (memasang) 1 1 1 0 Stabil I

1 0 0 1 Reset (melepas) 1 1 0 1 Stabil II

0 0 1 1 Terlarang

1 1 Q

n Q

n

Kondisi memori

(mengingat)

Yang dimaksud kondisi terlarang yaitu keadaaan yang tidak diperbolehkan kondisi output Q sama dengan Q not

yaitu pada saat S=0 dan R=0.

Yang dimaksud dengan kondisi memori yaitu saat S=1 dan R=1, output Q dan Qnot akan menghasilkan perbedaan yaitu jika Q=0 maka Qnot=1 atau sebaliknya jika Q=1 maka Q not =0.

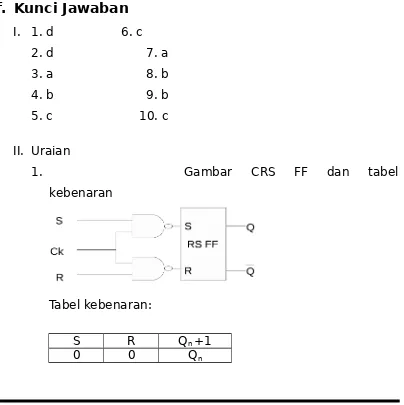

ad 2.CRS Flip-Flop

Tabel kebenarannya:

0 0 Qn

0 1 0

1 0 1

1 1 terlarang

Keterangan:

Qn = Sebelum CK

Qn +1 = Sesudah CK

CRS Flip-flop adalah clocked RS-FF yang dilengkapi dengan sebuah terminal pulsa clock. Pulsa clock ini berfungsi mengatur keadaan Set dan Reset. Bila pulsa clock berlogik 0, maka perubahan logik pada input R dan S tidak akan mengakibatkan perubahan pada output Q dan Qnot. Akan tetapi apabila pulsa clock berlogik 1, maka perubahan pada input R dan S dapat mengakibatkan perubahan pada output Q dan Q not.

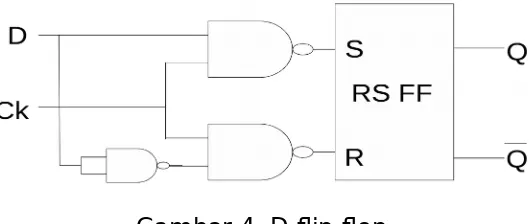

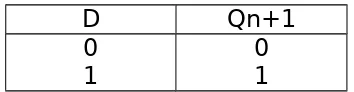

ad 3.D Flip-Flop

D flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer pada reset inputnya. Sifat dari D flip-flop adalah bila input D (Data) dan pulsa clock berlogik 1, maka output Q akan berlogik 1 dan bilamana input D berlogik 0, maka D flip-flop akan berada pada keadaan reset atau output Q berlogik 0.

D Qn+1 0

1 01

ad 4.T Flip-Flop

Gambar 5. T flip-flop

Tabel Kebenaran:

T Q

0 0

1 0

0 1

1 1

0 0

1 0

0 1

1 1

ad 5.J-K Flip-Flop

JK flip-flop sering disebut dengan JK FF induk hamba atau Master Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF dan Slave FF. Master Slave JK FF ini memiliki 3 buah terminal input yaitu J, K dan Clock. Sedangkan IC yang dipakai untuk menyusun JK FF adalah tipe 7473 yang mempunyai 2 buah JK flip-flop dimana lay outnya dapat dilihat pada Vodemaccum IC (Data bookc IC). Kelebihan JK FF terhadap FF sebelumnya yaitu JK FF tidak mempunyai kondisi terlarang artinya berapapun input yang diberikan asal ada clock maka akan terjadi perubahan pada output.

Gambar 6. JK FF

Tabel Kebenaran:

J K Qn+1 Keterangan

0 0 Qn Mengingat

0 1 0 Reset

1 0 1 Set

1 1 Qn (strep) Togle

c. Rangkuman

tidak dapat) memiliki masukan langsung untuk operasi asinkron/tak sinkron, masukan J dan K Data dan Clear. Masukan langsung hanya dapat berharga 0 diantara pulsa jam (Clock) ketika CK=0. Bilamana CK=1 kedua masukan asinkron harus dalam keadaan tinggi dan harus tetap bertahan pada keadaanya selama jangka waktu pulsa, CK=1. Untuk flip-flop majikan budak (Master Slave), keluaran Q tetap sama selama jangka waktu pulsa dan hanya berubah setelah CK berubah dari 1 ke 0, pada tepi pulsa kearah negatif flip-flop togle atau komplementer tidak terdapat secara komersial karena JK FF dapat juga digunakan sebagai T FF dengan menghubungkan langsung masukan J dan K seperti gambar dibawah.

d. TUGAS

1.

Berikan definisi dari suatu flip-flop!2.

Tuliskan 2 fungsi dari flip-flop !3.

Sebutkan jenis-jenis flip-flop yang pengaturnya menggunakan jam (clock)!4.

Gambarkan sebuah flip-flop RS yang tidak menggunakan dan disusun dari pintu/gerbang NAND!5.

Apa arti dari Men-Set flip-flop?e. Test Formatif

I Berilah tanda silang pada jawaban yang paling benar! 1. Flip-flop termasuk golongan/keluarga:

a. Univibrator

2. Yang bukan merupakan jenis flip-flop yang diatur dengan clock adalah:

a. JK FF

b. D FF

c. CRS FF

d. RS FF

3. Daerah terlarang untuk RS FF yang disusun dari pintu NAND yaitu:

a. S=0 , R=0 c. S=0 , R=0

b. S=1 , R=0 d. S=1 , R=1

4. Daerah stabil untuk RS FF yang dibangun dari pintu NAND yaitu:

a. S=0 , R=0 c. S=1 , R=0

b. S=1 , R=1 d. S=0 , R=1

5. Yang disebut dengan Me-Reset sebuah FF yaitu dengan membuat keluaran:

a. Q=1 , Qnot=0 c. Q=0 , Qnot=1 b. Q=1 , Qnot=1 d. Q=0 , Qnot=0

6. Jenis flip-flop yang tidak mempunyai kondisi terlarang adalah:

a. RS FF dari NAND c. JK FF

b. CRS FF d. RS FF dari NOR

7. Daerah terlarang untuk CRS flip-flop adalah:

a. R=1 , S=1 c. R=0 , S=1

b. R=0 , S=0 d. R=1 , S=0

8. Pernyataan berikut merupakan fungsi dari flip-flop, kecuali:

a. Memory

d. Rangkaian hitung

9. Jenis IC yang melaksanakan fungsi NAND adalah:

a. 7402 c. 7473

b. 7400 d. 7474

10. Jenis IC yang melaksanakan fungsi JK FF adalah:

a. 7402 c. 7473

b. 7400 d. 7474

II Jawablah pertanyaan berikut dengan tepat, jelas dan benar!

1. Gambarkan dan buatlah tabel kebenaran dari CRS Flip-flop!

2. Gambarkan dan buatlah tabel kebenaran dari JK Flip-flop!

f. Kunci Jawaban

I. 1. d 6. c

2. d 7. a

3. a 8. b

4. b 9. b

5. c 10. c

II. Uraian

1. Gambar CRS FF dan tabel

kebenaran

Tabel kebenaran:

S R Qn +1

0 1 0

1 0 1

1 1 terlarang

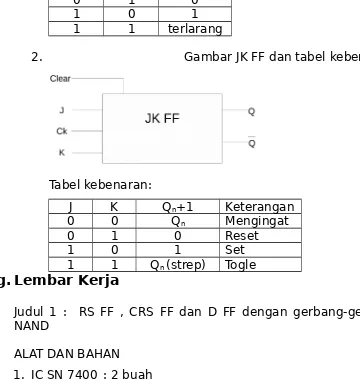

2. Gambar JK FF dan tabel kebenaran

Tabel kebenaran:

J K Qn+1 Keterangan

0 0 Qn Mengingat

0 1 0 Reset

1 0 1 Set

1 1 Qn (strep) Togle

g. Lembar Kerja

Judul 1 : RS FF , CRS FF dan D FF dengan gerbang-gerbang NAND

ALAT DAN BAHAN 1. IC SN 7400 : 2 buah

2. LED : 2 buah

3. R : 220 Ω : 2 buah 4. Multimeter

5. Catu daya 5 Volt 6. Breadboard

7. Kabel penghubung secukupnya

R-S Flip-flop

C-RS Flip-Flop

D Flip Flop

IC SN 7400

LANGKAH KERJA MERAKIT RS FF

2. Masukkanlah tegangan +5V pada kaki 14 dan ground pada kaki 7.

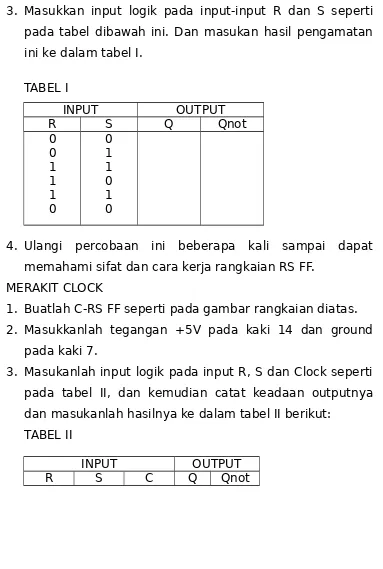

3. Masukkan input logik pada input-input R dan S seperti pada tabel dibawah ini. Dan masukan hasil pengamatan ini ke dalam tabel I.

TABEL I

INPUT OUTPUT

R S Q Qnot

0 0 1 1 1 0

0 1 1 0 1 0

4. Ulangi percobaan ini beberapa kali sampai dapat memahami sifat dan cara kerja rangkaian RS FF.

MERAKIT CLOCK

1. Buatlah C-RS FF seperti pada gambar rangkaian diatas. 2. Masukkanlah tegangan +5V pada kaki 14 dan ground

pada kaki 7.

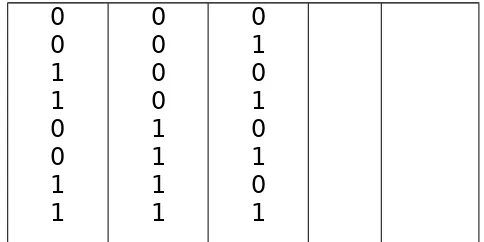

3. Masukanlah input logik pada input R, S dan Clock seperti pada tabel II, dan kemudian catat keadaan outputnya dan masukanlah hasilnya ke dalam tabel II berikut:

TABEL II

INPUT OUTPUT

0 memahami sifat dan cara kerja C-RS FF dengan gerbang NAND.

MERAKIT D FF

KESIMPULAN

Apakah kesimpulan dari percobaan ini? Judul 2 : JK Flip-Flop dan T Flip-Flop

ALAT DAN BAHAN 1. IC SN 7473

2. R : 220 Ω : 2 buah

3. LED : 2 buah

4. Catu Daya 5 Volt 5. Bread Board

6. Kabel Penghubung secukupnya

GAMBAR RANGKAIAN

J-K FF induk Hamba

T FF Induk hamba

LANGKAH KERJA

2. Masukan tegangan +5 V pada kaki 4 dan ground pada kaki 11.

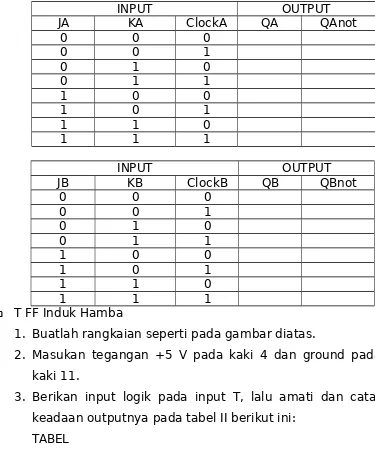

3. Berikan keadaan logik pada input J, K dan Clock. Lalu amatilah keadaan outputnya dan catat hasilnya pada tabel I.

4. Ulangi percobaan ini beberapa kali sampai dapat memahami sifat dan cara kerja rangkaian JK FF induk hamba.

INPUT OUTPUT

JA KA ClockA QA QAnot

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

INPUT OUTPUT

JB KB ClockB QB QBnot

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

T FF Induk Hamba

1. Buatlah rangkaian seperti pada gambar diatas.

2. Masukan tegangan +5 V pada kaki 4 dan ground pada kaki 11.

3. Berikan input logik pada input T, lalu amati dan catat keadaan outputnya pada tabel II berikut ini:

INPUT OUTPUT

T (Togle) Q Qnot

0 1 0 1 0 1 0 1

KESIMPULAN

Kesimpulan apakah yang diperoleh dari percobaan JK FF dan T FF ini?

KEGIATAN BELAJAR 5: REGISTER

a. Tujuan Pemelajaran

1. Dapat menganalisa dan menggunakan flip-flop dalam rangkaian Register

4. Menggambarkan macam-macam Register

5. Menjelaskan prinsip kerja macam-macam register

b. Uraian Materi

Register adalah sekelompok flip-flop yang dapat dipakai untuk menyimpan dan untuk mengolah informasi dalam bentuk linier. Ada 2 jenis utama Register yaitu:

1. Storage Register (register penyimpan) 2. Shift Register (register geser)

Register penyimpan (Storage Register) digunakan apabila kita hendak menyimpan informasi untuk sementara, sebelum informasi itu dibawa ke tempat lain. Banyaknya kata/bit yang dapat disimpan, tergantung dari banyaknya flip-flop dalam

register.

Satu flip-flop dapat menyimpan satu bit. Bila kita hendak menyimpan informasi 4 bit maka kita butuhkan 4 flip-flop.

Contoh: Register yang mengingat bilangan duaan (biner): 1101 terbaca pada keluaran Q.

Shift Register adalah suatu register dimana informasi dapat bergeser (digeserkan). Dalam register geser flip-flop saling dikoneksi, sehingga isinya dapat digeserkan dari satu flip-flop ke flip-flop yang lain, kekiri atau kekanan atas perintah denyut lonceng (Clock).

Ada 4 Shift Register yaitu:

1. SISO (Serial Input Serial Output)

Gambar Register SISO yang menggunakan JK FF

Q3 register akan digrser ke kanan selama tebing dari denyut lonceng (Clock).

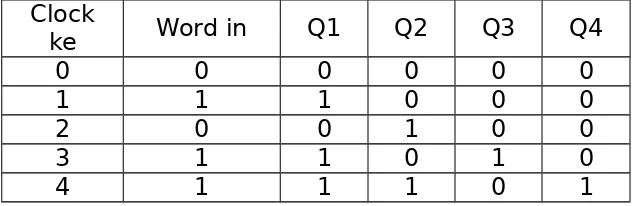

Tabel Kebenaran (Misal masuknya 1101)

Clock

Register geser SISO ada dua macam yaitu:

a) Shift Right Register (SRR)/Register geser kanan

b) Shift Left Register (SLR)/Register geser kiri

Rangkaian Shift control adalah sebagi berikut: rangkaian selengkapnya adalah sebagai berikut:

SLR

Jika SC=0,maka input geser kanan akan aktif. Keluaran NAND diumpamakan ke input DFF1 dan setelah denyut lonceng berlaku (saat tebing depan), maka informasi diteruskan ke output Q1. Dan output Q1 terhubung langsung keoutput DFF2 berikutnya sehingga dengan proses ini terjadi pergeseran ke kanan.

Clock ke Input Q1 Q2 Q3 Q4

0 0 0 0 0 0

1 1 1 0 0 0

2 1 1 1 0 0

3 0 0 1 1 0

4 1 1 0 1 1

Informasi digit digeser kekanan setiap ada perubahan pulsa clock tebing atas. Geser kanan berfungsi sebagai operasi aritmatika yaitu pembagi dua untuk tiap-tiap flip-flop.

Jika SC = 1 , maka akan mengaktifkan input geser kiri. Output NAND masuk ke input D-FF4 dan setelah diberi pulsa clock informasi dikeluarkan melalui Q4 dan keluaran Q4 dihubungkan ke input FF3, keluaran D-FF3 dimasukan ke D-FF berikutnya, sehingga dengan demikian terjadi pergeseran informasi bit ke arah kiri. TABEL KEBENARAN (jika input 1101)

Clock ke Input Q1 Q2 Q3 Q4

0 0 0 0 0 0

1 1 0 0 0 1

2 1 0 0 1 1

3 0 0 1 1 0

4 1 1 1 0 1

Register geser kiri berfungsi sebagai operasi aritmatika yaitu sebagai pengali dua untuk tiap-tiap flip-flop.

2. Register Geser SIPO

Gambar rangkaiannya adalah sebagai berikut: (SIPO

Masukan-masukan data secara deret akan dikeluarkan oleh D-FF setelah masukan denyut lonceng dari 0 ke 1. Keluaran data/informasi serial akan dapat dibaca secara paralel setelah diberikan satu komando (Read Out). Bila dijalan masuk Read Out diberi logik 0, maka semua keluaran AND adalah 0 dan bila Read Out diberi logik 1, maka pintu-pintu AND menghubung langsungkan sinyal-sinyal yang ada di Q masing-masing flip-flop.

1

3. Register Geser PIPO

Adalah register geser dengan masukan data secara jajar/paralel dan keluaran jajar/paralel.

Gambara rangkaiannya adalah sebagai berikut: (PIPO

Sebelum dimasuki data rangkaian direset dulu agar keluaran Q semuanya 0. Setelah itu data dimasukkan secara paralel pada input D-FF dan data akan diloloskan keluar secara paralel setelah flip-flop mendapat pulsa clock dari 0 ke 1. Contoh:

4. Register geser PISO

Adalah register geser dengan masukan data secara paralel dan dikeluarkan secara deret/serial.

Serial

Rangkaian diatas merupakan register geser dengan panjang kata 4 bit. Semua jalan masuk clock dihubungkan jajar. Data-data yang ada di A, B, C, D dimasukkan ke flip-flop secara serempak, apabila dijalan masuk Data Load diberi logik 1.

Cara Kerja:

Mula-mula jalan masuk Data Load = 0, maka semua pintu

register dengan cara memasukkan denyut lonceng, denyut-demi denyut keluar deret/seri. Untuk keperluan ini jalan masuk D dihubungkan kepada keluaran Q.

Ada juga register yang dapat digunakan sebagai Shift register SISO maupun PIPO dengan bantuan suatu control sbb:

Reset

Input Control (IC)

Preset

Data jajar

Input Control = 0, berfungsi sebagai register geser SISO Input Control = 1, berfungsi sebagai register geser PIPO

Data IC Preset Reset

0 1 1 0

1 1 0 1

0 0 1 1

1 0 1 1

Rangkaian kontrol diatas dapat disimbolkan sbb:

Input Control 5

2

Preset

3

Reset 4

Data Paralel 1

D1

Jika IC=0, maka input yang dimasukan ke D0, D1, D2, D3 tidak mempengaruhi keadaan output QA, QB, QC, QD tetapi yang mempengaruhinya adalah data yang dimasukkan ke input D-FF secara serial, maka pada kondisi ini rangkaian akan bekerja senagai register geser SISO.

Jika IC=1, maka input yang dimasukkan ke gate D seri tidak akan mempengaruhi output, tetapi output dipengaruhi oleh data paralel (D0, D1, D2, D3). Input dimasukkan secara serempak dan keluaran ditunjukkan secara serempak begitu pulsa clock berguling dari 1 ke 0, maka pada kondisi ini rangkaian akan bekerja sebagai registeer geser PIPO.

c. Rangkuman

dihubungkan dengan masukan dari flip-flop berikutnya. Konfigurasi seperti ini yang disebut dengan register geser. Masing-masing flip-flop banyak menggunakan JK-FF dan D-FF. Perhatikan pada uraian materi diatas bahwa tahapan yang harus menyimpan bit paling berarti adalah MSB (Most Significant Bit). Bit paling tidak berarti adalah LSB (List

Significant Bit) yang berada pada bit disebelah paling kanan.

Macam-macam register yang digunakan adalah berdasarkan fungsinya yaitu meliputi:

1. Register SISO yaitu merupakan register yang masukan

datanya seri dan keluar secara seri. Penerapan Register ini yaitu untuk Register geser kanan, geser kiri. Beberapa jenis register yang banyak dipasaran dilengkapi dengan gerbang-gerbang yang memungkinkan pemindahan data dari kanan ke kiri atau sebaliknya. Suatu penerapan untuk operasi-operasi ini adalah dalam perkalian dan pembagian oleh angka kelipatan 2

2. Register SIPO yaitu merupakan register yang masukan

datanya secara seri dan keluar secara paralel. Flip-flop yang telah dijelaskan diatas dapat dikosongkan isinya dengan memberi bit 0 pada Clear sehingga semua keluaran Q1, Q2, Q3 dan Q4 = 0, setelah clear diberi logik 1, clock diberikan, data dimasukan misalnya 1101 maka data yang tak berarti akan tersimpan pada FF4 = 1, berturut-turut menuju ke kiri (data yang paling berarti) FF3 akan tersimpan logik 0, FF2 = logik 1 dan FF1=logik 1

3. Register PISO yaitu merupakan register yang masukan

datanya secara paralel dan keluarannya secara seri.

1101 maka data yang tersimpan itu selanjutnya dapat dibaca secara serial pada FF yang paling kanan dengan menggunakan 4 pulsa clock. Sistem ini merupakan suatu konverter paralel ke serial.

4. Register PIPO yaitu data dimasukkan seperti dijelaskan diatas secara paralel dan kemudian akan digeserkan secara paralel pada keluarannya. Dan masing-masing flip-flop hanya digunakan sebagai suatu memori.

Salah satu penerapan yang penting dari register adalah penggunaanya sebagai pembangkit barisan biner. Sistem ini juga disebut pembangkit kata, kode atau huruf.

Suatu register geser juga dapat dipakai untuk menimbulkan penundaan waktu ∆ dalam suatu sistem. Jadi suatu deretan pulsa masuk akan muncul pada keluaran suatu register n tahapan dengan penundaan waktu selama ∆=(n-1)T

Disamping itu register geser juga dapat digunakan sebagai Ring Counter (pencacah sim vol). Jadi suatu pencacah sim vol mempunyai fungsi serupa dengan sebuah saklar Steping

(Stepping Switch), karena setiap pulsa penggeser memajukan

saklar itu sejauh satu langkah.

d. Tugas

1. Apa yang dimaksud

dengan register?

2. Ada berapa jenis

register, sebutkan!

3. Gambarkan rangkaian

4. Gambarkan rangkaian register geser SRR dan SLR menggunakan Shift Control!

5. Kenapa dalam register

SIPO dalam membaca keluaran paralel, input Read Out diberi logik 1?

e. Tes Formatif

1. Sebutkan 5 fungsi dari

Register?

2. Apakah fungsi Clear pada

Register?

3. Lengkapilah tabel kebenaran

berikut ini jika Shift Register tersebut mempunyai output 8 bit secara SIPO, dimana Q8 merupakan LSB!

Clock Data input Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

0 0 0 0 0 0 0 0 0 0

1 1

2 1

3 1

4 1

5 1

6 1

7 1

8 1

4. Gambarkan SIPO Shift Register

tersebut diatas secara blok diagram?

f. Kunci Jawaban

1. Lima fungsi dari Register yaitu

b. Penggeser data dari input seri ke output paralel c. Penggeser data kekanan (SRR) dan kekiri (SLR) d. Pembangkit barisan biner (sequence generator) e. Saluran penunda digital

2. Fungsi clear pada register

untuk membersihkan data yang ada pada flip-flop (membersihkan memory) supaya sebelum data dimasukan output flip-flop semua dalam kondisi 0.

3. Tabel Kebenaran

Clock Data input Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

0 0 0 0 0 0 0 0 0 0

1 1 1 0 0 0 0 0 0 0

2 1 1 1 0 0 0 0 0 0

3 1 1 1 1 0 0 0 0 0

4 1 1 1 1 1 0 0 0 0

5 1 1 1 1 1 1 0 0 0

6 1 1 1 1 1 1 1 0 0

7 1 1 1 1 1 1 1 1 0

8 1 1 1 1 1 1 1 1 1

4. Blok diagram SIPO untuk tabel

diatas

Q5 Q3 Q1

LSB

Clear

Q6 Serial Input

MSB

Q4

Q7 Q2

Q8 Clk

g. Lembar Kerja

Judul : RegisterBAHAN KERJA

1. IC SN 7473 (dual JK FF with clear) 2 buah 2. IC SN 7400 (quadraple Z inputs NAND gate) 1 buah 3. IC SN 7474 (dual DFF with Preset dan Clear) 2 buah

4. IC SN 7495 (4 bit SRR or SLR) 1 buah

5. IC SN 74164 (8 bit SIPO Shift Register) 1 buah

6. Indikator (LED) 8 buah

7. Rangkaian Clock ALAT KERJA

1. Papan percobaan 2. Kabel penghubung 3. Catu daya + 5 volt DC 4. Multimeter

KESELAMATAN KERJA

1. Selalu berhati-hati dalam membuat rangkaian.

2. Meneliti terlebih dahulu sebelum melakukan percobaan. 3. Menggunakan catu daya yang sesuai untuk setiap

percobaan.

4. Menanyakan kepada instruktur bila mengalami kesulitan. PETUNJUK UMUM

1. Menyiapkan alat dan bahan yang diperlukan.

2. Membuat rangkaian seperti pada gambar percobaan.

3. Bila dalam merangkai telah baik dan benar, laporkan kepada instruktur.

6. Memperhatikan dan mencatat hasilnya (outputnya). 7. Melakukan percobaan sampai 2 atau 3 kali.

8. Bila telah selesai melakukan percobaan mematikan catu daya.

9. Mengembalikan alat dan bahan ke tempat semula.

10. Membersihk

an ruangan tempat percobaan. LANGKAH KERJA

1. Percobaan I (SRR menggunakan JK FF). Rangkaian gambar berikut: pulsa clock diberikan, FF direset terlebih dahulu dengan cara memberikan logik 0 ke pin Clear. Masukkan data dengan memberikan pulsa clock sesuai tabel berikut:

Word in Clock QA QB QC QD

Clear

Bit-bit dimasukkan ke input D FF-I. Sebelum pulsa clock diberikan, FF direset terlebih dahulu. Berikan data input dan catat outputnya dalam tabel berikut:

Input Clock QA QBOutputQC QD 0

1 1 0 1

3. Percobaan III (Register PIPO menggunakan D FF) Buat rangkaian berikut: pulsa clock dimasukkan, resetlah terlebih dahulu. Masukkan data dan catat outputnya dalam tabel berikut:

Clock

PARALEL IN PARALEL OUT

0 0 0 1

0 1 0 1

1 1 0 1

1 0 0 1

4. Percobaan IV (SRR menggunakan IC SN 7495) Buatlah rangkaian berikut: catat outputnya dalam tabel berikut:

Serial

Input D Clock 2 QA QB QC QD 1

1 0 1

6. Percobaan VI (SRR menggunakan IC SN 74164) Buatlah rangkaian berikut: dimasukkan melalui pin 8 dan reset melalui pin 9. Sebelum data dimasukkan resetlah terlebih dahulu. Masukkan data dan catat outputnya dalam tabel berikut:

Inpu