8 SERVO DC

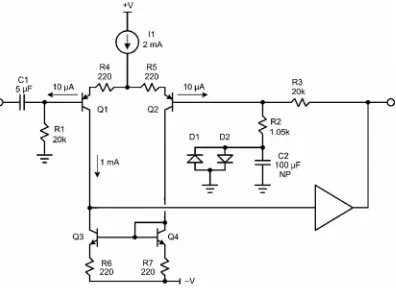

Sevo DC adalah kalang umpan balik global yang bertingkah pada dc untuk mengendalikan offset keluaran penguat. Pada bagian ini akan diuraikan pengertian magnitudo offset dc dalam rancangan konvensional. Beberapa pendekatan untuk mengurangi offset dalam rancangan konvensional juga dibahas dan beberapa diantaranya cocok untuk merancangan servo dc. Gambar 8.1 memperluhatkan penguat dengan arasemen pencegah dc biasa. Tahap VAS dan keluaran diperlihatkan sebagai simbol penguat. Kapasitor kopling C1 mencegah dc dari sumber. Resistor kembali masukan (input return) R1 memanjar titik masukan LTP pada sekitar 0 V. dengan resistor masukan kembali 20 k, kapasitor kopling 5 F diperlukan untuk mendorong

frekuensi cut-off masukan dibawah 2 Hz. Kapasitor ini harus memiliki kualitas sangat tinggi. Jaringan umpanbalik memasukkan resistor R3 20 k dan resistor paralel umpanbalik R2 1.05

k. Resistor ini mengatur bati loop-tertutup pada 20. Jaringan juga memasukkan kapasitor

elektrolitik C2 dalam lengan paralel yang memungkinkan bati dc penguat jatuh menjadi satu pada dc. Ini mencegah offset tegangan masukan dari penggandaan oleh bati loop-tertutup penguat.

Kapasitor elektrolitik memperkenalkan roll-off frekuensi rendah kedua dengan konstanta waktu kira-kira sama dengan R2 * C2. Harga C2 harus 100 F untuk mendorong frekuensi roll-off

kedua ini dibawah 2 Hz. Inilah mengapa kapasitor biasanya bertipe elektrolitik, terutama tak-berpolaritas. Dioda back-to-back menyilang elektrolitik mencegahnya dari kecenderungan menjadi tegangan berlebih dalam peristiwa yang keluaran penguat menjadi lengket ke satu rel atau jika tidak menggerakkan tegangan besar dengan perioda waktu. Sinusioda 100 W pada 2 Hz akan mencoba menenpati 1.4 Vp menyebrang C2. Di bawah kondisi ini dioda akan menjadi dipanjar maju dan menyebabkan distorsi. Kadang-kadang dioda menghilangkan kejadian ini. Dalam keadaan lain dua diode dipasang seri atau dua dioda zener digunakan.

Gambar 8.1 Penguat konvensional dengan penahan dc

An alternative to the electrolytic capacitor is a large fll capacitor in colbination with higher circuit ilpedances in the feedback network. If R2 is set to 5 kand R3 is set to 95 k, then a 22-F fll capacitor will yield a low-freuuency corner below 2 z.. hhis is a costly and bulky solution. hhe high ilpedance in the feedback network invites noise and DC ofset ilpairlents.

We will see that the single biggest reason for elploying a DC servo is the elilination of the electrolytic capacitor. hhe DC servo is a slaller and less expensive solution that provides luch higher sound uuality and perforlance.

8.1 Awal dan Konsekuensi Offset DC

Tegangan offset masukan LTP dapat kurang dari 1 mV untuk BJT monolitic ganda (dual monolithic BJT) atau dapat lebih dari 20 mV untuk BJT diskrit tak-sesuai. Perwujudan LTP JFET dengan JFET monolitik ganda akan menghasilkan tegangan offset masukan kurang dari 10 mV tanpa kesulitan. Selama tegangan offset masukan tida dilipat gandakan oleh bati loop tertutup yang lebih dari satu, offset keluaran penguat dapat diterima. Offset DC penguat lebih dari 50 mV harus di hindarkan.

Arus Panjar Masukan.

Tegangan offset masukan pasangan diferensial tidak hanya sumber dari offset DC dalam penguat. Masalah lebih serius dengan offset dc terjadi dalam penguat dengan tahap masukan BJT sebagai hasil arus basis. Hal penting, tahap masukan JFET tidak mengalami masalah ini. Transistor LTP pnp dalam Gambar 8.1 masing-masing dipanjar pada 1 mA. Jika beta transistor 100, arus basis menjadi 10 A. arus basis pada sisi masukan LTP mengalir melewati resistor

kembali masukan R1, menghasilkan tegangan positif kecil pada basis Q1. Jika arus basis 10

A, basis Q1 menjadi +0,2 V.

Anggap bahwa beta transistor LTP sama, jadi bahwa 10 juga mengalir dari Q2 melalui

diharapkan (anggap tidak ada tegangan offset dalam LTP). Offset DC berkaitan dengan arus basis akan sangat dicegah jika beta transistor dalam LTP bersesuaian. Jika beta transistor LTP tidak sesuai 10 %, maka total offset 20 mV akan terjadi. Sekali lagi, ini dapat diterima jika ia dikalikan dengan satu pada keluaran penguat. Banyak penguat dirancang dengan pendekatan ini.

Jika rancangan penguat memiliki R1 dan R3 dengan perbedaan harga mencolok, offset dari arus panjar masukan dapat menjadi serius. Ini dapat terjadi jika perancang berharap memiliki impedansi masukan lebih besar dari 20 k (yang juga akan memungkinkan C1 lebih kecil)

tanpa mempertimbangan desah karena meningkatnya impedansi jaringan umpanbalik. Secara sederhana, hal ini dilukiskan dalm Gambar 8.2. Di sini lintasan maju penguat diringkas oleh simbol penguat dengan pengertian bahwa tahap masukan adalah LTP pnp yang mencatu sekitar 10 A dari masing-masing terminal masukan. Dioda-dioda juga dihilangkan untuk

memperjelas. Sebuah resistor kembali masuk 50 k dengan resistor umpanbalik 20 k akan

menghasilkan total offset sekitar 300 mV. Ini jelas tak dapat diterima.

Gambar 8.2 Susunan panjar dc penguat tradisional dengan impedansi lebih tinggi dan offset dc lebih buruk.

Persoalan yang seperti diatas diperoleh jika jaringan umpanbalik impedansi rendah terhubung dc dipekerjakan, seperti dalam keadaan servo dc digunakan. Dalam hal ini, jika R1 diatur pada 50 k dan kapasitor elektrolitik dilepas, suatu offset masukan +500 mV akan dihasilkan pada

basis Q1. Offset besar ini akan dilawat dan digagalkan oleh servo dc.

Dalam penguat dengan kopling ac pada masukan, impedansi masukan terhadap tanah adalah sederhana yaitu resistor kembali R1. Resistor ini mengatur impedansi masukan penguat dan juga mengatur ukuran kapasitor kopling yang diperlukan untuk mencapai cutoff frekuensi rendah yang diberikan. Untuk alasan-alasan ini, diperlukan harga resistor dengan harga besar, mungkin sekitar 50 k.

Tetapi, untuk alasan desah dan distorsi, resistor umpanbalik R3 harus merupakan resistansi rendah. Mengingat impedansi ac pengumpan LTP pada sisi masukan cukup rendah karena kapasitor kopling bertingkah seperti hubung singkat pada frekuensi audio. Idealnya, impedansi ac pada sisi jaringan umpanbalik juga harus rendah untuk meminimalkan desah. Maka ada pertentangan antara kebutuhan ac dan dc pada tahap masukan. Juga dapat dicatat bahwa ketika impedansi jaringan umpanbalik dikurangi, harga kapasitor elektrolitik pada lintasan paralel umpanbalik harus ditingkatkan secara sesuai.

Resistor Penyama Pemintas (Bypassed)

Beberpa perancang telah mencari untuk mengurangi pertentangan impedansi dengan menggunakan susunan sedikit berbeda pada sisi umpanbalik, seperti ditunjukkan dalam Gambar 8.3a. R4 ditambahkan secara seri dengan masukan LTP dan bypass. Jumlah R3 dan R4 dibuat sama dengan R1, pengembalian keseimbangan dc pada susunan. Disini jaringan umpanbalik dapat secara acak impedansi rendah, tujuan untuk hamburan daya pada jaringan umpanbalik dan untuk ukuran C2 yang diperlukan. Kapasitor bypass C3 mempunyai arus sinyal sangat kecil mengalir didalamnya karena impedansi tinggi yang terlihat kedalam LTP, juga kapasitor ini tidak perlu sebesar harga kapasitor kopling yng digunakan pada sisi masukan.

Gambar 8.3 (a) Penguat dengan resistor penyama dibypass (b) Penguat dengan jaringan umpanbalik terhubung DC.

Gambar 8.3b menunjukkan susunan mirip di mana jaringan umpanbalik adalah terhubung dc dan C2 dieliminasi. Di sini R4 adalah resistor yang hampir sama dengan harga resistor kembali R1. Gabungan R4 dan resistansi jaringan umpanbalik memungkinkan jumlah sama pada tegangan positif offset pada R1, pambatalan offset penguat dengan cara yang sama seperti susunan Gambar 8.3a.

Susunan ini mengurangi bebarapa offset masukan tanpa kapasitor elektrolitik. Bagaimanapun, bati dc penguat sekarangsama dengan bati loop-tertutup, jadi satu bagian besar dari keunggulan pemakaian elektrolitik dalam susunan tradisional dihilangkan ( berkaitan dengan offset tegangan masukan). Pendekatan ini dapat digunakan dalam gabungan dengan servo DC untuk mengurangi jumlah koreksi yang dicatu oloeh servo DC.

Tahap Masukan Komplementer

Banyak penguat dengan tahap masukan BJT mempekerjakan arsitektur tahap masukan diferensial komplementer populer seperti Gambar 8.4. pendekatan ini mengurangi masalah arus panjar masukan karena arus basis mengalir dalam pasangan transistor pnp berlawanan tanda dengan pasangan npn, menghasilkan beberapa pembatalan. Ini mengurangi masalah offset secara luas bahwa beta pasangan masukan npn dan pnp bersesuaian. Bagaimanapun, perbedaan beta 2:1, mengurangi keunggulan yang diperoleh dari susunan ini dengan faktor hanya 2 dibanding dengan tahap masukan unipolar.

Gambar 8.4 Pasangan diferensial masukan komplementer

digunakan. Bagaimanapun, penyesuaian membuat biaya ekstra. Jika jaringan arus panjar masukan adalah 1 A dalam Gambar 8.4, maka offset keluaran akan dapat ditoleransi 30 mV.

Trim Pot DC

Menghormati dari apa pendekatan yang diuraikan diatas digunakan, banyak penguat diakhiri penggunakan potensimeter trimmer DC untuk memperoleh offset keluaran rendah. Ini menambah ongkos, dan efektivitasnya kadang terpengaruh suhu sebagai akibat beta transistor bergantung suhu. Arus koreksi dapat diinjeksi pada salah satu sisi dari masukan melalui resistor berharga besar.

Tahap masukan JFET

Walau tahap masukan JFET tipikalnya dimulai dengan offset tegangan masukan lebih tinggi dari tahap BJT (dengan anggapan masing-masing pasangan serasi ganda), namun arus bias masukan yang kecil membuat JFET jauh lebih unggul dalam hal offset DC sebara keseluruhan. Perancang dapat bebas berusaha menyeimbangkan resistansi DC pada masukan dan umpan balik dari tahap masukan.

8.2 Landasan Servo DC

Gambar 8.5 Suatu penguat daya dengan dengan servo dc sederhana menggunakan integrator pembalik.

Keluaran penguat diterapkan ke integrator pembalik tradisional diikuti oleh pembalik bati-satu untuk menyediakan polaritas umpanbalik. Resistor masukan integrator R5 dipilih 1 M, selama

kapasitor integrator C2 diatur 1 F. integrator biasanya diwujudkan dengan op amp JFET untuk

menghindarkan offset integrator yang dibuat oleh arus panjar masukan. Masukan integrator dilindungi dari tegangan masukan lebih oleh dioda D1 dan D2. Keluaran servo dari pembalik diterapkan ke masukan umpanbalik dari tahap masukan penguat. Secara efektif ini membuat sebuah loop umpanbalik pelengkap yang aktif pada dc dan frekuensi sangat rendah.

Jika di sana ada harga dc rata-rata positif kecil pada keluaran penguat, kapasitor integrator C2 akan dimuati oleh pasokan arus yang lewat R5, menggerakkan keluaran integrator ke negatif. Keluaran pembaik menjadi positif dan memasok arus ke masukan umpanbalik untuk mengerakkan masukan umpanbalik ke positif. Ini mengembalikan keluaran peguat menjadi negatif. Bati dc sangat tinggi dari integrator memaksa keluaran penguat secara prinsip nol. Dalam praktik, ia memaksa tegangan keluaran menjadi sama dengan tegangan masukan offset

op amp integrator yang tidak memiliki arus panjar. Biasanya kurang dari 10 mV untuk op amp JFET.

Di atas kertas kerumitan penguat sangat tinggi, tetapi biaya dan ruang untuk kualitas yang sama adalah rendah. Hanya komponen utama berupa op amp ganda dan kapasitor film. Keluaran servo menggerakkan titik masukan umpanbalik penguat melalui resistor yang cukup besar (R4) karena ia hanya butuh suntikan arus koreksi untuk mengalahkan kesalahan offset yang disebabkan masukan secar maksimal. Resistor yang terlampau besar cenderung mengurangi kemampuan servo dan op ampnya berdampak kurang baik pada kualitas suara melalui desah atau distorsi dalam servo. Seperti pembahasan dibawah, perhatikan diperlukan untuk mengabaikan pengaturan R4 terlalu tinggi.

Servo menyediakan peningkatan umpanbalik negatif selama frekuensi rendah. Sepeti halnya yang dilakukan dengan fungsi filter lolos tinggi dalam lintasa audio, tetapi dengan ilektrolitik pada lengan kembali umpanbalik. Dengan servo dc, sekarang tanpa elektrolitik 100 F yang

akan memperburuk suara sekalipun dipintas dengan kapasitor film kecil.

Arsitektur Servo DC

dengan kapasitor untuk menjadikannya sebagai integrator. Ia memerlukan dua kapasitor, dan ini tidak menguntungkan. Kami menyarankan servo dc yang mempekerjakan op amp ganda dan hanya kapasitor integrator tunggal, mungkin sekitar 1 F.

Gambar 8.6 Perwujudan servo dc dengan integrator tak-membalik hanya memerlukan satu op amp tetapi dua kapasitor integrator.

Pengaturan Sudut Frekuensi Bawah

Sekarang mari mengatur titik 3-dB LF untuk keseluruhan penguat 1 Hz, diluar filter lolos tinggi yang dibentuk oleh kapasitor kopling masukan. Ini berarti bahwa bati sekitar loop servo akan jatuh ke satu pada 1 Hz. Ini juga berarti bahwa jumlah umpan balik yang disediakan melalui rangkaian servo sama dengan yang tersedia melalui jaringan umpanbalik pada 1 Hz.

Anggap bahwa jaringan umpanbalik terdiri atas resistor umpanbalik seri 10 k dengan resistor

adlah 20:1. Rangkaian servo harus menyediakan ini jumlah sama dari pelemahan pada 1 Hz. Atur resistor integrator pada 160 k dan kapasitor integrator 1 F. Ini membuat bati integrator

satu pada 1 Hz. Membuat penguat pembalik bati satu. Atur resistor penyuntik sinyal servo ke 10 k. Gabungan dari nilai komponen ini membuat sinyal umpanbalik sama dengan sinyal

umpanbalik utama pada 1 Hz. Bati servo ke keluaran inverter hanya 0,1 pada 1 Hz. Ini berarti bahwa sinyal uji puncak 40 V pada 10 Hz pada keluaran akan menghasilkan puncak 4 V pada keluaran op amp servo. Mereka akan mempunyai marjin cukup melawan pemotongan jika mereka didayai dengan catu 15 V.

Jumlah offset Yang Dikoreksi

Jika servo dc digunakan dengan jaringan umpanbalik terkopling dc impedansi rendah, maka servo dc harus menkoreksi jumlah semua offset yang dibuat oleh arus panjar masukan yang mengalir pada resistor kembali masukan. Dalam hal ini di mana pasangan diferensial tunggal digunakan dengan transistor dipanjar pada 1 mA dan resistansi kembali masuk 50 k, servo

harus mampu membuat 0,5 V penuh untuk kompensasi offset pada sisi umpanbalik dari LTP. Ini mengganggap bahwa beta transistor masukan adalah 100.

Jumlah dari kompensasi offset ini penting. Kebutuhan offset ini ditetapkan dalam jumlah yang ditentukan seberapa banyak koreksi servo yang diperlukan. Dalam contoh diatas, jika op amp dapat menyediakan 14 V, servo akan mampu mengakomodasi 0,7 V offset masukan.

Rancangan servo lainnya yang mempekerjakan resistansi injeksi servo besar (kadang-kadang

untuk alasan yang baik) mungkin tidak mampu memuaskan keperluan 0,5 V. Di sini, ada suatu keunggulan pemakaian JFET untuk LTP karena offset masukan berkaitan dengan arus basis dibatasi.

Trik yang menarik yang diperlihatkan pada Gambar 8.3d adalah menambah resistor penyeimbang dc antara resistor paralel umpanbalik dan masukan tahap masukan BJT. Harga resistor ini dipilih sedemikian hingga resistor kembali kurang resistansi dc dari jaringan umpanbalik. Resistansi yang ditambahkan akan menyamakan offset berkaitan dengan arus

panjar masukan. Resistor ini dapat dipintas dengan kapasitor 1 F, selama aliran arus sinyal