Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 1

MODUL 2 PENGENALAN DESAIN MENGGUNAKAN FPGA

Iskandar Setiadi (13511073)

Asisten: Alfian Abdi / 13208044 Tanggal Percobaan: 01/10/2012 EL2195-Praktikum Sistem Digital

Laboratorium Dasar Teknik Elektro - Sekolah Teknik Elektro dan Informatika ITB

Abstrak

Pada era modern ini, pemodelan rangkaian digital tidak

hanya dapat dilakukan secara manual, tetapi dapat didesain

menggunakan IC dengan bantuan komputer. Salah satu

teknik perancangan yang sering digunakan adalah FPGA

dengan pendekatan skematik maupun bahasa VHDL.

Pada kesempatan ini, kita akan mengimplementasikan

rangkaian full-adder dengan target FPGA.

Kata kunci: FPGA, full-adder, skematik, dan bahasa

VHDL

1. P

ENDAHULUANPerancangan fungsi logika dapat dilakukan dengan setidaknya dua cara, yaitu secara manual maupun digital. Perancangan digital dapat dilakukan di berbagai macam target, salah satunya adalah FPGA.

FPGA, atau dikenal juga sebagai field-programmable gate array, merupakan sebuah devais yang dapat mengimplementasikan fungsi logika berulang kali. Pada percobaan ini, perancangan rangkaian dibantu dengan dua piranti lunak tambahan, yaitu ALTERA QUARTUS II dan ModelSim.

Ada sedikitnya dua cara dalam melakukan perancangan digital, yaitu menggunakan bahasa VHDL maupun pendekatan secara skematik. Dengan mendesain rangkaian full-adder, 4-bit ripple carry adder, maupun 4-bit adder menggunakan berbagi metoda, diharapkan dasar-dasar perancangan rangkaian digital dapat dikuasai dengan baik.

2. S

TUDIP

USTAKACara tradisional dalam mengimplementasikan fungsi logika adalah dengan menggunakan rangkaian CMOS / TTL. Seiring perkembangan zaman, penggunaan chip yang dapat diprogram secara digital pun bermunculan dan disebut juga Programmable Logic Devices (PLDs), [3]. Salah satu teknik perancangan rangkaian digital untuk mengimplementasikan fungsi logika adalah dengan menggunakan FPGA.

2.1

F

IELDP

ROGRAMMABLE GATE ARRAY(FPGA)

FPGA adalah sebuah integrated circuit yang dapat dikonfigurasi dan diprogram berkali-kali. FPGA terdiri atas logika yang dapat diprogram, yang disebut dengan blok logika (logic blocks),[5].

Gambar 2-1 Core dari FPGA Stratix IV ALTERA

Setiap pin masukkan dari FPGA memiliki fungsionalitasnya sendiri dan secara umum, setiap gerbang logika yang dimiliki oleh FPGA mampu menyimpan baik logika HIGH dan logika LOW dalam komponen logika yang disebut dengan Look-Up Table (LUT),[1].

2.2

A

LTERAUP2

E

DUCATIONK

ITPada percobaan ini, salah satu board yang digunakan dalam laboratorium adalah ALTERA UP2 Education Kit. IC ini termasuk dalam kelas (Family) FLEX10K,[7].

Gambar 2-2 IC ALTERA UP2

Pin-pin yang nantinya akan digunakan pada percobaan ini terangkum dalam tabel berikut:

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 2 Tabel 2-1 Referensi Kaki UP2

Nama PIN Kaki yang digunakan UP2

A PIN_41 B PIN_40 C PIN_39 A_OUT PIN_6 B_OUT PIN_13 C_OUT PIN_9 CARRY PIN_24 SUM PIN_17

2.3

F

ULLA

DDERSeperti penjumlahan dalam basis desimal, kita dapat mengoperasikan penjumlahan dalam basis biner menggunakan gerbang logika, yaitu dengan mengimplementasikan full adder dalam rangkaian kita. Full adder bekerja dengan prinsip Sum dan Cout. Perhatikan rangkaian berikut ini,[9]:

Gambar 2-3 Rangkaian Full Adder

Full adder menerima 3 buah masukkan, biasanya disebut dengan A,B, dan Cin. Nilai total dari full adder (sum) didefinisikan sebagai 2 kali nilai Cout ditambah dengan nilai S ( sum = 2 x Cout + S).

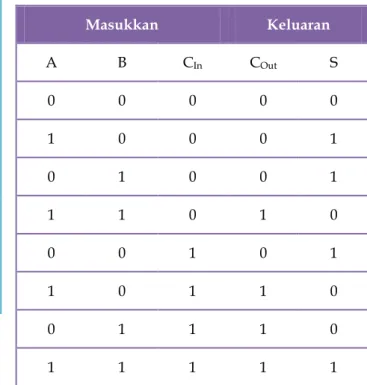

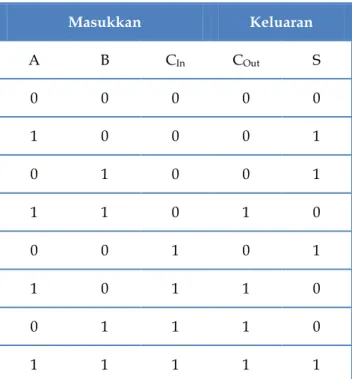

Berikut ini adalah tabel kebenaran dari Full adder:

Tabel 2-2 Tabel Kebenaran Full Adder

Masukkan Keluaran A B CIn COut S 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 1 0 1 1 0 1 1 0 0 1 1 1 0 1 1 1 1 1

Selain adder yang disebutkan diatas, terdapat beberapa jenis adder lainnya seperti half-adder, ripple-carry adder, carry-lookahead adder, dan lookahead carry unit.

2.4

B

AHASAVHDL

VHDL (Very-high-speed integrated circuits Hardware Description Language) adalah bahasa pemrograman perangkat keras yang digunakan untuk memodifikasi sistem logika dalam FPGA ataupun IC. VHDL merupakan pengembangkan dari bahasa prosedural seperti ADA maupun PASCAL, yang kemudian dikembangkan untuk tujuan spesifik,[6].

Salah satu keuntungan menggunakan bahasa VHDL adalah implementasinya yang sederhana dan lebih compact dibandingkan pendekatan skematik. VHDL sendiri dapat dibuat dan disimulasikan pada ALTERA QUARTUS II maupun ModelSim.

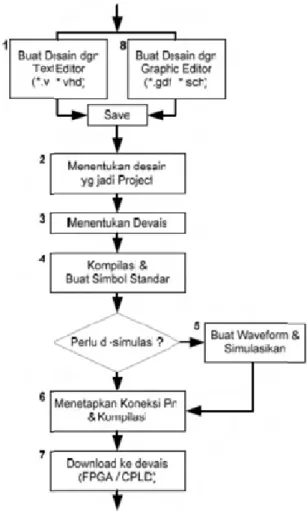

3. M

ETODOLOGIPercobaan ini akan dibagi menjadi delapan bagian. Secara garis besar, perancangan rangkaian digital menggunakan FPGA dapat menggunakan flowchart berikut:

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 3 Gambar 3-2 Flowchart Proses Perancangan Digital

Pada percobaan 2A, kita akan mendesain rangkaian full-adder dengan pendekatan skematik. Pendesainan ini akan dibantu dengan piranti lunak ALTERA QUARTUS II. Berikut adalah rancangan desain dari percobaan ini:

Gambar 3-2 Gambar Skematik Percobaan 2A

Rangkaian tersebut akan menerima 3 masukkan (A, B, Cin) dan memberikan 2 keluaran secara umumnya, yaitu SUM dan CARRY. Setelah proses simulasi menggunakan Netlist berjalan lancar, rangkaian tersebut diimplementasikan pada IC Board FPGA tipe UP-2.

Percobaan 2B akan mendesain full-adder (seperti percobaan 2A) menggunakan bahasa VHDL. File yang dikodekan dalam “modul2vhdl.vhd” adalah sebagai berikut:

Gambar 3-3 Bahasa VHDL untuk Percobaan 2B

Kode tersebut kemudian dikompilasi dan seperti percobaan 2A, pendekatan tersebut diimplementasikan pada Board FPGA tipe UP-2.

Pada percobaan 2C, 4-bit ripple carry adder akan diimplementasikan menggunakan bahasa VHDL. Berikut ini adalah kode VHDL untuk percobaan 2C:

Gambar 3-4 Bahasa VHDL untuk Percobaan 2C

Setelah kita menggunakan pendekatan dengan VHDL, pada percobaan 2D, kita akan menggunakan pendekatan skematik. Kita dapat mensimulasikannya seperti pada proses percobaan 2A. Berikut ini adalah rancangan desain dari percobaan ini:

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 4 Gambar 3-5 Gambar Skematik Percobaan 2D

Selain menggunakan ALTERA QUARTUS II, pemodelan rangkaian digital dapat disimulasikan menggunakan ModelSim. Pada percobaan 2E, kita akan mensimulasikan rangkaian full-adder dengan pendekatan bahasa VHDL. Berikut ini adalah kode VHDL yang akan digunakan:

Gambar 3-6 Bahasa VHDL untuk Percobaan 2E

Stimulus dapat diberikan dengan Right Click ->

Clock dengan memberikan nilai masukkan

periode untuk sinyal A, B, dan C sebesar 50ps, 100ps, dan 200 ps secara terurut. Setelah itu, kita cukup mensimulasikannya dengan menu Tools ->

Run atau dengan mengetikkan run[spasi](time).

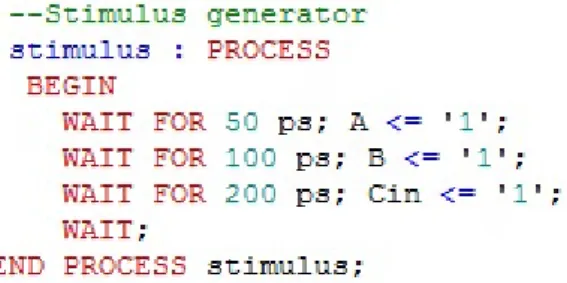

Ada tiga gambar sinyal yang akan disimulasikan, yaitu mode normal, no force, dan dengan force. Pada percobaan 2E, kita memberikan stimulus secara manual. Percobaan 2F ini akan menggunakan konsep testbench, dengan memberikan stimulan melalui kode VHDL. File VHDL yang kita buat akan berfungsi sebagai DUT, yaitu Design Under Test.

Berikut ini adalah kode VHDL yang akan kita gunakan untuk memberikan stimulus pada percobaan ini:

ENTITY tb_modul2vhdl IS END tb_modul2vhdl;

ARCHITECTURE testbench OF tb_modul2vhdl IS COMPONENT modul2vhdl IS

PORT (A,B,Cin : IN BIT; S,Cout : OUT BIT); END COMPONENT; SIGNAL A : BIT := '0'; SIGNAL B : BIT := '0'; SIGNAL Cin : BIT := '0'; SIGNAL S : BIT; SIGNAL Cout : BIT;

BEGIN --Instance module dut : modul2vhdl PORT MAP( A => A, B => B, Cin => Cin, S => S, Cout => Cout); --Stimulus generator clock_A : PROCESS BEGIN

WAIT FOR 50 ps; A <= not A; end PROCESS clock_A; clock_B : PROCESS BEGIN

WAIT FOR 100 ps; B <= not B; end PROCESS clock_B; clock_C : PROCESS BEGIN

WAIT FOR 200 ps; C <= not C; end PROCESS clock_C;

END testbench;

Setelah menggunakan stimulus diatas, kita akan mengganti stimulus dengan kode VHDL berikut ini:

Gambar 3-7 Stimulus untuk Percobaan 2F

Setelah mensimulasikan fungsi logika dengan ModelSim, pada percobaan 2G, kita akan menggunakan ModelSim untuk melakukan proses tapping sinyal dari sebuah desain. Kita akan melakukan modifikasi pada file DUT dengan script berikut:

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 5 Gambar 3-8 Script Tapping Percobaan 2G

Setelah mengetikkan script diatas, kita cukup mensimulasikan ulang seperti pada percobaan 2F. Jika proses-proses diatas dilakukan secara manual, kita dapat membuat script untuk menghindari proses yang sama berulang kali. Pada percobaan 2H, kita akan membuat file bernama sim.do dengan spesifikasi script sebagai berikut:

Gambar 3-9 Script file sim.doPercobaan 2H

Hal selanjutnya yang perlu kita lakukan adalah mensimulasikannya dengan mengetikkan “do sim.do”. Seperti percobaan 2F, kita akan menguji script diatas dengan melakukan pengaturan pada preferensi clock. Lalu kita akan mendapatkan kode berikut ini:

Gambar 3-10 Stimulus Percobaan 2H

Selanjutnya kita akan mensimulasikan testbench yang telah dibuat sebelumnya menggunakan script

file.do. Berikut ini adalah kode yang digunakan

dalam pembuatan file file.do:

Gambar 3-11 Script file file.doPercobaan 2H

4. H

ASIL DANA

NALISIS4.1

M

ENDESAIN FULL ADDER DENGAN SKEMATIKPada percobaan ini digunakan ALTERA QUARTUS II dan board UP2 dengan pendekatan skematik. Dengan menggunakan overwrite clock masukkan A sebesar 10 ns, B sebesar 20 ns, dan Cin sebesar 40 ns, maka ditampilkan hasil simulasi seperti gambar 4-1 berikut:

Gambar 4-1 Simulasi Percobaan 2A pada QUARTUS II Tabel 4-1 Tabel Kebenaran Full Adder Percobaan 2A

Masukkan Keluaran A B CIn COut S 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 0

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 6

0 0 1 0 1

1 0 1 1 0

0 1 1 1 0

1 1 1 1 1

Hasil yang ditunjukkan pada tabel 4-1 diatas sesuai dengan tabel kebenaran full adder referensi pada tabel 2-2. Hal selanjutnya yang akan dilakukan adalah mengimplementasikan pendekatan skematik ini ke FPGA. Gambar 4-2 berikut ini adalah hasil implementasi pada board UP2:

Gambar 4-2 Simulasi Percobaan 2A pada FPGA

Gambar diatas menunjukkan IC diberikan masukkan A dan Cin, sehingga logika S bernilai 0 dan logika COut bernilai 1. Hasil percobaan ini membuktikan logika full adder berjalan dengan baik di board UP2 yang digunakan.

4.2

M

ENDESAINF

ULLA

DDERD

ENGANP

ENDEKATANB

AHASAVHDL

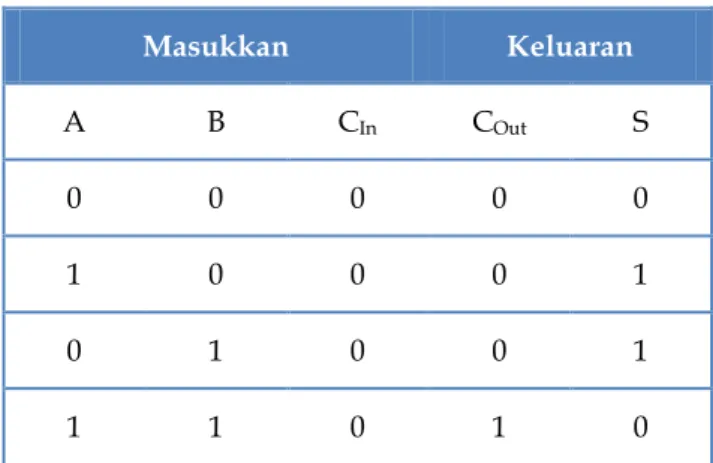

Pada percobaan ini, kita akan menggunakan implementasi bahasa VHDL dalam board yang digunakan. Simulasi yang dilakukan menggunakan bahasa VHDL menghasilkan wave seperti gambar 4-3 berikut:

Gambar 4-3 Simulasi Percobaan 2B Tabel 4-2 Tabel Kebenaran Full Adder Percobaan 2B

Masukkan Keluaran A B CIn COut S 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 1 0 1 1 0 1 1 0 0 1 1 1 0 1 1 1 1 1

Hasil simulasi diatas menunjukkan kesamaan antara keluaran menggunakan pendekatan skematik dan bahasa VHDL. Hal ini menunjukkan bahwa kita dapat menggunakan pendekatan skematik maupun bahasa VHDL dalam melakukan implementasi pada board FPGA.

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 7 Gambar 4-4 Simulasi Percobaan 2B pada FPGA

Gambar diatas menunjukkan IC FPGA diberikan masukkan A, B, dan Cin sehingga menghasilkan logika S dan Cout bernilai 1.

Dari dua percobaan diatas, kita dapat menganalisis kelebihan dan kerugian dari dua pendekatan tersebut. Pendekatan VHDL lebih sederhana untuk digunakan, karena apabila kita ingin mengimplementasikan rangkaian yang kompleks seperti membuat sebuah rangkaian berukuran besar secara manual, maka faktor resiko galat menggunakan pendekatan skematik akan meningkat.

Disisi lain, bahasa VHDL memerlukan pembelajaran bahasa terlebih dahulu, sehingga untuk rangkaian-rangkaian sederhana, pendekatan skematik lebih mudah digunakan dan lebih user-friendly.

4.3

M

ENDESAIN4-B

ITR

IPPLEC

ARRYA

DDERD

ENGANVHDL

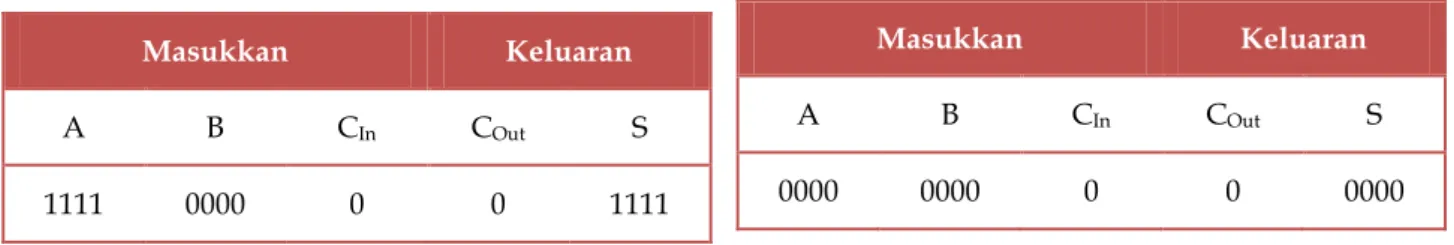

4-Bit ripple carry adder menerima masukkan A dan B 4 bit, serta Cin 1 bit dan mengembalikan hasil berupa Sum 4 bit dan Cout 1 bit.

A0, A1, A2, dan A3 dibuat menjadi satu grup (misalkan A), sedangkan B0, B1, B2, dan B3 dibuat menjadi satu grup pula (misalkan B). Perhatikan hasil waveform berikut ini (gambar 4-5):

Gambar 4-5 Simulasi Percobaan 2C pada QUARTUS II

Perhatikan bahwa waveform diatas akan membentuk tabel kebenaran sebagai berikut:

Tabel 4-3 Tabel Kebenaran 4-Bit Ripple Carry Adder

Masukkan Keluaran A B CIn COut S 1111 0000 0 0 1111 0000 1111 0 0 1111 1111 1111 0 1 1110 0000 0000 1 0 0001 1111 0000 1 1 0000 0000 1111 1 1 0000 1111 1111 1 1 1111 0000 0000 0 0 0000

Hasil keluaran dari 4-Bit ripple carry adder diatas sesuai dengan definisi referensi. Sebagai contoh, saat A = 1111, B = 1111, dan Cin = 0, maka nilai penjumlahan A + B + CIn dalam basis 2 adalah 11110. Perhatikan pada tabel diatas bahwa untuk nilai A,B, CIn yang diberikan, menghasilkan Cout = 1 dan S = 1110 (A + B + CIn =Cout * 10000 + Sum).

4.4

M

ENDESAIN4-B

ITA

DDERD

ENGANS

KEMATIKSetelah sebelumnya kita menggunakan pendekatan menggunakan bahasa VHDL, pada percobaan ini kita akan menggunakan pendekatan skematik. Berikut ini adalah hasil waveform menggunakan pendekatan skematik (gambar 4-6):

Gambar 4-6 Simulasi Percobaan 2D pada QUARTUS II

Hasil waveform diatas dapat ditranslasikan kedalam tabel kebenaran sebagai berikut:

Tabel 4-4 Tabel Kebenaran 4-Bit Adder Dengan Skematik

Masukkan Keluaran

A B CIn COut S

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 8 1111 0000 0 0 1111 0000 1111 0 0 1111 1111 1111 0 1 1110 0000 0000 1 0 0001 1111 0000 1 1 0000 0000 1111 1 1 0000 1111 1111 1 1 1111

Perhatikan bahwa tabel kebenaran 4-4 identik dengan hasil tabel kebenaran 4-3 (menggunakan bahasa VHDL). Hal ini menunjukkan bahwa kita dapat menggunakan baik pendekatan skematik maupun bahasa VHDL dalam merancang rangkaian digital seperti 4-Bit carry adder.

4.5

S

IMULASIS

EDERHANAM

ENGGUNAKANM

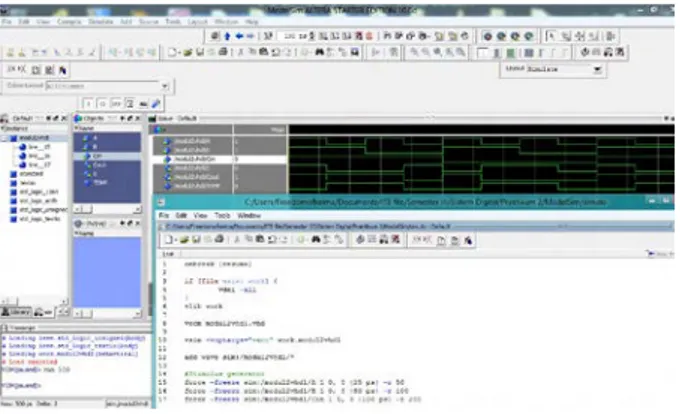

ODELISMSetelah sebelumnya kita mensimulasikan rangkaian digital menggunakan ALTERA QUARTUS II, berikut ini adalah hasil simulasi menggunakan piranti lunak ModelSim:

Gambar 4-7 Simulasi Percobaan 2E pada ModelSim Hasil waveform diatas didapatkan dengan mengatur clock dari masukkan (A,B,Cin) menjadi masing-masing 50ps, 100ps, dan 200ps. Stimulus yang diberikan memberikan hasil waveform yang berlogika sama dengan menggunakan ALTERA QUARTUS II.

Hal selanjutnya yang diuji pada bagian ini adalah menggunakan perintah (command) No Force. Perintah tersebut berfungsi untuk membatalkan (undo) dari perintah force yang diberikan sebelumnya. Pada kondisi default, perintah ini akan memberikan hasil keluaran 0.

Gambar 4-8 Force Value B Menjadi 1 pada ModelSim Perhatikan gambar 4-8 diatas. Gambar tersebut merupakan representasi hasil ketika value B diberikan force agar selalu bernilai 1. Perintah force berfungsi untuk memaksakan agar masukkan input selalu bernilai logika tertentu (1 / 0).

4.6

M

EMBUATT

ESTBENCHSalah satu kelebihan ModelSim dibandingkan ALTERA QUARTUS II adalah simulasi rangkaian mengunakan testbench. Perhatikan gambar 4-9 berikut ini:

Gambar 4-9 Stimulus Generator pada ModelSim

Perintah (command) clock yang semula menggunakan cara Right Click -> Clock dapat digantikan dengan testbench (Design Under Test / DUT). Gambar 4-9 menunjukkan hasil keluaran waveform menggunakan stimulus generator. Amati potongan kode berikut ini:

clock_A : PROCESS BEGIN

WAIT FOR 50 ps; A <= not A; end PROCESS clock_A;

Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 9

Perintah tersebut menunjukkan bahwa setiap 50ps, nilai logika A akan di-invert. Ketika logika A bernilai 0, maka setelah 50ps, logika A akan bernilai 1 dan berlaku sebaliknya. Selain cara tersebut, kita dapat memaksakan suatu value logika tertentu pada masukkan. Perhatikan contoh berikut ini (gambar 4-10):

Gambar 4-10 Stimulus : PROCESS pada ModelSim WAIT FOR 50 ps; A <= ‘1’;

Potongan kode diatas menunjukkan, setelah 50ps, maka logika A akan selalu bernilai 1. Hal yang sama berlaku untuk logika B yang di inisialisasi 100ps serta logika C yang di inisialisasi 200ps. Dari dua contoh berbeda diatas, maka kita dapat mengkombinasikan kemungkinan-kemungkinan logika yang kita inginkan.

4.7

M

ELAKUKANP

ROSEST

APPINGS

INYAL DARIS

EBUAHD

ESAINProses tapping sinyal adalah sebuah proses pengambilan nilai sinyal yang bukan merupakan bagian dari keluaran sistem rangkaian digital yang diuji. Pada percobaan ini, kita misalkan sinyal tersebut adalah Temp, yang bernilai logika A XOR B. Berikut ini adalah hasil waveform dari simulasi yang dijalankan (gambar 4-11):

Gambar 4-11 Proses Tapping pada ModelSim Dari waveform tersebut, kita dapat menganalisis kebenaran dari A XOR B. Perhatikan bahwa saat logika A bernilai 0 dan logika B bernilai 0, maka logika Temp bernilai 0. Dilain waktu, saat logika A

bernilai 1 dan logika B bernilai 0, maka logika Temp bernilai 1. Hal ini menunjukkan bahwa hasil waveform keluaran sesuai dengan definisi operasi XOR pada referensi.

4.8

M

EMBUATS

CRIPTU

NTUKM

ELAKUKANS

IMULASIKeunggulan lain dari piranti lunak ModelSim adalah penggunaan script untuk menjalankan proses yang sama berulang kali. Script file ini memiliki ekstensi ”.do”, yang berisikan sekumpulan instruksi untuk melakukan sesuatu. Dengan mengetikkan stimulus generator pada script yang digunakan (Gambar 3-10), maka simulasi dapat di eksekusi tanpa perlu menunggu masukkan manual. Perhatikan hasil perintah ”do sim.do” berikut ini (gambar 4-12):

Gambar 4-12 Simulasi script file sim.do

Perintah yang kita jalankan ini sama seperti menjalankan manual file modul2vhdl seperti pada

percobaan 2E (Gambar 4-7).

Gambar 4-13 Simulasi script file file.do

Selain itu, script juga dapat mensimulasikan testbench / DUT yang digunakan dalam percobaan. Hasil waveform gambar 4-13 menunjukan eksekusi “run 500” pada file tb_modul2vhdl yang telah kita buat sebelumnya.

5. K

ESIMPULANTerdapat dua pilihan piranti lunak yang dapat digunakan, yaitu ALTERA QUARTUS II (Percobaan 2A – 2D) dan ModelSim (Percobaan

2E-Laporan Praktikum - Laboratorium Dasar Teknik Elektro – STEI ITB 1 0

2H). ALTERA QUARTUS II dan ModelSim memiliki kelebihan dan kekurangan masing-masing. Dari segi penggunaan, ALTERA QUARTUS II lebih spesifik untuk pemrosesan dengan FPGA secara langsung sedangkan ModelSim digunakan untuk simulasi lokal tanpa perangkat IC,[8].

Keuntungan dari ModelSim adalah kita dapat menggunakan testbench, yaitu sebuah file yang digunakan untuk menguji desain (Device Under Test / DUT) yang telah kita buat. Selain itu, ModelSim dapat menggunakan dan membuat script, sehingga prosedur simulasi yang berulang-ulang dapat disingkat dan diproses lebih cepat. Kita dapat memberikan stimulus melalui bahasa VHDL sehingga kita tidak perlu memasukkan input secara manual satu-persatu.

Sedangkan keuntungan dari ALTERA QUARTUS II adalah integrasinya dengan FPGA yang lebih user-friendly dan mudah digunakan. Selain itu, kita dapat menggunakan pendekatan secara skematik ketika ModelSim harus menggunakan bahasa VHDL (file skematik harus di convert terlebih dahulu).

Dari pertimbangan diatas, dapat disimpulkan bahwa ModelSim lebih baik digunakan dalam proses pembelajaran karena lebih compact dan dapat memproses stimulus tanpa membutuhkan interferensi manual dari pengguna.

Secara umum, perangkaian secara digital dapat dilakukan dengan dua pendekatan, baik secara skematik (Percobaan 2A & 2D), maupun menggunakan bahasa seperti bahasa VHDL (Percobaan 2B, 2C, 2E, 2F, 2G & 2H).

Rangkaian Full adder dapat diimplementasikan dengan berbagai cara (seperti cara diatas). Fungsi utama dari rangkaian ini adalah untuk menjumlahkan bilangan biner menggunakan fungsi gerbang logika. Ada beberapa jenis rangkaian adder seperti Full adder (Percobaan 2B), maupun Ripple carry adder (Percobaan 2C).