BAB I

DASAR-DASAR ELEKTRONIKA DIGITAL

Pada bab-bab Elektronika Analog telah dibahas saklar transistor dan

multivibrator. Kedua pembahasan itu kini telah berkembang lebih jauh sebagai

Elektronika Digital, dimana saklar transistor berkembang menjadi yang dikenal sebagai

pintu logika, yaitu saklar elektronik yang memiliki kemampuan untuk mengambil

keputusan berdasar pada keadaan beberapa masukannya. Dengan kombinasi antara

pintu logika dan flip-flop dibuat bermacam-macam alat yang menggunakan elektronika

digital. Lebih jauh lagi Elektronika Digital telah banyak beralih ke dalam IC

membentuk mikroprosesor dan berbagai komponen bantuannya.

Pada bahan ajar ini dan berikutnya kita akan mempelajari Elektronika Digital.

Bahan ajar ini membahas dasar-dasar elektronika digital, yaitu pengertian tentang

logika biner dan bilangan biner, beberapa pengertian dan penerapan pintu logika,

rangkaian elektronika dibalik pintu-pintu logika, dan terakhir tentang flip-flop. Pada

bab-bab terakhir pembahasan kita lanjutkan hingga mencakup komponen-komponen

digital yang lebih canggih. Sudah barang tentu kita tak akan membahas segala sesuatu

tentang elektronika digital hanya dengan dua bab saja.

1.1 SISTEM BILANGAN

Desimal : 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 (bilangan dasar 10)

Biner : 0 dan 1 (bilangan dasar 2)

Heksadesimal : 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F (bilangan dasar 16)

Oktaf : 0, 1, 2, 3, 4, 5, 6, 7 (bilangan dasar 8)

Tabel 1-1. Bilangan biner, desimal, hexadesimal

Biner Desimal Heksadesimal 1

Konversi Desimal ke Biner

Ada beberapa cara konversi desimal ke biner, antara lain adalah dengan menggunakan

cara pembagian:

Contoh: ubah 5310 menjadi bilangan biner.

Solusi:

Contoh konversi lain:

Biner ke Desimal:

110012 = 11001B = 1 x 24 + 1 x 23 + 0 x 22 + 0 x 21 + 1 x 20

= 16D + 8D + 0D + 0D +1D

Hexadesimal ke Desimal:

152B16 = (1 x 163) + (5 x 162) + (2 x 161) + (11 x 160)

= (1 x 4096) + (5 x 256) + (2 x 16) + (11 x 1)

= 4096 + 1280 + 32 + 11

= 541910 = 5419D

Desimal ke Hexadesimal:

5419/16 = 338 sisa 1110 B16 LSB

338/16 = 21 sisa 210 216

21/16 = 1 sisa 510 516

1/16 = 0 sisa 110 116 MSB

Sehingga 541910 = 152B16

Hexadesimal ke Biner:

Ubah 2A5C16 ke BilanganBiner

216 = 00102 MSB

A16 = 10102

516 = 01012

C16 = 11002 LSB

Sehingga 2A5C16 = 0010 1010 0101 11002

Biner ke Hexadesimal:

Ubah 0010 1010 0101 11002 ke Bilangan Hexadesimal.

00102 = 216 MSB

10102 = A16

01012 = 516

11002 = C16 LSB

Sehingga 0010 1010 0101 11002 = 2A5C16

Desimal ke BCD

Pada beberapa aplikasi sering kali lebih sesuai apabila setiap digit bilangan desimal

diubah menjadi 4 digit bilangan biner. Hasilnya sering disebut Binary Code Decimal

Contoh:

17510 = 1 7 5

0001 0111 0101

Sehingga: 17510 = 0001 0111 0101 BCD

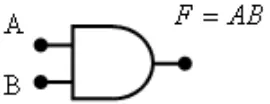

1.2 GERBANG LOGIKA 1.2.1 Gerbang AND

Simbol:

Gambar 1-1. Simbul dan persamaan gerbang AND

Tabel 1-2. Tabel kebenaran gerbang AND

A B F AB

1 1 1

1 0 0

0 1 0

0 0 0

Keluaran yang dihasilkan pada gerbang AND dalam

keadaan tinggi (high) jika semua masukan dalam

keadaan tinggi. Sebaliknya jika keadaan masukan

berbeda atau semua masukan dalam keadaan rendah

(low) maka keluaran yang dihasilkan dalam keadaan

rendah (low).

1.2.2 Gerbang OR

Simbul:

Gambar 1-2. Simbul dan persamaan gerbang OR

Tabel 1-3. Tabel kebenaran gerbang OR

A B F AB

1 1 1

1 0 1

0 1 1

0 0 0

Keluaran yang dihasilkan oeh gerbang OR dalam

kea- daan tinggi jika masukan memiliki keadaan

berbeda atau semua masukan mempunyai keadaan

tinggi. Sebaliknya, jika semua masukan dalam

mempunyai ke adaan logika rendah.

1.2.3 Gerbang NOT

Simbul:

Gambar 1-3. Simbul dan persamaan gerbang NOT

Tabel 1-4. Tabel Kebenaran gerbang NOT

A F A

1 0

0 1

Keluaran yang dihasilkan oleh gerbang NOT

mempunyai keadaan yang berkebalikan dengan

keadaan masukannya. Jika masukan dalam keadaan

tinggi maka keluaran yang dihasilkan dalam keadaan

rendah, sebaliknya jika masukan dalam keadaan

rendah maka keluaran yang dihasilkan dalam keadaan

tinggi.

1.2.4 Gerbang NAND (NOT dan AND)

Simbol:

Gambar 1-4. Simbul gerbang AND dan NOT

Biasa disimbulkan dengan:

Gambar 1-5. Simbul gerbang AND

Tabel 1-5. Tabel Kebenaran gerbang NAND

Masukan Keluaran

A B AB F=AB

1 1 1 0

1 0 0 1

0 1 0 1

0 0 0 1

Gerbang NAND adalah gerbang gerbang

AND yang diNOTkan. Keluaran yang

dihasilkan pada gerbang NAND ini dalam

keadaan tinggi jika masukan dalam

keadaan logika berbeda atau semua

masukannya memiliki keadaan logika

1.2.5 Gerbang NOR (NOT dan OR)

Simbol:

Gambar 1-6. Gerbang NOT – OR

Biasanya dinyatakan dengan simbul

Gambar 1-7. Gerbang NOR

Tabel 1-6. Tabel Kebenaran NOR

Masukan Keluaran

A B AB F AB

1 1 1 0

1 0 1 0

0 1 1 0

0 0 0 1

Gerbang NOR adalah gerbang OR yang

diNOTkan. Keluaran yang dihasilkan dalam

keadaan tinggi jika semua masukan dalam

keadaan rendah. Sebaliknya keluaran dalam

keadaan rendah jika masukan dalam keadaan

berbeda atau semua masukan dalam keadaan

tinggi.

1.2.6 Gerbang EXOR Simbol:

Gambar 1-8. Simbul dan persamaan gerbang EXOR

Tabe 1-7. Tabel Kebenaran Gerbang EXOR

A B F AB

1 1 0

1 0 1

0 1 1

0 0 0

Gerbang EXOR mempunyai keluaran yang unik.

Keluaran dalam keadaan logika tinggi jika

masukannya mempunyai keadaan yang berbeda.

Sebaliknya jika semua masukan dalam keadaan

logika sama maka keluaran yang dihasilkan dalam

keadaan rendah.

Gambar 1-9. Gerbang EXNOR

Tabel 1-8. Tabel Kebenaran gerbang EXNOR

diNOTkan. Sehingga keluaran yang dihasilkan

merupakan kebalikan dari keluaran yang

dihasulkan oleh gerbang EXOR. Keluaran dalam

keadaan tinggi jika semua masukan mempunyai

keadaan sama, sebaliknya keluaran yang

dihasilkan dalm keadaan rendah jika masukan

dalam keadaan berbeda.

1.3 ALJABAR BOOLE 1.3.1 Teorema Aljabar Boole

0

1.3.2 Teorema D’Morgan

B

B

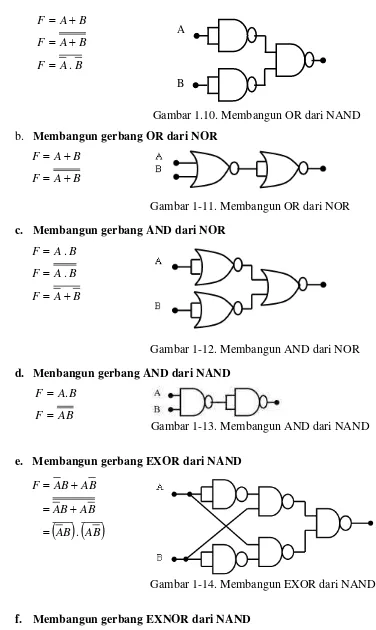

Gambar 1.10. Membangun OR dari NAND

b. Membangun gerbang OR dari NOR

B

Gambar 1-11. Membangun OR dari NOR

c. Membangun gerbang AND dari NOR

B

Gambar 1-12. Membangun AND dari NOR

d. Menbangun gerbang AND dari NAND

B

Gambar 1-13. Membangun AND dari NAND

e. Membangun gerbang EXOR dari NAND

AB ABGambar 1-14. Membangun EXOR dari NAND

f. Membangun gerbang EXNOR dari NAND

A

AB

ABGambar 1-15. Membangun EXNOR dari NAND

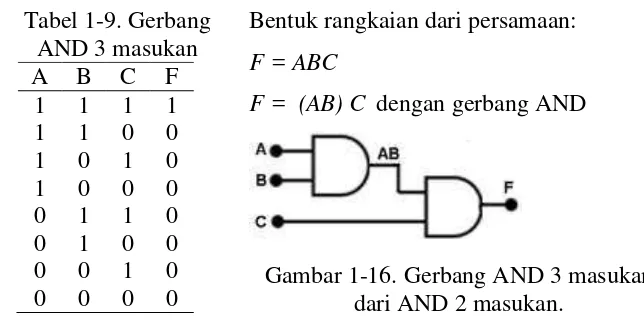

1.3.3 Gerbang logika 3 masukan Tabel 1-9. Gerbang

AND 3 masukan

Bentuk rangkaian dari persamaan:

F = ABC

F = (AB) C dengan gerbang AND

Gambar 1-16. Gerbang AND 3 masukan dari AND 2 masukan.

Bentuk rangkaian dari persamaan F ABCdengan gerbang NAND

Gambar 1-17. Gerbang AND 3 masukan dari NAND 2 masukan.

Rangkaian berikut hasilnya sama, tapi rangkaiannya berbeda:

C

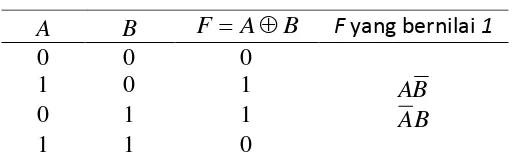

1.3.4

Sum of Product

Tabel 1-10. Tabel kebenaran EXOR

Persamaan EXOR menjadi: F AB AB

b. Rangkaian Half Adder (HA):

Keterangan: A, B = input C, S = output S = Sum C = Carry Gambar 1-18. Rangkaian Half Ader

Tabel 1-11. Tabel kebenaran rangkaian Half Adder

Persamaan HA menjadi:

C = AB adalah pers. AND gate

a. Bangun rangkaian HA tersebut menggunakan NAND gate (gunakan persamaan

aljabar Boole dan d’Morgan).

b. Bangun rangkaian HA tersebut menggunakan NOR gate.

Persamaan tiga masukan:

Tabel 1-12. Cara menentukan persamaan tiga masukan

Persamaan menjadi: F ABC ABC ABC ABC

Tugas: dengan menggunakan persamaan aljabar Boole dan d’Morgan, bangun rangkaian tersebut menggunakan NAND gate dua masukan.

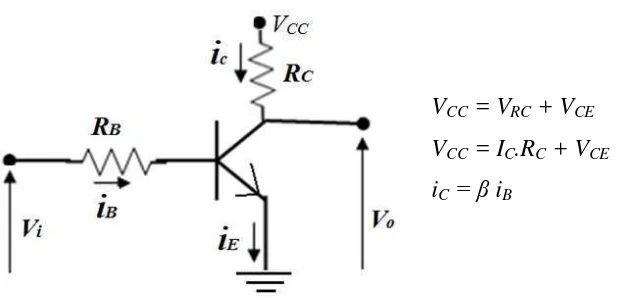

1.4 RANGKAIAN DIGITAL 1.4.1 Aplikasi pada gerbang NOT Saklar transistor

VCC = VRC + VCE

VCC = IC.RC + VCE

iC= β iB

Ganbar 1-19. Rangkaian saklar elektronik

1.4.2 Aplikasi pada gerbang OR

Gambar 1-20. Rangkaian gerbang OR

Jika salah satu masukan 1 akan menghasilkan

F = 1.

Jika dioda diberi panjar maju, maka

hambatannya kecil. Sebaliknya jika dioda

diberi panjar mundur, maka hambatannya

besar.

1.4.3 Aplikasi pada gerbang AND

Gambar 1-21. Rangkaian

Jika kedua masukan A dan B adalah 1,

maka keluaran F = 1.

Jika salah satu masukan adalah 1, maka

gerbang AND

1.5 FLIP-FLOP

Flip-flop atau bistabil atau mempunyai dua keadaan stabil. Satu ciri dari flip-flop adalah

keluaran tetap berada pada keadaan stabilnya walaupun isyarat masukan yang

menyebabkan keadaan itu telah berubah. Perubahan berikutnya pada masukan akan

mengubah keadaan ke luaran flip-flop. Jadi flip-flop ini mempunyai kemampuan

mengingat keadaan logika. Dengan flip-flop ini dapat dibuat pencacah, pembagi

frekuensi, memori komputer dan lainnya. Flip-flop ang akan dibahas dalam topik ini

adalah berbagai macam flip-flop, seperti S-R latch, flip-flop JK, flip-flop D, dan flip-flop

T.

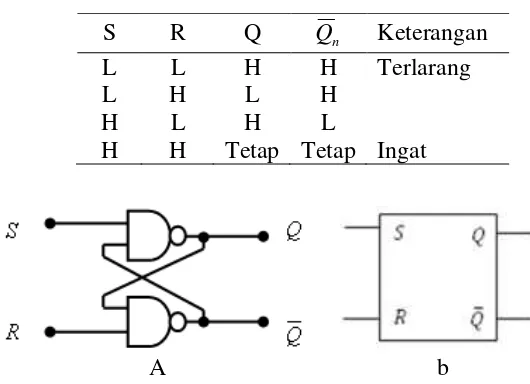

1.5.1 LATCH

Suatu flip-flop sederhana dapat dibuat dengan pintu NAND seperti pada Gambar 1-22

Tabel 1-13: Tabel kebenaran latch SR

S R Q Qn Keterangan

L L H H Terlarang

L H L H

H L H L

H H Tetap Tetap Ingat

A b

Gambar 1-22. (a) Rangkaian Latch RS, (b) Simbul Latch RS.

Bila masukan R pada keadaan HIGH dan S pada keadaan LOW, maka keluaran Q akan

LOW dan Q akan HIGH. Dari tabel kebenaran terlihat bahra selama masukan R dan S

berbeda, maka keluaran pada Q ikut S dan keluaran Q nengikuti R.

Jika kedua masukan HIGH maka keadaan keluaran akan tetap pada keadaan sebelum

keadaan masukan menjadi HIGH, keadaan ini disebut keadaan INGAT. Jika kedua

masukan LOW maka keadaan keluaran adalah HIGH, selajutnya jika kedua masukan

Keadaan ini haruslah dihindari, sehingga keadaan ini disebut keadaan terlarang. Sebagai

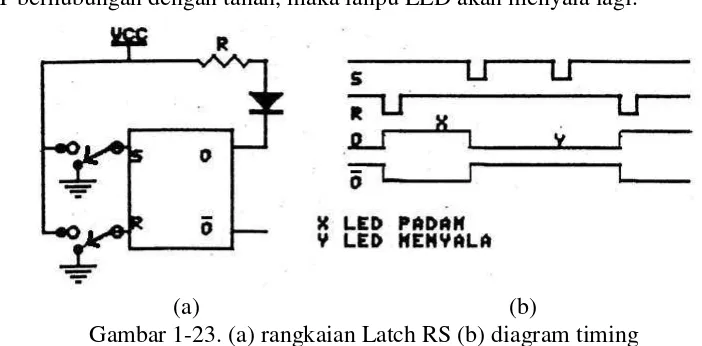

contoh penggunaan LATCH RS pada Gambar 1-23.

Mula-mula saklar reset ditekan sebentar akan membuat Q nenjadi H sehingga lanpu LED

padam dan Q nenjadi L seperti pada diagram timing pada Gambar 1-23(b). Bila pada

suatu saat saklar T terhubung dengan tanah walau hanya sekejap, keluaran Q akan

menjadi L sehingga lanpu LED akan nenyala, dan Q menjadi H. Dalam keadaan ini bila

saklar T terhubungkan ke tanah keadaan flip-flop tidak berubah, oleh karena flip-flop

dalam keadaan ingat. Baru setelah saklar reset dihubungkan dengan tanah walau hanya

sebentar Q nenjadi H sehingga lampu LED padam, dan Q menjadi L. Bila setelah ini

saklar T berhubungan dengan tanah, maka lanpu LED akan menyala lagi.

(a) (b)

Gambar 1-23. (a) rangkaian Latch RS (b) diagram timing

Kata LATCH dapat diterjemahkan dengan kata mengait. Perubahan keadaan sekejap (S

→ L, R → H) pada masukan menyebabkan keadaan keluaran mengait pada suatu

keadaan. Walaupun masukan sudah berubah kena lagi (S → H, R → H) keadaan

keluaran tetap pada keadaannya. Sifat int dimanfaatkan pada penggunaan flip-flop

sebagai komponen memori semikonduktor. LATCH RS juga dapat dibuat dengan pintu

NOR seperti dditunjukkan pada Gambar 1-24.

Tabel 1-14. Tabel kebenaran RS Latch dengan pintu NOR

S R Q Q

L L Tetap Tetap

L H L H

H L H L

Gambar 1-24. Latch RS dengan pintu NOR

LATCH RS juga dapat dibuat dengan pintu NAND seperti dditunjukkan pada Gambar

1-25 dan tabel kebenrannya ditunjukkan seperti pada Tabel 1-15.

(a) (b)

Gambar 1-25. (a) Gated RS Latch (b) Simbul RS Latch

Tabel 2-3: Tabel kebenaran RS Latch

dengan: X = DON'T CARE

Bila G pada keadaan L, maka flip-flop pada keadaan ingat, tak perduli keadaan S atau R.

Fip-flop akan bekerja bila G pada keadaan H. Dengan memasang suatu inverter antara S

dan R kedua masukan ini akan merupakan komplemen satu dengan lainnya dan

komplemen yang dihasilkan disebut D-LATC. D berarti data (Gambar 1-26 a)

G S R Qn+1 Qn1

L X X Qn Qn

H L L Qn Qn

H L H L H

H H L H L

(a) (b)

Gambar 1-26. (a) Rangkaian D-Latch, (b) Simbul D-Latch

Tabel 1-16. Tabel kebenaran D-Latch

G D Qn1 Qn1

L X Qn Qn

H L L H

H H H L

dari tabel kebenaran tampak bahwa keluaran akan nengikuti saklar G ada pada keadaan

H. Agar lebih jelas kerja D-LATCH ini ditunjukkan dengan diagram timing pada Gambar

1-27.

Tanpak bahwa masukan D baru diteruskan ke keluaran Q setelah G dibuat H, walaupun

hanya sebentar.

Gambar 1-27. Diagram timing D-Latch

FLIP-FLOP J K

Masalah keadaan tertentu pada RS LATCH diatasi dengan menggunakan flip-flop JK

(a) (b)

Gambar 1.28. (a) Flip-flop JK (level triggered), (b) Simbul flip-flop JK

Tabel 1-17. Tabel kebenaran JK FF

Ck J K Qn+1 Qn1

L X X Qn Qn

H L L Qn Qn

H L H L H

H H L H L

H H H Qn Qn

Dari tabel kebenaran tampak bahwa bila kedua maskan ada pada keadaan L maka

keluaran akan berubah keadaan setiap kali CK menjadi H. Agar jelas ini dilukiskan

dengan diagram timing (Gambar 1-29).

(a) (b)

Gambar 1-29. (a) Flip-flop JK dipasang sebagai flip-flop toggle (b) Diagram timing untuk flip-flop toggle.

Pada flip-flop JK kadang-kadang diberi masukan kontrol yaitu preset (PR) dan clear

(CLR), seperti pada Gambar 1-30. Kedua masukan ini disebut masukan langsung (direct

Gambar 1-30. (a) Flip-flop JK dengan preset dan clear (b) Simbul flip-flop JK

Tabel 1-18. Tabel kebenaran Flip-flop JK dengan preset dan clear

PR CLR J K G Qn+1 Qn1

L X X X X Tak tentu Tak tentu

L H X X X L H

H L X X X H L

H H X X X Qn Qn

Masukan CK disebut masukan clock. Tampak bahwa masukan PR dan CLR berlaku

seperti masukan RS pada RS LATCH. Flip-flop JK masih mempunyai masalah yaitu

isyarat pada CK harus amat sempit, yaitu harus lebih sempit dari waktu propagasi pintu

togika dan latch. Agar bekerja baik, pulsa CK tak boleh lebih lebar dari 30 nS. Pulsa

sempit seperti ini dapat dibuat suatu monostabil. Masalah pulsa trigger sempit ini dapat

diatasi dengan menggunakan flip-flop dengan trigger tepi (edge-triggered flip-flop) atau

dengan flip-flop master slave.

Cara kerja edge-triggered flip-flop dapat diterangkan dengan diagram timing seperti pada

Gambar 31 untuk pentriggeran tepi negatif (negativ edge triggering). Pada Gambar

1-31 (a) tanda pada masukan CK menyatakan bahwa keadaan masukan akan ditransfer

kepada keluaran pada transisi negatif. Contoh flip-flop JK dengan trigger adalah 74H101,

74H102, 74H103, 74H105, 74H108 dari Texas Instruments.

Flip-flop masterslave terdiri dari dua flip-flop yang dihubungkan seri, flip-flop pertama

disebut master dan flip-flop kedua disebut slave. Transver keadaan masukan ke keadaan

Gambar 1-31. (a) Flip-flop JK master slave sebagai flip-flop (b) diagram timing

Gambar 1-32. Keadaan masukan-keluaran

Tahapan-tahapan tersebut adalah:

1 - 2 isolasi slave dari master

2 - 3 transfer data dari masukan kepada master

3 - 4 non aktifkan masukan data

4 transfer data dari master ke slave .

Diagram timing untuk flip-flop masterslave JK pada Gambar 1-33 (b)

Gambar 1-33. (a) Flip-flop master slave 7473 (b) Diagram timing

Pada diagram timing tanpak bahwa flip-flop masterslave dapat meneruskan pulsa data

pada pulsa clock no 4. Ini berlaku asalkan pulsa data lebih lebar dari 20 ns. Untuk edge

triggered flip-flop pulsa sata ini tidak diterima oleh karena saat transisi negatif pulsa data

sudah berakhir. Flip-f lop masterslave dengan data lock-ouc memungkinkan menerima