DESAIN METODE PENGATURAN DATA BARIS CITRA BLOK 8 PIXEL

UNTUK IMPLEMENTASI PADA IC FPGA SEBAGAI PENDUKUNG

PERCEPATAN OPERASI PERKALIAN QDCT DALAM PROSES KOMPRESI

CITRA JPEG

Drs. Lingga Hermanto, MMSi1 Anggi Nur Octavia2 1. Dosen Universitas Gunadarma 2. Mahasiswa Universitas Gunadarma Fakultas Ilmu Komputer dan Teknologi Informasi

Universitas Gunadarma

ABSTRAKSI

Dalam mendesain rangkaian pembagian data 8 blok pixel ini yang nantinya akan diproses dalam suatu kompresi citra lalu di implementasikan ke dalam ic FPGA merupakan salah satu bagian dari rangkaian keseluruhan kompresi citra dimana bagian ini merupakan proses input atau proses pembagian data 8 blok pixel. Rangkaian ini telah di desain sesuai dengan fungsi dan tujuannya dengan baik untuk melakukan proses input dan pembagian data 8 blok pixel. Rangkaian desain ini dibagi menjadi tiga unit yaitu unit shift register yang memiliki fungsi sebagai input data dan untuk memvalidasi (dengan bantuan clock) dan menyimpan setiap pixel yang masuk. Lalu ada rangkaian unit counter yang berfungsi sebagai penghitung hingga pixel ke-8 dan menginformasikan 8 D flip-flop untuk mengambil data 8 pixel. Sedangkan rangkaian unit D flip flop melakukan pengambilan data yang telah dip roses oleh shift register dengan bantuan counter dan menampilkan hasil proses tersebut secara serentak. Tujuan dari keseluruhan desain rangkaian ini adalah membagi 8 blok data secara bertahap pada rangkaian yang telah di desain dan menghasilkan data yang diinginkan user untuk nantinya akan di masukkan ke dalam proses kompresi citra.

Kata Kunci : Shift Register, Counter, D flip flop, Clock.

PENDAHULUAN

Perkembangan algoritma kompresi data seperti JPEG telah berkembang pesat. Terlebih di dalam pengolahan citra yang merupakan suatu signal dua-dimensi yang dapat diobservasi oleh sistem visual manusia. Suatu citra diperoleh dari penangkapan kekuatan sinar yang dipantulkan oleh objek. Dalam hal ini bagaimana caranya suatu data yang telah dikompresi hasilnya menjadi berukuran kecil tetapi kualitas yang dihasilkan tidak terlalu jauh berkurang.

FPGA (Field Programmable Gate Array) merupakan suatu IC digital yang sering digunakan untuk mengimplementasikan rangkaian digital, dalam hal ini digunakan untuk mengimplementasikan perangkat lunak yang telah dirancang sebelumnya untuk menghasilkan algoritma kompresi JPEG[1]. FPGA dipilih karena lebih mudah digunakan dan lebih cepat

dalam segi pengoperasiannya dibandingkan perangkat keras lainnya.

Skripsi ini merupakan salah satu usaha mengimplementasikan rangkaian-rangkaian digital ke dalam FPGA nantinya yang akan merancang algoritma kompresi JPEG dengan menggunakan bahasa VHDL yang telah ada di dalam FPGA, oleh karena itu penulis melakukan percobaan dalam ”Desain Metode Pengaturan Data Baris Citra Blok 8 Pixel Untuk Implementasi Pada IC FPGA sebagai Pendukung Percepatan Operasi Perkalian QDCT Dalam Proses Kompresi Citra Jpeg” yang nantinya akan digunakan untuk mengembangkan atau menciptakan IC (perangkat keras) kompresi citra/video.

RUMUSAN MASALAH

Rumusan masalah yang diambil penulis ialah mengembangkan dari latar belakang masalah yang telah diuraikan di atas, dan dapat diperoleh perumusan masalah sebagai berikut;

a. Bagaimana mendesain rangkaian Shift

register, Counter dan D flip flop yang

merupakan proses pengaturan data input 8 blok pixel 8 bit.

b. Mengimplementasikan proses pengaturan data input 8 blok pixel 8 bit dalam kompresi citra secara real-time. c. Rancang bangun perkalian dengan

FPGA ini dibatasi oleh beberapa parameter yang dimiliki FPGA Spartan3E, diantaranya: Four Input

LUTs, Occupied Slices, Bonded IOBs, Total Equivalent Gate Count, Average Connenction delay(ns) dan Maximum Pin delay(ns) [2]

TINJAUAN PUSTAKA

Untuk memahami desain yang penulis buat, sekaligus untuk lebih mendalami apa yang akan dibahas lebih lanjut, penulis akan menjelaskan dasar-dasar pengertian yang menjadi acuan penulis dalam Desain Metode Pengaturan Data Baris Citra Blok 8 Pixel Untuk Implementasi Pada IC FPGA sebagai Pendukung Percepatan Operasi Perkalian QDCT Dalam Proses Kompresi Citra Jpeg . F PGA

Field Programmable Gate

Array (FPGA) merupakan sebuah IC digital

yang sering digunakan untuk

mengimplementasikan rangkaian digital. Bila dilihat dari segi namanya, Field Programmable dapat diartikan bahwa FPGA ini bersifat dapat dirancang sesuai dengan keinginan dan kebutuhan user/pemakai tanpa melalui tahap “burn” di laboratoruim atau di “hardwire” oleh pabrik piranti. Bayangkan, bila kita hendak memprogram chip yang isinya dapat kita tentukan sendiri dan tidak perlu susah payah memesan dari pabrik. Cukup mudah dan mengasyikan bukan??? Sedangkan Gate Array artinya bahwa FPGA ini terdiri atas

gerbang-gerbang digital dimana interkoneksi masing-masing gerbang tersebut dapat dikonfigurasikan antara satu sama lainnya. [3]

Berikut isi dari FPGA pada umumnya: 1. Configure Logic Blocks (CLB). Bisa

dikatakan, bagian inilah yang akan memproses segala bentuk rangkaian logika yang dibuat oleh user/pemakai.

2. I/O Blocks. Sebagai interface antara external pin dari device dan internal user logic

3. Programmable Interconnect. Bagian ini berisi wire segments dan programmable switches, selain itu bagian ini juga akan menghubungkan antara CLB satu dengan CLB lainnya.

Sebagian besar FPGA memiliki arsitektur seperti di atas. Entah itu FPGA produksi Xilinx ataupun dari Altera. Bila berbeda pun tak akan sampai menimbulkan perbedaan yang terlalu signifikan.

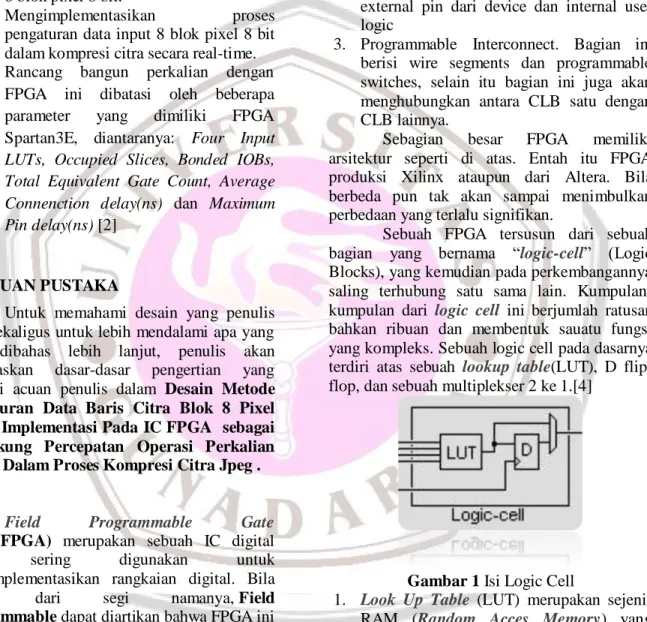

Sebuah FPGA tersusun dari sebuah bagian yang bernama “logic-cell” (Logic

Blocks), yang kemudian pada perkembangannya saling terhubung satu sama lain. Kumpulan-kumpulan dari logic cell ini berjumlah ratusan bahkan ribuan dan membentuk sauatu fungsi yang kompleks. Sebuah logic cell pada dasarnya terdiri atas sebuah lookup table(LUT), D flip-flop, dan sebuah multiplekser 2 ke 1.[4]

Gambar 1 Isi Logic Cell

1. Look Up Table (LUT) merupakan sejenis RAM (Random Acces Memory) yang berkapasitas kecil. Di dalam FPGA, LUT ini memegang peranan penting dalam proses implementasi fungsi-fungsi logika. Selain itu, LUT ini berciri khas memiliki input sejumlah 4 buah.

2. D Flip Flop. Seperti yang diketahui, flip-flop (Bistable Multivibrator) dalah suatu rangkaian sel biner yang memiliki dua buah

output yang saling berkebalikan keadaannya (0 atau 1). Di dalam FPGA, terdapat sebuah jenis flop yaitu D flop atau Data flip flop. Rangkaian D flip-flop ini berfungsi sebagai rangkaian logika sekuensial dimana di dalamnya terdapat peralatan memori dan pewaktu.

3. Multiplekser 2 ke 1. Sebuah multipleser adalah piranti digital yang bekerja sebagai switch (saklar) yang menghubungkan data dari n masukkan ke sebuah keluaran. Multiplekser berfungsi untuk memilih beberapa input untuk hanya menjadi 1 output saja. Di dalam FPGA, terdapat rangkaian multiplekser 2 ke 1 yang artinya, multiplekser tersebut memiliki 2 buah input dan 1 buah output.

Setiap logic cell tersebut dapat dihubungkan dengan logic cell lainnya melalui jalur/koneksi yang ada. Setiap cell hanya mampu bekerja secara sederhana dan ringkas, Namun bila antara satu cell saling terhubung satu sama lain sebuah fungsi-fungsi logika yang kompleks pun dapat terbentuk[5].

D-Flip-Flop

FD adalah D flip-flop dengan input data (D) dan data output (Q). Data pada D input dimuat ke flip-flop selama transisi clock dari Rendah (0) ke Tinggi (1).[6]

Gambar 2 Diagram blok D-Flip-Flop

Gambar 3 Rangkaian D-Flip-Flop

Tabel 1 Tabel Kebenaran D-Flip-Flop

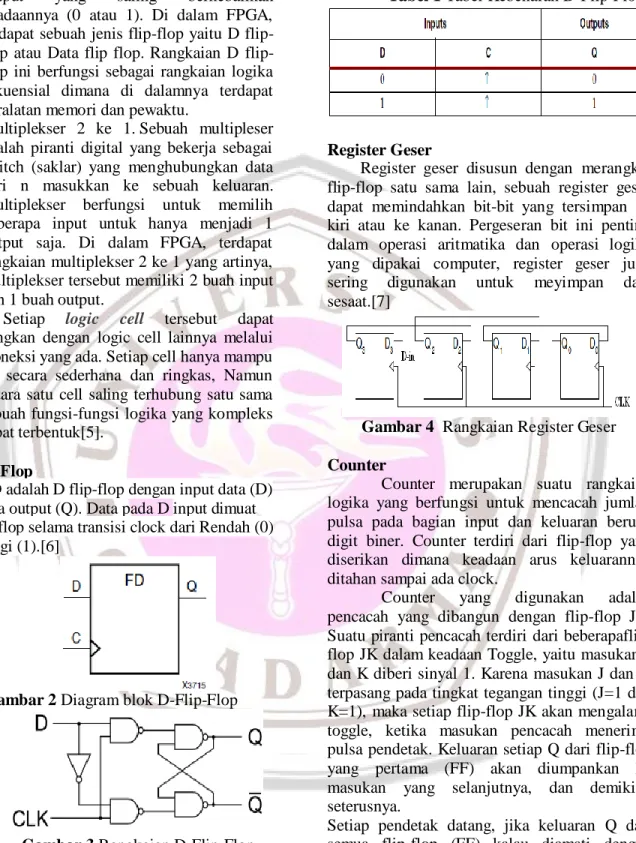

Register Geser

Register geser disusun dengan merangkai flip-flop satu sama lain, sebuah register geser dapat memindahkan bit-bit yang tersimpan ke kiri atau ke kanan. Pergeseran bit ini penting dalam operasi aritmatika dan operasi logika yang dipakai computer, register geser juda sering digunakan untuk meyimpan data sesaat.[7]

Gambar 4 Rangkaian Register Geser Counter

Counter merupakan suatu rangkaian logika yang berfungsi untuk mencacah jumlah pulsa pada bagian input dan keluaran berupa digit biner. Counter terdiri dari flip-flop yang diserikan dimana keadaan arus keluarannya ditahan sampai ada clock.

Counter yang digunakan adalah pencacah yang dibangun dengan flip-flop JK. Suatu piranti pencacah terdiri dari beberapaflip-flop JK dalam keadaan Toggle, yaitu masukan J dan K diberi sinyal 1. Karena masukan J dan K terpasang pada tingkat tegangan tinggi (J=1 dan K=1), maka setiap flip-flop JK akan mengalami toggle, ketika masukan pencacah menerima pulsa pendetak. Keluaran setiap Q dari flip-flop yang pertama (FF) akan diumpankan ke masukan yang selanjutnya, dan demikian seterusnya.

Setiap pendetak datang, jika keluaran Q dari semua flip-flop (FF) kalau diamati dengan cermat akan kita lihat adanya suatu aturan tertentu, yaitu aturan sistem bilangan biner. Jadi secara tidak langsung piranti digital ini telah melaksanankan suatu proses perhitungan biner yang disebut dengan pencacah bilangan biner.[8]

Gambar 5 Rangkaian counter Tabel 2 Tabel kebenaran Counter

(pencacah) Pencacah Q2 Q1 Q0 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1

Perangkat Lunak Yang Berhubungan Dengan Perancangan FPGA

Penggunaan perangkat lunak dalam suatu perancangan sistem elektronis bertujuan untuk memperoleh efisiensi dalam hal sintesis dan optimalisasi rancangan. Karakter suatu rancangan dapat diketahui sebelum diimplementasikan dalam bentuk perangkat keras sehingga memudahkan untuk melakukan perbaikan terhadap rancangan tersebut. Berdasarkan pedoman yang didokumentasikan oleh Xilinx, rancangan suatu sistem digital yang akan diimplementasikan dalam bentuk perangkat keras menggunakan FPGA dibuat melalui beberapa tahap sebagai berikut.

1. Pembuatan desain (Design Entry), yaitu proses pembuatan rangkaian yang akan diimplementasikan menggunakan FPGA. 2. Verifikasi desain (Design Verification),

yaitu memerikasa desain yang telah dibuat dengan cara simulasi.

3. Pemetaan, penempatan dan routing desain (Mapping, placing and routing), yaitu pemetaan gerbang, penempatan pin dan routing pembuatan jalur jalur koneksi desain ke dalam FPGA.

4. Implementasi desain (Design

Imlementation), yaitu mengimplementasikan rancangan dalam bentuk perangakat keras.

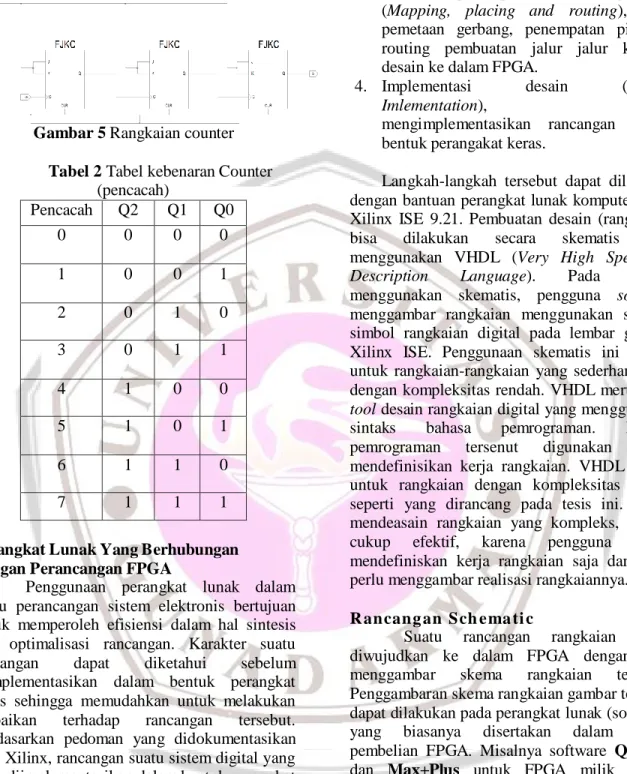

Langkah-langkah tersebut dapat dilakukan dengan bantuan perangkat lunak komputer yaitu Xilinx ISE 9.21. Pembuatan desain (rangkaian) bisa dilakukan secara skematis atau menggunakan VHDL (Very High Speed IC

Description Language). Pada desain menggunakan skematis, pengguna software menggambar rangkaian menggunakan simbol-simbol rangkaian digital pada lembar gambar Xilinx ISE. Penggunaan skematis ini efisien untuk rangkaian-rangkaian yang sederhana atau dengan kompleksitas rendah. VHDL merupakan

tool desain rangkaian digital yang menggunakan

sintaks bahasa pemrograman. Bahasa pemrograman tersenut digunakan untuk mendefinisikan kerja rangkaian. VHDL sesuai untuk rangkaian dengan kompleksitas tinggi, seperti yang dirancang pada tesis ini. Untuk mendeasain rangkaian yang kompleks, VHDL cukup efektif, karena pengguna cukup mendefiniskan kerja rangkaian saja dan tidak perlu menggambar realisasi rangkaiannya. R ancang an Sch e ma ti c

Suatu rancangan rangkaian dapat diwujudkan ke dalam FPGA dengan cara menggambar skema rangkaian tersebut. Penggambaran skema rangkaian gambar tersebut dapat dilakukan pada perangkat lunak (software) yang biasanya disertakan dalam setiap pembelian FPGA. Misalnya software Quartus dan Max+Plus untuk FPGA milik Altera. Sedangkan FPGA buatan Xilinx dengan perangkat lunaknya yakni ISE WebPack. Selanjutnya, skema rangkaian digambar dengan cara membuat tiap komponen serta jalur-jalur yang menghubungkan komponen-komponen tersebut menjadi satu kesatuan. Hingga akhirnya tercipta gambar skema rangkaian yang utuh. Metode ini terbilang mudah dan efektif terutama bila dipakai untuk skema rangkaian yang

sederhana serta tidak memiliki jalur-jalur yang rumit.[6]

Gambar 6 Rangkaian yang dibuat dengan Metode Schematic

Skema desain schematic merupakan seperangkat sistem yang memungkinkan Anda untuk menangkap struktur desain baik sebagai deskripsi datar atau hirarkis seperangkat komponen, dan konektivitas antara komponen-komponen ini. Kemudian Anda dapat menggunakan deskripsi ini untuk mendorong pelaksanaan dan verifikasi alat. Anda membuat desain skematis menggunakan Schematic Editor. Schematics dapat single-level (flat) atau multi-tingkat (hirarkis). Schematics dapat ditarik pada beberapa "lembar" dan ukuran apapun.

PEMBAHASAN Metode Penelitian Bahan Penelitian

Bahan penelitian terdiri atas :

a. FPGA Spartan-3E starter board

Keping XC3S500E mempunyai 500.000 gerbang dengan jumlah CLB sebesar 1164, IOB sebesar 232 pengali sebanyak 20 unit, dan interkoneksi yang dapat diprogram. Alat Penelitian

a. Satu set komputer Pentium® Dual-Core CPU E5200 @2.50GHz(2 CPUs), ~2.5GHz.

b. Satu perangkat lunak Sistem Operasi Windows XP.

c. Satu perangkat lunak Xilinx ISE 9.2i. Pelaksanaan penelitian dimulai dengan merancang gambaran skematik yang terbagi atas beberapa bagian rangkaian. Beberapa bagian

rangkaian yang dirancang akan dihubungkan dengan metode skematik pada perangkat lunak Xilinx ISE 9.2i.

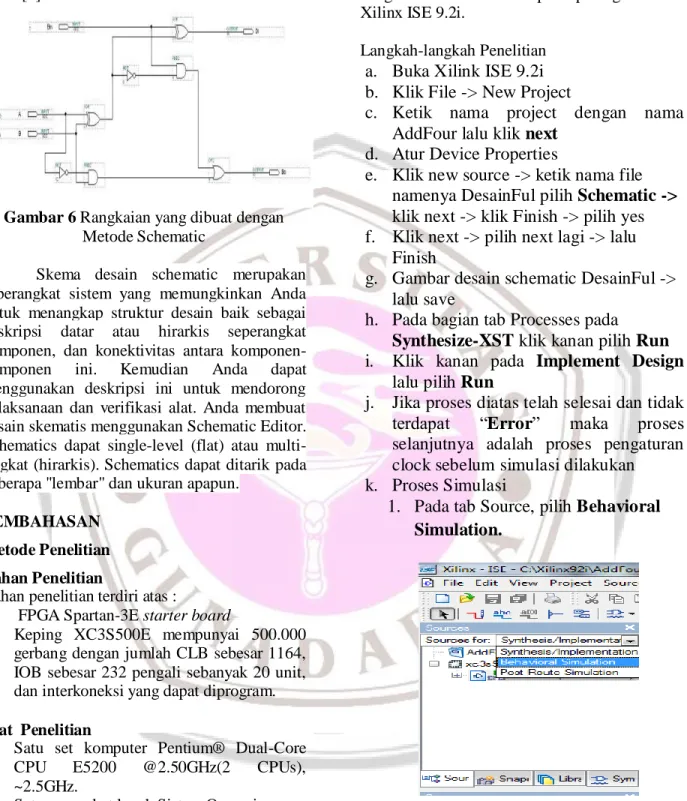

Langkah-langkah Penelitian

a. Buka Xilink ISE 9.2i

b. Klik File -> New Project

c. Ketik nama project dengan nama

AddFour lalu klik next

d. Atur Device Properties

e. Klik new source -> ketik nama file

namenya DesainFul pilih Schematic ->

klik next -> klik Finish -> pilih yes

f. Klik next -> pilih next lagi -> lalu

Finish

g. Gambar desain schematic DesainFul ->

lalu save

h. Pada bagian tab Processes pada

Synthesize-XST klik kanan pilih Run

i. Klik kanan pada Implement Design

lalu pilih Run

j. Jika proses diatas telah selesai dan tidak

terdapat

“Error”

maka

proses

selanjutnya adalah proses pengaturan

clock sebelum simulasi dilakukan

k. Proses Simulasi

1. Pada tab Source, pilih Behavioral

Simulation.

2. Kemudian pilih Create new Source

3. Kemudian ketik nama source, pilih

Test Bench WaveForm klik Next,

Next lagi, lalu Finish.

4. Lalu ikuti perintah seperti dibawah,

lalu klik Finish:

5. Pada langkah terakhir ini merupakan

simulasi rangkaian dengan

memasukan nilai inputan dan nilai

Load, lalu Save :

6. Setelah memasukan nilai inputan,

maka source yang kita bikin akan

muncul, lalu klik kanan pada

Simulate Behavioral Model pilih

Run, setelah itu akan tampil hasil

simulasi.

Modul perancangan Pembagian data 8 Blok Pixel

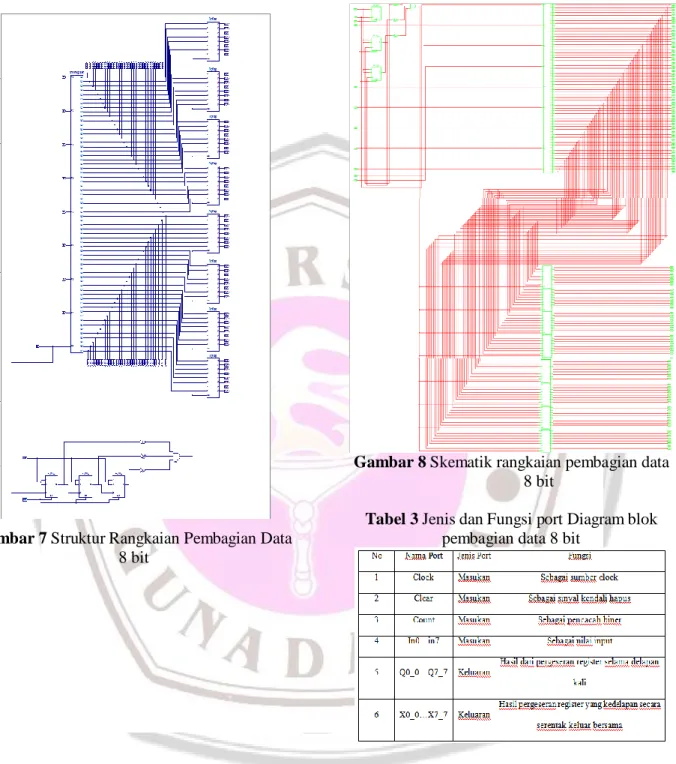

Gambar 7 Struktur Rangkaian Pembagian Data 8 bit

Skematik rangkaian pembagian data 8 bit

Gambar 8 Skematik rangkaian pembagian data 8 bit

Tabel 3 Jenis dan Fungsi port Diagram blok pembagian data 8 bit

Dalam masing-masing perancangan pembagian data ini terdiri dari beberapa unit yaitu Shift Register 8 bit, Counter, D Filp-Flop 8 bit, tiap-tiap blok rangkaian mempuyai fungsi masing-masing.

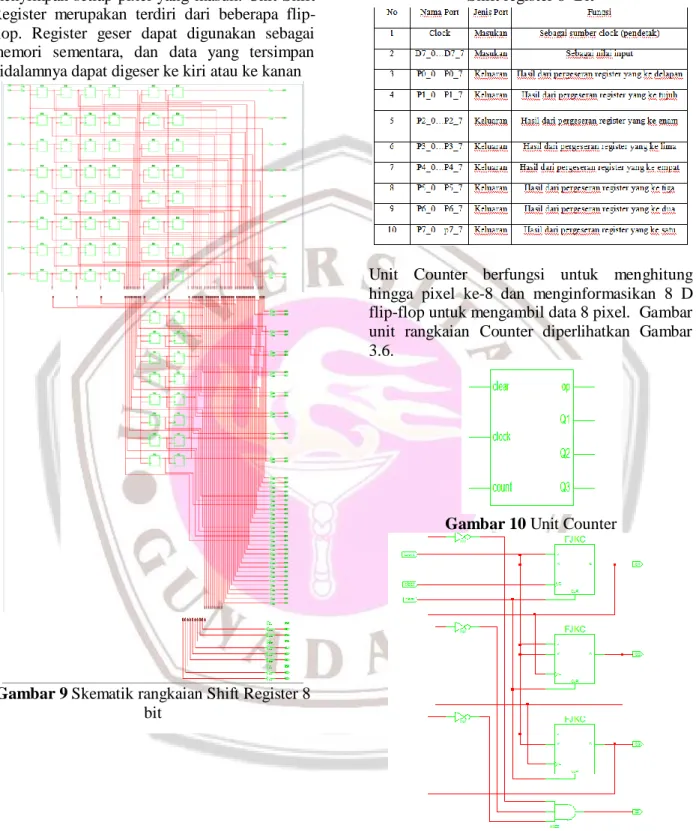

Unit Register Geser berfungsi untuk menggeser data partial produk dan menyimpannya, data yang digeser lebih banyak dari 1 bit berupa data 0 atau 1. Unit shift register berfungsi sebagai

memvalidasi (dengan bantuan clock) dan menyimpan setiap pixel yang masuk. Unit Shift Register merupakan terdiri dari beberapa flip-flop. Register geser dapat digunakan sebagai memori sementara, dan data yang tersimpan didalamnya dapat digeser ke kiri atau ke kanan

Gambar 9 Skematik rangkaian Shift Register 8 bit

Tabel 4 Jenis dan Fungsi port dari rangkaian Shift register 8 Bit

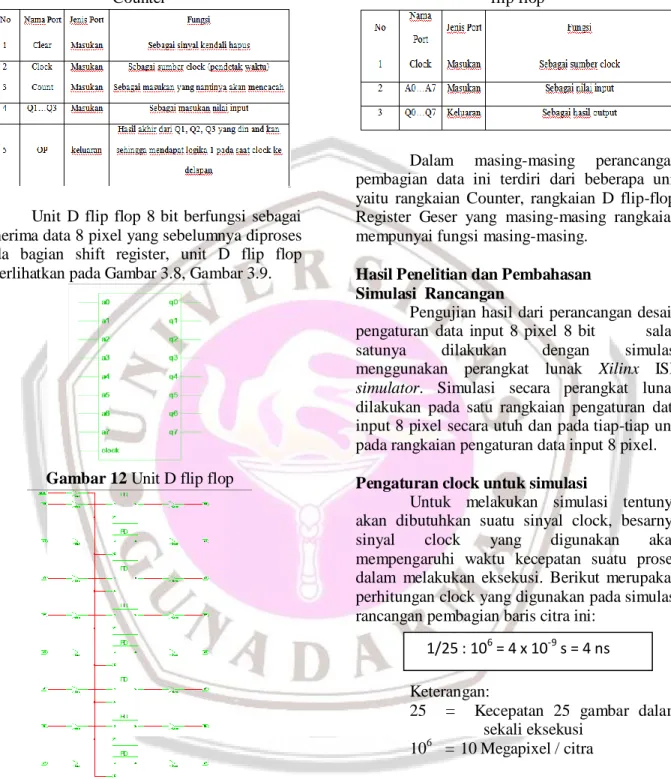

Unit Counter berfungsi untuk menghitung hingga pixel ke-8 dan menginformasikan 8 D flip-flop untuk mengambil data 8 pixel. Gambar unit rangkaian Counter diperlihatkan Gambar 3.6.

Gambar 10 Unit Counter

Table 5 Jenis dan Fungsi port dari rangkaian Counter

Unit D flip flop 8 bit berfungsi sebagai penerima data 8 pixel yang sebelumnya diproses pada bagian shift register, unit D flip flop diperlihatkan pada Gambar 3.8, Gambar 3.9.

Gambar 12 Unit D flip flop

Gambar 13 Skematik rangkaian D fli flop

Table 6 Jenis dan Fungsi port dari rangkaian D flip flop

Dalam masing-masing perancangan pembagian data ini terdiri dari beberapa unit yaitu rangkaian Counter, rangkaian D flip-flop, Register Geser yang masing-masing rangkaian mempunyai fungsi masing-masing.

Hasil Penelitian dan Pembahasan Simulasi Rancangan

Pengujian hasil dari perancangan desain pengaturan data input 8 pixel 8 bit salah satunya dilakukan dengan simulasi menggunakan perangkat lunak Xilinx ISE

simulator. Simulasi secara perangkat lunak

dilakukan pada satu rangkaian pengaturan data input 8 pixel secara utuh dan pada tiap-tiap unit pada rangkaian pengaturan data input 8 pixel. Pengaturan clock untuk simulasi

Untuk melakukan simulasi tentunya akan dibutuhkan suatu sinyal clock, besarnya sinyal clock yang digunakan akan mempengaruhi waktu kecepatan suatu proses dalam melakukan eksekusi. Berikut merupakan perhitungan clock yang digunakan pada simulasi rancangan pembagian baris citra ini:

Keterangan:

25 = Kecepatan 25 gambar dalam sekali eksekusi

106 = 10 Megapixel / citra

Simulasi Rancangan Pengaturan Data Input 8 Blok data pixel

Perancangan pengaturan data input baris citra ini terdiri dari beberapa unit yaitu Shift register 8 bit, Counter, dan D flip-flop 8 bit.

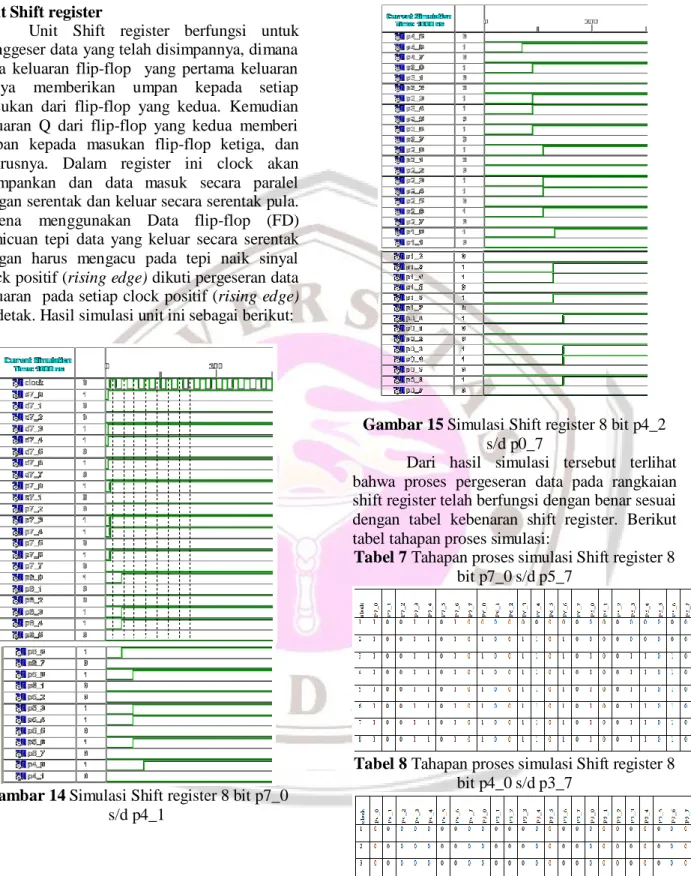

Unit Shift register

Unit Shift register berfungsi untuk menggeser data yang telah disimpannya, dimana pada keluaran flip-flop yang pertama keluaran Q-nya memberikan umpan kepada setiap masukan dari flip-flop yang kedua. Kemudian keluaran Q dari flip-flop yang kedua memberi umpan kepada masukan flip-flop ketiga, dan seterusnya. Dalam register ini clock akan diumpankan dan data masuk secara paralel dengan serentak dan keluar secara serentak pula. Karena menggunakan Data flip-flop (FD) pemicuan tepi data yang keluar secara serentak dengan harus mengacu pada tepi naik sinyal clock positif (rising edge) dikuti pergeseran data keluaran pada setiap clock positif (rising edge) berdetak. Hasil simulasi unit ini sebagai berikut:

Gambar 14 Simulasi Shift register 8 bit p7_0 s/d p4_1

Gambar 15 Simulasi Shift register 8 bit p4_2 s/d p0_7

Dari hasil simulasi tersebut terlihat bahwa proses pergeseran data pada rangkaian shift register telah berfungsi dengan benar sesuai dengan tabel kebenaran shift register. Berikut tabel tahapan proses simulasi:

Tabel 7 Tahapan proses simulasi Shift register 8 bit p7_0 s/d p5_7

Tabel 8 Tahapan proses simulasi Shift register 8 bit p4_0 s/d p3_7

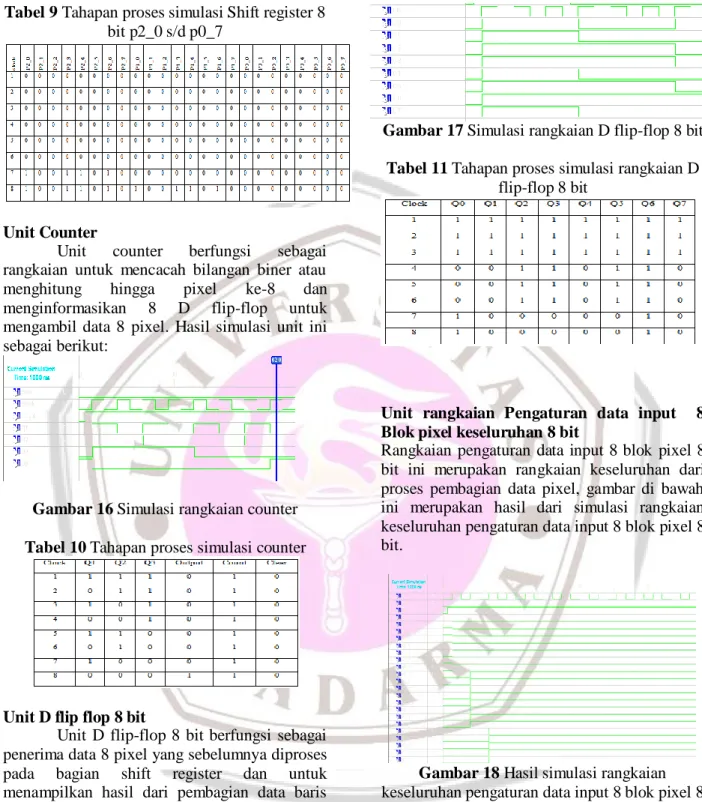

Tabel 9 Tahapan proses simulasi Shift register 8 bit p2_0 s/d p0_7

Unit Counter

Unit counter berfungsi sebagai rangkaian untuk mencacah bilangan biner atau menghitung hingga pixel ke-8 dan menginformasikan 8 D flip-flop untuk mengambil data 8 pixel. Hasil simulasi unit ini sebagai berikut:

Gambar 16 Simulasi rangkaian counter Tabel 10 Tahapan proses simulasi counter

Unit D flip flop 8 bit

Unit D flip-flop 8 bit berfungsi sebagai penerima data 8 pixel yang sebelumnya diproses pada bagian shift register dan untuk menampilkan hasil dari pembagian data baris citra secara serentak. Hasil simulasi unit ini sebagai berikut:

Gambar 17 Simulasi rangkaian D flip-flop 8 bit Tabel 11 Tahapan proses simulasi rangkaian D

flip-flop 8 bit

Unit rangkaian Pengaturan data input 8 Blok pixel keseluruhan 8 bit

Rangkaian pengaturan data input 8 blok pixel 8 bit ini merupakan rangkaian keseluruhan dari proses pembagian data pixel, gambar di bawah ini merupakan hasil dari simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8 bit.

Gambar 18 Hasil simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8

Gambar 19 Hasil simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8

bit dari x5_2 s/d x2_4

Gambar 20 Hasil simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8

bit dari x2_3 s/d x0_0

Gambar 21 Hasil simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8

bit pada q0_0 s/d q2 _6

Gambar 22 Hasil simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8

bit dari q2_7 s/d q5_5

Gambar 23 Hasil simulasi rangkaian keseluruhan pengaturan data input 8 blok pixel 8

bit dari q5_6 s/d q7_7 Disain Placed and Route

Disain placed and route ini digunakan untuk mengetahui letak – letak CLB ( Configure

Logic Blocks ) dan untuk mengetahui apakah

CLB-CLB tersebut saling terhubung atau tidak, bisa dikatakan bagian inilah yang akan memproses rangkaian – rangkaian yang telah dibentuk.

Pada bagian placed, bagian ini menampilkan bagaimana rangkaian – rangkaian ini terbentuk di dalam IC FPGA, kemudian pada bagian route bagian ini menampilkan CLB – CLB yang digunakan oleh rangkaian – rangkaian tersebut, namun pada bagian ini penulis hanya memberikan gambaran kecil pada CLB yang digunakan, untuk lebih jelas berikut adalah gambar dari disain placed and route setiap rangkaian.

Gambar 24 Disain Placed pengaturan data input 8 blok pixel 4 Bit

Gambar 25 Disain Placed pengaturan data input 8 blok pixel 4 Bit

Gambar 26 Disain Route pengaturan data input 8 blok pixel 4 Bit

Gambar 27 Disain Placed pengaturan data input 8 blok pixel 8 bit

Gambar 28 Disain Placed pengaturan data input 8 blok pixel 8 bit

Gambar 29 Disain Route pengaturan data input 8 blok pixel 8 bit

Desain dan Implementasi pada FPGA

Desain dari rangkaian Shift register, Counter, dan D flip-flop 4x4 dan 8x8 telah diselesaikan dengan menggunakan VHDL dan implementasi dalam Xilinx Spartan-3E (package :FG320, speed :-4), dalam proses pembuatan desain ini menggunakan Design tool Xilinx ISE 9.2i . Berikut Tabel Pemanfaatan sumber daya untuk Spartan-3E pada desain dan implementasi pengaturan data input 8 blok pixel ini:

PENUTUP Kesimpulan

Dalam mendesain rangkaian pengaturan data input 8 blok pixel 8 bit ini yang nantinya akan diproses dalam suatu kompresi citra lalu di implementasikan ke dalam ic FPGA merupakan salah satu bagian dari rangkaian keseluruhan kompresi citra dimana bagian ini merupakan proses input atau proses pembagian data 8 blok pixel. Rangkaian ini telah di desain sesuai dengan fungsi dan tujuannya dengan baik untuk melakukan proses input dan pembagian data 8 blok pixel.

Rangkaian desain ini dibagi menjadi tiga unit yaitu unit shift register yang memiliki fungsi sebagai input data dan untuk memvalidasi (dengan bantuan clock) dan menyimpan setiap pixel yang masuk. Lalu ada rangkaian unit counter yang berfungsi sebagai penghitung hingga pixel ke-8 dan menginformasikan 8 D flip-flop untuk mengambil data 8 pixel. Sedangkan rangkaian unit D flip flop melakukan pengambilan data yang telah dip roses oleh shift register dengan bantuan counter dan menampilkan hasil proses tersebut secara serentak.

Desain dan perancangan proses pengaturan data input 8 pixel 8 bit lebih efektif dibandingkan proses pengaturan data input 8 pixel baik untuk 4 bit dan 6 bit dilihat dari sumber daya yang digunakan dengan parameter

Four Input LUTs, Occupied Slices, CLB, Bonded IOBs, Total Equivalent Gate Count, Average Connenction delay(ns) dan Maximum Pin delay(ns).

Tujuan dari keseluruhan desain rangkaian ini adalah membagi 8 blok data secara bertahap pada rangkaian yang telah di desain dan menghasilkan data yang diinginkan user untuk nantinya akan di masukkan ke dalam proses kompresi citra.

Saran

Dari hasil perancangan dan desain rangkaian pengaturan data input 8 blok pixel 8 bit ini, diberikan beberapa saran kepada pembaca yaitu:

1. Desain rangkaian ini nantinya akan digabungkan dengan blok-blok desain selanjutnya yang akan secara utuh melakukan suatu proses kompresi citra. 2. Desain rangkaian ini bisa di

implementasikan ke dalam ic FPGA yang sesuai dengan tipenya seperti video dan gambar.

3. Desain rangkaian ini bisa di kembangkan lagi dengan rangkaian-rangkaian yang lebih spesifik jika inginmenambahkan suatu kondisi lagi.

Tabel 17 Pemanfaatan sumber daya untuk pengaturan data input 8 blok pixel untuk Spartan-3E Lebar Bit Rangkaian Four Input

LUTs {9312} Occupied Slices {4656} Bonded IOBs {232} Total Equivalent Gate Count Average Connection delay (ns)

Maximum Pin delay

(ns)

D flip flop 0 0 17 67 0.161 816

Counter 4 3 4 51 1.122 192

Rangkaian 4 bit 4 27 75 5.66 1.176 4.656

DAFTAR PUSTAKA

[1] http://www.springer.com/computer/image+processing/journal/11554 Journal of

Real-Time Image Processing.

[2] http://te.ugm.ac.id/~enas/tesis260199.pdf

[3] http://repository.usu.ac.id/bitstream/123456789/16876/.../Chapter%20II.pdf

[4] Asisten FPGA, “Modul Panduan FPGA”, Laboratorium Lanjut Universitas Gunadarma, Depok, 2010

[5] http://www.scribd.com/doc/38151138/Field-Programmable-Gate-Array

[6] http://materikuliah.info/artikel/mipa/teori-dasar-rangkaian-flip-flop-ff.aspx / 15 April 2010 [7] Widjanarka N,IR.Wijaya.2006.Teknik Digital.Jakarta,Erlangga.