PERBANDINGAN PEMODELAN LEVEL TRANSAKSI

DAN LEVEL REGISTER TRANSFER

PADA PERANCANGAN HARDWARE EMBEDDED SYSTEM

Maman Abdurohman1, Kuspriyanto2, Sarwono Sutikno3, Arif Sasongko41Fakultas Informatika, Institut Teknologi Telkom

1,2,3,4Sekolah Teknik Elektro dan Informatika, Institut Teknologi Bandung

1m_abdurohman@yahoo.com, 2kuspriyanto@gmail.com, 3sarwono@gmail.com, 4sasongko@gmail.com

Abstrak

Peningkatan kinerja pemodelan pada perancangan embedded system merupakan salah satu tantangan dalam mengikuti perkembangan teknologi IC dan kebutuhan pasar. Perancangan yang lebih baik akan meningkatkan produktivitas perancangan dan memenuhi kebutuhan pasar. Pendekatan perancangan Embedded System yang saat ini digunakan adalah pemodelan pada level Register Transfer Level (RTL). Pada pemodelan RTL satuan komponen rancangan adalah register. Perancangan level RTL tidak dapat lagi memenuhi kompleksitas proses perancangan embedded system. Diperlukan suatu metode perancangan baru dengan abstraksi yang lebih tinggi dari RTL. Metode perancangan baru untuk meningkatkan kinerja proses perancangan adalah pemodelan level transaksi (TLM). Makalah ini membahas perbandingan perancangan hardware embedded system dengan menggunakan metode TLM dan RTL dengan menggunakan bahasa SystemC untuk memprogram aplikasinya. Hasil penelitian menunjukan bahwa pemodelan dengan metode TLM memiliki kinerja yang lebih baik dibandingkan dengan pemodelan level RTL.

Kata Kunci: Transaction Level Modeling (TLM), SystemC, Register Transfer Level (RTL). Abstract

Performance modeling enhancement on embedded system design is one of many challenges to face the growing of IC techonology and market necesity. Better modeling will incresae the productifity of modeling and accomplish the market necesity. The existing embedded system design approach is RTL level modeling. On RTL modeling, register is the design component. RTL design approach is lack of facing the complexity design process of embedded system. So, we need the new design method with higher abstraction layer more than RTL. The method that will increase performance of embedded system design process is transaction level modeling (TLM). In this paper we compared two embdedded system hardware design using TLM and RTL method. We use SystemC language to program both TLM and RTL application. The result shows that TLM method has better performance than RTL modeling.

Keywords: Transaction Level Modeling (TLM), SystemC, Register Transfer Level (RTL). 1. Pendahuluan

Salah satu tantangan dalam pengembangan perangkat embedded system adalah peningkatan metode perancangan. Perkembangan teknologi IC yang semakin cepat, mengacu pada hukum Moore, dan kebutuhan pasar, mendorong para perancang untuk mencari metode perancangan baru yang lebih fleksibel dan lebih baik. Saat ini perancangan embedded system mengacu pada level perancangan RTL (Register Transfer Level). Pada model perancangan RTL satuan terkecil rancangannya adalah register. Model perancangan RTL merupakan perbaikan dari proses perancangan sebelumnya yaitu perancangan level gerbang.

Pada perancangan RTL satuan komponen perancangan adalah komponen yang di dalamnya terdapat komponen register seperti register file, ALU, memori, dan prosesor. Bahasa yang banyak digunakan pada pemodelan level RTL adalah VHDL dan Verilog. Keduanya populer digunakan oleh para perancang embedded system.

Gambar 1. Peningkatan Kapasitas IC Sampai Tahun 2005 [5]

Perkembangan teknologi IC yang saat ini terus berlanjut dan tekanan waktu pasar menjadi tantangan baru dalam perancangan embedded system. Sampai tahun 2005 (Gambar 1) tingkat kemampatan (density) IC mencapai lebih dari 1

miliar transistor per chip [10]. Peningkatan teknologi IC yang tidak diimbangi dengan peningkatan metode perancangan menyebabkan celah produktivitas perancang. Secara empiris, kemampuan sumber daya teknologi banyak yang tidak termanfaatkan dengan optimal salah satunya karena lambannya proses perancangan embedded system.

Tekanan waktu pasar adalah rentang waktu yang diperlukan untuk memasuki pasar produk embedded system. Saat ini persaingan antar vendor semakin ketat. Ide bukanlah hal yang terlalu sulit dibandingkan dengan mewujudkannya. Semakin cepat suatu vendor memasuki pasar maka peluang mendapatkan keuntungan semakin besar. Kecepatan memasuki pasar adalah tergantung dari proses perancangan dan waktu pembuatan prototype produk. Kedua hal tersebut menjadikan produk embedded system semakin komplek dan menuntut fleksibilitas dari sisi pengembangan software dan hardware.

Perancangan level RTL terlalu lamban untuk mengatasi kompleksitas dan fleksibilitas rancangan. Terdapat tujuh tahap dalam perancangan ES yaitu spesifikasi produk, pemisahan HW/SW, implementasi, perancangan HW/SW rinci, integrasi HW/SW, pengujian, dan pemeliharan [1].

Diperlukan metode perancangan baru yang dapat mengakomodasi kebutuhan tersebut. Metode dengan abstraksi yang lebih tinggi dari RTL yang dapat mengatasi kerumitan perancangan.

Beberapa konsep perancangan Embedded System yang dirancang oleh para peneliti adalah Cosyma [7], System-Level Cosynthesis [3], IP Reuse [8], Hardware Software codesign [9] dan Electronic System Level [11].

Salah satu metode perancangan dengan abstraksi level rancangan yang lebih tinggi dari RTL adalah dengan pendekatan pemodelan level transaksi, Transaction Level Modeling (TLM).

Pemodelan TLM berbeda dengan RTL dalam hal pemodelan interaksi antar komponen. Pada pemodelan TLM komunikasi antar komponen dipisahkan dengan komputasi komponen. Komunikasi antar komponen dilakukan dengan menggunakan suatu metode transaksi dengan memperlakukan proses transaksi sebagai pemanggilan fungsi.

2. Pemodelan Embedded System

Embedded system adalah sebuah sistem yang

terdiri dari hardware dan software yang dibuat dengan tujuan khusus yang biasanya ditanamkan pada sistem lain yang lebih besar. Dalam pembuatan suatu embedded system terdapat dua tahapan utama yaitu proses perancangan dan implementasi. Perancangan embedded system yang saat ini digunakan adalah perancangan level RTL. Perbaikan terhadap perancangan ini adalah dengan peningkatan abstraksi perancangan dengan pendekatan level

TLM. Pada bagian ini akan dibahas kedua pendekatan pemodelan tersebut.

2.1 Pemodelan Register Transfer Level (RTL) Level register adalah abstraksi perangkat keras dengan satuan komponen terkecilnya adalah register. Register adalah komponen komputasi yang dibangun dari sekumpulan gerbang dasar dan flip-flop. Contoh komponen level ini adalah adder, multiplexer, decoder, dan memori.

Usaha untuk meningkatkan kualitas perancangan telah dilakukan yaitu dengan meningkatkan level abstraksi perancangan dari level gerbang ke level transfer register, Register Transfer Level (RTL). Langkah ini sebenarnya termasuk langkah yang signifikan dan ada yang menyebutnya sebagai revolusi teknologi [12] bagi peningkatan produktivitas perancang. Perancang tidak perlu merancang pada level gerbang. Perancangan dimulai dengan mendefenisikan komponen-komponon diatas gerbang yaitu register. Berikut ini contoh rancangan ADDER dengan model RTL:

entity ADDER is generic(n: natural :=2);

port(A: in std_logic_vector(n-1 downto 0); B : in std_logic_vector(n-1 downto 0); carry: out std_logic;

sum: out std_logic_vector(n-1 downto 0) ); end ADDER;

architecture behv of ADDER is

signal result: std_logic_vector(n downto 0);

begin

result <= ('0' & A)+('0' & B); sum <= result(n-1 downto 0); carry <= result(n);

end behv;

Terdapat dua buah bahasa perancangan level RTL yang dikenal luas dan telah ditetapkan menjadi standar oleh IEEE, yaitu Verilog dan VHDL. Keduanya, secara de facto, dianggap sebagai bahasa perancangan perangkat keras, Hardware Description Language (HDL). Pada awalnya, kedua bahasa ini adalah alat yang digunakan untuk menyimpan notasi hasil rancangan, bukan bahasa pemrograman umumnya. Para perancang yang telah membuat rancangan rangkaian menemukan kendala cara menyimpan hasil rancangannya. Dengan adanya HDL, maka perancang dapat menyimpan notasi rangkaian dalam bentuk kode program. Hasil rancangan yang telah dibuat sering diistilahkan sebagai kekayaan intelektual, Intelectual Property (IP).

2.2 Pemodelan Transaction Level Modeling (TLM)

Metodologi untuk memodelkan perangkat keras saat ini terus dikembangkan dengan meningkatkan level abstraksi perancangan. Pada

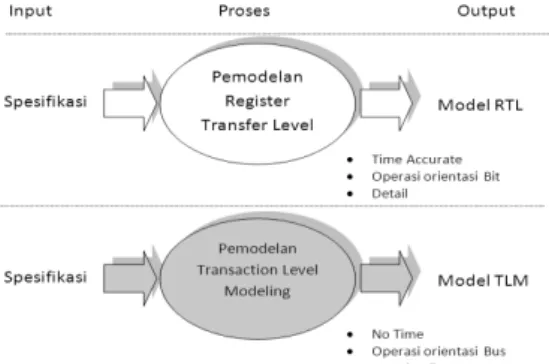

Gambar 2. Perbandingan Proses TLM dan RTL pemodelan level transaksi tidak dilakukan pendefinisian sinyal secara tunggal melainkan sekumpulan sinyal yang beroperasi pada tipe data abstrak, yang dapat meningkatkan kecepatan waktu simulasi. Dengan cara ini proses simulasi pada level transaksi jauh lebih cepat dibandingkan dengan pemodelan level RTL (Gambar 2).

Level Transaksi adalah suatu abstraksi pemodelan yang menjembatani antara pemodelan Register Transfer Level (RTL) dengan penjelasan fungsionalitas sistem [4].

Konsep utama yang diperkenalkan oleh TLM adalah pemisahan komunikasi antar komponen dengan proses yang ada dalam komponen tersebut. Komunikasi dimodelkan sebagai channel yang dirancang sebagai satu abstraksi tingkat tinggi yang tidak menunjukan secara rinci proses yang ada di dalamnya. Dengan cara ini, TLM dapat meningkatkan kecepatan dalam proses simulasi perancangan.

Pemodelan TLM dapat menghilangkan rincian waktu dan cycle. Dengan mengabaikan rincian waktu, fungsi-fungsi yang didefinisikan pada level yang lebih atas memungkinkan pemodelan yang lebih cepat. Meskipun tidak terlalu rinci, fungsional sistem tetap dipertahankan sesuai dengan spesifikasi awal rancangan.

3. Perancangan dan Implementasi Aplikasi TLM dan RTL

Aplikasi yang dirancang pada bagian ini melibatkan beberapa buah komponen komunikasi yang saling berinteraksi (Gambar 3). Komponen dibedakan menjadi dua jenis yaitu master dan slave. Master adalah komponen yang memiliki inisiatif untuk berkomunikasi dengan komponen lain sementara slave adalah komponen yang melayani transaksi dari master. Contoh komponen master adalah prosesor dan digital signal processor, sementara slave seperti RAM dan ROM.

3.1 Kebutuhan Perangkat Keras dan Perangkat Lunak

Perangkat keras yang digunakan pada penelitian ini memiliki karakteristik sebagai berikut: CPU Intel Pentium 4 2,80 GHz, RAM 512 MB, dan HD 40 GB. Producer (Master) Consumer (Slave) Producer (Master) Consumer (Slave)

Fifo Channel Model TLM

Model RTL Data Enable Ack Producer (Master) ready Consumer

(Slave) Model RTLRinci

Gambar 3. Model TLM dan RTL 2-tiers Perangkat lunak yang diperlukan dalam perancangan sistem adalah: Cygwin 2 (www.cygwin.com), SystemC-2.2.0 (www.osci.org), Java (jdk-6u4-windows-i586-p dan jre-6u3-windows-i586-p-s) dan Netbeans IDE 6.1.

Aplikasi TLM dan RTL yang akan dibangun menggunakan bahasa pemodelan SystemC yang dijalankan di atas IDE Netbeans 6.1. Bahasa SystemC merupakan bahasa yang cocok digunakan untuk pemodelan level transaksi [2]. SystemC-2.2.0 adalah Library C++ untuk perancangan perangkat keras [6].

3.2 Skenario Pengujian

Pengujian dilakukan untuk mengukur peningkatan kinerja pada perancangan. dengan menggunakan alur perancangan baru Pemodelan Level Transaksi (TLM) dibandingkan dengan pemodelan Level Register Transfer (RTL). Pada pengujian ini akan dilakukan beberapa skenario.

Dalam pengujian ini dibuat model TLM dan RTL untuk satu fungsi tertentu yang melibatkan beberapa master dan slave. Pengukuran dilakukan dengan dibandingkan waktu proses yang diperlukan untuk membuat kedua model tersebut.

Pengukuran waktu proses dilakukan dengan membandingkan jumlah line code kedua buah model yang masing-masing telah distandarisasi. Untuk menghindarkan deviasi yang terlalu lebar yang mungkin disebabkan oleh tingkat keahlian perancang maka proses yang diujikan adalah proses standar komunikasi master dengan slave yaitu proses read() dan write().

Aplikasi yang dibuat terdiri dari beberapa skenario uji yaitu:

a. Pengujian model TLM-RTL 2-tiers: melibatkan 1 buah master dan 1 buah slave dengan menggunakan sebuah bus TLM dan RTL. b. Pengujian model TLM-RTL 3-tiers: melibatkan

1 buah master, 1 buah slave, dan 1 buah arbiter. Arbiter dianggap sebagai salah satu komponen yang berfungsi dalam mengendalikan bus TLM dan RTL.

c. Pengujian model TLM-RTL 4-tiers: melibatkan 2 buah master, 1 buah slave dan 1 buah arbiter. d. Pengujian model TLM-RTL 5-tiers: melibatkan

3.3 Transformasi model TLM-RTL

Proses transformasi model TLM ke RTL adalah proses sistematis dengan melakukan peruahan cara komunikasi komponen yaitu dengan meningkatkan kerincian komunikasi. Diperlukan sebuah standar bus untuk komunikasi antar komponan. Bus yang digunakan pada transformasi ini adalah sistem bus Avalon.

Bus Avalon adalah jenis Bus SoC (System on Chip) yang dikembangkan oleh Altera (www.altera.com). Bus ini dirancang untuk aplikasi berbasis chip. SoC adalah sebuah sistem kompak yang di dalamnya terdapat tiga komponen utama yaitu komponen master yang aktif, komponen slave yang pasif dan sistem bus.

Bus Avalon digunakan pada tahap implemen-tasi pada level RTL. Pada Bus Avalon terdapat 5 buah komponen utama dengan masing-masing fungsi sebagai: master, slave, request logic, arbitrator logic, dan multiplexer.

4. Analisis Perbandingan Pemodelan TLM dan RTL

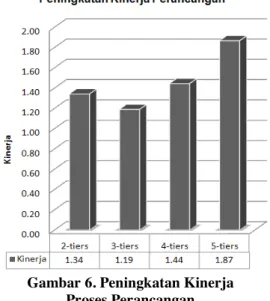

Analisis dilakukan terhadap hasil pengukuran data yang dihasilkan dalam percobaan. Pengukuran dilakukan untuk menentukan peningkatan kinerja proses perancangan TLM dibandingkan dengan RTL. Peningkatan kinerja TLM dibandingkan RTL berdasarkan waktu proses perancangan kedua pemodelan tersebut. Semakin tinggi peningkatan kinerja TLM dibandingkan RTL artinya pemodelan dengan TLM semakin efesien dan memerlukan waktu yang lebih sedikit dibandingkan dengan RTL dengan hasil yang sama.

4.1 Pengukuran Berdasarkan Baris Kode Gambar 4 menunjukkan data hasil pengukuran terhadap model TLM dan RTL untuk skenario 1 – 4. Berdasarkan data tersebut terlihat bahwa lebih sedikit jumlah baris yang diperlukan untuk memodelkan sistem dengan menggunakan TLM dibandingkan dengan RTL. Kondisi ini dapat terjadi kerana pendefinisian master, slave, dan bus pada RTL lebih rinci dibandingkan dengan TLM.

Tingkat kerincian pemodelan pada RTL mempengaruhi beberapa bagian program yaitu: a. Definisi port pada masing-masing komponen

master dan slave.

b. Definisi awal pada top level sistem yaitu menambahkan port, instantiasi, pemetaan port, dan destruksi.

c. Definisi komponen baru yaitu multiplexer. Pada bus Avalon setiap penambahan slave maka harus menambahkan 6 buah multiplexer baru.

Pada TLM proses definisi komponen dan pemetaan port lebih sederhana dibandingkan dengan RTL sehingga tidak memerlukan instruksi yang banyak seperti RTL. Pemetaan port baru pada saat

terjadi penambahan master adalah pemetaan dengan bus dan clock.

4.2 Pengukuran Berdasar Waktu Perancangan Waktu perancangan adalah waktu yang diperlukan oleh pemrogram untuk pembuatan kode dan laporannya. Standar yang digunakan adalah 8 baris kode dan laporan per-man-day. Waktu perancangan dapat diturunkan langsung dari jumlah kode pemodelan untuk masing-masing pemodelan TLM dan RTL. Gambar 5 menunjukkan hasil perbandingan waktu yang diperlukan untuk merancang untuk keempat skenario pengujian. 4.3 Pengukuran kinerja proses perancangan

Kinerja adalah salah satu parameter penting untuk mengukur keberhasilan sebuah metode baru. Pada disertasi ini kinerja proses perancangan diukur berdasarkan perbandingan antara waktu proses perancangan yang diperlukan dengan model RTL dibanding dengan model TLM.

Gambar 4. Perbandingan Jumlah Baris Kode

Gambar 6. Peningkatan Kinerja Proses Perancangan

Pengukuran peningkatan kinerja proses perancangan dapat dilakukan dengan menggunakan persamaan 1. ( ) rtl tlm T T e T (1)

Berdasarkan hasil uji coba yang telah dilakukan yang tergambar pada Gambar 4 dan 5 diperoleh sebuah grafik peningkatan kinerja pada Gambar 6. Berdasarkan Gambar 6, dapat terlihat bahwa kinerja proses perancangan meningkat sejalan dengan peningkatan jumlah komponen pada embedded system tersebut kecuali pada studi kasus 2–tiers yang kinerjanya lebih tinggi dibandingkan dengan 3-tiers.

Salah satu kelebihan pemodelan TLM terletak pada transaksi antar komponen. Semakin banyak komponen pada suatu sistem maka tingkat transaksi yang menggunakan Bus akan semakin meningkat. Peningkatan transaksi antar komponen sangat cocok dengan pemodelan TLM. Sebaliknya dalam pemodelan level RTL banyaknya jumlah komponen dan transaksi pada suatu sistem akan semakin meningkatkan kerumitan perancangan. Sehingga semakin banyak jumlah komponen dan transaksi di dalamnya maka proses perancangan semakin lambat. Dengan kondisi tersebut maka proses perancangan pada pemodelan TLM semakin lebih baik pada kondisi dengan banyak komponen yang berinteraksi. Itulah kelebihan pemodelan level TLM yang berada pada level transaksi.

5. Kesimpulan dan Saran

Dari serangkaian pengujian, maka ditarik kesimpulan sebagai berikut:

1. Pemodelan level TLM lebih baik diterapkan pada sistem yang kompleks yaitu pada kondisi lebih dari dua komponen yang berinteraksi yang di dalamnya terdapat proses arbitrasi.

2. Kinerja proses perancangan TLM terhadap RTL meningkat sejalan dengan peningkatan kompleksitas sistem dan transaksi.

Saran untuk penelitian selanjutnya antara lain: 1. Perlu diuji untuk beberapa jenis bus selain

Avalon seperti Wishbone dan AMBA. Peningkatan kinerja TLM terhadap RTL dipengaruhi oleh jenis bus yang digunakan. 2. Perlu dilakukan uji coba untuk mengetahui batas

maksimal jumlah komponen dalam sebuah embedded system.

Daftar Pustaka

[1] Berger, Arnold S., “Embedded System Design: An Introduction to Processes, Tools, and Techniques”, CMP Books, 2002.

[2] Black, David, Jack Donovan, “SystemC: From the Ground Up”, Kluwer Academic Publisher, USA, 2004.

[3] Chatha, Karamvir Sigh, “System-Level Cosynthesis of Transformative Application for Heterogeneous Hardware-Software Architecture”, Dissertation at University of Cincinnati, 2001.

[4] Cornet, Jerome, “Separation of Functional and Non-Functional Aspects in Transactional Level Models of Systems-on-Chip”, Dissertation at Institut Polytechnique De Grenoble, 2008.

[5] Genovese, Matt, ”A Quick-Start Guide for Learning SystemC”, The University of Texas, Austin, 2004.

[6] Grotker, Thorsten, Stan Liao, “System Design with SystemC”, Kluwer, USA, 2002.

[7] Gupta, Rajesh Kumar, “Co-Synthesis of Hardware and Software for Digital Emmbedded Systems”, Dissertation at Stanford University, 1993.

[8] Mathaikutty, Deepak A., “Metamodeling Driven IP Reuse for System-on-chip Integration and Microprocessor Design”, Dissertation at Virginia Polytechnic Institute and State University, 2007.

[9] Mooney III, Vincent John, “Hardware/ Software Co-design of Run-time Systems”, Dissertation at Stanford University, 1998. [10] Moore, Gordon E., “Cramming More

Components onto Integrated Circuits”, Electronics, 38(8): 114-117, 19 April 1965. [11] Patel, H., D. (2007) : Ingredients for

Successful System Level Automation & Design Methodology, Dissertation at Virginia Polytechnic Institute and State University. [12] Vahid, Frank, Tony Givargis. “Embedded

System A Unified Hardware/Software Introduction”, JohnWiley & Sons Inc., New York, 2002.

![Gambar 1. Peningkatan Kapasitas IC Sampai Tahun 2005 [5]](https://thumb-ap.123doks.com/thumbv2/123dok/4375335.3192444/1.892.468.787.772.1015/gambar-peningkatan-kapasitas-ic-sampai-tahun.webp)