Fakultas Teknologi Industri, Universitas Gunadarma

Jl. Margonda Raya 100, Depok 16424

E-mail : [email protected] Abstrak

Penulisan ini adalah suatu analisa terhadap divais Graded-Channel Metal-Oxide-Semiconductor Field-Effect-Transistor atau disingkat GCMOSFET. Teknologi GCMOSFET dewasa ini berkembang sebagai salah satu usaha untuk memenuhi kebutuhan divais dalam aplikasi berdaya rendah dan mempunyai performansi lebih tinggi. Pada penulisan ini ditekankan untuk menganalisa keunggulan GCMOSFET dibanding dengan MOSFET ungraded. GCMOSFET dapat menghasilkan output ID yang lebih besar jika dibandingkan dengan MOSFET ungraded. Peningkatan arus ID ini terjadi disebabkan pengaruh graded channel pada divais yang menghasilkan panjang channel efektif yang lebih kecil daripada panjang channel efektif MOSFET ungraded. Dari hasil simulasi dengan berbantuan perangkat lunak S-PISCES 2B dan MATLAB dapat ditunjukkan bahwa ID yang dihasilkan GCMOSFET lebih besar daripada ID yang dihasilkan MOSFET ungraded, sebagai contohnya untuk VG = 4 V dan VD = 4 V, ID pada MOSFET sama dengan 1,47589798 e-04 A, sedangkan pada GCMOSFET sama dengan 2,59738752 e-04 A. Di samping itu, misalkan untuk menghasilkan ID = 1,10687718 e-04 A pada MOSFET diperlukan VG = 3 V dan VD = 4 V, sedangkan pada GCMOSFET diperlukan VG = 2 V dan VD = 3,4 V. Hal ini menunjukkan bahwa GCMOSFET mengkonsumsi daya yang lebih rendah dibandingkan MOSFET ungraded.

.

1. Pendahuluan

Peningkatan aplikasi Digital Signal Processing (DSP) untuk produk komunikasi merupakan salah satu penyebab meningkatnya pengembangan teknologi VLSI tegangan rendah/daya rendah, performansi tinggi dan biaya rendah untuk aplikasi DSP [1].

Pada rangkaian CMOS, konsumsi daya total terdiri dari dua komponen, yaitu: daya dinamik dan daya statik. Daya dinamik proporsional dengan VDD

2

. VDD merupakan tegangan

supply. Daya statik ditentukan oleh leakage current. Disini berarti jika VDD diturunkan, maka akan

menurunkan konsumsi daya. Akan tetapi menurunkan VDD , juga berarti menurunkan current drive.

Hal ini disebabkan oleh karena current drive proporsional dengan (VDD - Vt) 2

. [2] Vt adalah

tegangan threshold.

Disebabkan hal-hal di atas, harus dilakukan penurunan skala divais dan penurunan tegangan threshold atau Vt. Akan tetapi, muncul masalah lain, yaitu short channel effect yang

mengakibatkan peningkatan leakage current, yang berarti naiknya konsumsi daya statik. Di samping itu, pengskalaan divais memerlukan tingkat teknologi yang lebih baik dan kompleks. Oleh karenanya, mengembangkan kecepatan rangkaian pada tegangan rendah merupakan suatu tantangan.

Kebutuhan divais berperformansi tinggi, daya rendah, dan juga ekonomis terus meningkat; oleh karenanya, teknologi Graded Channel MOSFET dikembangkan dengan tujuan untuk memperoleh divais yang memiliki peningkatan kecepatan pada tegangan yang lebih rendah, tetapi juga lebih ekonomis.

2.

Struktur dan TeknologiI GCMOSFET

2.1 Struktur GCMOSFET

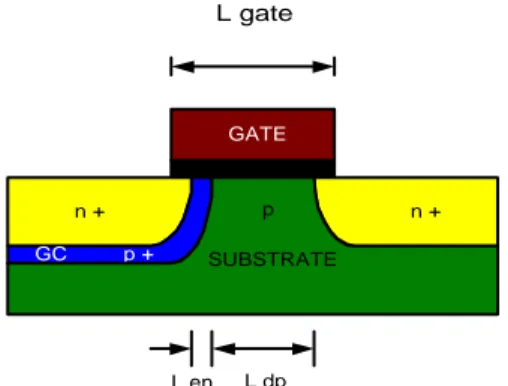

Struktur GCMOSFET hampir sama dengan struktur MOSFET ungraded, kecuali pada implantasi pengatur tegangan threshold, Vt, pada MOSFET diganti dengan suatu implantasi

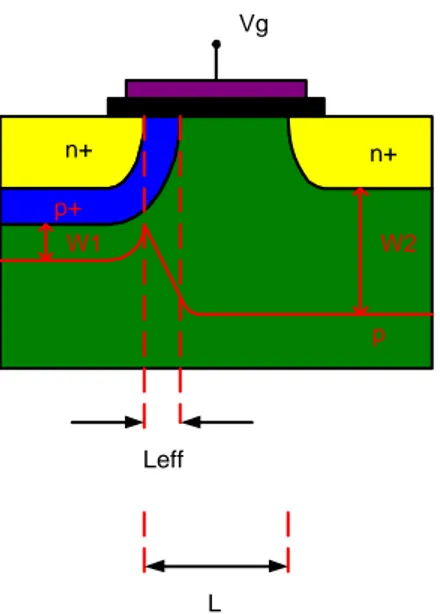

graded-channel pada sisi source saja (disebut unilateral) . Species implantasi GC (grade-channel) berlawanan dengan yang terdapat pada source/drain, sebagai contoh suatu GC tipe-p untuk divais n-channel dan GC tipe-n untuk divais p-channel. [3] Gambar 1. menunjukkan struktur dasar divais untuk unilateral GCMOSFET dibandingkan dengan divais MOSFET ungraded.

SUBSTRATE p n + n + GATE a n + n + p + GC GATE p SUBSTRATE b

Gambar 1. Struktur Divais (a) CMOS ungraded, (b) GCMOSFET Unilateral

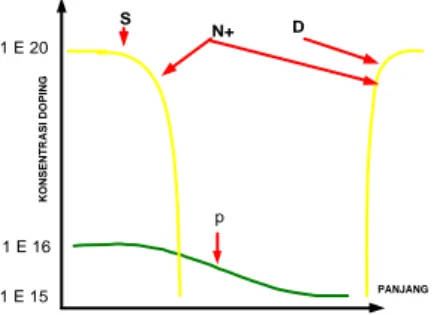

Gambar 2. menunjukkan bentuk doping dari struktur GCMOSFET. Dibandingkan dengan MOSFET ungraded dengan channel terdoping merata, maka doping channel sepanjang permukaan pada GCMOSFET adalah “bertingkat” atau “graded”.

N+ 1 E 20 1 E 16 1 E 15 D S p KO NS E NTRAS I DO P ING PANJANG

Gambar 2. Bentuk Doping Dari Unilateral GCMOSFET

Divais GCMOSFET, seperti ditunjukkan gambar 3., dapat dilihat sebagai dua subdivais yang dihubungkan series, satu pada sisi source dan yang lain pada sisi drain, dengan tegangan threshold (Vt) masing-masing yang berbeda. Pada sisi source, karena doping GC yang lebih tinggi

daripada doping well, subdivais dengan panjang “channel” Len, memiliki Vt yang lebih tinggi.

Sebaliknya pada sisi drain, doping channel sama dengan doping well, karenanya subdivais ini memiliki Vt yang lebih rendah dengan suatu panjang channel Ldp. Vt dari GCMOS ditentukan oleh

subdivais pada sisi source. Panjang channel effektif ditentukan oleh region GC , yaitu Len, yang

tentunya jauh lebih pendek daripada panjang gate secara phisik. Sebagai hasilnya, untuk panjang gate secara phisik yang sama, divais GCMOSFET dapat menghasilkan arus drive yang lebih tinggi dan puncak transkonduktansi yang lebih tinggi dibandingkan divais MOSFET ungraded, berarti menghasilkan suatu divais berperformansi tinggi. Implantasi GC juga efektif untuk menekan short

suatu divais dengan arus drive yang lebih tinggi .Di samping itu, teknologi GCMOSFET adalah kompatibel dengan teknologi CMOS.

n + n + p + GC GATE p SUBSTRATE L gate L en L dp

Gambar 3. Struktur GCMOSFET Unilateral menunjukkan konsep dari dua subdivais

2.2

Teknologi GCMOSFET

GCMOSFET berdasarkan proses CMOS, dengan modul GC ditambahkan untuk menggantikan modul implantasi Vt, ditambah modifikasi minor pada front-end-of-the-line (FEOL), atau bagian awal proses, untuk mengoptimasi GCMOSFET. Back-end-of-the-line (BEOL), atau bagian akhir dari proses, adalah identik dengan teknologi CMOS. Karena modul GC hanya merupakan penambahan pada proses GCMOSFET, sembarang garis produksi dengan kapabilitas submikron dapat menghasilkan GCMOSFET performansi tinggi tanpa peningkatan teknologi yang berlebihan, yang berarti menghasilkan suatu penghematan biaya yang penting.

3.

Analisa

3.1 Analisa Kedalaman Channel Pada Saturasi

Pada Gambar 4. di bawah ini, kembali ditunjukkan sebuah MOSFET

Qn adalah densitas muatan pada inversion layer dan Qn dapat dinyatakan dengan: Qn = √2 q .NA. LD ( )

(

)

⎪ ⎭ ⎪ ⎬ ⎫ ⎪ ⎩ ⎪ ⎨ ⎧ Ψ − ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + Ψ Ψ − 2 1 2 1 0 0 s V p p s D s e p nβ

β

β β (1) Jika Qn = 0, maka √2 q .NA. LD ( )(

)

⎪ ⎭ ⎪ ⎬ ⎫ ⎪ ⎩ ⎪ ⎨ ⎧ Ψ − ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + Ψ Ψ − 2 1 2 1 0 0 s V p p s D s e p nβ

β

β β = 0 (2)Setelah itu, kedua ruas kiri dan kanan dibagi dengan √2 q .NA. LD, sehingga dapat dinyatakan

dengan persamaan (3): ( )

(

)

2 1 2 1 0 0 s V p p S D s e p n Ψ − ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + Ψ Ψ −β

β

β β = 0 (3)kemudian, dengan memindahkan bagian negatif ke ruas kanan dari persamaan, sehingga diperoleh:

( ) 2 1 0 0 ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + Ψ Ψs− VD p p s e p n β β

β

=(

)

2 1 sΨ

β

(4)Dilanjutkan dengan pengkuadratan pada kedua ruas dari persamaan (4), maka akan diperoleh persamaan (5) ( s VD) p p s

e

p

n

β ββ

Ψ −⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

+

Ψ

0 0 =β

Ψ

s (5)Dengan memindahkan βΨs dari ruas kiri ke ruas kanan dari persamaan

(5), akan diperoleh: ( s VD) p p

e

p

n

βΨ −β⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

0 0 = 0 (6)Sehingga dapat dinyatakan dengan:

( )

= 0 (7)

D

s V

e

βΨ−βatau dengan cara penulisan lain dapat dinyatakan dengan:

D s V

e

e

β βΨ ≈ 0 (8)ini dapat terjadi jika dan hanya jika

D

V

e

β >>e

βΨsdan ini berarti

VD >> Ψs

Seperti ditunjukkan oleh Gambar 5, jika VD >> Ψs, akan menghasilkan nilai kedalaman channel

atau xi = 0

Gambar 5. Variasi Energy Band Pada Keadaan Nonequilibrium Pada Drain. [4]

3.2

Analisa Lebar Depletion

Pada Gambar 6 ditunjukkan bahwa pada y = L, maka xi = 0 ketika VD = Vsat.

Gambar 6. MOSFET Pada Saturasi [4]

Qs = Qn + Qd (9)

Dengan

Qs = densitas total muatan pada semikonduktor per satuan luas

Qn = densitas muatan pada inversion layer

Qd = densitas muatan pada depletion layer

Disebabkan pada sa’at pinch-off , Qn = 0, maka Qd akan mencapai nilai maksimum. Oleh

Lebar depletion dapat dinyatakan dengan:

(

B BS)

As V qN

W= 2

ε

2Ψ + / (10)dengan NA merupakan doping acceptor, dan jika NA semakin tinggi, akan mengakibatkan nilai W

semakin rendah, atau sebaliknya, nilai NA semakin rendah, maka nilai W atau lebar depletion

semakin tinggi.

Sekarang jika dilihat pada divais GCMOSFET, karena konsentrasi pada region GC lebih tinggi daripada konsentrasi pada bagian substrate, maka lebar depletion pada daerah GC region lebih rendah dari lebar depletion pada daerah lainnya.

Sehingga ketika VDS mencapai nilai saturasi pada GCMOSFET, maka lebar depletion pada

bagian substrate lain akan semakin lebar dan ini mengakibatkan seluruh bagian lain tersebut sebagai kepanjangan dari drain untuk divais. Hal ini mengakibatkan panjang channel efektif divais merupakan Leff yang tentunya lebih pendek dari pada L gate yang sebenarnya, seperti yang

ditunjukkan pada Gambar 7, dengan W1 adalah lebar depletion pada sisi source dan W2 adalah

lebar depletion pada sisi drain. Karena ID berbanding terbalik dengan panjang channel, sehingga

dengan hal ini, dapat diperoleh ID yang lebih besar.

Gambar 7. Lebar Depletion Dari GCMOSFET

Ini berarti lebar depletion pada bagian well yang lain lebih besar daripada lebar depletion pada bagian GC. Sehingga, mengakibatkan bagian GC menjadi panjang channel efektif, sedangkan bagian well lainnya menjadi seolah-olah kepanjangan daripada drain. Hal ini mengakibatkan GCMOSFET menghasilkan suatu divais dengan panjang channel efektif yang lebih kecil daripada panjang channel efektif pada MOSFET ungraded.

3.3

Simulasi Dengan S-PISCES 2B

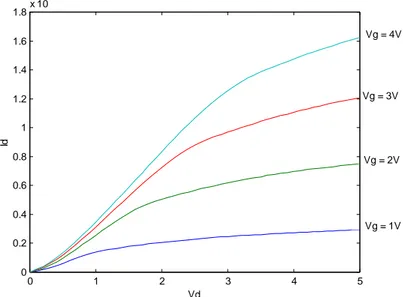

Pada bagian ini akan diperlihatkan hasil simulasi dari MOSFET ungraded dan GCMOSFET. Simulasi dilakukan dengan bantuan S-PISCES2B [5] dan MATLAB [6].

n+ p+ Vg n+ W1 W2 p Leff L

0 1 2 3 4 5 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8x 10 -4 Vd Id Vg = 1V Vg = 2V Vg = 3V Vg = 4V

Gambar 8. ID Versus VD Pada MOSFET Berdasarkan Hasil Simulasi

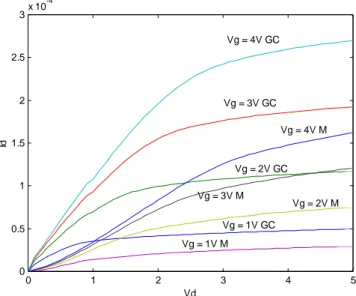

Kemudian simulasi dilakukan untuk GCMOSFET, dan diperoleh hasil seperti ditunjukkan pada Gambar 9. 0 1 2 3 4 5 0 0.5 1 1.5 2 2.5 3x 10 -4 Vd Id Vg = 1V Vg = 2V Vg = 3V Vg = 4V

Gambar 9. ID Versus VD Pada GCMOSFET Berdasarkan Hasil Simulasi

Kemudian hasil simulasi MOSFET dan hasil simulasi GCMOSFET digabungkan menjadi satu, sehingga dapat terlihat perbandingannya secara lebih jelas. Perbandingan ini dapat dilihat pada Gambar 10. Pada gambar ini VG = 1V M menyatakan kurva untuk VG = 1V pada MOSFET,

0 1 2 3 4 5 0 0.5 1 1.5 2 2.5 3x 10 -4 Vd Id Vg = 1V GC Vg = 2V GC Vg = 3V GC Vg = 4V GC Vg = 1V M Vg = 2V M Vg = 3V M Vg = 4V M

Gambar 10. Perbandingan Hasil Simulasi ID – VD pada MOSFET dan GCMOSFET

Berdasarkan hasil simulasi ini, sebagai contoh perbandingan dapat dilihat pada Tabel 1. Pada Tabel 1 ditunjukkan bahwa ID yang dihasilkan GCMOSFET lebih besar daripada ID yang

dihasilkan MOSFET.Seperti telah dijelaskan pada bagian sebelumnya dari tesis ini, hasil yang diperoleh dapat terjadi karena GCMOSFET memiliki Leff atau panjang channel efektif yang lebih

kecil daripada panjang channel efektif MOSFET, dan ID berbanding terbalik dengan panjang

channel efektif, sehingga GCMOSFET dapat menghasilkan ID yang lebih besar daripada ID yang

dihasilkan MOSFET.

Tabel 1 Perbandingan ID pada MOSFET dan GCMOSFET

VG VD ID pada MOSFET ID pada GCMOSFET

1 V 4 V 2,73351427 e-05 4,75760908 e-05

2 V 4 V 6,97524141 e-05 1,13266075 e-04

3 V 4 V 1,10687718 e-04 1,86067396 e-04

4 V 4 V 1,47589798 e-04 2,59738752 e-04

Di samping itu, misalkan untuk memperoleh ID = 1, 10687718 e-04 A, pada MOSFET

diperlukan VG = 3 V dan VD = 4 V, sedangkan pada GCMOSFET diperlukan VG = 2 V dan VD =

3,4 V. Untuk hal ini jelas terlihat bahwa GCMOSFET mengkonsumsi daya yang lebih rendah daripada MOSFET , dengan tanpa mengurangi hasil performansi arus drainnya. Sehingga dapat dikatakan bahwa GCMOSFET dapat dikatakan sebagai suatu divais yang mengkonsumsi daya rendah, dan GCMOSFET dapat memenuhi kebutuhan akan divais untuk aplikasi daya rendah.

4. Kesimpulan

Dari tulisan ini, dapat diambil tiga kesimpulan utama seperti uraian di bawah ini

1. GCMOSFET dapat menghasilkan suatu divais dengan panjang channel efektif yang lebih pendek daripada panjang gate secara phisik. Dalam hal ini dapat diperoleh suatu divais yang kecil, tanpa memerlukan penekanan teknologi yang berlebihan.

channel efektif MOSFET ungraded, sehingga GCMOSFET menghasilkan arus ID yang lebih

besar daripada arus ID yang dihasilkan oleh MOSFET ungraded. Dari hasil simulasi dengan

perangkat lunak S-PISCES 2B, dapat dilihat bahwa GCMOSFET menghasilkan ID yang lebih

besar jika dibandingkan dengan MOSFET ungraded. Sebagai contoh, pada VG = 4 V dan VD = 4

V, pada MOSFET menghasilkan ID = 1,47589798 e-04 A, sedangkan pada GCMOSFET

menghasilkan ID = 2,59738752 e-04 A.

3. Untuk memperoleh ID tertentu, misalkan untuk memperoleh ID = 1,10687718 e-04 A, pada

MOSFET diperlukan VG = 3 V dan VD = 4 V, sedangkan pada GCMOSFET diperlukan VG = 2

V dan VD = 3,4 V. Karena hal ini, berarti GCMOSFET mengkonsumsi daya yang lebih rendah

dibandingkan MOSFET ungraded.

5. Daftar Pustaka

[1] Ma, J. , Han. B.L. , R.A. Pryor, S. Cheng, M.H. Kaneshiro, C.S. Kyono, dan K. Papworth, “A Graded-Channel MOS (GCMOS) VLSI Technology for Low Power DSP Application,” ISLPED, pp. 129-132, 1996.

[2] Weste, N.H.E. dan K.esraghian, “Principles of CMOS VLSI Design,” 1st ed. Reading, Massachusetts: Addison-Wesley, 1985.

[3] Ma, J. , Han. B.L. , R.A. Pryor, S. Cheng, M.H. Kaneshiro, C.S. Kyono, dan K. Papworth, “Graded-Channel MOSFET (GCMOSFET) for High Performance, Low Voltage DSP Applications,” IEEE Trans. VLSI System, vol.5, pp. 352-359, Desember 1997.

[4] Sze, S.M., “Physics of Semiconductor Devices,” 2nd ed., New York: John Wiley & Sons, 1981.

[5] Silvaco International, “S-Pisces2B Version 4.09 User Manual,” 1991.

[6] The Math Works Inc, “The Student Edition of MATLAB for MS-DOS Personal Computers,” Englewood Cliffs, New Jersey: Prentice-Hall, 1992.

![Gambar 5. Variasi Energy Band Pada Keadaan Nonequilibrium Pada Drain. [4]](https://thumb-ap.123doks.com/thumbv2/123dok/4322686.2912869/5.892.379.659.333.567/gambar-variasi-energy-band-keadaan-nonequilibrium-drain.webp)