LAPORAN PRAKTIKUM SISTEM DIGITAL

SD-01 : DASAR-DASAR LOGIKA DAN RANGKAIAN

KOMBINASIONAL

NAMA

: HANNA YASMINE

NO. MHS

: 13/348217/TK/40828

ASISTEN

: ASIH ISTIQOMAH

HARI / TANGGAL PRAKTIKUM

: 29 Oktober 2014

HARI / TANGGAL LAPORAN

: 05 November 2014

JURUSAN TEKNIK FISIKA

FAKULTAS TEKNIK

I.

Tujuan

1. Mahasiswa mengenal dasar-dasar logika, operasi-operasi yang berlaku dan teknik matematis yang digunakan untuk menyelesaikan persoalan-persoalan logika.

2. Mahasiswa mengenal implementasi gerbang-gerbang ke dalam bentuk hardware (IC / Integrated Circuits).

3. Mahasiswa dapat menjelaskan rangkaian logika secara aljabar dengan menggunakan ekspresi Boolean.

4. Mahasiswa dapat mengevaluasi output dari suatu rangkaian logika.

5. Mahasiswa dapat mengimplementasikan rangkaian dari ekspresi Boolean.

II.

Data

A B Y2

0 0 1

1 - a

1 - b

A B Y1

0 0 0

0 1 0

1 0 0

0 1 1

1 0 0

1 1 1

A B C Y3

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 1

2 - a

Rangkaian dari Asisten

A B C Y4

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 0

III.

Analisis Data

1) Tabel Kebenaran

Rangkaian 1- a

Rangkaian 1 - b

1 4

2

3

1

2

A B ~A ~B 1 2 3 4 Y1

0 0 1 1 0 0 0 0 0

0 1 1 0 1 0 1 0 1

1 0 0 1 0 1 1 0 1

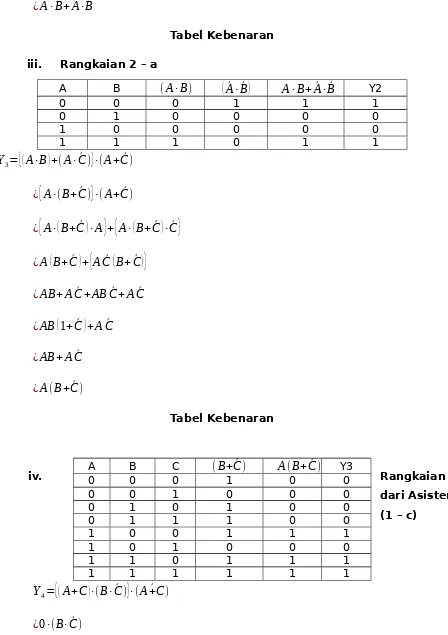

Rangkaian 2 – a

Rangkaian dari Asisten ( 1 – c )

4 1 2 3 3 1 4 2

A B ~A ~B 1 2 Y2

0 0 1 1 1 1 1

0 1 1 0 0 1 0

1 0 0 1 1 0 0

1 1 0 0 1 1 1

A B C 1 2 3 4 Y3

0 0 0 0 0 1 0 0

0 0 1 0 0 0 0 0

0 1 0 0 0 1 0 0

0 1 1 0 0 0 0 0

1 0 0 0 1 1 1 1

1 0 1 0 0 1 0 0

1 1 0 1 1 1 1 1

1 1 1 1 0 1 1 1

A B C 1 2 3 4 Y4

0 0 0 0 0 1 0 0

0 0 1 1 0 0 0 0

0 1 0 0 1 1 0 0

0 1 1 1 0 0 0 0

1 0 0 1 0 0 0 0

1 0 1 1 0 0 0 0

1 1 0 1 1 0 1 0

2) Penyederhanaan Rangkaian

i. Rangkaian 1-a

Y

1=

{

(

A ∙ B

´

)

∙

(

A ∙

B

´

)

}

+(

B

+

A

)

¿0+B+A

¿

A

+

B

Tabel Kebenaran

ii. Rangkaian 1 - b

Y

2=(

A

+ ´

B

)

∙

(

A

´

+

B

)

¿

A ∙

A

´

+

A ∙ B

+ ´

B .

A

´

+

B ∙

B

´

¿

0+

A ∙ B

+ ´

B ∙

A

´

+0

A B A +

B Y1

0 0 0 0

0 1 1 1

1 0 1 1

¿

A ∙ B

+ ´

A ∙

B

´

Tabel Kebenaran iii. Rangkaian 2 – a

Y3=

{

(

A ∙ B)

+(A ∙C´)}

∙(A+ ´C)¿

{

A ∙

(

B

+ ´

C

)

}

∙

(

A

+ ´

C

)

¿

{

A ∙

(

B

+ ´

C

)

∙ A

}

+

{

A ∙

(

B

+ ´

C

)

∙

C

´

}

¿

A

(

B

+ ´

C

)

+

{

A

C

´

(

B

+ ´

C

)

}

¿

AB

+

A

C

´

+

AB

C

´

+

A

C

´

¿

AB

(

1+ ´

C

)

+

A

C

´

¿

AB

+

A

C

´

¿

A

(

B

+ ´

C

)

Tabel Kebenaran

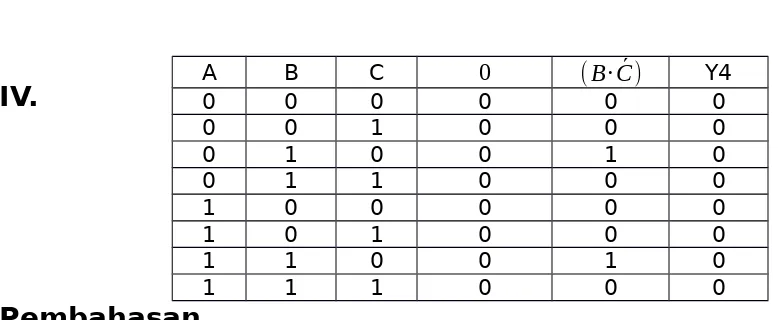

iv. Rangkaian

dari Asisten (1 – c)

Y

4=

{

(

A

+

C

)

∙

(

B ∙

C

´

)

}∙

( ´

A

+

C

)

¿

0

∙

(

B∙

C

´

)

A B (A ∙ B)

(

A ∙

´

B

´

)

A ∙ B

+ ´

A ∙

B

´

Y20 0 0 1 1 1

0 1 0 0 0 0

1 0 0 0 0 0

1 1 1 0 1 1

A B C

(

B

+ ´

C

)

A

(

B

+ ´

C

)

Y30 0 0 1 0 0

0 0 1 0 0 0

0 1 0 1 0 0

0 1 1 1 0 0

1 0 0 1 1 1

1 0 1 0 0 0

1 1 0 1 1 1

¿

0

Tabel Kebenaran

IV.

Pembahasan

Dapat dilihat bahwa hasil yang didapat melalui praktik nyata yang dilakukan oleh praktikan mempunyai hasil yang berbeda dengan tabel kebenaran dan simulasi multisim pada rangkaian 1 – a, 1 – b, 2 – a. Satu-satunya rangkaian yang memberikan output yang sama antara praktikum, tabel kebenaran, dan simulasi multisim adalah rangkaian dari asisten (1 – c).

Pada rangkaian 1 – a dan 1 - b, ada dua input yaitu A dan B yang terhubung dengan gerbang logika AND, OR, dan inverter (NOT).

Operasi AND dilambangkan dengan dot (•), hanya menghasilkan nilai

benar (1) jika kedua variabel bernilai benar, selain itu akan bernilai salah (0).

Operasi OR dilambangkan dengan cross (+), hanya menghasilkan

benar (1) jika salah satu variabelnya bernilai benar.

Maksud dari invers atau keluaran inverter (NOT), adalah mengubah

logic salah (0) menjadi benar (1) dan begitu pula sebaliknya akan mengubah logic benar (1) menjadi salah (0).

Rangkaian 1 – a:

1) Mari ditinjau di bagian atas (nomor 1). A diinvers oleh inverter sehingga keluarannya adalah

A

´

.A

´

langsung dikombinasikandengan input B di gerbang AND yang menghasilkan nomor 1

(

A ∙ B

´

)

.A B C

0

(

B∙

C

´

)

Y40 0 0 0 0 0

0 0 1 0 0 0

0 1 0 0 1 0

0 1 1 0 0 0

1 0 0 0 0 0

1 0 1 0 0 0

1 1 0 0 1 0

2) Kemudian tinjau bagian tengah (nomor 2). Kali ini B yang diinvers oleh inverter sehingga keluarannya adalah

B

´

.B

´

dikombinasikandengan input A di gerbang AND yang menghasilkan nomor 2

(

A ∙B´)

. 3) Tinjauan berikutnya adalah bagian bawah (nomor 3). Input B dan inputA dikombinasikan di gerbang OR yang menghasilkan keluaran nomor 3

(B+A) .

4) Pada nomor 4, hasil dari nomor 1 dan nomor 2 diaplikasikan operasi

AND yang menghasilkan nomor 4

{

(

A ∙ B

´

)

∙

(

A ∙

B

´

)

}

, yang selanjutnyaakan dikombinasikan dengan hasil operasi OR (keluaran nomor 3), yang berakhir dengan pengoperasian OR antara nomor 4 dan nomor 3

(nomor 5 atau

Y

1=

{

(

A ∙ B

´

)

∙

(

A ∙

B

´

)

}

+(

B

+

A

)

).5) Variasi input dengan output dapat dilihat di tabel kebenaran, di bab analisis data.

6) Dari hasil pengoperasian persamaan Y1 terhadap variasi input, yang menghasilkan 1 0 0 1, hasilnya sesuai dengan tabel kebenaran dan simulasi multisim, namun berbeda dengan hasil praktikum yang menghasilkan 0 0 0 0.

7) Hasil praktikum yang berbeda dengan tabel kebenaran dan simulasi multisim kemungkinan besar disebabkan oleh performansi circuit board dan IC yang tidak optimal atau kabel yang kurang menancap pada circuit board, meskipun peletakan Vcc, ground, resistor, LED, hubungan antar kabel-IC sudah mematuhi peraturan yang ada.

Rangkaian 1 – b:

1) Tinjau di bagian nomor 1, yaitu input A dikombinasikan di gerbang OR dengan input B yang sudah diinvers menjadi

B

´

, menghasilkan keluarannomor 1

(

A

+ ´

B

)

.2) Tinjauan nomor 2 menunjukkan bahwa input A diinvers menjadi

A

´

dan dikombinasikan dengan input B di gerbang OR, menghasilkan keluaran 2( ´A+B) .

3) Tinjauan nomor 3, merupakan hasil kombinasi dari nomor 1 dan nomor 2

di gerbang AND (

Y

2=(

A

+ ´

B

)

∙

(

A

´

+

B

)

).5) Dari hasil pengoperasian persamaan output Y2 terhadap variasi input, yaitu 0 1 1 1, sesuai dengan hasil tabel kebenaran dan hasil simulasi multisim, namun berbeda dengan hasil praktikum yang outputnya adalah 1 1 0 1.

6) Hasil praktikum yang berbeda dengan tabel kebenaran dan simulasi multisim kemungkinan besar disebabkan oleh performansi circuit board dan IC yang tidak optimal atau kabel yang kurang menancap pada circuit board, meskipun peletakan Vcc, ground, resistor, LED, hubungan antar kabel-IC sudah mematuhi peraturan yang ada.

Pada rangkaian 2 – a dan 1 – c, ada 3 input yaitu A, B, C dan gerbang logika AND, OR, NOT.

Rangkaian 2 – a:

1) Tinjau di bagian nomor 1, yaitu input A dikombinasikan dengan input B di gerbang AND yang menghasilkan keluaran nomor 1

(

A ∙ B)

.2) Di bagian nomor 2, input A dikombinasikan dengan input C yang sudah diinvers menjadi C´ , kemudian keduanya dikombinasikan di gerbang

AND yang menghasilkan keluaran nomor 2

(

A ∙

C

´

)

.3) Di bagian nomor 3, input A dikombinasikan dengan input C yang sudah diinvers menjadi C´ , kemudian keduanya dikombinasikan di gerbang OR

yang menghasilkan keluaran nomor 3

(

A

+ ´

C

)

.4) Di bagian nomor 4, hasil keluaran nomor 1 dan nomor 2 dikombinasikan di

gerbang OR sehingga menghasilkan keluaran nomor 4

(

A ∙ B

)+(

A ∙

C

´

)

5) Output final yaitu nomor 5, merupakan kombinasi antara keluaran nomor4 dan nomor 3 pada gerbang AND Y3=

{

(

A ∙ B)

+(A ∙C´)}

∙(A+ ´C) .6) Variasi input dengan output dapat dilihat di tabel kebenaran, di bab analisis data.

7) Dapat dilihat dari pengoperasian persamaan Y3 terhadap variasi input yang menunjukkan outputnya adalah 0 0 0 0 1 0 1 1, sesuai dengan tabel kebenaran dan hasil simulasi multisim, namun berbeda dengan hasil praktikum yang outputnya adalah 0 0 0 0 1 1 1 1.

dan IC yang tidak optimal atau kabel yang kurang menancap pada circuit board, meskipun peletakan Vcc, ground, resistor, LED, hubungan antar kabel-IC sudah mematuhi peraturan yang ada.

Rangkaian 1 – c:

1) Di bagian nomor 1, input A dioperasikan OR bersama dengan input C yang

menghasilkan keluaran 1 yaitu

(

A+C)

.2) Di bagian nomor 2, input B dioperasikan AND dengan C yang diinvers

menjadi C´ sehingga menghasilkan keluaran 2 yaitu

(

B∙

C

´

)

.3) Kemudian nomor 3 yaitu keluaran nomor 1 yang diinvers dan

menghasilkan keluaran 3 yaitu

( ´

A

+

C

)

.4) Keluaran nomor 1 dan nomor 2 dioperasikan AND sehingga menghasilkan

keluaran 4 yaitu

{

(

A

+

C

)

∙

(

B ∙

C

´

)

}

.5) Sehingga keluaran akhir yaitu pengoperasian AND antara keluaran nomor 3 dengan nomor 4 yang menghasilkan keluaran 5 atau

Y4=

{

(

A+C)

∙(B ∙C´)}

∙( ´A+C) .6) Variasi input dengan output dapat dilihat di tabel kebenaran, di bab analisis data.

7) Dapat dilihat dengan mengoperasikan persamaan Y4 yang menyesuaikan dengan variasi input, hasilnya adalah 0 0 0 0 0 0 0 0 yang sesuai dengan tabel kebenaran, hasil simulasi multisim, dan hasil praktikum.

V.

Kesimpulan

1) Dari pembuatan rangkaian di atas, dapat disimpulkan bahwa praktikan sudah dapat mengenal dasar-dasar logika dan operasi-operasi yang berlaku, serta teknik matematis yang digunakan untuk menyelesaikan persoalan-persoalan logika. Hal tersebut ditunjukkan dengan praktikan mampu mendefinsikan dasar-dasar logika dan operasi yang berlaku, yang dalam praktikum ini adalah operasi AND, OR, dan NOT. Praktikan juga sudah mampu menyederhanakan rangkaian dengan menggunakan teknik matematis yang digunakan untuk menyelesaikan persoalan logika.

semua elemen tersebut menjadi rangkaian berbasis gerbang logika walaupun hasilnya kurang maksimal.

3) Praktikan sudah mampu menjelaskan rangkaian logika dengan ekspreksi aljabar Boolean, seperti yang sudah tertera dan dijelaskan di bab pembahasan.

4) Praktikan juga dapat mengevaluasi output dari suatu rangkaian logika, yang berlandaskan tabel kebenaran dan hasil simulasi multisim.

5) Praktikan juga dapat mengimplementasikan rangkaian dari suatu ekspresi Boolean, seperti yang sudah dijabarkan di bab pembahasan.

VI.

Lampiran

Simulasi Multisim

a. Rangkaian 1 – a dan 1 – b ketika:

A = 0 dan B = 0 dengan Y1 = 0 dan Y2 = 1

A = 0 dan B = 1 dengan Y1 = 1 dan Y2 = 0

b. Rangkaian 2 –a dan 1 – c ketika:

A = 0 B = 0 C = 0 dengan Y3 = 0 dan Y4 = 0

A = 0 B = 1 C = 0 dengan Y3 = 0 dan Y4 = 0

A = 1 B = 0 C = 0 dengan Y3 = 1 dan Y4 = 0

A = 1 B = 1 C = 0 dengan Y3 =1 dan Y4 = 0

Bandingkan Data, Hasil Simulasi, dengan Tabel Kebenaran

Semua hasil simulasi sama persis dengan tabel kebenaran tanpa terkecuali. Data berbeda karena faktor praktikan dan performansi komponen dalam rangkaian yang dipakai berbeda dengan keadaan ideal.

Rangkaian 1 – a:

Rangkaian 1 – b:

Rangkaian 2 – a:

A B Tabel

Kebenaran

Simulasi Multisim

Hasil Praktikum

0 0 0 0 0

0 1 1 1 0

1 0 1 1 0

1 1 1 1 0

A B Tabel

Kebenaran

Simulasi Multisim

Hasil Praktikum

0 0 1 1 1

0 1 0 0 1

1 0 0 0 0

Rangkaian 1 – c:

A B C Tabel

Kebenaran

Simulasi Multisim

Hasil Praktikum

0 0 0 0 0 0

0 0 1 0 0 0

0 1 0 0 0 0

0 1 1 0 0 0

1 0 0 1 1 1

1 0 1 0 0 1

1 1 0 1 1 1

1 1 1 1 1 1

A B C Tabel

Kebenaran

Simulasi Multisim

Hasil Praktikum

0 0 0 0 0 0

0 0 1 0 0 0

0 1 0 0 0 0

0 1 1 0 0 0

1 0 0 0 0 0

1 0 1 0 0 0

1 1 0 0 0 0