MODUL VI

BINARY COUNTER

1. Tujuan

Setelah melakukan percobaan ini, mahasiswa dapat :

a. Memahami koneksi yang diperlukan untuk D dan J-K berdasarkan UP counter. b. State gate koneksi diperlukan untuk mengurangi jumlah binary UP counter. c. State gate koneksi diperlukan untuk mengurangi jumlah binary DOWN counter.

2. Peralatan yang digunakan

a. CIRCUIT #2, #3 , #4 dan dan Logic Monitor of D3000 – 4.3 Sequential Logic-1 Module. b. Multimeter.

c. Shorting links dan connecting leads.

3. Dasar Teori

Counter

Counter merupakan rangkaian logika pengurut, karena counter membutuhkan karakteristik memori, dan pewaktu memegang peranan yang penting. Counter digital mempunyai karakteristik penting yaitu sebagai berikut :

1. Jumlah hitungan maksimum (modulus N-counter)

2. Menghitung ke-atas atau ke-bawah (up atau down - counter)

3. Operasi asinkron atau sinkron

4. Bergerak bebas atau berhenti sendiri

Sebagaimana dengan rangkaian sekuensial yang lain, untuk menyusun counter digunakan flip-flop. Counter dapat digunakan untuk menghitung banyaknya clock-pulsa dalam waktu yang tersedia (pengukuran frekuensi), Counter dapat juga digunakan untuk membagi frekuensi dan menyimpan data.

Counter merupakan aplikasi dari Flip-flop yang mempunyai fungsi menghitung. Proses penghitungan yang dilakukan Counter secara sekuensial, baik menghitung naik (Up Counting) maupun turun (Down Counting).

Berdasarkan pemberian trigger di masing-masing flip-flop penyusun rangkaian Counter, dikenal 2 macam Counter : Counter Sinkron (Synchronous Counter) dan Counter Asinkron (Asynchronous Counter).

Pada Counter Sinkron, sumber clock diberikan pada masing-masing input Clock dari Flip-flop penyusunnya, sehingga apabila ada perubahan pulsa dari sumber, maka perubahan tersebut akan men-trigger seluruh Flip-flop secara bersama-sama.

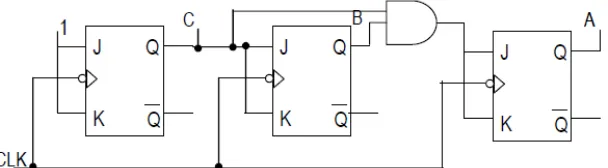

Gambar 6.1 Contoh Up Counter Sinkron 3 bit

Up Dan Down Counter

Sebuah Counter disebut sebagai Up Counter jika dapat menghitung secara berurutan mulai dari bilangan terkecil sampai bilangan terbesar. Contoh : 0-1-2-3-4-5-6-7-0-1-2-….

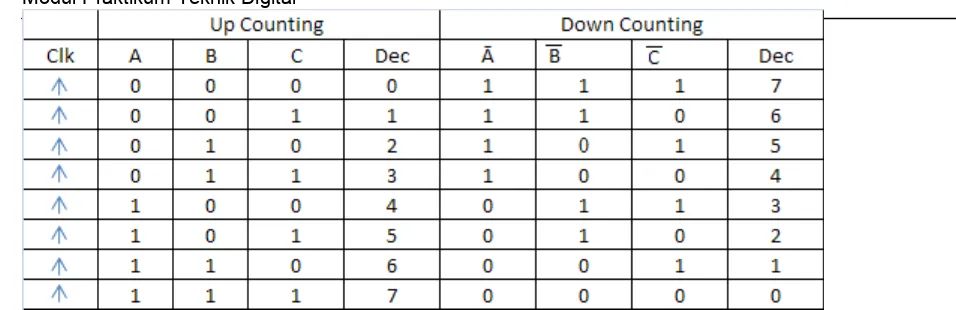

Sedangkan Down Counter adalah Counter yang dapat menghitung secara berurutan dari bilangan terbesar ke bilangan terkecil. Tabel PS/NS untuk Up dan Down Counter 3 bit seperti ditunjukan pada Tabel 6.1.

Untuk membuat sebuah rangkaian Up Counter, lakukan langkah-langkah sintesa rangkaian yang telah dijelaskan sebelumnya. Dari hasil persamaan logika berdasarkan Tabel PS/NS di atas didapatkan rangkaian seperti di bawah ini :

Gambar 6.2 Rangkaian Up Counter Sinkron 3 bit

Berdasarkan Tabel 6.1, dapat dilihat bahwa Down Counting merupakan kebalikan dari Up Counting, sehingga rangkaiannya masih tetap menggunakan rangkaian Up Counter, hanya outputnya diambilkan dari Q masing-masing Flip-flop. Bentuk rangkaian Down Counter adalah seperti gambar 6.3.

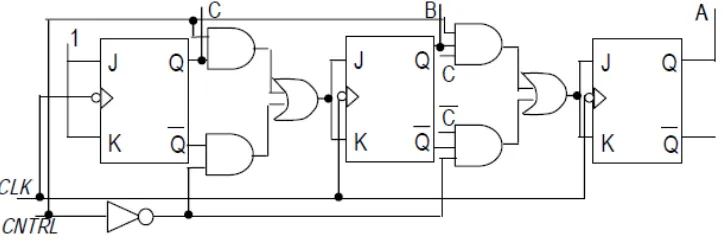

Rangkaian Up/Down Counter

Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down Counter. Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya input eksternal sebagai control yang menentukan saat menghitung Up atau Down. Pada gambar 6.4 ditunjukkan rangkaian Up/Down Counter Sinkron 3 bit. Jika input CNTRL bernilai ‘1’ maka Counter akan menghitung naik (UP), sedangkan jika input CNTRL bernilai ‘0’, Counter akan menghitung turun (DOWN).

Gambar 6.4 Rangkaian Up/Down Counter Sinkron 3 bit.

Counter Asinkron

Pada Counter Asinkron, sumber clock hanya diletakkan pada input Clock di Flip-flop terdepan (bagian Least Significant Bit / LSB), sedangkan input-input clock Flip-flop yang lain mendapatkan catu dari output Flip-flop sebelumnya. Konfigurasi ini didapatkan dari gambar timing diagram Counter 3-bit seperti ditunjukkan pada gambar 6.5. Dengan konfigurasi ini, masing-masing flip-flop di-trigger tidak dalam waktu yang bersamaan. Model asinkron semacam ini dikenal juga dengan nama Ripple Counter.

Gambar 6.5 Timing Diagram Up Counter Asinkron 3-bit

Berdasarkan bentuk timing diagram di atas, output dari flip-flop C menjadi clock dari flip-flop B, sedangkan output dari flip-flop B menjadi clock dari flip-flop A. Perubahan pada negatif edge di masing-masing clock flip-flop sebelumnya menyebabkan flip-flop sesudahnya berganti kondisi (toggle), sehingga input-input J dan K di masing-masing flip-flop diberi nilai ”1” (sifat toggle dari JK flip-flop). Bentuk dasar dari Counter Asinkron 3-bit ditunjukkan pada gambar 6.6.

Gambar 6.6 Up Counter Asinkron 3 bit.

Conter Asinkron Mod-N

Counter Mod-N adalah Counter yang tidak 2n. Misalkan Counter Mod-6, menghitung : 0, 1, 2, 3, 4, 5. Sehingga Up Counter Mod-N akan menghitung 0 s/d N-1, sedangkan Down Counter MOD-N akan menghitung dari bilangan tertinggi sebanyak MOD-N kali ke bawah. Misalkan Down Counter MOD-9, akan menghitung : 15, 14, 13, 12, 11, 10, 9, 8, 7, 15, 14, 13,..

dengan me-NAND kan input A dan B (ABC = 110 untuk desimal 6). Jika input A dan B keduanya bernilai 1, maka seluruh flip-flop akan di-reset.

4. Prosedur Percobaan

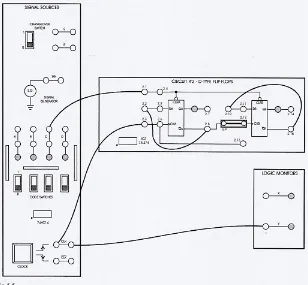

Karakteristik D-Type 2-bit Binary Counter

Gambar 6.7 Karakteristik D-Type 2-bit Binary Counter

1. Masukkan shorting link dan koneksikan rangkaian seperti gambar 6.7.

2. Switch modul power supply pada posisi On dan set switch C ke level logika 1.

3. Gunakan clock pulse satu, amati output state QA dan QB kemudian catat hasil datanya di baris kedua pada tabel 6.3.

4. Gunakan clock pulsa kedua. Amati output state QA dan QB kemudian catat hasil datanya pada tabel 6.3.

5. Ulangi prosedur, gunakan clock pulsa selanjutnya dan catat hasilnya untuk melengkapi tabel 6.3 dibawah ini.

Clock Pulse QB QA

6. Amati 2-bit output state dari QB dan QA. Kamu akan melihat binary output meningkat oleh satu pada tiap clock pulsa. Ini adalah 2-bit asynchronous UP counter.

7. Putuskan link antara socket 2.9 & 2.12 dan hubungkan lead antara socket 2.7 & 2.12 sehingga D-type flip-flop B adalah clock dari output QA. Ulangi prosedur dan lengkapi tabel 6.4 dibawah ini.

Tabel 6.4.

8. Amati 2-bit output state dari QB dan QA. Kamu akan melihat binary output menurun oleh satu pada tiap clock pulsa. Ini adalah 2-bit asynchronous DOWN counter.

Catatan :

...

...

...

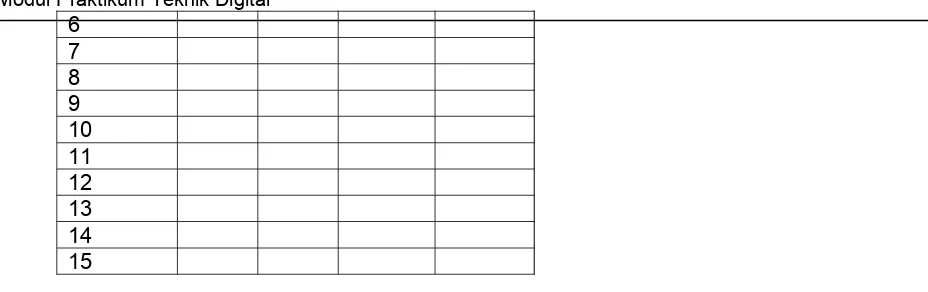

Karakteristik J-K 4-bit Binary Counter

Gambar 6.8 Karakteristik J-K 4-bit Binary Counter

1. Masukkan shorting link dan koneksikan rangkaian seperti pada gambar 6.8.

2. Switch modul power supply pada posisi ON dan set switch A, C dan D ke level logika 1. 3. Set rangkaian untuk inisialisasi state yang ditunjukkan di tabel 6.5.

4. Gunakan clock pulse satu, amati output state QA, QB, QC & QD kemudian catat hasil datanya di baris kedu pada tabel 6.5.

5. Ulangi prosedur, gunakan clock pulse selanjutnya, amati output state untuk setiap pulse dan catat hasil datanya di tabel 6.5.

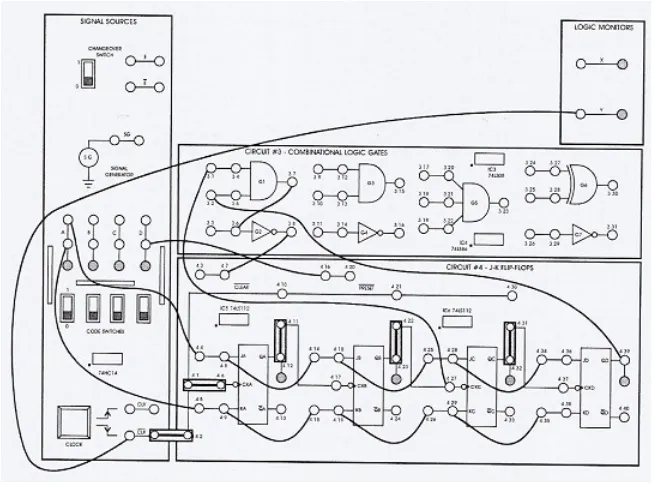

Tabel 6.5.

Clock Pulse

QB QA QC QD

0 0 0 0 Initial state 1

6

6. Amati 4-bit binary output dari QD, QC, QB dan QA. Pada setiap clock pulsa jumlah meningkat oleh satu. Ini adalah 4-bit asynchronous UP counter.

7. Putuskan shorting link antara socket 4.11 & 4.12, 4.22 & 4.23 dan 4.31 & 4.32.

8. Hubungkan leads antara socket 4.13 & 4.17, 4.24 & 4.27 dan 4.33 & 4.37 sehingga

flip-flop diclock dari output dari flip-flip-flop sebelumnya.

10 11 12 13 14 15

10. Amati 4-bit binary output dari QD, QC, QB dan QA. Pada setiap clock pulsa jumlah menurun oleh satu. Ini adalah 4-bit asynchronous DOWN counter.

Catatan :

...

...

...

...

...

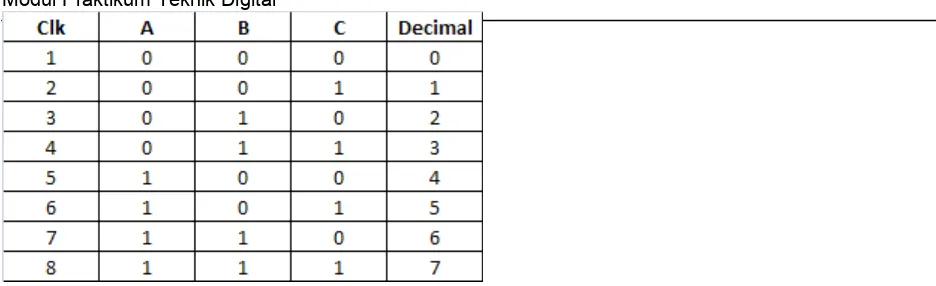

Karakteristik Binary Up Counter with Reduce Count

Gambar 6.4.

2. Switch modul power supply pada posisi ON dan set switch A dan D ke level logika 1. Menentukan tabel kebenaran untuk rangkaian diatas dan melengkapi tabel 6.5.

Tabel 6.5. HIGH, output gerbang NAND menghasilkan LOW dan menghapus semua filp-flop secara simultan, reset counter menjadi nol.

Karakteristik Binary Down Counter with Reduce Count

Gambar 6.5.

1. Masukkan shorting links dan koneksikan rangkaian seperti gambar 6.5.

2. Switch modul power supply pada posisi ON dan set switch A dan D ke level logika 1. Menentukan tabel kebenaran untuk rangkaian diatas dan melengkapi tabel 6.6.

Rangkaian ini bekerja dengan cara yang sama seperti rangkaian sebelumnya kecuali bahwa count yang di reset oleh pulsa clock yang ke tiga belas. Rangkaian gerbang NAND tiga-masukan yang digunakan untuk memantau QA, QC dan QD. Ketika tiga output menghasilkan HIGH bersama-sama output gerbang NAND menghasilkan LOW dan menolak semua flip-flop JK secara bersamaan. Counter direset ke nol dan mulai menghitung lagi.

Catatan :

...

...

...

...