BAB III

METODE PENELITIAN

3.1 Tahap Proses Perancangan Alat

Gambar 3.1 Proses perancangan catu daya elektronik [Sumber:(Rashid, Elektronika Daya: rangkaian, devais, dan aplikasinya, 1999)]

Menurut (Rashid, Elektronika Daya: rangkaian, devais, dan aplikasinya, 1999), perancangan peralatan elektronika daya dapat dibagi menjadi empat bagian:

1. Perancangan rangkaian daya 2. Proteksi perangkat daya 3. Penentuan strategi kontrol

4. Perancangan rangkaian logika dan nilai nominal.

3.2 Spesifikasi Inverter Fasa Tunggal Jembatan Penuh

Spesifikasi inverter yang akan dirancang ini dapat dijadikan sebagai acuan untuk membuat inverter kedalam bentuk hardware. Sumber tegangan yang digunakan untuk mencatu inverter berasal dari sumber tegangan DC. Inverter yang akan dirancang memiliki spesifikasi daya output dan tegangan output sebesar 600 VA dan 220 Volt. Bentuk gelombang yang diharapkan dari inverter adalah sinusoidal murni (pure sine wave). Diharapkan pula efisiensi yang dihasilkan oleh inverter yang dirancang mencapai 90% dan THD yang timbul sebesar kurang dari 5%.

Tabel 3.1 Spesifikasi Perancangan Inverter Fasa Tunggal Jembatan Penuh yang diharapkan

Nama Keterangan

Tegangan 220 Volt

Daya Semu 600 VA

Bentuk Gelombang Sinuoidal Murni (pure sine wave)

THD <5%

Efisiensi 90%

Ukuran (132,08x70,21) mm

3.3 Tahap Proses Simulasi

Gambar 3.2 Tahap proses simulasi [Sumber:(Mohan, Undeland, & Robbins, 2003, hal. 63)]

Dalam merancang peralatan elektronika daya, beberapa analisis harus dilakukan. Di setiap jenis analisis memiliki derajat ketelitian simulasi masing-masing, yaitu bagaimana komponen rangkaian dan kontroler dimodelkan dalam simulasi. Di setiap tahap analisis, hasil simulasinya dapat diverifikasi dengan membuat prototipnya. Berikut adalah tahap-tahap dalam proses simulasi:

ini memberi kesempatan untuk memilih topologi rangkaian dan nilai-nilai komponen. Di tahap ini, tidak ada keuntungan dalam memodelkan komponen rangkaian secara detail. Oleh karena itu komponen dimodelkan sebagai komponen ideal. Desain kontroler dan perilaku dinamis sistem tidak diperlukan dalam tahap awal ini.

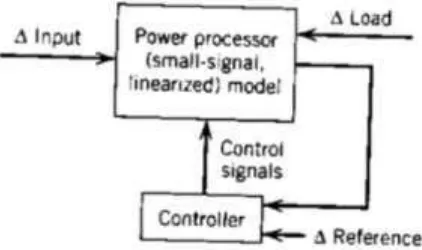

2. Tahap model sinyal kecil (linier) dan desain kontroler. Setelah menentukan topologi rangkaian dan nilai-nilai komponen, prosesor daya dapat dikembangkan menjadi model sinyal kecil (linier) sebagai fungsi transfer. Dalam model ini, saklar-saklar dimodelkan dengan karakteristik rata-ratanya. Setelah model rangkaian menjadi linier, selanjutnya menerapkan desain kontroler untuk memastikan stabilitas dan respon dinamis terhadap gangguan atau perubahan kecil pada input, beban, dan referensi.

Gambar 3.3 Simulasi loop terbuka dengan simulasi sinyal besar [Sumber: (Mohan, Undeland, & Robbins, 2003, hal. 63)]

Gambar 3.4 Model sinyal kecil (linier) dan desain kontroler [Sumber: (Mohan, Undeland, & Robbins, 2003, hal. 63)]

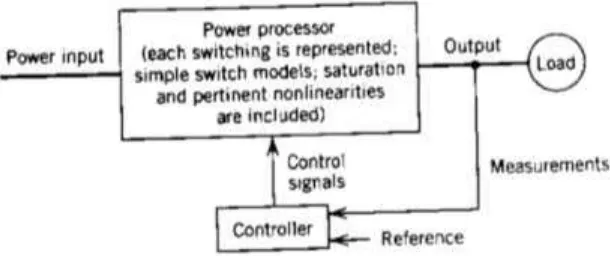

menggabungkan kontroler dan rangkaian pada operasi loop tertutup, dalam merespon gangguan besar seperti perubahan step di sisi beban dan input. Simulasi sinyal besar dilakukan dalam domain waktu di sepanjang waktu yang terdiri dari beberapa (ribuan) siklus penyaklaran. Oleh karena itu, perangkat penyaklaran harus dimodelkan secara sederhana, yaitu sebagai saklar ideal. Namun saturasi, ketidaklinieran, dan rugi-rugi bisa dimasukkan pula dalam model. Rangkaian kontroler dalam simulasi sudah cukup dimodelkan dengan sesederhana mungkin, daripada dimodelkan dengan rinci pada tingkat komponen dengan op-amp, komparator, dan lain-lain.

4. Tahap rincian penyaklaran. Tahap sebelumnya bertujuan untuk mendapatkan perilaku sistem secara menyeluruh yang batasannya hanya dipengaruhi oleh ketidaklinieran komponen semikonduktor. Sedangkan tahap keempat ini bertujuan untuk mendapatkan tegangan berlebih (overvoltages), rugi-rugi daya, dan tekanan-tekanan komponen lainnya dikarenakan tidak idealnya perangkat penyaklaran dan induktansi menyimpang (stray inductances) dan kapasitansi di dalam prosesor daya. Hal ini penting untuk memilih nominal komponen, menilai kebutuhan rangkaian proteksi seperti snubber dan kebutuhan untuk meminimalisir induktansi menyimpang dan kapasitansi (Mohan, Undeland, & Robbins, 2003).

Gambar 3.6 Rincian penyaklaran [Sumber: (Mohan, Undeland, & Robbins, 2003, hal. 64)]

3.4 Blok Diagram Sistem Inverter Fasa Tunggal

Gambar 3.7 Blok Diagram Sistem Inverter Fasa Tunggal yang diajukan

Sistem inverter fasa tunggal yang dibuat merupakan sistem loop tertutup. Sistem loop tertutup diharapkan dapat membuat inverter merespon terhadap gangguan atau perubahan di sisi beban atau perubahan pada nilai referensi (set point), sehingga tegangan output AC inverter memiliki respon transien yang relatif cepat menuju ke nilai set point dan pada keadaan tunak, tegangan output AC yang stabil dan sesuai dengan set point.

Jika input sumber daya DC tidak memiliki karakteristik sumber tegangan ideal (impedansi internal sama dengan nol), maka di sisi input inverter disisipkan tapis input yang fungsinya untuk merendahkan nilai impedansi internal atau memblok/melemahkan frekuensi tegangan diatas nol (karena frekuensi DC adalah nol). Karena hubungan antara kapasitansi (C) dengan impedansi (Z) adalah berbanding terbalik (�� ≈ 1/�), sehingga dengan memasang kapasitor dengan kapasitansi yang relatif cukup besar di sisi input inverter dapat merendahkan nilai impedansi internal.

Inverter fasa tunggal merupakan komponen utama di sistem yang diajukan. Kualitas inverter ditentukan oleh bentuk gelombang output yang dihasilkannya. Berdasarkan bagian 2.3, skema penyaklaran PWM dapat membuat inverter menghasilkan gelombang output sinusoidal PWM (SPWM) yang relatif lebih baik gelombang outputnya dibandingkan skema penyaklaran gelombang kotak, multiple PWM, atau gelombang kotak-quasi (3-level). Topologi inverter yang sesuai dengan skema penyaklaran PWM adalah topologi jembatan penuh.

Gelombang output dari inverter masih berupa sinusoidal PWM yang masih kaya dengan kandungan harmonisa frekuensi tinggi. Diharapkan gelombang tegangan output

adalah “true sine wave”, yaitu mendekati bentuk sinusoidal dengan frekuensi jala-jala 50 Hz. Oleh karena itu di sisi output disisipkan tapis untuk memblok atau melemahkan harmonisa frekuensi tinggi. Topologi tapis yang sesuai untuk memblok frekuensi tinggi adalah tapis low-pass.

Tegangan keluaran dari inverter adalah 12Vac peak-to-peak, sedangkan beban inverter membutuhkan 220Vac rms. Oleh karena itu dibutuhkan trafo untuk menaikkan tegangan dari 12Vac peak-to-peak ke 220Vac rms. Trafo yang digunakan memiliki frekuensi nominal sesuai dengan frekuensi jala-jala, yaitu 50Hz, hal ini untuk menghindari terjadinya permasalahan seperti yang telah dijelaskan pada bab 2.7.4.

Skema penyaklaran PWM membutuhkan dua sinyal input: (1) gelombang sinusoidal sebagai sinyal kontrol, dan (2) gelombang segitiga sebagai sinyal pembawa. Sehingga dibutuhkan pembangkit sinyal sinusoidal dan sinyal segitiga agar rangkaian kontroler bekerja dengan baik.

Karena inverter yang dirancang posisinya sebagai inverter pada UPS, maka diharapkan frekuensi output konstan, memiliki respon transien yang baik, tegangan output yang stabil, dan menghasilkan gelombang output yang baik. Dari bab 2.4, rangkaian kontroler yang sesuai dengan spesifikasi UPS adalah fixed-frequency control dimana frekuensi inverter/sinyal pembawa tidak berubah-ubah. Sedangkan kontrol pita-toleransi lebih sesuai dengan aplikasi driver motor listrik karena frekuensi outputnya yang berubah-ubah.

Driver saklar berfungsi sebagai antarmuka antara rangkaian kontrol dengan rangkaian

inverter, karena tegangan kerjanya berbeda. Setelah pemrosesan sinyal dilakukan oleh rangkaian kontroler, driver saklar menguatkan arus atau tegangan dari rangkaian kontroler untuk menyalakan atau mematikan saklar semikonduktor daya. Selain sebagai antarmuka, driver saklar berfungsi sebagai isolasi antara rangkaian kontrol dan rangkaian inverter.

![Gambar 3.2 Tahap proses simulasi [Sumber: (Mohan, Undeland, & Robbins, 2003, hal. 63)]](https://thumb-ap.123doks.com/thumbv2/123dok/1949327.1592238/2.595.72.481.169.511/gambar-tahap-proses-simulasi-sumber-mohan-undeland-robbins.webp)

![Gambar 3.6 Rincian penyaklaran [Sumber: (Mohan, Undeland, & Robbins, 2003, hal. 64)]](https://thumb-ap.123doks.com/thumbv2/123dok/1949327.1592238/5.595.84.515.260.426/gambar-rincian-penyaklaran-sumber-mohan-undeland-robbins-hal.webp)