CS2624

CS2624 -- COMPUTER COMPUTER

ORGANIZATION & ARCHITECTURE ORGANIZATION & ARCHITECTURE ORGANIZATION & ARCHITECTURE ORGANIZATION & ARCHITECTURE

(COA) (COA)

Rangkaian

Rangkaian Kombinasional

Kombinasional

Rangkaian

Rangkaian Kombinasional

Kombinasional

bagian

bagian 44

bagian

bagian 44

Pokok Bahasan

Pokok Bahasan

Pokok Bahasan

Pokok Bahasan

•

Shifter

–Non-Arithmatic Shifter A ith ti Shift –Arithmatic Shifter•

Programmable Logic Array (PLA)

•

Programmable Logic Array (PLA)

•

Hazard

Hazard

dan

dan

Propagation delay

Propagation delay

Shift Register

Shift Register

(1)(1)Shift Register

Shift Register

(1)(1)Komponen yang digunakan pada beberapa operasi: 1. Penyimpanan data serial

2 Konversi data serial ke parallel dan sebaliknya 2. Konversi data serial ke parallel dan sebaliknya 3. Operasi aritmatika: Left/Right Shifting pada

bilangan tak bertandag

R=Rotate (0=Shift; 1=Rotate) F=Fill (0=0 Fill; 1= S Fill) F=Fill (0=0-Fill; 1= S-Fill) D=Direction (0=Left; 1=Right)

Shift R i t

Shift R i t

Shift Register

Shift Register

(2)(2)f

• m addresses input berfungsi untuk menentukan jumlah posisi bit

yang akan digeser

• D control berfungsi untuk menentukan arah pergeseran ke kiri (D=0) • D control berfungsi untuk menentukan arah pergeseran ke kiri (D 0)

atau ke kanan (D=1)

• F control berfungsi menentukan posisi bit FILL pada output diisi l h bit 0 (F 0) t dii i l h bit SPILL (F 1)

oleh bit 0 (F=0) atau diisi oleh bit SPILL (F=1)

• R control berfungsi untuk menentukan tipe operasi pergeseran (R=0) atau rotasi (R=1)

(R 0) atau rotasi (R 1) Note:

• Untuk Left shifter posisi bit MSB disebut SPILL dan posisi bit LSB disebut FILL

• Untuk Right shifter posisi bit MSB disebut FILL dan posisi bit LSB • Untuk Right shifter posisi bit MSB disebut FILL dan posisi bit LSB

disebut SPILL

• Jika R=1 (active), F dan D control tidak digunakan

20090327 #3

( ) g

N

N

A i h

A i h

i Shif

i Shif

Non

Non--Arithmatic Shifter

Arithmatic Shifter

(1)(1)• Fungsi utamanya adalah untuk melakukan bit SPILL-OFF/ZERO FILL dan operasi rotasi, yaitu “mengalirkan” bit per bit ke ALU

SPILL OFF artinya bit pada posisi SPILL dianggap hilang/tidak • SPILL-OFF artinya bit pada posisi SPILL dianggap hilang/tidak

N

N

A ith

A ith

ti Shift

ti Shift

Non

Non--Arithmatic Shifter

Arithmatic Shifter

(2)(2)• Rotasi ke kanan sebanyak 1 bit:

20090327 #5

N

N

A ith

A ith

ti Shift

ti Shift

Non

Non--Arithmatic Shifter

Arithmatic Shifter

(3)(3)• Contoh 1: Rancanglah sebuah non-arithmatic shifter 4 bit yang mampu melakukan pergeseran atau rotasi ke kiri

sebanyak 2 bit !

N

N

A ith

A ith

ti Shift

ti Shift

Non

Non--Arithmatic Shifter

Arithmatic Shifter

(4)(4)• MEV-nya:

20090327 #7

Non

Non Arithmatic Shifter

Arithmatic Shifter

(5)(5)Non

Non--Arithmatic Shifter

Arithmatic Shifter

(5)(5)Non

Non Arithmatic Shifter

Arithmatic Shifter

(6)(6)Non

Non--Arithmatic Shifter

Arithmatic Shifter

(6)(6)• Solusi untuk contoh 1 dengan modul MUX 8-to-1

20090327 #9

Arithmatic Shifter

Arithmatic Shifter

(1)(1)Arithmatic Shifter

Arithmatic Shifter

(1)(1)• Merupakan unit penggeser (shifter) yang mampu menangani bit tanda (sign)

• Aritmatika pergeseran bit:

– Geser ke kiri 1 bit = perkalian dengan 21

– Geser ke kiri 2 bit = perkalian dengan 22

– Dan seterusnya

– Geser ke kanan 1 bit = pembagian dengan 21

– Geser ke kanan 2 bit = pembagian dengan 22

– Dan seterusnya

• Contoh:

– 00001100 (=12) digeser ke kanan 2 bit (2sr) menjadi 00000011 (=3)

Identik dengan 12 : 4 = 3

– 00001100 (=12) digeser ke kiri 3 bit (3sl) menjadi 01100000 (=96)00001100 ( 12) digeser ke kiri 3 bit (3sl) menjadi 01100000 ( 96)

Arithmatic Shifter

Arithmatic Shifter

(2)(2)Arithmatic Shifter

Arithmatic Shifter

(2)(2)G ki i d i it d d k l 2 • Geser kiri pada sign-magnitude dan komplemen 2

20090327 #11

Arithmatic Shifter

Arithmatic Shifter

(3)(3)Arithmatic Shifter

Arithmatic Shifter

(3)(3)Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (1)(1)

Merupakan salah satu perangkat kombinasional logik yang direpresentasikan

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (1)(1)

Merupakan salah satu perangkat kombinasional logik yang direpresentasikan dalam suatu elemen-elemen array.

Blok diagram PLA:

Jenis-jenis PLA:

– Programmable Logic Array – mask programmable AND and OR planeg g y p g p

– Field Programmable Logic Array (FPLA) – user programmable PLA

– Programmable Array Logic (PAL) – mask programmable AND only

– Field Programmable Array Logic (FPAL) – user programmable PALg y g ( ) p g Dimensi PLA: n x p x m

n = jumlah input (8 – 20)

p = jumlah product term (20 – 80) p = jumlah product term (20 80) m = jumlah output (8 – 20)

20090327 #13

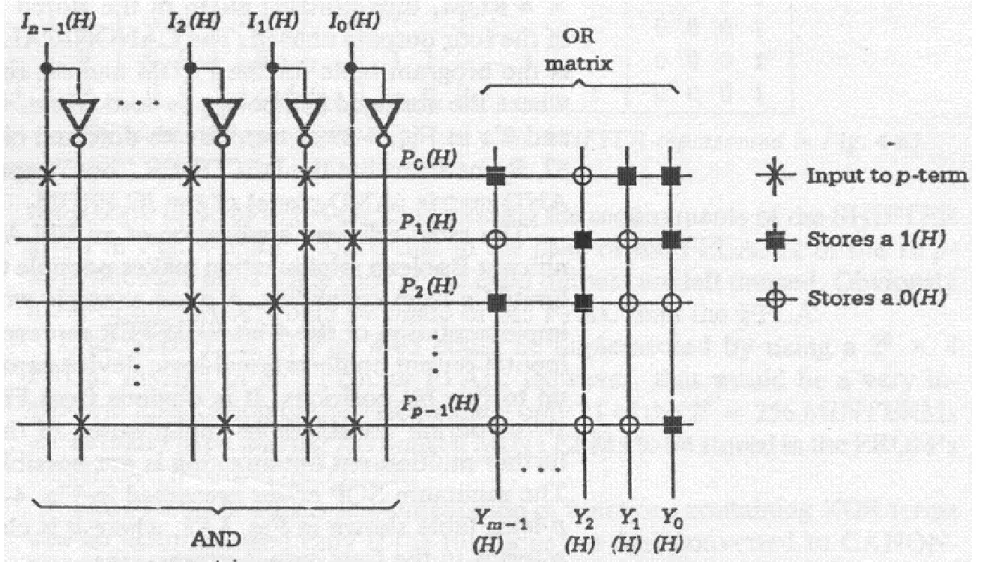

Programmable Logic Array (PLA

Programmable Logic Array (PLA)) (2)(2)

R k i FPLA b l di

Programmable Logic Array (PLA

Programmable Logic Array (PLA) ) (2)(2)

Programmable Logic Array (PLA

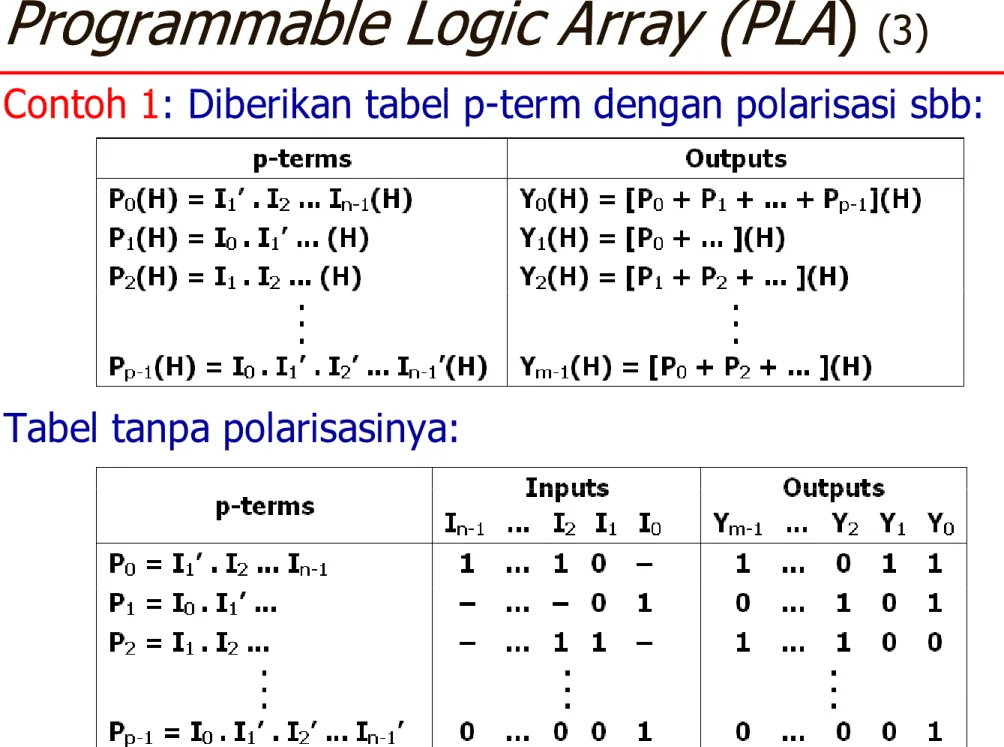

Programmable Logic Array (PLA) ) (3)(3)

C t h 1 Dib ik t b l t d l i i bb

Contoh 1: Diberikan tabel p-term dengan polarisasi sbb:

Tabel tanpa polarisasinya:

20090327 #15

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (4)(4)

G b i b lik k i FPLA

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (4)(4)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (5)(5)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (5)(5)

C t h 2 C t bil 2 bit d PROM d d

Contoh 2: Comparator bilangan 2 bit dengan PROM decoder

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (6)(6)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (6)(6)

C t h 3 T b l t t k hift 4 bit

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (7)(7)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (7)(7)

C t h 3 Si b l t i FPLA 8 16 8 ( t 8 12 4)

Contoh 3: Simbol representasi FPLA 8x16x8 (atau 8x12x4) sebagai non-arithmatic shifter

20090327 #19

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (8)(8)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (8)(8)

C t h 4 Contoh 4:

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (9)(9)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (9)(9)

C t h 5 Contoh 5:

20090327 #21

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (10)(10)

Programmable Logic Array (PLA)

Programmable Logic Array (PLA) (10)(10)

C t h 6 Contoh 6:

Hazards

Hazards Pada Rangkaian KombinasionalPada Rangkaian Kombinasional (1)(1)

Hazards

Hazards Pada Rangkaian Kombinasional Pada Rangkaian Kombinasional (1)(1)

• Terjadi pada saat transisi yang berbeda dari input ke output yang memiliki delay propagasi yang berbeda St ti 1 h d

• Static 1-hazard

– Output rangkaian berubah menjadi 0, padahal h k t d 1

seharusnya konstan pada 1

• Static 0-hazard

O k i b b h j di 1 d h l – Output rangkaian berubah menjadi 1, padahal

seharusnya konstan pada 0

D i h d • Dynamic hazard

– Terjadi jika output berubah 3 kali atau lebih, pada saat output seharusnya berubah dari 0 ke 1 atau saat output seharusnya berubah dari 0 ke 1 atau sebaliknya

Delay Propagasi

Delay Propagasi

dan

dan

Hazard

Hazard

Delay Propagasi

H

d C

H

d C

Hazard Cover

Hazard Cover

(1)(1)d C

d C

Hazard Cover

Hazards

Hazards Pada Rangkaian Kombinasional Pada Rangkaian Kombinasional (2)(2)

1 00 01 11 10 0 AB C 1 00 01 11 10 AB C 1 1 1 1 0 1 1 1 1 1 0 1 BC ' AB f ABBC f AB'BC AC f f ABBC AC To avoid hazards: 20090327 #27 To avoid hazards:

Hazards

Hazards Pada Rangkaian Kombinasional Pada Rangkaian Kombinasional (3)(3)

Kenapa harus perduli dengan hazards? • Rangkaian Kombinasionalg

– don’t care – Rangkaian akan tetap befungsi dengan baik

• Rangkaian Synchronous Sequential

– don’t care – sinyal input tetap dalam keadaan stabildon t care sinyal input tetap dalam keadaan stabil pada saat waktu setup dan waktu hold dari flip-flops

• Rangkaian Asynchronous sequential • Rangkaian Asynchronous sequential

– hazards dapat menyebabkan rangkaian dalam keadaan state yang tidak tepat

keadaan state yang tidak tepat

• Konsumsi Power proportional terhadap jumlah transisi

Hazard

Hazard

Pada

Pada

Output

Output

Hazard

Hazard

Pada

Pada

Output

Output

• Hazard: Kondisi error sementara (glitch) yang muncul pada output

yang muncul pada output • Penyebab:y

– Waktu tunda propagasi gerbang Wakt t nda RC Inte connect

– Waktu tunda RC Interconnect

• Jenis:Jenis:

– Hazard Fungsi – Hazard Logik

H

d

H

d

P d

P d

O t t

O t t

F

F

i

i

Hazard

H

d

P d

O t t

L ik

Hazard

Pada

Output

: Logik

H

d i C

bi ti

l N t

k

H

d i C

bi ti

l N t

k

Hazards in Combinational Networks

Hazards in Combinational Networks

• Apakah itu Hazards pada CM?

– Transisi pada output yang tidak diinginkan (glitches)Transisi pada output yang tidak diinginkan (glitches)

• Contoh

ABC 111 B b b h k 0 – ABC = 111, B berubah ke 0

Pustaka

Pustaka

Pustaka

Pustaka

[TIN91] Tinder, Richard F. 1991. “Digital Engineering

Design : A Modern Approach”. - edition. Prentice Hall.

Pustaka

Pustaka

Pustaka

Pustaka

[TIN91] Tinder, Richard F. 1991. “Digital Engineering

Design : A Modern Approach”. - edition. Prentice Hall.