A. Memori Cache

Memori cache adalah suatu buffer tengah antara CPU dan memori utama. Tujuan memori cache adalah untuk mengurangi waktu tunggu CPU selama pengaksesan memori utama. Pada sistem yang tanpa memori cache, setiap akses memori utama menghasilkan sejumlah waktu tunda dalam pemrosesan intruksi karena waktu akses memori utama yang lebih besar dari preidode clock prosesor. Kecepatan CPU yang tinggi terbuang selama akses memori karena waktu akses memori utama yang besar. Untuk mengurangi waktu tunggu CPU, diperkenalkan sebuah memori yang kevil tetapi ceoat sebagai memori cache yang berada di antara memori utama dan CPU.

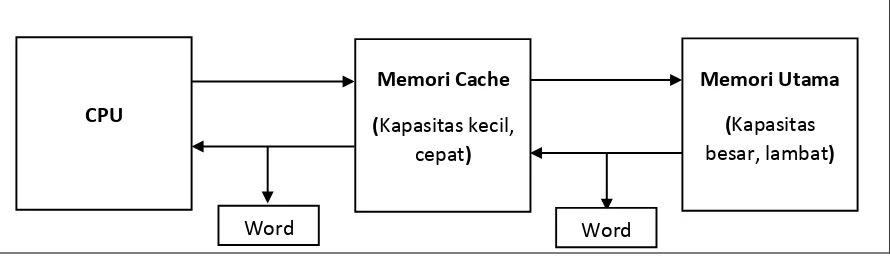

Gambar 4.1 Penggunaan memori cache

Sebagaian program dan data dibawa sebelumnya ke dalam memori cache. Pengontrol cache menjaga lokasi memori utama yang akan disalin pada memori cache pada waktu yang diberikan. Bila CPU memerlukan suatau instruksi atau operand, dia menerimanya dari memori cache (jika tersedia) sebagai penggantinya dari pengaksesan memori utama. Jadi, akses memori selesai dalam waktu yang singkat sehingga memori utama tampak seperti memori cepat. Namun, jika item yang diperlukan tidak terdapat di dalam memori cache, maka akses di lakukan ke memori utama sehingga item dibaca dari memori utama dan diletakan di memori cache. Kapasitas memori chace sangat kecil dibandingkan dengan memori utama. Jika memori cache penuh, maka beberapa item di hapus. Hardware “cache controller”

mengatur semua persyaratan dengan melakukan operasi-operasi yang diperlukan. Transfer antara CPU dan memori cache biasanya satu word dalam bentuk block. Memori cache secara fisik dapat diintegrasikan dengan IC prosessor sebagai cache internal, yang juga dikenal dengan nama on-chip cache.

Operasi cache berdasarkan pada “locality of reference” yang merupakan sifat yang melekat dalam program. Hampir semua waktu, pemrosesan intruksi dan data yang diperlukan tersedia dalam lokasi memori utama tersebut yang secara fisik dekat dengan lokasi memori utama tersebut yang secara fisik dekat dengan lokasi memori utama yang sedang diakses. Ada dua macam pola tingkah laku :

1. Temporal locality : Intruksi yang sedang diambil dapat diperlukan kembali dengan segera. 2. Spatial locality :Intruksi-intruksi yang berdekatan dengan instruksi sekarang dapat diperlukan

segera.

Dari pandangan dua sifat ini, bila pengaksesan memori utama untuk suatu instruksi, sebagai pengganti dari pengambilan suatu intruksi saja darimemori utama, beberapa instruksi berurutan diambil bersama dan disimpan dalam memori cache.

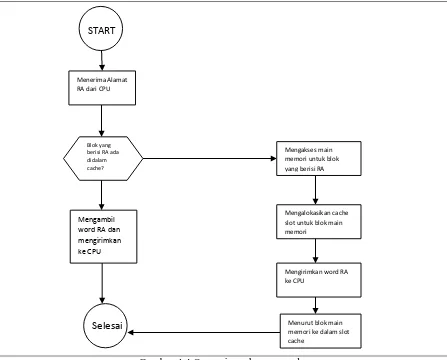

Gambar 4.2 Organisasi memori utama dan memori cache

Secara konseptual memori utama dibagi menjadi banyak blok, setiap blok berisi sejumlah lokasi dari memori utama, isi seluruh blok ditransfer dan disimpan dalam memori cache. Memori cache disusun atas sejumlah bari-baris atau blok dan ukuran setiap baris sama seperti kapasitas blok memori utama. Jumlah blok-blok memori utama lebih banyak dari pada jumlah baris dalam memori cache. Karena itu, satu fungsi digunakan untuk memetakan secara simetris suatu blok memori utama ke salah satu baris cache. Bila suatu blok memori utama disimpan dalam memori cache, maka baris cache (nomor baris) dimana blok harus ditulisi ditentukan dari fungsi pemetaan (mapping function). Dengan cara yang sama, bila CPU membaca dari satu lokasi memori utama, maka cache menggunakan fungsi pemetaan yang mengidentifikasi baris cache dimana blok memori utama disimpan (jika tersedia). Ada tiga metode popular untuk pemetaan memori cache :

1. Pemetaan langsung 2. Pemetaan asosiatif penuh 3. Pemetaan asosiatif set

Secara fungsional, memori cache mempunyai dua bagian yaitu : 1. Memori data cache

2. Memori tag cache

Setiap baris dari memori data cache berisi blok memori. baris tag yang bersesuaikan dalam memori tag cache menunjukan jumlah blok dari blok memori ini. Pola tag adalah suatu bagian alamat memori utama dari blok. Ini berbeda untuk setiap teknik pemetaan (langsung, asosiatif penuh, dan asosiatif set) yang akan dibahas pada bagian berikutnya.

Memori Utama

Blok 0

Blok 1

Panjang word

Lokasi memori

Memori Cache

TAG DATA

Memori

tag cache Memori data cache

Gambar 4.3 Prinsip dasar operasi cache B. Hit dan Miss

Bila CPU mengakses memori utama, pengotrol cache memeriksa memori cache untuk melihat apakah alamat memori sekarang yang dilepaskan oleh CPU dipetakan ke dalam cache. Jika alamat memori sekrang dilepskan oleh CPU dipetakan ke dalam cache. Jika alamat memori yang sekarang dipetakan, item yang diperlukan tersedia dalam memori cache. Keadaan ini disebut “cache hit”. Informasi yang

diperlukan dibaca dari memori cache. Pada sisi lain, jika alamat memori utama yang sekarang tidak ditetapkan dalam memori cache, informasi yang diperlukan tidak tersedia dalam memori cache. Keadaan ini disebut “cache miss”. Karena itu semua blok yang berisi alamat memori utama dikirimkan ke dalam memori cache. Sekarang ada dua cara suplai informasi ke prosessor:

1. Simpan semua blok dalam memori cache pertama dan kemudian baca item yang diperlukan dari memori cache dan suplai ke prosessor.

2. Item yang segera diperlukan dibaca dari memori utama, disuplai ke prosesor dan kemudian disimpan dalam memori cache.

Cache hit yang lebih sering terjadi lebih baik karena setiap terjadi ‘miss’ maka harus dilakukan pengaksesan memori utama. Waktu yang digunakan untuk membawa item yang diperlukan dari memori utama dan menyuplainya ke prosesor disebut ‘miss pinalty’. Hit rate (disebut juga hit ratio) menyediakan bilangan jumlah akses yang dihadapi ‘cache hit’ terhadap jumlah akses yang terjadi. Hit rate bergantung pada faktor-faktor berikut :

1. Ukuran baris memori cache. 2. Kapasitas total memori cache. 3. Fungsi pemetaan yang digunakan.

4. Algoritma penggantian yang digunakan oleh sistem operasi yang memutuskan apakah akan berada dalam memori cache.

5. Jenis program yang dijalankan.

Algoritma penggantian universal yang dapat mengurangi hit rate untuk semua situasi adalah mustahil. Panjang Blok

Pengendalia cache Pemilihan offset

(X,Y)

Alamat memori utama

(X,Y) = data yang diperlukan

X Y

Memori tag cache Memori data cache

Tag

HIT

Gambar 4.4 Operasi pembacaan cache

Gambar di atas menjelaskan tentang operasi pembacaan. CPU membuat alamat word yang akan dibaca (RA). Bila tersimpan dalam cache, maka word akan dikirimkan ke CPU. Sedangkan bila tidak berada dalam cache, blok yang berisi word tersebut disimpan ke dalam cache dan kemudian word dikirimkan ke CPU.

C. Elemen-elemen Rancangan Cache Unsur-unsur rancangan cache yaitu :

1. Ukuran cache : Direct (langsung), Associative (Asosiatif), Set associative (Asosiatif set) 2. Algoritma Penggantian : recently used (LRU), First-in-first-out (FIFO),

Least-frequently-used (LFU), Random.

3. Write Policy : Write throught, Write back, Write once. 4. Ukuran blok

5. Banyaknya cache : Singe atau dua-level, Unified atau split D. Fungsi Pemetaan

a. Pemetaan Langsung

Pada pemetaan langsung, blok memori utama yang ada dipetakan ke suatu baris khusus dalam memori cache. Dengan kata lain, pengontrol cache tidak lah fleksibel dalam penempatan blok memori utama dalam baris-baris memori cache. Pemetaanya dinyatakan sepeti dibawah ini :

j = nomor blok memori utama

m = jumlah saluran yang terdapat di dalam cache

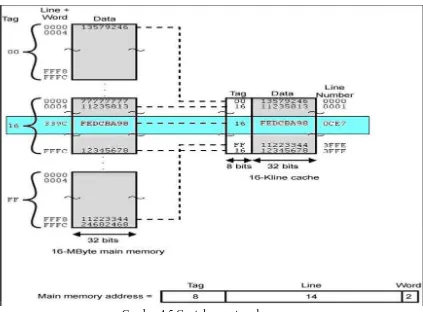

Gambar 4.5 Contoh pemetaan langsung

Alamat memori utama dikelompokkan ke dalam tiga field : TAG, LINE, WORD. Bit-bit dalam filed WORD menunjukan banyaknya WORD dalam blok. Field TAG dan LINE bersama-sama menentukan jumlah blok. Bila prosesor melakukan pembacaan memori utama, pengontrol cache mendapatkan nomor baris cache dari field LINE alamat memori utama. Tag pada baris cache tersebut cocok dengan field TAG pada alamat memori. Sekarang ada dua kemungkinan :

1. Jika dia cocok maka dia adalah HIT, data yang diperlukan tersedia pada cache data pada baris ini. Pembacaan dari baris tersebut dimulai. Word yang diperlukan dalam blok tersebut diseleksi menggunakan filed WORD dalam alamat memori.

2. Jika tag dalam baris cache tidak cocok dengan field TAG dalam alamat memori, maka dia adalah MISS. Karena itu, pengontrol cache melakukan operasi pada memori utama. Semua blok ditransfer dan disimpan dala baris cache tersebut menggantikan blok lama. Memori tag juga diperbarui dengan field TAG dari alamat memori. Word yang diperlukan dikirim ke prosesor.

Berdasarkan teknik pemetaan langsung, memory management unit melakukan transisi alamat yang diberikan oleh prosesor dengan melakukan pembagian alamat menjadi tiga field (field untuk word, blok dan tag ).

mengeluarkan informasi hit atau miss. Kekurangan dari pemetaan langsung adalah tidak fleksibel dalam sistem pemetaan. Blok memori tentu dipetakan pada suatu baris cache yang tetap. Jika dua blok yang sering diakses terjadi untuk dipetakan pada baris cache yang sama (krena alamat memorinya), maka hit ratio yang dihasilkan pada penggantian baris cache yang sering adalah kecil. Hal ini memberikan eksekusi program yang lambat. Namun, masalah ini banyak terjadi hanya pada beberapa jenis program saja.

b. Pemetaan Asosiatif Penuh

Pemetaan asosiatif penuh memperbaiki masalah kekakuan yang terdapat pada pemetaan langsung. Pada pemetaan asosiatif penuh, blok memori dapat dipetakan pada sembarang baris cache. Alamat memori terdiri dari dua field : TAG dan WORD. Field TAG menunjukan nomor blok memori. Bila prosesor melakukan operasi pembacaan memori, pengontrol cache harus mencocokan field TAG dama alamat dengan isi TAD pada semua baris dalam cache. Jika cocok (hit) dengan satu baris tag, aka blok yang tersimpan dalam baris tersebut dibaca dari cache. Jika tidak cocok (miss) dengan semua baris, pengontrol cache mulai operasi pembacaaan memori utama. Blok yang dibaca dari memori utama disimpan pada suatu baris cache jika cache tidak penuh. Jika cache penuh, maka hanya dilakukan penggatian blok yang diperlukan dalam cache. Blok yang harus diganti ditetapkan oleh algoritma penggantian yang digunakan oleh pengontrol cache.

Berdasarkan teknik pemetaa asosiatif penuh, memory management unit melakukan transisi alamat yang diberikan oleh prosesor dengan melakukan pembagian alamat menjadi dua field yaitu (field word dan tag).

Keuntungan teknik pemetaan asosiatif oenih menawarkan fleksibelitas yang tinggi. Suatu blok memori dapat dipindahkan ke sembarang baris cache. Karena itu, penggantian blok cache diperlukan hanya jika cache penuh secara total. Hal ini memberikan kinerja yang lebih baik karena waktu yang dgunakan dalam penggantian berkurang. Tentunya ukuran cache juga mempengaruhi frekuwnsi penggantian. Dalam pemetaan asosiatif penuh, jumlah baris dalam cache tidaklah tetap. Kekuranganya karena dalam implementasi, pemetaan asosiatif penuh merupakan sistem yang mahal. Pengontrol cache menjadi kompleks karena tag semua baris cache dicocokan secara simulta untuk mengurangu delay pengontrolan cache. Dengan kata lain, pencarian paralel semua baris cache dilakukan untuk suatu pole TAG khusus. Hal ini disebut pencarian asosiatif penuh. Suatu memori khusus ‘memori asosiatif’ atau cotent addressable memory digunakan untuk tujuan ini.

c. Pemetaan Asosiatif Set

Pemetaan asosiatif set menggabungkan konsep pemetaan langsung dengan pemetaan asosiatif, untuk memberikan biaya efektif dan kelayakan selama pemetaan yang fleksibel. Jumlah total baris cache dikelompokan ke dalam set yang banyak. Setiap set mempunyai baris jamak (multiple line) dari nomor yang sama. Jika ada/baris dalam setiap set, maka sistem pemetaan dikenal dengan pemetaan asosiatif set I-Way. Dalam suatu set, blok memori dapat ditempatkan dimana saja dalam/baris. Format alamat memori mempunyai tiga field : TAG, SET dan WORD. Khusus field SET menyediakan nomor seri.

Pemetaan asosiatif set memanfaatkan kelebihan-kelebihan pedekatan pemetaan langsung dan pemetaan asosiatif. Dalam kasus ini, cache dibagi menjadi v buah set, yang masing-masing terdiri dari k saluran. Hubungan yang terjadi adalah

m = v x k i = j modulus v

dengan

i = nomor set cache

j = nomor blok memori utama

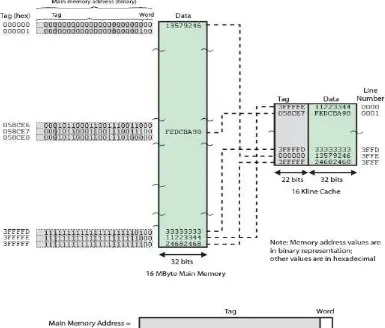

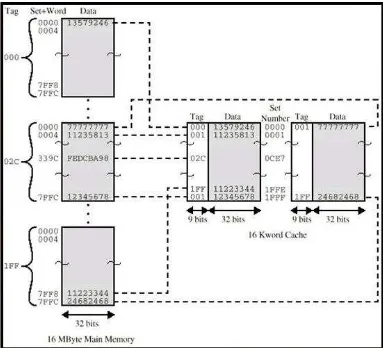

Gambar 4.7 Pemetaan asosiatif set dua arah

Jika prosesor melakukan operasa pembacaan memori, pengontrol cache menggunakan field SET untuk mengakses cache. Dalam set, ada/jumlah baris. Karena itu filed TAG dalam alamat dicocokkan dengan isi tag dalam semua/baris. Pada penerimaan suatu HIT, blok yang bersesuaian dibaca dan word yang diperlukan dipilih. Pada penermaan MISS, blok dibaca dari memori utama dan disimpan dalam set yang ditentukan sebelumnya. Jika cache (set) penuh, maka penggantian salah satu baris dilakukan seperti pada setiap algoritma penggantian. Setiap set seperti sebuah memori cache kecil. jika hanya ada satu set, maka dia sama seperti pemetaan asosiatif. Di sisi lain, jika hanya terdapat satu baris/set, maka dia sama seperti pemetaan langsung.

Berdasarkan teknik pemetaan asosiatif set, memory management unit melakukan translasi alamat yang diberikan oleh prosesor dengan melakukan pembagian alamat menjadi tiga field seperti yang ditunjukkan yaitu (Word, Set dan Tag).

asosiatif set dalam implementasinya, biayanya sangat mahal dari pada pemetaan langsung dan lebih murah dari pada pemetaan asosiatif penuh. Namun, dibandingkan terhadap keuntungan pemetaan asosiatif set. Biaya ini meningkat tidak relevan.

E. Algoritma Penggantian dan Aturan Penulisan Cache

Bila suatu alamat yang di akses oleh CPU tidak dipetakan dalam memori cache, maka pengaksesan dilakukan langsung ke memori utama. Bersama dengan word yang diperlukan, semua blok ditransfer ke memori cache. Anggap memori cache sudah penuh, maka beberapa isi memori cache dihapus untuk membuat ruang bagi entry baru. Porsi memori cache yang dihaous untuk pembuatan ruang bagi entry baru. Porsi memori cache yang dihapus untuk pembuatan ruang bagi entry baru merupakan hal yang penting. Terdapat sejumlah algoritma khusus untuk memaksimalkan hit rate.

a. Algoritma Penggantian

Masalah penggantian adalah suatu hal yang penting bila memori cache penuh dan suatu blok baru dari memori utama harus disimpan dalam memori cache. Jelas keberadaan suatu blok dari memori cache harus diganti dengan blok baru. Pada kasus cache pemetaan langsung, kita tidak punya pilihan. Blok baru harus disimpan hanya dalam suatu baris cache yang ditetapkan per aturan pemetaan untuk cache pemetaan langsung. Untuk pemetaan asosiatif dan pemetaan asosatif set kita memerlukan suatu algoritma yang baik karena kita mempunyai beberapa pilihan. Jika kita menghapus suatu blok yang akan diakses segera oleh CPU, maka terjadi miss penalty. Karena itu, diperlukan suatu keputusan cerdas dari suatu pilihan baris cache yang akan dikosongkan. ALgoritma penggantian tertentu telah dicoba dan dipelajari efesiensinya. Beberapa di antaranya akan dibahas sebagai berikut :

Algoritma Random Choice : Algoritma ini memilih baris cache secara acak tanpa suatu acuan pada frekuensi penggunaan sebelumnya. Algoritma ini diimplementasikan dengan hardware yang sederhana. Walaupun dapat muncul pada suatu algoritma biasa, dia mempunyai efesiensi praktis yang menarik.

Algoritma First-in-First-Out (FIFO): Algoritma ini memilih set yang telah berada pada cache dalam waktu yang lama. Dengan kata lain, blok yang dimasukkan dalam cache pertama didorong keluar pertama. Asumsinya adalah item yang baru saja dimasukkan mungkin yang akan diperlukan.

Algoritma Least Frequently Used (LFU) : Algoritma ini memilih suatu blok yang telah digunakan oleh CPU yang paling sedikit. Asumsinya adalah cara serupa juga mungkin akan terjadi kemudian.

Algoritma Least Recently Used (LRU) : Algoritma ini memilih item yang terlama dalam cache tidak (jarang) digunakan. Asumsinya adalah cara serupa akan berlanjut dan tidak mungkin dibutuhkan segera. Implementasi algoritma ini dapat dilakukan dengan menjajaki sejarah penggunaan item oleh CPU. Penggunaan sebuah pencacah untuk setiap baris adalah merupakan suatu metode sederhana pemenuhan persyaratan.

b. Kebijakan Penulisan Cache

(operand) tidak sedang dipetakan dalam cache, maka jelas hasil akan disimpan di dalam memori utama. Di sisi lain, jika alamat pada saat sekarang dipetakan dalam cache, terdapat dua opsi :

1. Penulisan hasil dalam memori utama dan memori cache. Kebijakan ini dikenal sebagai

write-trhough policy.

2. Penulisan hasil hanya dalam memori cache, tetapi ditandai sebuah flag dalam cache untuk mengingatkan isi memori utama yang bersesuaian adalah usang. Ke depan, kapan saja isi dalam memori cache akan diganti, cukup jika disimpan dalam memori utam pada saat itu. Kebijakan ini dikenal sebagai write-back policy.

Write-Throught Policy sederhana dan implementasinya tidak bertele-tele, tetapi memerlukan satu akses memori utama setiap saat ada keperluan penulisan. Karenanya, hal ini memperlambat eksekusi program. Juga kadang-kadang terjadi bahwa apa yang disimpan dalam memori utama hanyalah suatu hasil sementara (intermediate result) yang segera dibawa ke dalam cache atau diperbarui. Sehingga waktu yang tidak dibutuhkan digunakan dalam penyimpanan item tersebut dalam memori utama. Namun, frekuensi penulisan yang sia-sia tersebut bergantung pada tingkah laku program aplikasi.

Write-Black Policy menghemat waktu karena penulisan dalam memori utama tidak dilakukan pada setiap waktu operasi penulisan. Item tertentu mungkin tidak pernah ditulis dalam memori utama di mana bergantung pada instruksi selanjutnya. Hanya bila item harus dihapus dari cache, dia ditulis ke dalam memori utama. Apakah penghapusan akan terjadi atau tidak, tidak diketahui saat permulaan. Bergantung pada instruksi-instruksi selanjutnya

F. Kinerja Cache dan Hit Rate

Desain memori cache dilakukan karena pertimbangan biaya dan kinerja. Parameter-parameter utama desain memori cache adalah :

1. Kapasitas memori cache : Peningkatan biaya sebanding dengan kapasitas. Dalam kenyataan, ada biaya tambahan yang tak terlihat karena pendekodean dan sirkuit kontrol lainya. Karena itu, diperlukan untuk menjaga kapasitas memori cache sekecil mungkin.

2. Ukuran baris cache (ukuran blok cache) : Jika ukuran baris besar, membantu mengurangi jumlah pengaksesan memori utama. Tetapi ukuran baris yang besar mengurangi jumlah blok yang dapat dimuat dalam memori cache. Karena itu ukuran sebaiknya dipilih setelah studi yang hati-hati dari tingkah laku sifat untuk berbagai ukuran blok.

3. Ukuran set : Jika terdapat baris yang lebih setiap set, hit rate menjadi lebih baik. Tetapi ukuran set yang terlalu besar meningkatkan biaya karena sirkuit bertambah untuk kesesuaian tag.

Hit rate idealnya 1 agar setiap pengaksesan memori utama oleh prosesor dilayani oleh memori cache dan tidak ada akses memori utama yang diperlukan secara keseluruhan. Secara praktis, tidak mungkin hal ini tercapai dan karena itu dicoba hit rate mendekati 1. Desain yang sangat buruk menghasilkan hit rate mendekati 0. Ini artinya pengaksesan memori utama sangat banyak. Hit rate 0 artinya semua hasil pengaksesan memori utama oleh prosesor adalah MISS. Walaupun parameter-parameter desain tertentu membantu dalam pencapaian hit rate mendekati 1, tingkah laku program aplikasi dapat dengan mudah menggangu hit rate. Kinerja sistem rata-rata diberikan oleh kebalikan dari waktu siklus itu rata-rata. Waktu siklus intruksi terdiri atas dua komponen :

1. Waktu aktivitas cache independent selama siklus intruksi