REED-SOLOMON (7,3 )

BERBASIS DIGITAL

TUGAS AKHIR

Diajukan Untuk Memenuhi Salah Satu Syarat Memperoleh Gelar Sarjana Teknik pada Program Studi Teknik Elektro Fakultas Teknik

Universitas Sanata Dharma

Disusun Oleh:

YOACHIM SALA BONGO

NIM : 005114094

PROGRAM STUDI TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

ERROR DETECTING USING REED-SOLOMON

CODE (7.3) BASED ON DIGITAL CIRCUITS

FINAL PROJECT

Presented as Partial Fulfillment of the Requirements To Obtain the Sarjana Teknik Degree

in Electrical Engineering Study Program

By:

YOACHIM SALA BONGO

Student Number : 005114094

ELECTRICAL ENGINEERING STUDY PROGRAM

ELECTRICAL ENGINEERING DEPARTMENT

ENGINEERING FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

2007

DETEKSI GALAT MENGGUNAKAN SANDI

REED-SOLOMON ( 7,3 )

BERBASIS DIGITAL

Disusun oleh:

YOACHIM SALA BONGO NIM : 005114094

Telah disetujui oleh :

Dosen Pembimbing I,

HALAMAN MOTO

“

Buanglah kebodohan maka kamu akan hidup

dan ikutilah jalan pengertian ”

“ GUTTA CAVAT LAPIDEM NON VI SET SAEPE CADENDO ”

HALAMAN PERSEMBAHAN

..

Kupersembahkan karya ini untuk Yesus dan Bunda Maria yang telah

memberiku anugerah yang begitu indah,

...Untuk kedua orang tuaku yang telah membesarkan aku dengan cinta dan

kasih sayang mereka yang begitu besar,

...Kakak dan adikku, serta seluruh saudaraku yang menyayangiku,

… Seluruh teman-temanku yang telah mengisi hari-hariku

Pernyataan Keaslian Karya

Saya menyatakan dengan sesungguhnya bahwa tugas akhir yang saya tulis ini tidak memuat karya atau bagian karya orang lain, kecuali yang telah disebutkan dalam kutipan dan daftar pustaka, sebagaimana layaknya karya ilmiah.

Yogyakarta, Januari 2007 Penulis

INTISARI

Sandi Reed-Solomon (7,3) merupakan sandi pendeteksi dan koreksi kesalahan berbasis blok, yang akan menyandikan runtun pesan sepanjang 3 simbol menjadi runtun kata sandi menjadi 7 simbol dengan 4 simbol paritas. Sandi RS (7,3) mampu mendeteksi galat lebih dari satu simbol dengan maksimal galat 3 bit persimbol tetapi hanya mampu mengoreksi 2 simbol.Penelitian ini hanya akan mengimplementasikan pendeteksi kesalahan saja.

Sistem deteksi sandi RS ( 7,3) terbagi menjadi 3 bagian besar, yaitu rangkaian penyandi, rangkaian pembuat galat dan rangkaian pendeteksi galat atau rangkaian sindrom. Tiga simbol pesan dimasukkan ke dalam rangkaian penyandi melalui saklar geser, selanjutnya diproses oleh rangkaian penyandi sehingga menghasilkan 4 simbol paritas. Hasil dari proses kerja rangkaian penyandi membentuk sebuah katasandi yang selanjutnya dikirimkan ke rangkain sindrom melalui sebuah rangkaian pembuat galat. Bila kita menginginkan bahwa kata sandi yang dikirimkan diberi galat, maka pemberian galat dilakukan pada rangkaian pembuat galat. Rangkaian sindrom akan mendeteksi kata sandi yang diterimanya, apakah ada galat atau tidak ada galat..

ABSTRACT

The Reed-Solomon (7.3) code is a block-based error detecting and correcting code which encodes the messages sequence consist of three codes to be the codeword. This codeword consist of seven codes with four parity symbols. The code can detect more than one error with its three bit error per code maximum, but capable to correct two codes only. This research implements only the error detection.

The framework of detection system of this code consist of three main parts namely the encoder circuit, error generator circuit and the error detector circuit or the syndrome circuit. Three messages are put into the encoder circuit trough the electric switch, then those codes are processed by the encoder circuit resulting in four parity symbols. The result of this process forms a codeword that will be sent to syndrome circuit trough an error generator circuit. Suppose that the codeword is put in with any errors, it should be done on the error generator circuit. The syndrome circuit will detect the codeword accepted whether it has any errors or not.

KATA PENGANTAR

Puji dan syukur penulis panjatkan kehadirat Tuhan Yang Maha Esa yang telah melimpahkan berkat dan rahmat-Nya, sehingga penulis dapat menyelesaikan Tugas Akhir ini yang berjudul “ DETEKSI GALAT MENGGUNAKAN SANDI REED-SOLOMON (7,3) BERBASIS DIGITAL” dengan baik

Tugas akhir ini disusun sebagai salah satu syarat untuk memperoleh gelar Sarjana pada jurusan Teknik Elektro, Fakultas Teknik Universitas Sanata Dharma Yogyakarta. Dalam penyusunannya, banyak pihak yang telah membantu dan memberikan dukungan pada penulis, oleh karena itu penulis ingin mengucapkan terima kasih kepada:

1. Ibu Ir. Th. Prima Ari Setiyani, M.T. sebagai pembimbing I yang senantiasa membagikan ilmu-ilmu dan pengalaman yang dimilikinya dan membantu mengatasi masalah yang di hadapi dalam proses penyusunan tugas akhir ini.

2. Orang tuaku tersayang, bapak Petrus Lelo dan mama Paulina Wini yang tidak pernah berhenti memberikan doa, cinta, kasih sayang, semangat, dan dukungannya.

3. Kakak-kakak dan adikku : Krens Boo dan Eja Napoleon (Mboh Saleh), Ponaan Agung kecil, Mersi Leni, Rini Deka Iko dan Eja Charles, Hans Don Bosco Bheda, terima kasih untuk doa, dukungan, dan semangatnya yang membuat aku bisa menyelesaikan semua ini dan membuat aku tetap berdiri tegar sampai tujuanku tercapai.

Twins Vita dan Vira, Bang Harjono sekeluarga, Mba Wiwik dan Pak Hanes, Mas Joko, Mas Budoyo, Mba Siti, Mas Gunawan, Pa Kijan dan Bu Atun, Bu Tatik dan Pak Giono sekeluarga, Spesial thanks buat Mas Irwan (makasih atas segala bantuannya) dan semua saudaraku yang memberikan doa dan dukungannya.

5. Kekasihku Nur“Si Oneng”, terima kasih untuk semua kasih dan cintamu serta nasehat-nasehatnya.

6. Sahabat-sahabat dekatku : Marcelo Hala Boli, Sendy Limantara, Ignasio Leha, Pa Eko (Raja), Onsha, Enni,Wayan Santra, Hadi Sanjaya, Suryo(Mr.SS), Anan Sila Onang (Si Kambing), Bruno Wanggol, Ferdin Buu (Si Betu), Dus Kopa, Yenni Riwu, dan lain-lain yang telah memberikan doa dan semangatnya.

7. Teman–teman cah Kos Dwi Tunggal : Kak Will, Mas Kris Bucek, Mas Yuli Kajawen, Mas Jhoni , Mas Andri Yamto(Langganan First Blood), Mas Beni (Bentol), Mas Putra, Mas Tomi, Mas Dedi Dores, Mas Komang, Mas Putu, Mas Ardi (Artol), Si Danang Gokong , Mas Gatot , Mas Heston, Mas Koko, Thanks ya atas kebersamaannya (Hidup Dotha All Star…….).

8. Teman–teman seperjuangan angkatan 2000 di Prodi Teknik Elektro yang tidak dapat penulis sebutkan satu persatu.

Semoga Tuhan membalas semua kebaikan yang telah diberikan kepada penulis. Penulis sungguh sangat menyadari bahwa masih banyak kekurangan dalam pembuatan dan penyusunan Tugas Akhir ini, maka dari itu segala saran dan kritik yang bersifat membangun sangat diharapkan penulis.

Yogyakarta, Januari 2007

DAFTAR ISI

HALAMAN JUDUL ………..……….i

HALAMAN PERSETUJUAN ………..…… ii

HALAMAN PENGESAHAN ………...iii

HALAMAN MOTO ………..iv

HALAMAN PERSEMBAHAN ………... v

HALAMAN PERNYATAAN KEASLIAN KARYA ………...vi

INTISARI ……….vii

ABSTRACT ………...viii

KATA PENGANTAR ………...ix

DAFTAR ISI ………..x

DAFTAR TABEL ………...xv

DAFTAR GAMBAR ………xx

BAB I PENDAHULUAN 1.1 Latar Belakang ……….1

1.2 Tujuan Penelitian ………..1

1.3 Manfaat Penelitian ………...2

1.4 Batasan Masalah ………..2

1.5 Metodologi Penelitian ………...2

BAB II DASAR TEORI

2.1 Sandi Reed-Solomon ………4

2.1.1 Penyandian Sandi Reed-Salomon ……….6

2.1.2 Pengawasandi Reed-Solomon………7

2.1.2 1 Menghitung Nilai Sindrom ………7

2.2 Gerbang Logika ………...8

2.2.1 Gerbang AND ………...9

2.2.2 Gerbang OR ………12

2.2.3 Gerbang X-OR ………...10

2.2.4 Gerbang NAND ………..11

2.2.5 Gerbang NOT ………..12

2.3 Pencacah ………...………..12

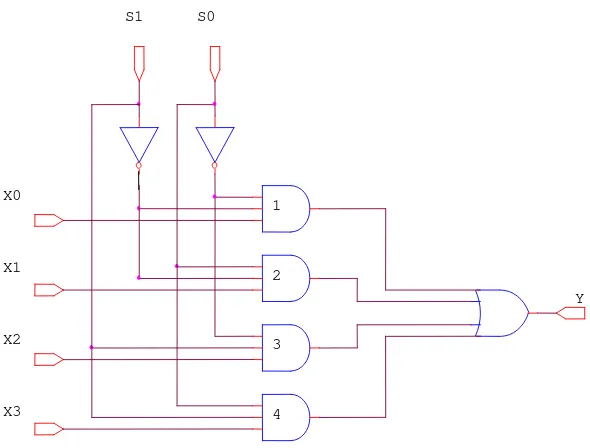

2.4 Multiplexer ………..14

2.5 Register ………...15

2.5.1 Register Geser ( Shift Register ) ……….15

2.6 Saklar ………..17

2.7 LED ( Light Emiting Diode) ………...17

2.8 Penambah ………...….19

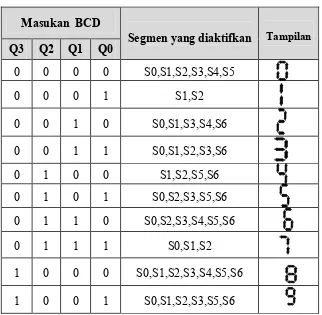

2.9 Penyandi BCD ke Tujuh Segmen ………...19

2.10 Tujuh Segmen ……….20

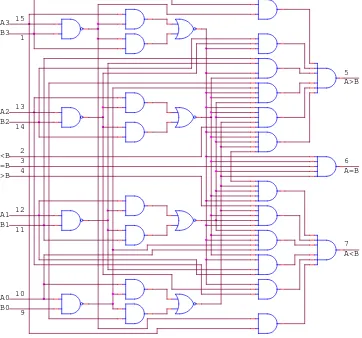

2.11 Pembanding / Comparator ………..22

BAB III PERANCANGAN

3.1 Diagram Blok Penyandian Sandi Reed-Solomon ( 7,3 ) ………27

3.2 Perancangan Rangkaian Penyandi ………..29

3.2.1 Perancangan Rangkaian Gate ……….32

3.2.2 Perancangan Rangkaian Multiplexer ………..34

3.2.3 Perancangan Rangkaian Komparator sebagai pengendali gate dan multiplexer ………. ……36

3.3 Perancangan Pencacah / Counter modulo 7 ………..….39

3.4 Perancangan Rangkaian Pembuat Galat ……….………40

3.4.1 Tampilan Rangkaian Pembuat Galat ………..41

3.4.2 Rangkain Pembuat Galat ……….41

3.5 Perancangan Rangkaian Sindrom ………...………43

3.5.1 Diagram Blok Rangkaian Sindrom ……….………43

3.5.2 Rangkaian Sindrom ……….45

3.5.3 Tampilan Rangkaian Sindrom……….46

BAB IV HASIL DAN PEMBAHASAN 4.1 Analisa Hasil Penyandian ……….………. 48

4.1.1 Percobaan 1 ………...……….48

4.1.2 Percobaan 2 ……….………..…………..54

4.1.3 Percobaan 3 ……….……….……….. 55

4.1.4 Percobaan 4 ………..….. 56

4.1.5 Percobaan 5 ………...…………. 57

4.2.1 Analisa Nilai Sindrom Tanpa Galat ………..……….58 4.2.2 Analisa Nilai Sindrom Dengan Galat ………..……….. 62 BAB V KESIMPULAN DAN SARAN

5.1 Kesimpulan ……….... 78 5.2 Saran ……….………. 78

DAFTAR TABEL

Tabel 2.1 Tampilan himpunan dari GF( 23 ) yang dibangkitkan oleh

polinomial primitive p(X) = 1 + X + X3 ……….5

Tabel 2.2 Daftar macam-macam polynomial ……….5

Tabel 2.3 Tabel kebenaran gerbang logika AND, NAND, OR, XOR ……… 10

Tabel 2.4 Tabel kebenaran gerbang logika NOT ………...………….10

Tabel 2.5 Tabel Kebenaran Pencacah maju Modulus 7 ………...…………13

Tabel 2.6 Tabel kebenaran multiplexer 4 ke 1 ………..……15

Tabel 2.7 Tabel operasi penjumlahan modulo 2 ………...19

Tabel 2.8 Jalur segmen yang aktif ……… ………...20

Tabel 2.9 Tabel kebenaran pembanding (comparator) ……….23

Tabel 3.1 Tabel kebenaran Gate ………...…………33

Tabel 3.2 Tabel kebenaran Multiplexer ………34

Tabel 3.3 Urutan perhitungan modulo 7 ………...39

Tabel 3.4 Tabel kebenaran rangkaian pembuat galat……….41

Tabel 4.1 Hasil percobaan 1 ……….….53

Tabel 4.2 Hasil percobaan 2 ……….……….54

Tabel 4.3 Hasil percobaan 3 ……….….55

Tabel 4.4 Hasil percobaan 4 ………..56

Tabel 4.5 Hasil percobaan 5 ………..57

Tabel 4.6 Hasil Pengamatan Nilai Sindrom Percobaan 1 tanpa galat …...…………59

Tabel 4.8 Hasil Pengamatan Nilai Sindrom Percobaan 3 tanpa galat ..……….60 Tabel 4.9 Hasil Pengamatan Nilai Sindrom Percobaan 4 tanpa galat .………..61 Tabel 4.10 Hasil Pengamatan Nilai Sindrom Percobaan 5 tanpa galat .………..61 Tabel 4.11 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan 1 bit galat

pada posisi 1 ………...………..63 Tabel 4.12 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan 2 bit galat

pada posisi 1. ………64 Tabel 4.13 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan 3 bit

galat pada posisi 1………...………..65 Tabel 4.14 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan 1 bit galat

pada posisi 4 ……….……….…65 Tabel 4.15 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan 2 bit galat

pada posisi 4 ………..66 Tabel 4.16 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan

3 bit galat pada posisi 4 ………..………..67 Tabel 4.17 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan

1 bit galat pada posisi 7 ………..……..67 Tabel 4.18 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan

2 bit galat pada posisi 7 ………..……68 Tabel 4.19 Hasil pengamatan nilai sindrom untuk 1 simbol galat dengan

3 bit galat pada posisi 7 ………...……….69 Tabel 4.20 Hasil pengamatan nilai sindrom untuk 2 simbol galat dengan 1 bit galat

Tabel 4.21 Hasil pengamatan nilai sindrom untuk 2 simbol galat dengan 2 bit galat pada posisi1 dan posisi 2 ……….……..72 Tabel 4.22 Hasil pengamatan nilai sindrom untuk 2 simbol galat dengan 3 bit galat

pada posisi 1 dan posisi 2 ………..73 Tabel 4.23 Hasil pengamatan nilai sindrom untuk 3 simbol galat dengan 1 bit galat

pada posisi 1 ,2 dan 3 ……….………..75 Tabel 4.24 Hasil pengamatan nilai sindrom untuk 3 simbol galat dengan 2 bit galat pada posisi 1 ,2 dan 3 ………..76 Tabel 4.25 Hasil pengamatan nilai sindrom untuk 3 simbol galat dengan 3 bit galat

pada posisi 1 ,2 dan 3 ………...………77

DAFTAR GAMBAR

Gambar 2.1 Diagram Penyandian sandi RS (n,k) ………..………..6

Gambar 2.2 Rangkaian pembangkit sindrom sandi RS ………...8

Gambar 2.3 Simbol gerbang AND ………..…9

Gambar 2.4 Simbol gerbang OR ………..………10

Gamabr 2.5 Simbol logika gerbang X-OR ……….………11

Gambar 2.6 Simbol gerbang logika NAND ………...………11

Gambar 2.7 Simbol logika NOT ………12

Gambar 2.8 Rangkaian Pencacah maju Modulus 7 ………...…13

Gambar 2.9 Multiplexer 4 ke 1 ………..14

Gambar 2.10 Register geser 4 bit masukan seri – keluaran parallel ………16

Gamar 2.11 Saklar ……….17

Gambar 2.12 Simbol LED ………...………18

Gambar 2.13 Rangkaian LED ……….…18

Gambar 2.14 Untai penampil tujuh segmen ………21

Gambar 2.15 Penampil tujuh segmen ………..22

Gambar 2.16 Tujuh segmen dalam digit decimal ………22

Gambar 2.17 Rangkaian pembanding besaran ………23

Gambar 2.18 IC 74LS85 ………..24

Gambar 2.19 Gambar rangkaian dari komparator IC 74LS85 ……….24

Gambar 3.1 Diagram kotak sistem Sandi RS (7,3) ………...………27

Gambar 3.2 Diagram kotak penyandi sandi RS(7,3) ………...………. 30

Gambar 3.3 Gambar bentuk rangkaian persamaan 3-4……….31

Gambar 3.4 Gambar bentuk rangkaian persamaan 3-5……….32

Gambar 3.5 Rangkaian digital Gate ………..33

Gamabr 3.6 Rangkaian lengkap Gate ………...…33

Gambar 3.7 Rangkaian multiplexer ……….. ………35

Gambar 3.8 Gambar Rangkaian lengkap multiplexer ………36

Gambar 3.9 Diagram pewaktuan kendali sandi RS (7,3) …….……….36

Gambar 3.10 Rangkaian Komparator ……….…….37

Gambar 3.11 Rangkaian penyandi sandi RS (7,3) ………...38

Gambar 3.12 Gelombang keluaran counter modulo 7 ……….39

Gambar 3.13 Rangkaian pencacah maju modulo 7 ……….40

Gambar 3.14 Tampilan rangkaian Pembuat Galat ……….41

Gambar 3.15 Rangkaian pembuat galat ………...42

Gambar 3.16 Diagram Penghitung Sindrom sandi RS (7,3) ………44

Gambar 3.17 Rangkaian penghitung sindrom sandi RS (7,3) ……….46

BAB I

PENDAHULUAN

1.1

Latar Belakang

Seiring dengan perkembangan teknologi yang kian pesat, dunia komunikasi juga mengalami perkembangan yang luar biasa. Dalam dunia komunikasi, manusia tidak lagi dibatasi oleh jarak dan waktu.

Untuk berkomunikasi, manusia menggunakan berbagai alat bantu, seperti telephone, faximile, hand phone, email dan lain sebagainya. Semua sistem ini melakukan proses transmisi data guna menyampaikan informasi. Proses perpindahan data terjadi pada banyak sistem. Pada saat data digital ditransmisikan melalui saluran dalam sebuah sistem komunikasi atau saat perekaman data oleh media penyimpan dalam sistem komputer, data digital berpindah dari sumber data ke tempat tujuan. Dalam proses transmisi data, sering terjadi kesalahan (galat) yang menyebabkan data yang diterima oleh penerima tidak sesuai dengan pesan dari sumber atau pengirim. Terjadinya kesalahan ini tergantung pada media transmisi yang sangat peka terhadap derau dan interferensi, sehingga perlu dicari suatu sandi yang dapat mendeteksi dan mengoreksi kesalahan tersebut sehingga data yang dikirim dapat diterima secara benar dan sesuai.

1.2 Tujuan Penelitian

1.3 Manfaat Penelitian

Dengan dilaksanakannya penelitian ini maka diharapkan dapat memberikan pengetahuan mengenai prinsip dasar dari pengkodean dengan menggunakan

sandi Reed-Solomon. Hasil penelitian ini diharapkan dapat digunakan sebagai prototipe dan dasar pengembangan implementasi sandi RS dari GF(23) dengan koreksi galat ganda baik yang bersifat acak maupun hamburan.

1.4

Batasan Masalah

Alat yang akan dibuat dibatasi : 1. Sebuah rangkaian penyandi RS (7,3) 2. Sebuah rangkaian sindrom

3. Sebuah rangkaian pembangkit galat

1.5

Metodologi Penelitian

Untuk dapat merencanakan dan membuat peralatan sistem ini, diperlukan langkah-langkah sebagai berikut :

1. Mencari dan mempelajari literatur tentang permasalahan yang ada, cara kerja dan sekaligus cara-cara merencanakan dalam membuat peralatan tersebut.

2. Perancangan peralatan menggunakan teori yang ada untuk mendapatkan karakteristik yang sesuai dengan spesifikasi yang ditentukan.

1.6 Sistematika Penulisan

Penulisan laporan penelitian tugas akhir ini disusun dengan menggunakan sistematika sebagai berikut :

BAB I PENDAHULUAN

Pendahuluan berisi judul, latar belakang masalah, tujuan, manfaat, batasan masalah, metodologi penelitian dan sistematika penulisan.

BAB II DASAR TEORI

Bab ini berisi dasar-dasar teori yang digunakan dalam pembuatan rangkaian digital pendeteksi galat menggunakan sandi Reed-Solomon (7,3) dan penjelasan masing-masingnya.

BAB III PERANCANGAN PERANGKAT KERAS

Bab ini berisi tentang penjelasan perancangan perangkat keras rangkaian digital pendeteksi galat menggunakan sandi Reed-Solomon (7,3) yang meliputi spesifikasi sistem dan cara kerja rangkaian.

BAB IV PENGUJIAN DAN PEMBAHASAN

Pada bab ini berisi analisis dan pembahasan mengenai hasil penelitian yang telah dilaksanakan.

BAB V PENUTUP

Pada bab ini berisi kesimpulan hasil penelitian yang telah dilakukan dan saran yang berisi ide-ide untuk perbaikan atau pengembangan terhadap penelitian yang telah dilakukan. DAFTAR PUSTAKA

BAB II

DASAR TEORI

2.1

Sandi Reed-solomon

Sandi Reed-Solomon (RS) pertama kali dipublikasikan oleh Irving Reed dan Gustave Solomon sekitar tahun 1960. Sandi ini didasarkan pada perhitungan matematis yang dikembangkan oleh Evariste Galois, seorang ahli matematika dari Perancis pada tahun 1830. Pada tahun 1976, seorang ahli matematika E. Berlekamp menemukan metode pengawasan sandi yang efisien. Sandi RS digunakan pada sistem komunikasi modern, jaringan komputer dan sistem penyimpan magnetis karena keunggulannya dalam mengoreksi banyak galat , baik akibat gangguan yang bersifat random maupun hamburan.

Sandi Reed-Solomon merupakan sandi tak biner yang elemen-elemennya membentuk suatu medan hingga (finite field) yaitu medan yang anggota-anggotanya terbatas. Medan ini lebih dikenal sebagai medan Galois (GF). Setiap GF(q) mempunyai sedikitnya sebuah elemen primitif. Elemen primitif yang biasanya diberi simbol α, mempunyai sifat adalah bahwa semua elemen lain dalam medan, kecuali nol, dapat diekspresikan sebagai bentuk pangkat dari α .

GF(2m) merupakan medan hingga yang terdiri dari 2m elemen dengan m adalah bilangan bulat positif dengan anggota himpunan F sebagai berikut :

F = {0,1, α, α2, ….., α2m−2} ……….. ..(2-1)

penjumlahan. Tabel 2.1 juga memperlihatkan bentuk m-tuple untuk anggota F dari GF(23) yang dibangkitkan oleh polinomial p(X) = 1 + X +X3

Tabel 2.1 Tampilan himpunan dari GF( 23 ) yang dibangkitkan oleh polinomial primitif p(X) = 1 + X + X3

Representasi Pangkat Representasi Polinomial Representasi m-tuple Simbol Oktal 0 1 α α2 α3 α4 α5 α6 0 1 α α2 1+ α α + α2 1 + α + α2 1 + α2

( 0 0 0 ) ( 1 0 0 ) ( 0 1 0 ) ( 0 0 1 ) ( 1 1 0 )

( 0 1 1 ) ( 1 1 1 )

( 1 0 1 )

0 1 2 4 3 6 7 5

Daftar polinomial primitif untuk setiap tingkatan m dapat dilihat pada Tabel 2-2.

Tabel 2.2 Daftar polinomial primitif

m Polinomial M Polinomial 3 3

1+X + X 14 1+X +X6+X10 +X14 4 4

1+X + X 15 1+X +X15 5 2 5

1+X +X 16 1+X +X3 +X12 +X16 6 6

1+X +X 17 1+X3+X17 7 3 7

1+X +X 18 1+X7 +X18 8 2 3 4 8

1+X +X +X +X 19 1+X +X2 +X5 +X19 9 4 9

1+X +X 20 1+X3+ X20 10 3 10

1+X +X 21 1+X2 +X21 11 2 11

1+X +X 22 1+X + X22 12 1+X + X4 +X6 +X12 23 1+X5+ X23

13 3 4 13

1

b b2t−2 b2t−1 2

b

0

b

0

g g1 g2 g2t−2 g2t−1

2.1.1 Penyandian Sandi Reed-Salomon

Penyandian merupakan proses penambahan sejumlah simbol paritas pada simbol pesan. Sebuah sandi RS (n,k) dengan simbol dari GF(2m) mempunyai

parameter-parameter: : n = 2m – 1 : panjang sandi ( pesan + cek paritas )

k = n - 2t : panjang pesan ( t = galat yang dapat dikoreksi) n – k = 2t : panjang cek paritas

dmin = 2t+1 : jarak minimum antara sandi

Sandi RS merupakan sandi blok linear yang bersifat siklis. Pada sandi blok, runtun simbol pesan dibagi ke dalam blok-blok pesan dengan panjang yang tetap. Masing –masing blok pesan dinyatakan dengan u(X) yang terdiri dari k simbol pesan sehingga total ada 2k pesan berbeda. Penyandi kemudian akan menambah pesan u(X) tersebut dengan sejumlah simbol paritas sehingga menjadi kata sandi c(X) yang terdiri dari n-tuple simbol dari GF(2m) dengan n>k. Dengan demikian jika ada 2k pesan, maka akan ada 2k kata sandi.

Penyandi RS (n,k) menggunakan rangkaian register geser dengan menggunakan flip-flop. Gambar rangkaian penyandi RS (n,k) secara umum bisa dilihat pada Gambar 2.1 .

2.1.2 Pengawasandi Reed-Solomon

2.1.2.1 Menghitung Nilai Sindrom.

Saat proses pengiriman c(X) ada kemungkinan terjadi gangguan pada media transmisi dan timbul galat, sehingga symbol r(X) yang diterima menjadi tidak sama dengan c(X). Dengan demikian langkah pertama proses pengawasandi adalah menentukan apakah r(X) sama dengan c(X) atau tidak, dengan cara menghitung nilai sindrom S.

Sandi RS dengan kemampuan mengoreksi t galat akan mempunyai 2t sindrom yaitu S = (S1, S2, . . . . , S2t). Jika representasi polinomial c(X) dan r(X) dituliskan

sebagai berikut :

c(X) = c0 + c1X + ……+cn-1Xn-1 ………...(2-2)

r(X)= r0 + r1X + …….+rn-1Xn-1 ………...(2-3)

maka sindrom dapat diperoleh dengan mensubtitusi αi kedalam r(X) sehingga diperoleh: Si = r( αi )

=

∑

= v

l jl

e

1

α(jl)i

= r0 + r1αi + r2α2i + ….+ rn-1α(n-1)i .………..(2-4)

+ x

Register j

α

Data yang diterima SindromSj

Sindrom Si juga bisa dihitung dari hasil pembagian antara r(X) dengan x + αi sebagai

berikut :

r(X) = Ci (X) (X + α ) + bi .………..(2-5)

dengan Ci (X) adalah hasil bagi dan bi merupakan sisa hasil bagi. Jika X disubsitusikan

dengan αi akan diperoleh :

r(αi) = Ci (α) (αi + αi ) + bi .………..(2-6)

= bi

Jadi Si = r(αi) = bi .………..(2-7)

Sindrom merupakan sisa pembagian dari polinomial kata sandi yang diterima r(X) dengan polinomial pembangkit g(X). Idealnya, jika tidak ada kesalahan, maka hasil pembagian antara r(X) dengan g(X) menghasilkan nilai nol. Jika nilai sindrom tidak bernilai nol, maka hal ini mengindikasikan adanya galat pada data yang diterima. Rangkaian sindrom secara umum digambarkan pada Gambar 2.2 .

Gambar 2.2 Rangkaian pembangkit sindrom sandi RS

2.2 Gerbang Logika

gerbang logika biner. Tegangan yang digunakan dalam gerbang logika adalah tinggi (high) atau rendah (low). Tegangan tinggi berarti biner 1 sedangkan tegangan rendah berarti biner 0. Harus kita ingat bahwa gerbang logika merupakan rangkaian elektronika. Rangkaian ini hanya tanggap terhadap tegangan tinggi (yang disebut satuan) atau tegangan rendah (tegangan tanah) yang disebut nol.

Semua sistem digital disusun hanya menggunakan tiga gerbang logika dasar. Gerbang-gerbang dasar ini disebut gerbang AND, gerbang OR dan gerbang NOT.

2.2.1 Gerbang AND

Gerbang AND digunakan untuk menghasilkan logika 1 jika semua masukan mempunyai logika 1. Jika tidak maka akan menghasilkan logika 0.

1 2

3

A

B

Y

Gambar 2.3 Simbol gerbang AND

Simbol logika standar untuk gerbang AND digambarkan pada Gambar 2.3. Simbol ini menunjukkan masukan sebagai A dan B, sedangkan keluaran dinyatakan sebagai Y. Simbol tersebut merupakan simbol untuk suatu gerbang AND 2-masukan. Tabel kebenaran untuk gerbang AND 2-masukan ini ditunjukkan pada Tabel 2-3. Masukan-masukan ditunjukkan sebagai digit biner (bit). Pernyataan logika untuk rangkaian logika pada Gambar 2.3 adalah:

1 2

3 Y

A

B

Tabel 2.3 Tabel kebenaran gerbang logika AND, NAND, OR, XOR Masukan Keluaran A B AND NAND OR XOR

0 0 0 1 0 0 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 1 0

Tabel 2.4 Tabel kebenaran gerbang logika NOT Masukan A Keluaran Y

0 1

1 0

2.2.2 Gerbang OR

Gerbang OR akan memberikan keluaran 1 jika salah satu dari masukannya pada keadaan 1. Jika diinginkan keluaran bernilai 0, maka semua masukan harus dalam keadaan 0.

Gambar 2.4 Simbol gerbang OR

Simbol logika standar untuk suatu gerbang OR digambarkan pada Gambar 2.4. Tabel kebenaran untuk gerbang OR 2-masukan ditampikan pada Tabel 2.3. Dalam aljabar Boolean, persamaan untuk gerbang OR dapat ditulis sebagai berikut :

A+B = Y ………..(2-9)

2.2.3 Gerbang

X-OR (Exclusive-OR)

A

B Y

A

B

Tabel tersebut dapat dilihat bahwa keluaran pada gerbang XOR merupakan penjumlahan biner dari masukannya. Simbol logika gerbang X-OR dua masukan dapat dilihat pada Gambar 2.5

Gambar 2.5 Simbol logika gerbang X-OR

Dalam aljabar Boolean, persamaan untuk gerbang X-OR dapat ditulis sebagai berikut : Y = A⊕B ……….(2-10)

2.2.4 Gerbang

NAND

Gerbang NAND adalah gerbang logika dasar digital yang hanya akan memberikan keluaran rendah (logika 0) bila kedua masukannya tinggi (logika 1). Pada Gambar 2.6 memperlihatkan simbol gerbang NAND.

Gambar 2.6 Simbol gerbang logika NAND Pernyataan Boolean untuk gerbang NAND adalah sebagai berikut:

8 9

Keluaran akan menjadi rendah ( logika 0 ) hanya bila kedua masukan A dan B adalah tinggi ( logika 1 ). Biner 0 menyatakan tegangan rendah dan biner 1 menyatakan tegangan tinggi.

2.2.5 Gerbang

NOT

Gerbang NOT merupakan gerbang satu masukan yang berfungsi sebagai pembalik (inverter). Jika masukannya tinggi, maka keluarannya rendah, dan sebaliknya. Tabel kebenaran dari gerbang NOT tersaji pada Tabel 2.4. Gerbang NOT disimbolkan seperti pada Gambar 2.7

Gambar 2.7 Simbol logika NOT

Aljabar Boolean untuk gerbang NOT adalah sebagai berikut :

Y = A ………(2-12)

2.3 Pencacah

Dalam elektronika digital, pencacah merupakan rangkaian yang sangat penting yang berguna sebagai logika pengurut. Pencacah digital mempunyai karakteristik yang penting yaitu:

1. Modulus pencacah/ jumlah hitungan maksimum. 2. Menghitung ke atas atau ke bawah.

Clock Vcc Preset

J CLK K

Q

Q

PR

CL

J CLK K

Q

Q

PR

CL

LED B LED C

J CLK K

Q

Q

PR

CL

LED A

Pencacah digital hanya akan mencacah atau menghitung dalam kode biner dimana akan menghitung 000 sampai 111 untuk 3 bit. Perhitungan jumlah maksimum dari pencacah disebut modulus. Modulus dari suatu pencacah adalah jumlah hitungan yang dilaluinya. Gambar 2.8 adalah contoh pencacah modulo-7 dengan menggunakan JK flip-flop. Hitungan setelah cacahan ke-6 akan kembali ke nilai awal lagi.

Gambar 2.8 Rangkaian Pencacah maju Modulus 7

Tabel 2.5 Tabel Kebenaran Pencacah maju Modulus 7

Clock C B A

0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 0 0 0

Keluaran dari gerbang NAND akan terhubung dengan clear pada masing-masing flip flop. Dengan demikian setelah clock ke- 7 tiba semua flip flop akan direset.

2.4 Multiplexer

Multiplexer merupakan suatu selektor data dengan satu keluaran dan banyak masukan. Multiplexer bekerja untuk memilih salah satu dari beberapa (n) masukan data, guna dikirimkan melalui satu saluran saja. Multiplexer dibangun menggunakan beberapa gerbang logika dasar. Contoh sederhana multiplexer 4 ke 1 ditunjukkan pada Gambar 2.9

Gambar 2.9 Multiplexer 4 ke 1

0

S danS1digunakan untuk menyeleksi masukan mana yang akan dikeluarkan melalui keluaran Y. Misalnya jika masukan 00 ke S0dan S1, maka gerbang AND yang terhubung dengan logika 1 dari selektor adalah gerbang 1. Sehingga keluaran dari gerbang 1 akan sama seperti masukannya yaitu X0, sedangkan keluaran dari gerbang 2, gerbang 3, dan

S1

1

2

3

4

Y S0

X0

X1

X2

gerbang 4 akan bernilai logika 0. Kemudian keluaran dari gerbang-gerbang tersebut di OR kan sehingga didapat keluaran Y = X0. Untuk lebih jelasnya terdapat dalam Tabel 2.6

Tabel 2.6 Tabel kebenaran multiplexer 4 ke 1 Selektor

Masukan S0 S1

Keluaran (Y) X0, X1, X2, X3

X0, X1,X2, X3

X0, X1, X2, X3

X0, X1, X2, X3

0 0 1 1

0 1 0 1

X0

X1

X2

X3

2.5 Register

2.5.1 Register Geser (

Shift Register)

Register geser berfungsi untuk menggeser data baik itu ke kiri maupun ke kanan dan juga sebagai penyimpanan data sementara. Elemen penyimpan dasar adalah flip-flop. Setiap flip-flop menyimpan sebuah bit data. Sehingga, untuk menyimpan data n-bit, diperlukan n buah flip-flop yang tersusun sedemikian rupa dalam bentuk register geser. Data biner dapat dipindahkan secara seri atau paralel. Dalam mode seri, bit-bit dipindahkan secara berurutan satu persatu: b0, b1, b2, dan seterusnya. Dalam mode

paralel, bit-bit dipindahkan secara serempak sesuai dengan cacah jalur paralel ( empat untuk empat bit ) secara sinkron dengan sebuah pulsa dari sistem detak. Ada empat kategori register geser yaitu :

Clear Clock Data Seri

D CLK

Q CL

D CLK

Q CL

D CLK

Q CL

D CLK

Q CL

A B C D

D C

B A

3. Paralel masuk, seri keluar. 4. Paralel masuk, paralel keluar.

Tampilan Register geser 4 bit dapat dilihat pada Gambar 2.10.

Gambar 2.10 Register geser 4 bit masukan seri – keluaran parallel

Pada register geser serial masuk paralel keluar, data MSB dimasukkan terlebih dahulu. Saat pulsa clock pertama tiba, maka flip flop A akan terisi data MSB. Ketika pulsa clock kedua tiba, maka flip flop B akan terisi data flip flop A dan flip flop A akan terisi oleh data masukan berikutnya. Ketika pulsa clock ketiga, tiba maka flip flop C akan terisi oleh data flip flop B dan flip flop B akan terisi oleh data flip flop A dan flip flop A akan terisi oleh data masukan berikutnya. Ketika pulsa clock keempat tiba, maka flip flop D akan terisi data pada flip flop C, flip flop C akan terisi data flip flop B, flip flop B akan terisi data flip flop A dan flip flop A akan terisi data masukan berikutnya.

2.6 Saklar

Saklar merupakan perangkat yang digunakan untuk mendefinisikan suatu masukan, sebagai pemilih data mana yang akan dikirimkan terlebih dahulu pada rangkaian multiplexer dan sebagai pemberian galat. Pada saklar, apabila tombol dibiarkan off yaitu saat posisi tombol saklar menuju ke bawah, maka nilainya adalah 0. Jika tombol on yaitu saat tombol saklar menuju ke atas, maka terhubung ke tegangan masukan yaitu 5 V dan bisa dikatakan bahwa saklar berlogika 1.

(a) (b)

Gambar 2.11 Saklar

Saklar pada Gambar 2.11 (a) menunjukkan bahwa saklar akan on jika kaki 1 dan kaki 2 terhubung. Gambar 2.11 (b) menunjukkan bahwa saklar akan on jika kaki 2 dan kaki 3 terhubung.

2.7 LED (

Light Emiting Diode)

LED (Light Emitting Dioda) merupakan dioda yang dapat mengeluarkan emisi cahaya. LED merupakan produk temuan lain setelah dioda. Strukturnya juga sama dengan dioda. Untuk mendapatkan emisi cahaya pada semikonduktor, doping yang dipakai adalah galium, arsenic dan phosporus. Jenis doping yang berbeda menghasilkan warna cahaya yang berbeda pula. Simbol LED ditunjukkan pada Gambar 2.12.

s led cc

R V V

I = −

Gambar 2.12 Simbol LED

LED sering dipakai sebagai indikator yang masing-masing warna bisa memiliki arti yang berbeda. Menyala, padam dan berkedip juga bisa berarti lain. LED dalam bentuk susunan (array) bisa menjadi display yang besar. Dikenal juga LED dalam bentuk tujuh segmen atau ada juga yang 14 segmen. Biasanya digunakan untuk menampilkan angka numerik dan alphabet. Kecerahan LED tergantung dari arusnya. Dalam hal ini arus LED diberikan oleh :

...(2-13) Arus yang dibutuhkan LED sekitar 10mA – 20mA, dan tegangan yang dibutuhkan untuk menghidupkan LED antara 1 volt sampai 2 volt. Agar LED yang digunakan dapat menyala, maka diberikan suatu pembatas arus yang melewati LED yaitu dibatasi dengan resistor. Resistor dapat dipasangkan secara seri dengan LED seperti ditunjukkan pada Gambar 2.13.

LED R

VCC

s Iled

2.8 Penambah

Penambah berfungsi untuk menambahkan bit pada pengawasandi dan deteksi galat. Hasil penambahan kemudian dimasukkan dalam register yang kemudian akan menjadi isi register. Operasi penjumlahan modulo-2 dilambangkan dengan tanda ⊕. Dalam medan biner, aturan untuk penjumlahan ditunjukkan dalam Tabel 2.7.

Tabel 2.7 Tabel operasi penjumlahan modulo 2

Penjumlahan 0 ⊕ 0 = 0 0 ⊕ 1 = 1 1 ⊕ 0 = 1 1 ⊕ 1 = 0

Bila dilihat dari Tabel 2.7 maka operasi penjumlahan modulo-2 dapat menggunakan gerbang XOR.

2.9 Penyandi BCD ke Tujuh Segmen

S1, S3, S4, S6 akan diset berlogika satu untuk menghidupkan LED yang sesuai dengan segmen S0, S1, S3, S4, S6. Jalur yang lain tetap berlogika nol. Tabel 2.8 menunjukkan jalur-jalur yang harus diaktifkan untuk membentuk karakter yang dimaksud.

Tabel 2.8 Jalur segmen yang aktif

Masukan BCD Q3 Q2 Q1 Q0

Segmen yang diaktifkan Tampilan

0 0 0 0 S0,S1,S2,S3,S4,S5 0 0 0 1 S1,S2 0 0 1 0 S0,S1,S3,S4,S6 0 0 1 1 S0,S1,S2,S3,S6 0 1 0 0 S1,S2,S5,S6 0 1 0 1 S0,S2,S3,S5,S6 0 1 1 0 S0,S2,S3,S4,S5,S6 0 1 1 1 S0,S1,S2 1 0 0 0 S0,S1,S2,S3,S4,S5,S6 1 0 0 1 S0,S1,S2,S3,S5,S6

2.10 Tujuh Segmen

Common

S

S S S S S

Common

S

S S S S S

dengan yang lain. Pada common anoda, anoda dari ketujuh LED terhubung menjadi satu (Gambar 2.14a) sedangkan pada common katoda, katoda dari ketujuh LED yang terhubung menjadi satu (Gambar 2.14b).

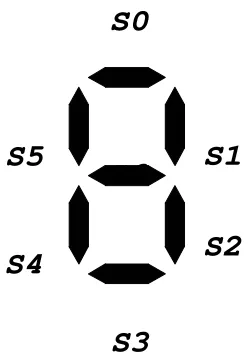

Pada umumnya, ketujuh LED pada seven segment diberi label S0 sampai S6 seperti disajikan pada Gambar 2.15. Ketujuh LED itu merupakan cacahan segmen minimum yang diperlukan untuk menampilkan angka 0 sampai 9 seperti diilustrasikan pada Gambar 2.16.

a) Common Anoda b) Common Katoda

S0

S1

Gambar 2.15 Penampil tujuh segmen

Gambar 2.16 Tujuh segmen dalam digit desimal

2.11 Pembanding / Comparator

Pembanding atau komparator adalah rangkaian yang membandingkan besaran masukan dengan suatu taraf referensi (atau dengan masukan lain) dan menghasilkan suatu perubahan keadaan di keluaran bila salah satu masukan melampaui yang lain. Jenis pembanding ada dua, yaitu pembanding analog dan pembanding digital. Yang akan dibahas disini adalah pembanding digital.

Pembanding digital adalah rangkaian logika yang dipakai untuk menentukan jika ada dua bilangan biner yang sama atau yang mempunyai besaran yang lebih besar. Diasumsikan data yang dibandingkan adalah bit tunggal maka dari Tabel 2.9 dapat dibandingkan masukan dari A dengan masukan dari B. Rangkaian pembanding dapat dilihat pada gambar 2.17.

S6

S2

S3

S4

Tabel 2.9 Tabel kebenaran pembanding (comparator) A B C

A>B

D A<B

E A=B 0 0 0 0 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1

(A=B)

E

(A<B)

D

(A>B)

C B

A

Gambar 2.17 Rangkaian pembanding besaran

74LS85 10 12 13 15 9 11 14 1 2 3 4 7 6 5 A0 A1 A2 A3 B0 B1 B2 B3 A<Bi A=Bi A>Bi A<Bo A=Bo A>Bo

Gambar 2.18 IC 74LS85

A3 B3 A2 B2 A1 B1 A0 B0 9 10 11 12 14 13 15 1 2 3 4 A<B A=B A>B A>B A=B A<B 5 6 7

2.12 Peta Karnaugh

Fungsi dari peta Karnaugh adalah untuk menyederhanakan perancangan untai digital. Peta Karnaugh berisi semua kemungkinan kombinasi dari sistem logika. Kombinasi ini dirangkai ke dalam bentuk tabel. Peta yang paling sederhana terdiri dari dua buah masukan atau peubah A dan B, seperti disajikan pada Gambar 2.20 a . Kolom menyajikan masukan A, dengan kolom di sebelah kiri menyajikan A = 0 dan kolom sebelah kanan menyajikan A = 1. Masukan B akan dituliskan pada baris, dengan baris pertama menunjukan B = 0, dan baris kedua menunjukan B = 1.

Dari empat kotak sel yang tersusun akan menyajikan semua kemungkinan nilai masukan, yaitu 22 = 4 buah masukan. Untuk suatu ungkapan Boole, keluaran ungkapan tersebut akan dituliskan di dalam sel yang sesuai dengan masukannya. Sebagai contoh, dari ungkapan

B A B A

F = . + .

maka peta Karnaugh seperti terlihat pada Gambar 2.20 b). Logika 1 ditempatkan didalam sel sesuai dengan bagian pertama dari ungkapan tersebut, A. maka 1 ditempatkan di B dalam sel A = 1 dan B = 0. Hal ini diulang untuk bagian kedua dari ungkapan tersebut,

B

A. pada A = 1 dan B = 0. Sisa sel yang lain boleh dibiarkan kosong atau diisi dengan 0. Angka 1 yang berdekatan kemudian dikelompokan seperti pada Gambar 2.20 c).

a ) b) c )

BAB III

PERANCANGAN

Dalam tugas akhir ini penulis merancang suatu sistem pendeteksian galat untuk sandi Reed-Solomon (7,3). Perancangan sistem penyandian dan pengawas sandi RS (7,3) ini akan dibagi menjadi 3 bagian besar yaitu rangkaian penyandi, rangkaian pembuat galat sebagai reperesentasi adanya e(X), serta rangkaian sindrom sebagai tempat pendeteksian ada tidaknya galat pada simbol data digital yang terkirim.

3.1 Diagram Blok Penyandian Sandi Reed-Solomon (7,3)

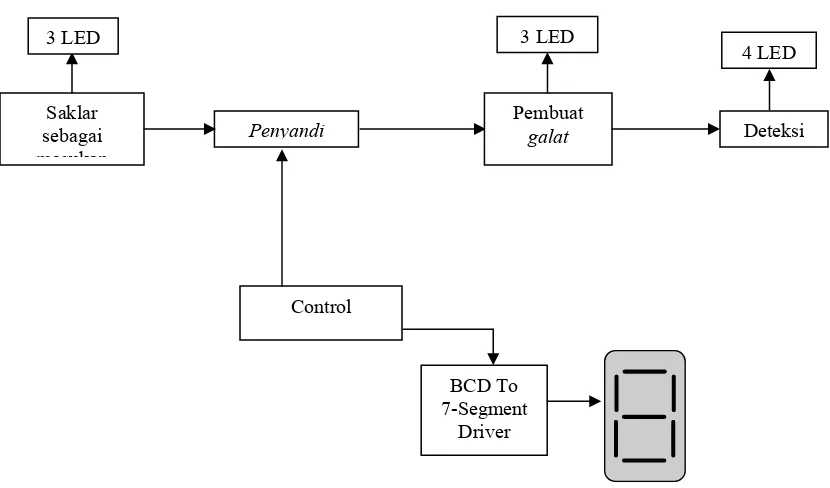

Bentuk diagram kotak sistem secara umum ditunjukan pada gambar 3.1.

Gambar 3.1 Diagram kotak sistem Sandi RS (7,3) Saklar

sebagai masukan

Penyandi

3 LED 3 LED

Pembuat

galat Deteksi

4 LED

Control

Sebuah simbol yang terdiri dari 3 bit data akan dimasukkan sebagai masukan melalui 3 buah saklar dan ditampilkan dengan 3 buah LED. Sedangkan polinomial pembangkit digunakan untuk membangkitkan bit paritas untuk mengoreksi galat. Bit paritas ini akan dikirimkan secara bersamaan dengan bit data.

Pada pengiriman ini, simbol yang terkirim menjadi 7 simbol yaitu terdiri dari 3 simbol pesan dan 4 simbol paritas. Kemudian data tersandi masuk pada rangkaian pembuat galat yang akan mengubah data yang masuk. Rangkaian pendeteksi galat (rangkaian sindrom) akan mengecek apakah data yang diterima dari penyandi terdapat galat atau tidak. Jika terdapat galat, maka LED akan menyala. Demikian pula bila data yang diterima tidak mengandung galat, maka LED akan mati.

Dalam perancangan ini LED digunakan sebagai penampil, baik masukan maupun keluaran. Agar LED yang digunakan dapat menyala, maka diberikan suatu pembatas arus yang melewati LED berupa resistor. Bila arus untuk menghidupkan LED adalah 1,7 volt, dan arus yang dibutuhkan adalah 10mA, maka :

Ω = =

⋅ − =

− =

−

330 01 , 0

3 , 3

10 10

) 7 , 1 5 (

) (

3

I V VCC

R LED

3.2 Perancangan Rangkaian Penyandi

Parameter-parameter untuk sandi RS(7,3) adalah sebagai berikut :

1. Elemen-elemen simbol berasal dari GF(23), berarti setiap simbol terdiri atas 3 bit.

2. Panjang kata sandi = n = 7 simbol 3. Panjang pesan = k = 3 simbol

4. Panjang cek paritas = n-k = 4 simbol

5. Jumlah maksimum galat yang bisa dikoreksi = t = 12 ( n – k ) = 2 simbol

6. Jarak minimum = dmin = 5

7. Polinomial primitif= p(X) = 1 + X + X3

8. Generator polinomial : g(X) = (X +α)(X +α2)(X +α3)(X +α4) Bentuk g(X) sesuai Tabel 2.1 dapat dituliskan kembali menjadi :

g(X)= α3 +αx+x2 +α3x3 +x4 ………(3-1) Persamaan ini diperoleh melalui perhitungan seperti berikut ini :

g(X)=(x+α)(x+α2)(x+α3)(x+α4)

=[x2 +(α +α2)x+α3][x2 +(α3+α4)x+α7] =(x2 +α4x+α3)(x2 +α6x+α7)

3

α α α3

Tahapan proses penyandian dapat dituliskan dalam diagram kotak seperti Gambar 3.2.

Pada Gambar3-2 tersebut terdapat rangkaian penjumlah dan pengali konstanta GF(23). Rangkaian penjumlah GF(23) merupakan penjumlah mod-2 sehingga dapat diimplementasikan dengan gerbang XOR. Pengali konstanta GF(23) mengalikan simbol pesan u(X) dengan koefesien generator paritas.

Gambar 3.2 Diagram kotak penyandi sandi RS(7,3)

Implementasi rangkaian pengali GF(23) dengan masing-masing koefisien tersebut adalah sebagai berikut :

Untuk simbol pesan yang terdiri atas 3 bit dapat dituliskan sebagai : )

, , (a0 a1 a2

us = ……….(3-2) maka representasi polinomialnya adalah :

2 2 1 0

)

(α a aα a α

1. Perkalian α3. Us(α)

α3. Us(α) = a0α3 +a1α4 +a2α5

= a0(1+α)+a1(α +α2)+a2(1+α +α2) = a0 +a0α +a1α +a1α2 +a2 +a2α +a2α2

= (a0 +a2)+(a0 +a1 +a2)α +(a1 +a2)α2 ……….(3-4) Jika persamaan diatas ditulis dalam bentuk A+Bα +Cα2, maka bentuk matematis persamaan tersebut dapat diimplementasikan menggunakan gerbang logika XOR seperti Gambar 3.3. :

C B A a0

a1 a2

a0

a2

a2 a1

Gambar 3.3 Gambar bentuk rangkaian persamaan 3-4.

2. Perkalian α . Us(α)

α . Us(α) = a0α +a1α2 +a2α3

= a0α +a1α2 +a2(1+α) = a0α +a1α2 +a2 +a2α

Jika persamaan diatas ditulis dalam bentuk A+Bα +Cα2 , maka bentuk matematis persamaan tersebut dapat diimplementasikan menggunakan gerbang logika XOR seperti Gambar 3.4.

Gambar 3.4 Gambar bentuk rangkaian persamaan 3-5.

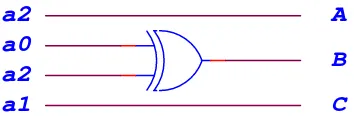

3.2.1 Perancangan Rangkaian

Gate

Gate pada Gambar 3.2 digunakan untuk memasukkan hasil penjumlahan 3 simbol pesan dan isi register ke-4 ke dalam rangkaian pengali konstanta GF(23). Saat kendali gate = 1, simbol pesan us= )(a0,a1,a2 satu persatu digeser masuk ke rangkaian dan secara bersamaan juga masuk ke dalam saluran komunikasi atau sebagai c(X). Pergeseran simbol pesan ke dalam rangkaian yang dilakukan dari bagian akhir (front end) sama artinya seperti mengalikan us (α) dengan X4. Kendali gate akan berubah menjadi 0 setelah 3 pulsa clock . Pada saat itu keempat register merupakan simbol paritas karena merupakan sisa hasil bagi b(X), antara Xn−k dengan g(x).

Berikut ini akan ditunjukkan perancangan Gate menggunakan Tabel kebenaran dan peta Karnough, dengan K adalah kendali Gate. Jika K bernilai 0 maka switch akan terbuka (off) dan jika K bernilai 1 maka Gate akan tertutup (on).

a2

a0

a2

a1

A

B

D2

D1

D0

KENDALI

OUTPUT

OUTPUT

OUTPUT

D0 K

OUTPUT D0

D0

K K 0 0 0 1

Tabel 3.1 Tabel kebenaran Gate

Kendali (K)

Data (D0) Keluaran

0 0 0 0 1 0 1 0 0 1 1 1

Dari Tabel 3.1 dapat dibuat peta Karnough sebagai berikut.

Dari peta karnough diatas didapat D·K yang dapat diimplementasikan dalam rangkaian digital menggunakan gerbang AND sebagai berikut.

Gambar 3.5 Rangkaian digital Gate

Karena terdapat 3 bit data, maka terdapat 3 gerbang and dua masukan seperti pada Gambar 3.5 sebagai Gate. Rangkaian Gate selengkapnya ditunjukan pada Gambar 3.6.

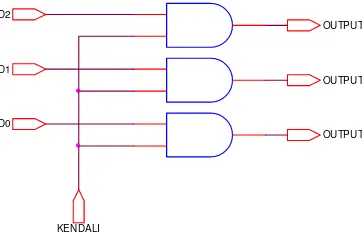

3.2.2 Perancangan Rangkaian Multiplekser

Multiplekser 3 bit pada Gambar 3.2 digunakan untuk mengatur pengiriman antara simbol paritas dan simbol pesan ke saluran komunikasi sebagai c(X).

Proses pertama saat kendali (K) bernilai 0 maka keluaran multiplekser adalah data. Saat kendali (K) bernilai 1 maka keluaran multiplekser adalah paritas. Selama clock ke-1 samapai clock ke-3, kendali bernilai 0, sehingga multiplekser akan memilih data sebagai keluarannya, sedangkan pada saat clock ke-4 sampai clock ke-7, multiplekser akan memilih paritas sebagai keluarannya. Berikut ini akan ditunjukkan perancangan Multiplekser menggunakan Tabel Kebenaran dan peta Karnough.

Tabel 3.2 Tabel kebenaran Multiplexer Kendali

(K)

Data (D0)

Paritas

(P0)

Keluaran

Ke

n

d

a

li

D0 P0

c(X)0

1

2

Dari Tabel 3.2 dapat dibuat peta Karnough sebagai berikut:

Dari peta Karnough di atas didapat D0·K + P0·K yang dapat diimplementasikan dalam rangkaian digital seperti ditunjukan pada Gambar 3.7. :

Gambar 3.7 Rangkaian multiplexer

K

K

D0

D0 D0

P0

P0 P0 P00

A

B

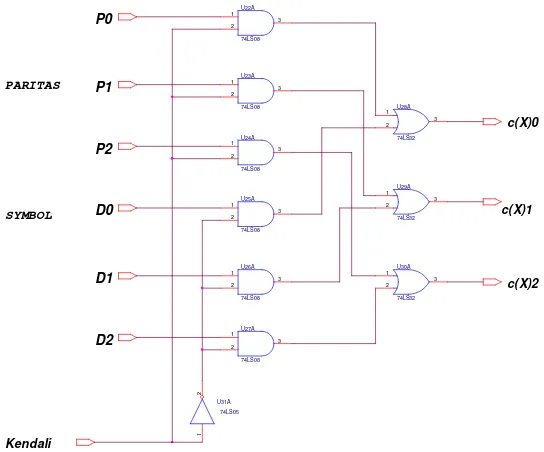

U25A 74LS08 1 2 3 U24A 74LS08 1 2 3 U23A 74LS08 1 2 3 U22A 74LS08 1 2 3 U31A 74LS05 1 2 U30A 74LS32 1 2 3 U29A 74LS32 1 2 3 U28A 74LS32 1 2 3 U27A 74LS08 1 2 3 U26A 74LS08 1 2 3 P0 P1 P2 D2 D0 D1 Kendali c(X)0 c(X)1 c(X)2 SYMBOL PARITASUntuk Rangkaian lengkap multiplekser ditunjukan pada Gambar 3.8.:

Gambar 3.8 Gambar Rangkaian lengkap multiplexer

3.2.3 Perancangan Rangkaian Komparator sebagai pengendali

gate

dan

multiplexer

Keluaran yang diinginkan dari unit kendali adalah ketika data terkirim yang berjumlah 3 simbol sudah semua terkirim, maka isi register terakhir akan digunakan sebagai keluaran (simbol paritas). Gambar diagram pewaktuan kendali RS(7,3) ditunjukan pada Gambar 3.9.

Gambar 3.9 Diagram pewaktuan kendali sandi RS (7,3)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17

clock

VCC U18 74LS85 10 12 13 15 9 11 14 1 2 3 4 7 6 5 A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B A<B A=B A>B U17 74LS93 14 1 2 3 12 9 8 11 A B R0(1) R0(2) QA QB QC QD CLOCK CLK REGISTER

M UX 3 BIT

A>3

Keterangan :

A : Gate terbuka , Multiplekser pilih data sebagai keluaran

B : Gate tertutup, Multiplekser pilih paritas sebagai keluaran

Untuk mendapatkan keluaran yang demikian, maka unit kendali dapat dibuat menggunakan komparator. Komparator ini digunakan sebagai pengatur keluaran data yang akan dikirimkan. Gambar 3.10 akan menampilkan rangkaian komparator sebagai pengatur keluaran data yang akan dikirimkan. Komparator ini dapat diimplementasikan menggunakan IC 74LS85.

Gambar 3.10 Rangkaian Komparator

Masukan B (B0, B1, B2, B3) akan diberi data

0 1 2 3 0 1 0 0 B B B B dengan cara menyambungkan ke Vcc untuk mendapatkan nilai 1 dan ke ground untuk mendapatkan nilai 0. Masukan A (A0, A1, A2, A3) akan di beri data QA, Q B, QC, QD yang merupakan

keluaran dari counter. Keluaran yang digunakan adalah keluaran A>B.

Komparator ini dibuat untuk memilih data yang akan dikeluarkan. Data yang dikirim berjumlah 3 simbol, jadi clock yang dibutuhkan adalah 3 clock. Clock akan menjalankan counter.

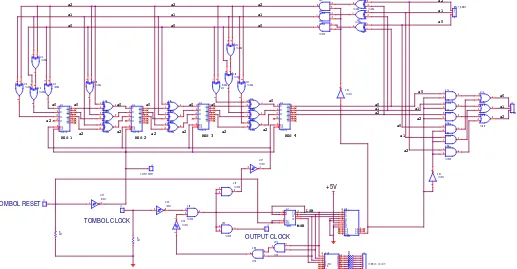

+5V U1A 74LS86 1 2 3 U1B 74LS86 4 5 6 U2A 74LS86 1 2 3 U15 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CLK CLR Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U3A 74LS86 1 2 3 U3B 74LS86 4 5 6 U3C 74LS86 9 10 8 U4D 74LS86 12 13 11 U5B 74LS86 4 5 6 U5A 74LS86 1 2 3 U12 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CLK CLR Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U4C 74LS86 9 10 8 U4A 74LS86 12 3 U7B 74LS08 4 5 6 U7A 74LS08 1 2 3 U8B 74LS08 4 5 6 U7D 74LS08 12 13 11 U7C 74LS08 9 10 8 U13 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CLK CLR Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U5C 74LS86 9 10 8 U11C 74LS32 9 10 8 J4

TOMBOL RESET 1

U11B 74LS32 4 5 6 U8A 74LS08 1 2 3 U6A 74LS86 1 2 3 U11A 74LS32 1 2 3 R1 560 U17 74LS93 14 1 2 3 12 9 8 11 A B R0(1) R0(2) QA QB QC QD U10E 74LS04 11 10 U5D 74LS86 12 13 11 R1 560 U10C 74LS04 5 6 U3D 74LS86 12 13 11 U10A 74LS04 1 2 U4B 74LS86 4 5 6 U10B 74LS04 3 4 U10F 74LS04 13 12 U9B 74LS08 4 5 6 J4 TOMBOL CLOCK 1 J3 CON3 1 2 3 J2 INPUT_TOMBOL 1 2 3 J4 OUTPUT RESET 1 U9C 74LS08 9 10 8 J4 OUTPUT CLOCK 1 R2 R R8 R R7 R R6 R R5 R R4 R U27B 7408 4 5 6 R3 R U2B 74LS86 4 5 6 U19 74LS47 7 1 2 6 4 5 3 13 12 11 10 9 15 14 16 8 1 2 4 8 BI/RBO RBI LT A B C D E F G VCC GND U8C 74LS08 9 10 8 U9A 74LS08 1 2 3 U8D 74LS08 12 13 11 U14 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CLK CLR Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U9D 74LS08 12 13 11 U2D 74LS86 12 13 11 J5 7_SEG 1 2 3 4 5 6 7 U2C 74LS86 9 10 8 U1D 74LS86 12 13 11 U10D 74LS04 9 8 U1C 74LS86 9 10 8 U27A 7408 1 2 3 U18 74LS85 10 12 13 15 9 11 14 1 2 3 4 7 6 5 16 8 A0 A1 A2 A3 B0 B1 B2 B3 A<B A=B A>B A<B A=B A>B VCC GND a1 a0 a2 a1 a0 a2 a1 a0 a2 a0 a2 a0 LSB a1 a0 MSB a2 a0 REG 1 a2 REG 2 a2 REG 3 a2 a0 REG 4 a2 a0 a0 a2 a0 a2 a0 a1 a2 a1 a2 a0 a2 a2 a1 a0 a1 a0 Common Anode

kompartor akan bernilai 1. Ketika komparator bernilai 1 maka isi register terakhir akan keluar.

Sistem penyandi ini membutuhkan 7 pulsa clock untuk membentuk c(X). Tiga clock pertama digunakan untuk mengirim simbol pesan kemudian 4 clock berikutnya digunakan untuk mengirim simbol paritas dengan cara menggeser masing-masing register. Rangkaian logika penyandi sandi RS(7,3) selengkapnya dapat dilihat pada Gambar 3.11 seperti berikut ini:

3. 3 Perancangan Pencacah /

Counter

Modulo 7

Dalam perancangan ini counter yang dibutuhkan adalah modulo 7. Penentuan modulo ini berdasarkan atas jumlah clock yang dibutuhkan dalam proses penyandian. Counter dibuat dengan JK flip flop yang menggunakan metode umpan balik menggunakan gerbang NAND. Tabel urutan perhitungan modulo 7 ditunjukan pada Tabel 3.3. Berikut ini akan dibahas pembuatan counter menurut perhitungan digital.

Tabel 3.3 Urutan perhitungan modulo 7

Clock C B A

0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 0 0 0

Gambar 3.12 Gelombang keluaran counter modulo 7

Clock Vcc Preset

J CLK K

Q

Q

PR

CL

J CLK K

Q

Q

PR

CL

LED B LED C

J CLK K

Q

Q

PR

CL

LED A

Gambar 3.13 Rangkaian pencacah maju modulo 7

3.4 Perancangan Rangkaian Pembuat Galat

Proses pengiriman data dari penyandi dan proses deteksi galat pada rangkaian deteksi (rangkaian sindrom) dilakukan secara paralel. Sebagai reperesentasi adanya e(X), maka diantara rangkaian penyandi dan rangkaian sindrom dibuat rangkaian pembuat galat.

3.4.1 Tampilan Rangkaian Pembuat Galat

Gambar 3.14 Tampilan rangkaian Pembuat Galat

Dari Gambar 3.14 terlihat bahwa data masukan dari penyandi akan ditampilkan dahulu ke LED-1, LED-2, dan LED-3. Galat akan dibangkitkan dari Saklar geser1, Saklar geser 2, dan Saklar geser 3, kemudian setelah galat dibangkitkan data yang telah diberi galat akan ditampilkan pada LED-4, LED-5 dan LED-6. Selanjutnya data yang telah digalatkan tersebut dikirim ke rangkaian deteksi (rangkaian sindrom).

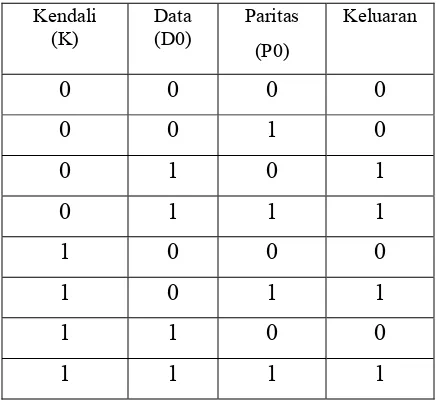

3.4.2

Rangkaian Pembuat Galat

Tabel 3.4 Tabel kebenaran rangkaian pembuat galat C(X) Sw Out

0 0 0 0 1 1 1 0 1 1 1 0

Dalam perancangan pembuat galat, digunakan gerbang logika XOR. Seperti terlihat pada Tabel kebenaran 3.4 di atas, berapapun nilai masukan dari c(X) bila nilai yang dimasukkan dari saklar adalah 1, maka nilai keluarannya (r(X)) akan menjadi

LED-1 LED-2 LED-3

LED-4 LED-5 LED-6

Saklar Geser 1

Saklar Geser 2

Saklar Geser 3

Galat

Tidak Galat Masukan

+5V U16A 7404 1 2 U24F 7404 13 12 U23E 7404 11 10 U22D 7404 9 8 U21C 7404 5 6 U20B 7404 3 4 U1C 7486 9 10 8 U1A 7486 1 2 3 J3 INPUT 1 2 3 4 J4 OUTPUT 1 2 3 4 J7

Input Tombol Error 1

2 3 D2 LED R13 330 R13 330 U1B 7486 4 5 6 R13 330 D2 LED R11 1 K R13 330 D2 LED R11 1 K D2 LED D2 LED R11 1 K R13 330 R13 330 D2 LED clock

komplemen dari nilai masukan tersebut. Pada perancangan ini ditetapkan bahwa bila saklar pada kondisi 1(ON) maka data masukan dari c(X) digalatkan dan sebaliknya bila saklar pada kondisi 0(OFF), maka nilai c(X) akan tetap atau tidak terjadi galat. Gambar rangkaian pembuat galat ditunjukan pada Gambar 3.15.

3.5

Perancangan Rangkaian Sindrom

3.5.1 Diagram Blok Rangkaian Sindrom

Sandi RS (7,3) mampu mendeteksi 2 galat sehingga sandi RS (7,3) mempunyai 4 buah sindrom S = ( S1, S2, S3, S4 ) yang dihitung menggunakan persamaan (2.4) yaitu :

i i

i

i r r r r

S = 0 + 1α + 2α2 +....+ 6α6 ………(3-2) dengan I = 1, 2, 3, 4

Sisi kanan persamaan (3-2) tersebut dapat diubah menjadi :

0 4

5

6. ) } ...]

[....{(r r r r

Si = αi + αi + αi + αi + …….. (3-3)

sehingga dengan bentuk kalang tersebut perhitungan sindrom dapat diimplementasikan karena perhitungan sindrom terdiri dari penjumlah GF(23) dan rangkaian pengali konstanta αi seperti pada rangkaian penyandi.

Gambar 3.16 Diagram Penghitung Sindrom sandi RS (7,3)

Sama seperti pada rangkaian penyandi, rangkaian pengali untuk us(α).αi dalam GF(23) dicari bentuk matematisnya sebagai berikut :

1. Perkalian α.Us(α) pada S1: )

( . α

αUs = a0α +a1α2 +a2α3

= a0α +a1α2 +a2(1+α) = a0α +a1α2 +a2 +a2α = 2

1 2

0

2 (a a )α aα

a + + +

2. Perkalian α2.Us(α) pada S2

) ( .

2 α

α Us = a0α2 +a1α3 +a2α4

= a0α2 +a1(1+α)+a2(α +α2) = a0α2 +a1+a1α +a2α +a2α2

4

α α3 α2 α

4

S S3 S2 S1

= a1+(a1+a2)α +(a0 +a2)α2 3. Perkalian α3.Us(α) pada S3

) ( .

3 α

α Us = a0α3 +a1α4 +a2α5

= a0(1+α)+a1(α +α2)+a2(1+α +α2) = a0 +a0α +a1α +a1α2 +a2α +a2α2 +a2

= (a0 +a2)+(a0 +a1 +a2)α +(a1+a2)α2 4. Perkalian α4.Us(α) pada S4

) ( .

4 α

α Us = a0α4 +a1α5 +a2α6

= a0(α +α2)+a1(1+α +α2)+a2(1+α2) = a0α +a0α2 +a1+a1α +a1α2 +a2 +a2α2 = (a1+a2)+(a0 +a1)α +(a0 +a1 +a2)α2

3.5.2 Rangkaian Sindrom

+5 V +5 V U8B 74LS32 4 5 6 U4C 74LS86 9 10 8 U8A 74LS32 1 2 3 U4D 74LS86 12 13 11 U6D 74LS86 12 13 11 C5 470 uF U10 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CL K CL R Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U9 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CL K CL R Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U2A 74LS86 1 2 3 U7D 74LS32 12 13 11 U7C 74LS32 9 10 8 U11 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CL K CL R Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 J1 CON4 1 2 3 4 U1A 74LS86 1 2 3 U1C 74LS86 9 10 8 U1B 74LS86 4 5 6 U12 74LS175 4 5 12 13 9 1 2 3 7 6 10 11 15 14 D1 D2 D3 D4 CL K CL R Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 U7A 74LS32 1 2 3 U7B 74LS32 4 5 6 U8C 74LS32 9 10 8 U8D 74LS32 12 13 11 R12 560 R12 560 R12 560 R12 560 U2B 74LS86 4 5 6 R12 560 U1D 74LS86 12 13 11 U2C 74LS86 9 10 8 R6 330 U3B 74LS86 4 5 6 U3A 74LS86 1 2 3 U2D 74LS86 12 13 11 U5C 74LS86 9 10 8 U5A 74LS86 1 2 3 U6C 74LS86 9 10 8 U6B 74LS86 4 5 6 U5B 74LS86 4 5 6 U6A 74LS86 1 2 3 R7 330 R8 330 U3C 74LS86 9 10 8 U4A 74LS86 1 2 3 U3D 74LS86 12 13 11 U4B 74LS86 4 5 6 J8 reset 1 2 R5 330 s2 r2 CLK r2 r0 r0 r2 r0 r0 r2 r0 r0 r2 r0 r0 r2 r0 r2 r0 r2 r0

s4 r0 s3 s2 s1

r2 s4 r2 s3 r2 s1 r2

Gambar 3.17 Rangkaian penghitung sindrom sandi RS (7,3)

3.5.3 Tampilan Rangkaian Sindrom

BAB IV

HASIL DAN PEMBAHASAN

Untuk mengetahui apakah alat yang dibuat telah sesuai dengan yang diinginkan, maka perlu dilakukan suatu npengujian. Pengujian terhadap kemampuan sistem sandi RS ( 7,3 ) dilakukan dengan menambahkan sejumlah galat sebelum sandi dikrim ke rangkaian pencari nilai sindrom. Untuk memudahkan analisa, data akan ditampilkan dalam bentuk tabel.

Tabel yang akan ditampilkan meliputi tabel hasil penyandian pada rangkaian penyandi, tabel hasil nilai sindrom tanpa galat, tabel hasil nilai sindrom dengan simbol yang diberi galat.

4.1 Analisa Hasil Penyandian

Pada data hasil proses penyandian sandi RS ( 7,3 ), akan dilakukan proses kalang sebnyak 3 kali sehingga akan dihasilkan simbol-simbol paritas. Pembuktian hasil ini secara manual dengan menggunakan perhitungan seperti dibawah ini.

4.1.1 Percobaan 1

Misalkan simbol pesan yang dikirimkan adalah: Simbol 1 : 001 = α2 = us1=(a0,a1,a2)1

1. Clock 1

Simbol pesan 1 ( 001 ) dikirimkan.

a) Dikalikan dengan koefisien generator paritas α3( 1 ) = (a0 +a2)+(a0 +a1 +a2)α +(a1 +a2)α2

= (0+1)+(0+0+1)α +(0+1)α2 = 1 + 1α + 1α2

= 111

b) Dikalikan dengan koefisien generator paritas α

= 2

1 2

0

2) ( ) ( )

(a + a +a α + a α = (1)+(0+1)α +(0)α2 = 1 + 1α + 0α2

= 110

c) Dikalikan dengan koefisien generator paritas 1 = (0 0 1) x 1

= 001

d) Dikalikan dengan koefisien generator paritas α3( 2 )

= 2

2 1 2

1 0 2

0 ) ( ) ( )

(a +a + a +a +a α + a +a α = (0+1)+(0+0+1)α +(0+1)α2

2). Clock 2

Simbol pesan 2 ( 010 ) dikirimkan, ditambahkan dengan hasil perkalian simbol pesan 1 dengan koefisien generator paritas α3( 2 ) pada clock sebelumnya.

010 + 111 = 101

a) Dikalikan dengan koefisien generator paritas α3( 1 )

= 2

2 1 2

1 0 2

0 ) ( ) ( )

(a +a + a +a +a α + a +a α = (1+1)+(1+0+1)α +(0+1)α2

= 0 + 0α + 1α2

= 001

b) Dikalikan dengan koefisien generator paritas α = (a2)+(a0 +a2)α +(a1)α2

= 2

) 0 ( ) 1 1 ( ) 1

( + + α + α = 1 + 0α + 0α2 = 100

Ditambahkan dengan hasil perkalian simbol pesan 1 dengan koefisien generator paritas α3( 1 ) pada clock 1.

100 + 111 = 011

c) Dikalikan dengan koefisien generator paritas 1 = (101) x 1

= 101

101 + 110 = 011

d) Dikalikan dengan koefisien generator paritas α3( 2 ) = (a0 +a2)+(a0 +a1 +a2)α +(a1 +a2)α2

= (1+1)+(1+0+1)α +(0+1)α2 = 0 + 0α + 1α2

= 001

Ditambahkan dengan hasil perkalian simbol pesan 1 dengan koefisien generator paritas 1 pada clock 1.

001 + 001 = 000 3. Clock 3

Simbol pesan 3 ( 011 ) dikirimkan, ditambahkan dengan hasil perkalian simbol pesan 2 dengan koefisien generator paritas α3( 2 ) pada clock 2

011 + 000 = 011

a) Dikalikan dengan koefisien generator paritas α3( 1 ) = (a0 +a2)+(a0 +a1 +a2)α +(a1 +a2)α2

= (0+1)+(0+1+1)α +(1+1)α2 = 1 + 0α + 0α2

= 100

b) Dikalikan dengan koefisien generator paritas α

= 2

1 2

0

2) ( ) ( )

= 111

Ditambahkan dengan hasil perkalian simbol pesan 2 dengan koefisien generator paritas α3( 1 ) pada clock 2.

111 + 001 = 110

c) Dikalikan dengan koefisien generator paritas 1 = (011) x 1

= 011

Ditambahkan dengan hasil perkalian simbol pesan 2 dengan koefisien generator paritas α pada clock 2.

011 + 011 = 000

d) Dikalikan dengan koefisien generator paritas α3( 2 ) = (a0 +a2)+(a0 +a1 +a2)α +(a1 +a2)α2

= (0+1)+(0+1+1)α +(1+1)α2 = 1 + 0α + 0α2

= 100

Ditambahkan dengan hasil perkalian simbol pesan 2 dengan koefisien generator paritas 1 pada clock 2.

100 + 011 = 111

Simbol paritas merupakan nilai-nilai hasil pekalian pada kalang (clock) 3, yaitu :

Paritas 3 = 110 = α3 Paritas 4 = 100 = 1

Sedangkan hasil pengamatannya dapat dilihat pada tabel 4.1, 4.2, 4.3 , 4.4 dan tabel 4.5.

Tabel 4.1 Hasil percobaan 1

Hasil akhir (keluaran) penyandi C (x) yang dicetak tebal merupakan sandi-sandi paritas.

Jadi sandi yang diperoleh untuk pesan us (α ) : [α2α α4] adalah :

c ( X) = [ 001, 010, 011, 111, 000, 110, 100] atau dalam bentuk α

c ( X ) = [α2,α, α4, α5, 0, α3, 1].

Hasil penyandian akan diperoleh pada clock ke – 7. Jadi untuk menyandikan 3 simbol pesan dibutuhkan 7 pulsa clock.

Clock Masukan Simbol

Pesan

Keluaran c (X) 0 0 0 1 0 0 1 1 0 1 0 0 1 0 2 0 1 1 0 1 1

3 x x x 1 1 1

4 x x x 0 0 0

5 x x x 1 1 0

6 x x x 1 0 0

4.1.2 Percobaan 2

Misalkan simbol pesan yang dikirimkan adalah: Simbol 1 : 011 = α4 = us1=(a0,a1,a2)

Simbol 2 : 100 = 1 = us2=(a0,a1,a2) Simbol 3 : 010 = α = us3=(a0,a1,a2)

Tabel 4.