Rancang Bangun Modul Pembelajaran Flip-flop untuk

Mata Kuliah Teknik Digital 2

Ella Prihatin Deliana Putri1, Kholilatul Wardani2, Irvania Sukma Kumala3, 1,2,3 Teknik Telekomunikasi, Politeknik Kota Malang

Jln Tlogowaru II no 3 Malang, Jawa Timur, Indonesia

1 [email protected], 2[email protected],3 [email protected]

ABSTRAK

Teknik digital 2 yang dipelajari di semester 3 program studi teknik telekomunikasi memiliki beberapa kompetensi dasar salah satunya adalah flip-flop. Flip-flop adalah suatu rangkaian yang dapat menyimpan state biner sepanjang masih terdapat daya pada rangkaian, sampai terjadi perubahan pada sinyal masukannya. Pada penelitian ini sebuah modul pembelajaran dibuat untuk mempermudah mahasiswa dalam praktikum. Modul menggunakan komponen elektronika yaitu IC, saklar dan LED. Modul ini juga memiliki 9 rangkaian flip-flop, satu rangkaian clock dan satu rangkaian adaptor. Pada modul ini terdapat tes poin untuk mempermudah mahasiswa untuk melakukan pengujian rangkaian. Hasil pengujian modul pembelajaran flip-flop diperoleh data dari mengamati perubahan output yang sesuai dengan tabel kebenaran di semua rangkaian flip-flop, mengukur output tegangan adaptor dan mengukur dan mengamati output dari clock. Data tersebut adalah berupa prosentase keberhasilan yaitu adaptor 5.22 volt, rangkaian clock menggunakan astabil multivibrator 60.08%, rangkaian flop RS NOR 100%, rangkaian flop RS NAND 100%, rangkaian flop RS Clock 100%, rangkaian flop D tanpa enable dan clock 100%, rangkaian flip-flop D dengan enable 100%, rangkaian flip-flip-flop D dengan clock 0%, rangkaian flip-flip-flop JK pemicu tepi 0%, rangkaian flip-flop JK master-slave 100%, rangkaian flip-flop T (toggle) 100%. Berdasarkan kuisioner hasil pengujian dari 30 pengguna menghasilkan nilai MOS 4.017 yang termasuk dalam kategori kualitas baik.

Kata kunci: Modul pembelajaran, Flip-flop, Teknik digital 2

ABSTRACT

Digital engineering 2 course which is learn in third semester in Telecommunication engineering study program has several basic competences one of them is flip-flop. Flip-flop is a circuit which can save binary state if there is still power in that circuit, until there is change on it’s input signal. In this final project a learning module made for easying student when they are practicing. The module used electronic components those are IC, switch, and LED. This module has also 9 flip-flop circuits, one clock circuit, and one adaptor circuit. In this module there is point test to make student easier to test circuit. The Testing result of flip-flop learning module, it is obtained the data from observing the output change which suit with truth table in all flip-flop circuit, measuring the output of adaptor voltage and measuring and observing output of clock. The data are in the form of success percentage those adaptor 5.22 volt, clock circuit use astable multivibrator 60.08%, RS NOR flip-flop circuit 100%, RS NAND flip-flop circuit 100%, RS Clock flip-flop

Ella Prihatin Deliana Putri

circuit 100%, flip-flop D circuit without enable and clock 100%, flip-flop D circuit with enable 100%, flip-flop D circuit with clock 100%, JK edge triggered flip-flop circuit 100%, JK master slave flip-flop circuit 100%, and flip-flop T (toggle) circuit 100%, Based on testing result questionnaire on 30 users, it got MOS value 4.017 and it’s categorized as good quality.

Keyword : Learning module, Flip-flop, Digital Engineering 2 PENDAHULUAN

Program studi teknik telekomunikasi memiliki beberapa mata kuliah yang diajarkan, salah satunya adalah mata kuliah teknik digital 2 yang ditempuh di semester 3. Pada penelitian ini akan dibahas lebih mendetail terkait flip-flop. Flip-flop adalah suatu rangkaian yang dapat menyimpan state biner sepanjang masih terdapat power pada rangkaian sampai terjadi perubahan pada sinyal input. Mempelajari teori flip-flop telah banyak literatur yang telah tersedia. Akan tetapi, dalam mempelajari flip-flop dalam praktikum akan sulit jika tidak ada modul untuk mempermudah melakukan praktikum. Oleh karena itu, dibutuhkan modul sebagai penunjang untuk praktikum mata kuliah teknik digital 2 dalam kompetensi dasar flip-flop. Dari permasalahan diatas penulis, maka penulis akan membuat penelitian dengan judul “rancang bangun modul pembelajaran flip-flop untuk mata kuliah teknik digital 2”.

KAJIAN PUSTAKA

Adaptor atau power supply

Adaptor adalah rangkaian elektronika yang berfungsi untuk mengubah tegangan AC yang tinggi menjadi tegangan DC yang lebih rendah. Bagian-bagian adaptor pada sebuah adaptor terdapat beberapa bagian atau blok yaitu trafo (transformator), rectifier (penyearah) dan filter trafo (transformator) adalah sebuah komponen yang berfungsi untuk menurunkan atau menaikan tegangan AC sesuai kebutuhan. Pada sebuah

adaptor, trafo yang digunakan adalah trafo jenis step down. Meskipun tegangan telah diturunkan, output dari transformator masih berbentuk arus AC. yang harus diproses selanjutnya. Rectifier rangkaian adaptor digunakan untuk menyearahkan output tegangan yang sudah di turunkan oleh trafo. Karena arus yang dibutuhkan oleh rangkaian elektronika adalah arus DC.

Rangkaian Clock

Membangun Astabil juga dapat di lakukan dengan rangkaian terpadu IC pewaktuan 555. Pewaktuan 555 mempunyai dua cara kerja, yaitu sebagai multivibrator astabil dan multivibrator monostabil, cara kerja pewaktuan ini di tentukan oleh jaringan resistor dan kapasitor yang di hubungkan dari luar ke ic tersebut. Multivibrator ini tidak mempunyai keadaan stabil, multivibrator akan berada pada salah satu keadaan selama sesaat dan selama sesaat pula. Output berosilasi di antara dua keadaan tinggi dan rendah yang di tentukan oleh parameter rangkaian dan tidak memerlukan pulsa input. Oleh karena itu multivibrator astabil disebut juga dengan multivibrator bergerak bebas atau free running multivibrator, dan dapat di gunakan sebagai pembangkit (clock). Rangkaian clock atau multivibrator astabil ditunjukkan pada gambar 2.2

Gambar 1. Rangkaian Clock Flip-flop

Suatu rangkaian gabungan gerbang-gerbang logika menjadi gerbang logika kombinasional dan kemudian diumpan-balikan yang dapat menyimpan data. Simbol flip-flop ditunjukkan pada gambar 2.3. Mempelajari rangkaian penyimpanan yang akan menahan (atau mengingat) data dalam sebuah keadaan digital yaitu 0 dan 1. Tiap elemen mampu menyimpan 1bit data biner, yang dinyatakan dalam sistem biner yaitu 0 dan 1. (Widjanarka, 2009)

Gambar 2. Simbol Flip-flopperancangan dan pembuatan

Flip-flop RS NOR

Flip-flop ini dibangun dengan menggunakan gerbang logika NOR dapat disebut juga penahan NOR. Rangkaian flip-flop RS NOR ditunjukkan pada gambar 2.4. Input R dalam keadaan 0 dan dalam keadaan 1 memberikan keadaan set. Sedangkan apabila R tinggi S rendah maka keadaan akan menjadi reset. Lainnya bila set dalam keadaan 1 dan reset dalam keadaan 1, maka akan terjadi keadaan pacu. Tabel kebenaran RS NOR dapat dilihat pada tabel 2.1. Oleh karena itu disarankan menghindari R dan S dalam keadaan 1.

Gambar 3. Flip-flop RS NOR Tabel 1. Tabel kebenaran RS NOR

Flip-flop RS NAND

Flip-flop yang terbuat dari gerbang logika NAND sering disebut sebagai penahan NAND. Rangkaian flip-flop RS NAND ditunjukkan pada gambar 2.5. Penahan NAND prinsip kerjanya sama dengan penahan NOR. Perbedaannya terletak pada keadaan level atau tingkat logikanya. Tabel kebenaran flip-flop RS NAND ditunjukkan pada tabel 2.2. Input-input set dan reset dari penahan NOR bekerja dari keadaan 0 menjadi 1, sewaktu mengubah keadaan, sedangkan penahan NAND bekerja dari keadaan 1 menjadi 0, sewaktu mengubah keadaan.

Gambar 4. Flip-flop RS NAND Tabel 2. Tabel Kebenaran RS NAND

Ella Prihatin Deliana Putri

Flip-flop RS Clock

Flip-flop RS Clock modifikasi dari flip-flop RS, Rangkaian flip-flop RS clock ditunjukkan pada gambar 2.6. Flip-flop RS clock ini harus menyesuaikan diri dengan sinyal clock. Apabila sinyal pendetak input pada logika 0, maka data yang masuk pada R dan S tidak akan ditanggapi atau diproses oleh flip-flop, sehingga output Q tetap tidak berubah. Tabel kebenaran RS Clock dapat dilihat pada tabel 2.3. Jika sinyal pendetak berubah dari logika 0 menjadi 1, seketika itu juga input set atau reset akan ditanggapi, sehingga output Q berubah. (Widjanarka, 2009).

Gambar 5. Flip-flop RS clock Tabel 3. Tabel kebenaran RS clock

Flip-flop D tanpa enable dan clock Flip-flop D yang paling sederhana dapat dibangun penahan NOR, akan tetapi pada bagian inputnya ditambah dengan gerbang logika NOT. Tetapi pada rangkaian ini gerbang logika logika NOT diganti dengan gerbang logika NAND. Flip-flop ini hanya memiliki satu input. Rangkaian D tanpa enable dan clock ditunjukkan pada gambar 2.7. Ketika D kondisi 1 maka output Q akan langsung berubah menjadi kondisi 1 dan ketika D kondisi 0 maka output Q akan langsung berubah kondisi menjadi 0. Tabel kebenaran flip-flop D tanpa enable dan clock dapat dilihat pada tabel 2.4.

Gambar 6. Flip-flop D tanpa enable & clock

Tabel 4. Tabel kebenaran D tanpa enable & clock

Flip-flop D dengan enable

Flip-flop D ini dapat dibentuk dari flip-flop RS dengan menambah sebuah gerbang logika inverter. Rangkaian D dengan enable ditunjukkan pada gambar 2.8. Rangkaian flip-flop ini dapat dilihat bahwa R dan S akan saling berlawanan satu sama lainnya dan S terhubung langsung dengan input tunggal D, sedangkan R melalui gerbang logika NOT. Jika digunakan akan sedemikian hingga output Q akan selalu sama dengan D selama enable dalam keadaan tinggi, tetapi data akan tetap ditahan dan input D ditolak, sampai enable menjadi 0. Tabel kebenaran dari flip-flop D dengan enable dapat dilihat pada tabel 2.6. (Widjanarka, 2009).

Gambar 7. Flip-flop D dengan enable Tabel 5. Tabel kebenaran D dengan

Flip-flop D dengan clock

Flip-flop D dengan clock adalah modifikasi dari flip-flop D. Flip-flop D dengan clock ditunjukkan pada gambar 2.9. Sinyal kendali enable tanpa sinyal pendetak dengan cara mengganti input enable dengan clock. Prinsip kerjanya sama, tidak ada perbedaan, hanya cara pengoperasiannya yang berbeda. Jika flip-flop D dengan enable, tidak dapat mengendalikan penahan D tanpa batasan waktu, atau disebut mode asinkron, maka flip-flop D dengan clock, harus mengikuti laju sinyal clock. Tabel kebenaran dari flip-flop D dengan clock dapat dilihat pada tabel 2.7 (Widjanarka, 2009).

Gambar 8. Flip-flop D dengan Clock Tabel 6. Tabel kebenaran D dengan

Clock

Flip-flop JK Pemicu tepi

Rangkaian flip-flop JK ini terdiri dari rangkaian gerbang logika, seperti halnya flip-flop lainnya. Flip-flop JK Pemicu Tepi ditunjukkan pada gambar 2.10. Tetapi JK flip-flop memiliki keunikan tersendiri pada output Q dan Q’ terdapat 2 jenis umpan balik dengan output yang diumpan balikkan kembali. Flip-flop JK memiliki 2 input kendali yang disebut J dan K yang berfungsi mengatur apa yang akan dilakukan rangkaian pada tepi sinyal clock. Tabel kebenaran flip-flop JK pemicu tepi dapat dilihat pada tabel 2.8. (Widjanarka, 2009)

Gambar 9. Flip-flop JK pemicu tepi Tabel 7. Tabel kebenaran JK pemicu tepi

Flip-flop JK Master-Slave

Flip-flop JK master-slave adalah kombinasi dari dua buah penahan yang diatur dengan master diatur oleh sinyal pendetak positif, sedangkan yang kedua atau yang terletak di belakang disebut dengan slave yang merupakan penahan yang diatur oleh sinyal pendetak negatif. Rangkaian flip-flop JK master-slave ditunjukkan pada gambar 2.11. Dari Tabel kebenaran JK master-slave dapat dilihat pada tabel 2.9 bahwa input asinkron preset dan clear adalah aktif rendah (low active). Artinya suatu keadaan low pada clear akan membuat flip-flop menjadi set (Q=1), dan suatu keadaan low pada clear akan menyebabkan flip-flop menjadi reset (Q=0). (Widjanarka, 2009).

Ella Prihatin Deliana Putri

Tabel 8. Tabel kebenaran JK master-slave

Flip-flop T (toggle)

Flip-flop T adalah kondisi khusus dari JK flip-flop. Input T didapatkan dari input J dan K saling dihubungkan. Rangkaian flip-flop T ditunjukkan pada gambar 2.12. Pada flip-flop T, J dan K akan bernilai sama 00 atau 11. Pada saat clock turun maka kondisi output Q tergantung pada input T. Kondisi output Q berubah-ubah (toggle) dicapai pada saat input T bernilai 1. Tabel kebenaran dari flip-flop T ditunjukkan pada tabel 2.10.

Gambar 11. Flip-flop T Tabel 9. Tabel kebenaran T

Mean Opinion Score (MOS)

Merupakan sistem penilaian yang berhubungan dengan desain alat, tampilan modul, dan pengoperasian modul. Standar penilaian MOS dikeluarkan oleh ITU-T pada tahun 1996. Tabel 2.11 adalah tabel yang menunjukkan skala penilaian MOS. MOS memberikan penilaian desain alat, tampilan modul, dan pengoperasian modul dengan skala 1 (satu) sampai 5 (lima), dimana satu mempresentasikan

kualitas hasil output yang sesuai dengan tabel kebenaran. Penilaian dengan menggunakan MOS masih bersifat subyektif karena kualitas pendengaran dan pendapat dari masing-masing orang.

Tabel 10. MOS (mean opinion score)

PEMBUATAN dan PERANCANGAN Modul pembelajaran flip-flop merupakan sebuah perangkat yang dimana didedikasikan kepada Mahasiswa Teknik Telekomunikasi Politeknik Kota Malang untuk mempermudah mahasiswa dalam praktikum. Modul ini merupakan suatu metode yang digunakan untuk mempelajari flip-flop. Jadi modul pembelajaran flip-flop ini terdiri dari IC gerbang logika dan Flip-flop. IC yang menyusun modul pembelajaran flip-flop yaitu untuk flip-flop RS menggunakan IC 74ls00 dan IC 74ls02, flip-flop D dengan enable menggunakan IC 74ls75, dan flip-flop D dengan clock menggunakan IC 74ls74, dan flip-flop JK pemicu tepi menggunakan IC 74ls73, dan flip-flop JK master-slave menggunakan IC 74ls76. Dan juga modul pembelajaran ini juga membutuhkan software dalam penyusunannya yaitu yang pertama software livewire untuk mendesain skematik, sprint layout 6.0 untuk mendesain layout rangkaian flip-flop.

PENGUJIAN DAN ANALISIS Pengujian Adaptor

Pengujian dilakukan untuk mengukur kestabilan tegangan output yang akan didistribusikan ke seluruh rangkaian. Output tegangan dari adaptor yang baik adalah 5V. Untuk mengetahui output tegangan adaptor tersebut dapat dilakukan dengan menggunakan Avometer. Pertama hidupkan avometer, putar rotary switch ke DCV. Setelah itu, hubungkan test point positif ke output adaptor positif dan hubungkan test point negatif ke output adaptor negatif. Amati nilai yang muncul pada LCD.

Tabel 11. Pengujian Tegangan adaptor Pengujian Rangkaian Clock

Pengujian pada rangkaian clock ini dilakukan untuk mengetahui output yang berupa 0 dan 1. Dalam keadaan 0 dan 1 diperoleh dari sebuah sinyal pulsa. Untuk melihat output sinyal tersebut dilakukan pengukuran melalui osiloskop. Pilih channel 1 untuk memasang kabel probe, kemudian kabel probe yang bernilai positif hubungkan pada TP1 sedangkan kabel probe yang negatif hubungkan pada gnd. Atur secon/div dan volts/div agar sinyal output dapat jelas terlihat. Berdasarkan data hasil pengujian, clock berjalan dengan baik sesuai dengan yang diharapkan. Rangkaian clock mampu menampilkan output 0 dan 1, ditandai dengan nyala LED. Rangkaian clock juga mampu menampilkan output sinyal pulsa pada osiloskop. Frekuensi output yang dihasilkan yaitu 50Hz yang juga mendekati perhitungan yaitu 68,96Hz.

Tabel 12. Pengujian clock

Pengujian RS NOR

Pengujian rangkaian flip-flop RS NOR bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop RS NOR, dan bagian output yang

2 buah LED dengan menggunakan kabel banana plug male.

Tabel 13. Pengujian RS NOR

Pengujian RS NAND

Pengujian rangkaian flip-flop RS NAND bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk

Ella Prihatin Deliana Putri

rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop RS NAND, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

Tabel 14. Pengujian RS NAND

Pengujian RS Clock

Pengujian rangkaian flip-flop RS Clock bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop RS Clock, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

Tabel 15. Pengujian RS Clock

Pengujian D tanpa enable dan clock Pengujian rangkaian flip-flop D tanpa enable dan clock bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop D tanpa enable dan clock, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

Tabel 16. Pengujian D tanpa enable dan clock

Pengujian D dengan enable

Pengujian rangkaian flip-flop D dengan enable bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop D dengan enable, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

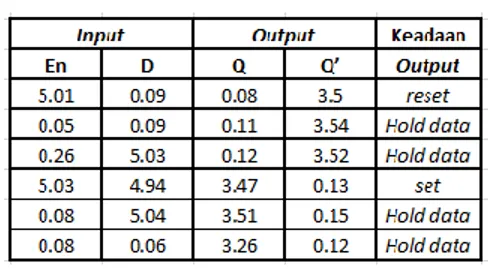

Tabel 17. Pengujian D dengan enable

Pengujian D dengan Clock

Pengujian rangkaian flip-flop D dengan clock bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop D dengan clock, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

Tabel 18. Pengujian D dengan clock

Pengujian JK Pemicu Tepi

Pengujian rangkaian flip-flop JK pemicu tepi bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input

bagian proses yang menggunakan gambar kerja rangkaian flip-flop JK pemicu tepi, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

Tabel 19. Pengujian JK Pemicu Tepi

Pengujian JK Master-Slave

Pengujian rangkaian flip-flop JK master-slave bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai dengan tabel kebenarannya. Untuk mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop JK master-slave dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male.

Tabel 20. Penujian JK master-slave

Pengujian T (Toggle)

Pengujian rangkaian flip-flop T bertujuan untuk mengetahui bahwa rangkaian ini dapat bekerja sesuai dengan teori, yaitu jika dengan mengubah input dan dapat menghasilkan output yang sesuai

Ella Prihatin Deliana Putri

mengetahui output yang sesuai dari rangkaian ini dilakukan pengukuran dengan menyambungkan bagian input yang menggunakan 2 buah saklar SPST, bagian proses yang menggunakan gambar kerja rangkaian flip-flop T, dan bagian output yang menggunakan 2 buah LED dengan menggunakan kabel banana plug male. Hasil pengujian didapatkan dari pengukuran tegangan pada bagian input dan outputnya.

Tabel 21. T (toggle)

Pengujian Kuisioner

Hasil data kuisioner “Rancang Bangun Modul Pembelajaran Flip-flop Teknik Digital 2 Program Studi Teknik Telekomunikasi Politeknik Kota Malang” dapat dilihat pada tabel 4.12.

Tabel 22. Hasil data kuisioner

PENUTUP

Dari hasil pengujian dan analisa yang telah dilakukan, dapat disimpulkan bahwa :

1. Proses pembuatan Rancang Bangun Modul Pembelajaran Teknik Flip-flop Untuk Mata Kuliah Teknik Digital 2 Program Studi Teknik Telekomunikasi

Politeknik Kota Malang yaitu pembuatan simulasi rangkaian, print layout pcb, proses etching pcb, pemasangan komponen, penyolderan komponen pada pcb.

2. Hasil data pengujian modul flip-flop yaitu berdasarkan tabel 5.1 Tabel 23. Tabel Hasil Data Pengujian

Flip-flop

3. Pembuatan jobsheet dimaksudkan untuk mempermudah mahasiswa untuk melakukan praktikum, karena didalam sebuah jobsheet sudah terdapat cara melakukan pengukuran, jadi dengan adanya jobsheet mahasiswa akan lebih mudah melakukan praktikum.

4. Kuisioner hasil data menhasilkan nilai MOS yaitu 4.017 memiliki kategori baik

DAFTAR PUSTAKA

Anonim. (2016, November 12). Rangkaian ¬Clock¬ dan ¬Prinsip ¬Kerja ¬Clock. Diperoleh dari http://www.laboreldi.or.id:

ngakian¬clock¬dan¬prinsip¬kerja¬cloc k.html

Kho, D. (2016, Agustus 2). Pengertian Flip-flop Jenis Flip-flop. Diperoleh dari https://teknikelektronika.com:

https://teknikelektronika.com/pengerti an-flip-flop-jenis-flip-flop/

Kho, D. (2018, April 12). Pengertian¬ LED Light -Emitting ¬Diode ¬Cara ¬Kerja. Diperoleh dari https://teknikelektronika.com:

https://teknikelektronika.com/pengerti

an-led¬light¬emitting¬diode¬cara¬kerja/ Kiswoyo, B. (2017, Maret 19). Jenis-jenis IC Gerbang Logika. Diperoleh dari https://www.jalankatak.com:

https://www.jalankatak.com/id/jenis-jenis-ic-gerbang-logika/

Muchlas. (2005). Rangkaian Digital. Jogjakarta: Gava Media.

Susanto, B. (2017, Febuari 3). Pengertian Saklar -Listrik ¬Cara¬ Kerjanya. Diperoleh dari https://teknikelektronika.com:

https://teknikelektronika.com/pengerti an-saklar¬listrik¬cara¬kerjanya/ Widjanarka, W. (2009). Teknik Digital. Surabaya: Erlangga.

Windiarto, A. (2017). Rancang Bangun Voice Over Internet Protocol dan GSM Gateway berbasis Raspberry Pi . Malang.