Analisis

Analisis

Analisis

Analisis

Rangkaian Listrik

Rangkaian Listrik

Rangkaian Listrik

Rangkaian Listrik

Jilid 2

Hak cipta pada penulis, 2010

SUDIRHAM, SUDARYATNO Analisis Rangkaian Listrik (2) Darpublic, Bandung

are-0710 edisi Juli 2011

http://ee-cafe.org

Alamat pos: Kanayakan D-30, Bandung, 40135. Fax: (62) (22) 2534117

BAB 8

Analisis Pada Suatu Sistem

Pengenalan pada sistem ini bertujuan agar kita

• memahami sinyal dalam pengertian yang lebih luas; • memahami pengertian tentang sistem;

• mampu membangun diagram blok suatu sistem; • mampu mereduksi diagram blok suatu sistem. 8.1. Sinyal

Di awal buku ini kita telah mempelajari bentuk gelombang sinyal yang merupakan suatu persamaan yang menyatakan sinyal sebagai fungsi dari waktu. Dalam analisis rangkaian listrik, sinyal-sinyal yang kita tangani biasanya berupa tegangan ataupun arus listrik. Pengertian ini dapat kita perluas menjadi suatu pengertian yang tidak hanya mencakup sinyal listrik saja tetapi juga mencakup sinyal-sinyal non-listrik yang juga merupakan fungsi waktu. Dengan perluasan pengertian ini maka kita mempunyai definisi untuk sinyal sebagai,

Sinyal adalah suatu fungsi yang menyatakan variasi terhadap waktu dari suatu peubah fisik.

Fungsi yang kita tetapkan untuk menyatakan suatu sinyal kita sebut representasi dari sinyal atau model sinyal dan proses penentuan representasi sinyal itu kita sebut pemodelan sinyal. Suatu sinyal yang tergantung dari peubah riil t dan yang memodelkan peubah fisik yang berevolusi dalam waktu nyata disebut sinyal waktu kontinyu. Sinyal waktu kontinyu ditulis sebagai suatu fungsi dengan peubah riil t seperti misalnya x(t). Sebagaimana telah disebutkan di awal buku ini, sinyal jenis inilah yang sedang kita pelajari.

Untuk memberi contoh dari sinyal non-listrik, kita bayangkan suatu benda yang mendapat gaya. Benda ini akan bergerak sesuai dengan arah gaya., posisinya akan berubah dari waktu ke waktu. Dengan mengambil suatu kooordinat referensi, perubahan posisi benda akan merupakan fungsi waktu dan akan menjadi salah satu peubah fisik dari benda tersebut dan merupakan suatu sinyal. Selain perubahan posisi, benda juga

mempunyai kecepatan yang juga merupakan fungsi dari waktu; kecepatan juga merupakan suatu sinyal.

Jika posisi benda dalam contoh di atas merupakan suatu sinyal, apakah ia dapat dijadikan suatu masukan (input) pada sebuah “rangkaian” ? Bayangkanlah benda yang bergerak itu adalah sebuah pesawat terbang. Kita ingin mengamatinya dengan menggunakan sebuah teropong, dan untuk itu teropong kita arahkan pada pesawat. Setiap saat pesawat berubah posisi, kedudukan teropong kita sesuaikan sedemikian rupa sehingga bayangan pesawat selalu terlihat oleh kita melalui teropong. Kita katakan bahwa posisi pesawat merupakan masukan pada kita untuk mengubah arah teropong; dalam hal ini kita dan teropong menjadi sebuah “rangkaian”. Apakah dari “rangkaian” ini ada suatu keluaran (output)? Keluaran dari “rangkaian” ini adalah berupa perubahan arah teropong. Jelaslah bahwa ada hubungan tertentu antara arah teropong sebagai keluaran dengan posisi pesawat sebagai masukan, dan hubungan keluaran-masukan demikian ini sudah biasa kita lihat pada rangkaian listrik. Kalau kita yang meneropong pesawat tersebut digantikan oleh sebuah mesin penggerak otomatis dan teropong diganti dengan sebuah meriam, maka jadilah sebuah “rangkaian” mesin penembak pesawat. Mesin penembak ini dapat kita sebut sebagai suatu perangkat yang mampu menetapkan arah meriam jika mendapatkan masukan mengenai posisi pesawat (istilah “perangkat” di sini kita beri pengertian sebagai gabungan dari banyak piranti untuk menjalankan fungsi tertentu). Dengan kata lain antara sinyal keluaran dengan sinyal masukan terdapat hubungan yang sepenuhnya ditentukan oleh perilaku perangkat; hal ini berarti bahwa perangkat “memiliki aturan” yang menetapkan bagaimana bentuk keluaran untuk sesuatu masukan yang ia terima.

8.2. Sistem

Dengan contoh di atas, kita sampai pada pengertian mengenai sistem yaitu :

sistem merupakan aturan yang menetapkan sinyal keluaran dari adanya sinyal masukan.

atau

sistem membangkitkan sinyal keluaran tertentu dari adanya sinyal masukan tertentu.

Jika kita ingat mengenai pengertian elemen sebagai model piranti dalam rangkaian listrik, maka sistem dapat dipandang sebagai model dari

perangkat. Dengan demikian rangkaian-rangkaian listrik yang sudah pernah kita pelajari, yang juga menetapkan hubungan antara keluaran dan masukan, dapat kita pandang sebagai suatu sistem. Kalau rangkaian tersebut merupakan bagian lain dari rangkaian (dalam hubungan kaskade misalnya) kita dapat memandangnya sebagai sub-sistem. Hubungan keluaran-masukan dari suatu sistem dapat kita nyatakan sebagai

[ ]

() )(t H xt

y = (8.1)

dengan y(t) sinyal keluaran dan x(t) sinyal masukan. Hubungan ini dapat kita gambarkan dengan diagram berikut.

Perhatikanlah bahwa sistem didefinisikan menurut sinyal keluaran dan masukannya. Jadi kita memandang sistem dari sudut pandang sinyal masukan dan keluaran. Selain dari pada itu, Gb.8.1. mempelihatkan bahwa arah propagasi sinyal adalah sesuai dengan arah anak panah. Jadi sinyal berasal dari masukan menuju ke keluaran. Penggambaran ini sesuai dengan definisi kita yaitu bahwa suatu sistem membangkitkan sinyal keluaran dari sinyal masukan.

Suatu sistem dapat mempunyai satu masukan atau lebih; demikian juga keluarannya bisa hanya satu atau lebih. Sistem dengan satu masukan dan satu keluaran disebut single-input-single-output (SISO) system atau kita terjemahkan dengan sistem masukan-tunggal-keluaran-tunggal (MTKT). Jika masukan dan keluarannya lebih dari satu disebut multi-input-multi-output (MIMO) system atau kita terjemahkan sistem masukan-ganda-keluaran-ganda (MGKG).

8.3. Model Sistem

Pernyataan matematis secara eksplisit dari suatu sistem seperti pada (8.1) disebut representasi sistem atau model sistem. Proses untuk memperoleh model sistem kita sebut pemodelan sistem. Ada dua cara yang dapat ditempuh untuk membangun model sistem. Cara pertama adalah menurunkan langsung dari hukum-hukum fisika dan cara kedua adalah melalui observasi empiris. Cara pertama dapat digunakan apabila proses-proses fisiknya terdefinisi dengan jelas dan difahami. Model sistem yang

H sinyal masukan sinyal keluaran x(t) y(t)

diturunkan haruslah cukup sederhana untuk keperluan analisis dan simulasi.

Cara kedua digunakan untuk sistem yang sangat kompleks dan sangat sulit untuk dianalisis langsung, dan perilaku dinamiknya tidak difahami secara baik. Untuk melakukan observasi empiris diperlukan sinyal masukan yang harus dipilih secara cermat, dan sinyal keluarannya diamati. Model sistem diperoleh dengan melakukan perhitungan balik dari kedua sinyal tersebut. Pembangunan model sistem melalui cara observasi sinyal masukan dan keluaran ini disebut identifikasi sistem. Kita telah melihat bahwa ada empat macam cara untuk menyatakan hubungan antara sinyal keluaran dan sinyal masukan, yaitu persamaan diferensial, transformasi Laplace, konvolusi, dan transformasi Fourier. Sejalan dengan itu, kita mengenal empat macam representasi sistem atau model sistem sebagai berikut.

1. Persamaan Diferensial. Bentuk ini kita kenal misalnya sistem orde kedua ) ( ) ( ) ( ) ( 2 2 t f t by dt t dy a dt t y d + + =

Bentuk umum dari model ini dinyatakan dalam persamaan diferensial : ) ( ) ( ) ( ) ( ) ( ) ( ) ( 0 ) 1 ( 1 ) ( 0 1 ) 1 ( 1 ) ( t x b t x b t x b t y a t y a t y a t y m m m m n n n + + + = + + + − − − − L & L . ) 0 ( , ) 0 ( , , ) 0 ( , ) 0 ( 0 1 2 ) 2 ( 1 ) 1 ( y y y y y y y y n n n n = = = = − − − − & L (8.2) Dalam (8.2) kita menganggap bahwa koefisien ak dan bk adalah

bilangan riil (konstan tidak tergantung waktu). Kita juga menganggap m ≤ n. Masukan sistem adalah x(t) dan keluarannya adalah y(t). Orde dari persamaan diferensial ini adalah n.

2. Fungsi Alih Laplace

)

(

)

(

)

(

)

(

0 1 1 1 0 1 1T

s

H

s

a

s

a

s

a

s

b

s

b

s

b

s

s

n n n m m m m=

=

+

+

+

+

+

+

+

=

− − − −L

L

X

Y

(8.3)Di sini sinyal keluaran dan masukan dinyatakan di kawasan s, yaitu

Y(s) dan X(s). T(s) adalah fungsi alih Laplace, yang untuk selanjutnya

akan kita gunakan sebagai representasi sistem di bab ini dan kita tuliskan sebagai H(s). 3. Integral Konvolusi

∫

∞−−

λ

λ

λ

=

0(

)

(

)

)

(

t

h

t

x

d

y

(8.4) denganh

(

t

)

=

L

−1{

H

(

s

)

}

. 4. Fungsi Alih Fourier)

(

)

(

)

(

ω

=

ω

X

ω

Y

H

(8.5)dengan

H

(

ω

)

=

F

{ }

h

(

t

)

adalah fungsi alih Fourier.Untuk selanjutanya, kita akan menggunakan cara representasi sistem yang ke-dua, yaitu menggunakan fungsi alih Laplace.

8.4. Diagram Blok

8.4.1. Penggambaran Sistem Dengan Diagram Blok

Diagram blok adalah representasi dari fungsi alih dengan menggunakan gambar. Diagram blok sangat bermanfaat untuk menggambarkan struktur sistem, terutama jika sistem tersusun dari banyak sub-sistem (penjelasan pengertian sub-sistem akan diberikan kemudian).

Diagram ini juga bermanfaat untuk melakukan analisis sistem. Di sub-bab ini kita mengambil model sistem dengan transformasi Laplace (di kawasan s). Hubungan masukan- keluaran sistem akan berbentuk :

) ( ) ( ) ( atau ) ( ) ( ) ( s s H s s H s s X Y X Y = = (8.6)

Diagram blok dari sistem ini adalah seperti terlihat pada Gb.8.2. Diagram blok seperti ini telah kita kenal dalam analisis rangkaian

listrik. Hanya di sini kita mempunyai pengertian H(s) sebagai representasi dari sistem. Diagram blok ini ekivalen dengan persamaan aljabar (8.6). Jadi susunan diagram blok merupakan pernyataan

operasi-H(s)

X(s) Y(s)

operasi matematis. Hal ini berbeda dengan Gb.8.1. yang hanya merupakan diagram untuk memperjelas definisi tentang sistem. Suatu sistem yang kompleks tersusun dari sistem-sistem yang lebih sederhana. Diagram blok dapat kita gunakan untuk menyatakan hubungan dari sistem-sistem yang lebih sederhana tersebut untuk membentuk sistem yang kompleks. Diagram blok akan mempelihatkan struktur dari sistem yang kompleks yaitu interkoneksi dari komponen-komponen sistem. Lebih dari itu, diagram blok juga dapat dimanfaatkan sebagai alat untuk melakukan perhitungan-perhitungan; fungsi alih sistem diturunkan dari diagram blok yang tersusun dari banyak komponen tersebut.

8.4.2. Hubungan-Hubungan Sistem

Berikut ini kita akan melihat hubungan-hubungan sederhana dari sistem yang akan menjadi dasar bagi kita untuk memandang sistem yang lebih kompleks. Kita akan meninjau dua sistem yaitu H1(s) dan H2(s). Untuk

menghubungkan dua sistem, atau dua blok, harus ada titik-titik hubung.

Titik Hubung. Ada dua macam titik hubung yang perlu kita perhatikan

yaitu titik pencabangan (pickoff point) dan titik penjumlahan. Titik pencabangan adalah titik tempat terjadinya duplikasi sinyal; sinyal-sinyal yang meninggalkan titik pencabangan sama dengan sinyal yang memasuki titik pencabangan. Hal ini digambarkan pada Gb.8.3.a. Pada titik penjumlahan, beberapa sinyal dijumlahkan. Sinyal yang keluar dari titik penjumlahan adalah jumlah dari sinyal yang masuk ke titik penjumlahan. Jika sinyal yang masuk bertanda “+” maka ia dijumlahkan dan jika bertanda “−” ia dikurangkan. Untuk titik penjumlahan ini ada konvensi, yaitu bahwa hanya ada satu sinyal saja yang meninggalkan titik penjumlahan. Hal ini digambarkan pada Gb.8.3.b.

a). titik pencabangan b). titik penjumlahan Gb.8.3. Titik-titik hubung.

Hubungan Kaskade atau Hubungan Seri. Hubungan seri antara dua

sistem terjadi jika keluaran dari sistem yang satu merupakan masukan

X(s) X(s) X(s) titik pencabangan X1(s)−X2(s)+ X3(s) X1(s) X2(s) X3(s) + + −

pada sistem berikutnya seperti terlihat pada Gb.8.4. Fungsi alih dari hubungan kaskade, yang merupakan fungsi alih total, adalah hasil kali dari fungsi alih sistem yang menyusunnya. Jadi hubungan kaskade sistem H1(s) dan H2(s) dapat digantikan oleh satu sistem H1(s)H2(s). Hal ini

sesuai dengan kaidah rantai yang telah kita pelajari dalam analisis rangkaian di kawasan s.

Gb.8.4. Hubungan seri

Hubungan Paralel. Hubungan paralel antara dua sistem terjadi jika

kedua sistem mendapat masukan yang sama sedangkan keluarannya merupakan jumlah dari keluaran kedua sistem tersebut, seperti terlihat pada Gb.8.4.b. Jadi hubungan paralel antara dua sistem H1(s) dan H2(s)

dapat digantikan oleh satu sistem dengan fungsi alih H1(s)+H2(s).

Gb. 8.5. Hubungan paralel.

Hubungan Umpan Balik. Pada hubungan umpan balik, keluaran dari

sistem pertama menjadi masukan pada sistem kedua dan keluaran sistem kedua menjadi pengurang pada sinyal dari luar R(s); sinyal hasil pengurangan ini menjadi masukan pada sistem pertama. Hubungan ini diperlihatkan pada Gb.8.6.

Gb.8.6. Hubungan umpan balik . H1(s) H2(s) R(s) Y(s) − −− − + X1(s) X2(s) Y2(s) Y(s) R(s) ) ( ) ( 1 ) ( 2 1 1 s H s H s H + H1(s) H2(s) X(s) Y(s) + + H1(s)+H2(s) Y(s) X(s) H1(s) H2(s) X(s) Y(s) H1(s)H2(s) Y(s) X(s)

Dari diagram blok pada Gb.8.6. diperoleh persamaan berikut.

[

]

[

( ) ( )]

) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( 2 1 1 2 1 1 2 1 1 1 s s H s H s s H s s H s s H s s s H s s H s Y R Y R Y R X Y − = − = − = =[

]

) ( ) ( 1 ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( 2 1 1 1 2 1 s H s H s H s s s s H s s H s H s + = ⇒ = + ⇒ R Y R Y YDengan hubungan umpan balik seperti pada Gb.8.6. fungsi alih sistem keseluruhan menjadi ) ( ) ( 1 ) ( 2 1 1 s H s H s H +

Fungsi alih H1(s) adalah fungsi alih dari suatu sistem yang disebut sistem

loop terbuka sedangkan

) ( ) ( 1 ) ( 2 1 1 s H s H s H

+ adalah fungsi alih dari sistem yang disebut sistem loop tertutup. Jika pada titik penjumlahan terdapat tanda negatif pada jalur umpan balik maka sistem ini disebut sistem dengan umpan balik negatif. Jika fungsi alih H2(s) = − 1 maka sistem

menjadi sistem dengan umpan balik negatif satu satuan.

Sub-Sistem. Jika kita memisahkan salah satu bagian dari diagram blok

suatu sistem yang tersusun dari banyak bagian dan bagian yang kita pisahkan ini merupakan suatu sistem juga maka bagian ini kita sebut sub-sistem. H2(s) dalam contoh hubungan paralel di atas merupakan salah

satu sub-sistem.

8.5. Pembentukan Diagram Blok

Berikut ini kita akan melihat contoh penggambaran diagram blok dan penyederhanaan diagram blok. Sebagaimana telah disebutkan, walaupun kita telah mengembangkan pengertian sistem akan tetapi dalam contoh-contoh yang akan kita lihat di sini kita membatasi diri pada sistem listrik. 8.5.1. Diagram Blok Elemen Rangkaian

Definisi sistem menyatakan bahwa dari sinyal masukan tertentu suatu sistem akan memberikan sinyal keluaran tertentu. Definisi ini dipenuhi oleh elemen-elemen rangkaian seperti R, L, dan C, karena elemen-elemen

ini akan memberikan sinyal keluaran (tegangan atau arus) tertentu jika diberi sinyal masukan (arus atau tegangan) tertentu yang kita kenal sebagai karakteristik i-v dalam analisis rangkaian listrik. Jika sistem dapat divisualisasikan menggunakan diagram blok, maka elemen-elemen rangkaian listrik dapat pula digambarkan dengan diagram blok.

Resistor. Gb.8.7. memperlihatkan diagram blok dari resistor. Hubungan

tegangan-arus resistor adalah V(s)=RI(s) atau I(s)=(1/R)V(s). Kedua relasi memberikan diagram blok seperti ditunjukkan pada gambar.

Gb.8.7 Diagram blok resistor.

Kapasitor. Gb.8.8. memperlihatkan diagram blok dari kapasitor.

Hubungan tegangan-arus kapasitor adalah V(s)=(1/sC)I(s) atau ) ( ) ( ) (s sCV s

I = . Kedua relasi memberikan diagram blok seperti ditunjukkan pada gambar.

Gb.8.8. Diagram blok kapasitor.

Berbeda dengan resistor, kapasitor adalah elemen dinamik. Hubungan yang pertama mengambil peubah status, yaitu tegangan kapasitor, sebagai keluaran dan dapat ditulis sebagai V(s)=(1/C)(1/s)I(s) dan diagram bloknya menjadi :

I(s)→→→→ C 1 → → → → s 1 → → → →V(s) R I(s) + V(s) − R 1 I(s) V(s) I(s) R V(s) I(s) + V(s) − sC 1 I(s) V(s) sC 1 I(s) V(s) sC

Di kawasan t hubungan tersebut adalah v(t)=(1/C)

∫

idt. Oleh karena itu bloks 1

disebut sebagai blok integrator.

Induktor. Gb.8.9. memperlihatkan diagram blok dari induktor.

Hubungan tegangan-arus induktor adalah V(s)=(sL)I(s) atau ) ( ) / 1 ( ) (s sLV s

I = . Kedua relasi memberikan diagram blok seperti ditunjukkan pada gambar.

Gb.8.9. Diagram blok induktor.

Seperti halnya kapasitor, induktor adalah elemen dinamik. Hubungan yang kedua mengambil peubah status, yaitu arus induktor, sebagai keluaran dan dapat ditulis sebagai I(s)=(1/L)(1/s)V(s). Dengan blok integrator diagram bloknya menjadi :

V(s)→→→→ L 1 → →→ → s 1 → → → →I(s).

8.5.2. Pembentukan Diagram Blok

Dalam contoh-contoh berikut ini kita akan melihat bagaimana diagram blok dibentuk. Kita menggabungkan pemahaman mengenai rangkaian listrik dengan pemahaman hubungan-hubungan sistem.

I(s) + V(s) − sL I(s) sL V(s) I(s) V(s)

sL

1

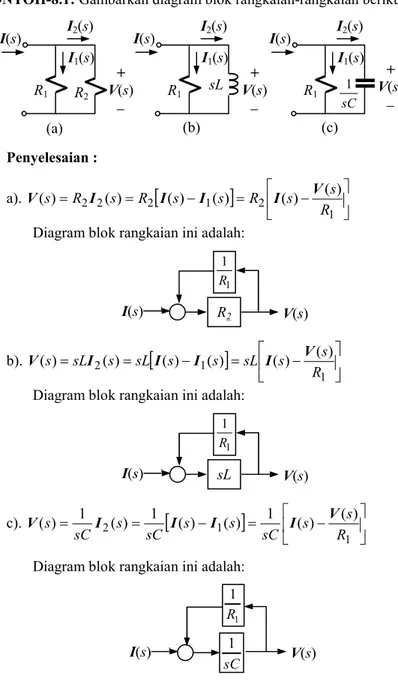

CO*TOH-8.1: Gambarkan diagram blok rangkaian-rangkaian berikut. Penyelesaian : a).

[

]

− = − = = 1 2 1 2 2 2 ) ( ) ( ) ( ) ( ) ( ) ( R s s R s s R s R s I I I I V VDiagram blok rangkaian ini adalah:

b).

[

]

− = − = = 1 1 2 ) ( ) ( ) ( ) ( ) ( ) ( R s s sL s s sL s sL s I I I I V VDiagram blok rangkaian ini adalah:

c).

[

]

− = − = = 1 1 2 ) ( ) ( 1 ) ( ) ( 1 ) ( 1 ) ( R s s sC s s sC s sC s I I I I V VDiagram blok rangkaian ini adalah: R2 I(s) + V(s) − R1 I2(s) I1(s) (a) I(s) + V(s) − R1 I2(s) I1(s) sL (b) sC 1 I(s) + V(s) − R1 I2(s) I1(s) (c) sL I(s) + V(s) 1 1 R − R2 I(s) + V(s) 1 1 R − sC 1 I(s) + − V(s) 1 1 R

CO*TOH-8.2: Gambarkan diagram blok rangkaian-rangkaian berikut. Penyelesaian : a). = =

[

−]

= − sL s s R s s R s R s) ( ) ( ) ( ) ( ) ( ) ( 1 2 1 1 1 V I I I I V Diagram blok: b). V(s)=R1I2(s)=R1[

I(s)−I1(s)]

=R1[

I(s)−sCV(s)]

Diagram blok:Tegangan V(s) pada contoh 8.1.b. dan 8.1.c. haruslah identik dengan tegangan pada contoh 8.2. karena tegangan ini adalah tegangan pada hubungan paralel dari dua elemen. Walaupun demikian kita mendapatkan diagram blok yang berbeda pada kedua contoh tersebut. Kita akan menguji apakah kedua diagram blok tersebut identik dengan mencari fungsi alih masing-masing. Untuk itu kita akan memanfaatkan formulasi hubungan blok paralel.

Untuk rangkaian R-L paralel di kedua contoh tersebut di atas kita peroleh : I(s) + − R1 V(s) sC I(s) + V(s) − R1 I2(s) I1(s) sL (a) + V(s) − sC 1 I(s) R1 I2(s) I1(s) (b) sL 1 I(s) + − R1 V(s)

Untuk rangkaian R-C paralel kita peroleh :

Fungsi alih dari kedua hubungan paralel terserbut ternyata sama yang tidak lain adalah impedansi total rangkaian R-L dan R-C paralel. Jadi diagram blok yang diperoleh pada kedua contoh di atas adalah identik.

I(s) + − R1 V(s) sC ) ( ) ( ) / 1 ( / ) )( ( 1 ) ( 1 1 1 1 4 s s R sC sC R sC R R s H I V = + = + = sC 1 I(s) + V(s) 1 1 R − ) ( ) ( ) / 1 ( / ) / 1 )( / 1 ( 1 / 1 ) ( 1 1 1 3 s s sC R sC R R sC sC s H I V = + = + = sL I(s) + V(s) 1 1 R − ) ( ) ( ) / 1 )( ( 1 ) ( 1 1 1 1 s s sL R sLR R sL sL s H I V = + = + = I(s) + − R1 V(s) sL 1 ) ( ) ( ) / 1 )( ( 1 ) ( 1 1 1 1 2 s s R sL sLR sL R R s H I V = + = + =

CO*TOH-8.3: Bangunlah diagram blok dari rangkaian listrik yang telah ditransformasikan ke kawasan s di bawah ini.

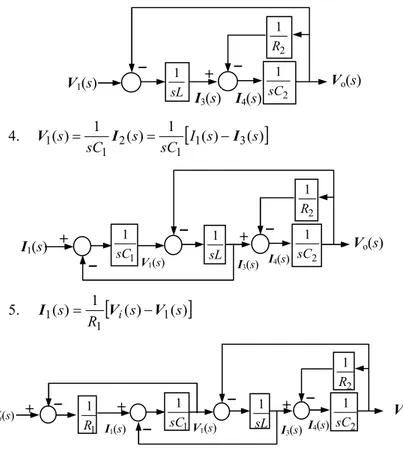

Penyelesaian :

Dalam membangun diagram blok rangkaian ini, kita akan menempuh langkah-langkah yang kita mulai dari tegangan keluaran dan mencari formulasinya secara berurut menuju ke arah masukan. Tegangan Vo(s) dapat dinyatakan sebagai

R I

2 5(

s

)

ataupun(1/sC2) I4(s). Kita ambil yang kedua.

1. ( ) 1 4( ) 2 o s sC s I V = 2. ( ) ( ) ( ) 1 o( ) 2 3 5 3 4 s R s s s I I I V I = − = − 3. 3( ) 1

[

1(s) o(s)]

sL s V V I = − 2 1 sC 1 1 sC R2 + Vo(s) − R1 sL I2(s) I3(s) I1(s) + Vi (s) − I4(s) I5(s) V1(s) 2 1 sC I4(s) Vo(s) 2 1 sC Vo(s) 2 1 R I3(s) − −− − + I4(s)4. ( ) 1 ( ) 1

[

1( ) 3( )]

1 2 1 1 I s s sC s sC s I I V = = − 5. ( ) 1[

( ) 1( )]

1 1 s s R s Vi V I = −Pada langkah ke-5 ini terbentuklah diagram blok yang kita cari. Walaupun diagram ini terlihat cukup rumit, tetapi sesungguhnya setiap blok menggambarkan peran dari setiap elemen. Perhatikan pula bahwa dalam diagram blok ini digunakan blok-blok integrator.

8.6. Reduksi Diagram Blok

Dalam Contoh-8.3 kita melihat bagaimana diagram blok dibentuk. Diagram blok ini cukup panjang. Dengan menggunakan relasi-relasi ekivalensi sistem terhubung seri dan paralel kita dapat menyederhanakan diagram blok tersebut. Penyederhanaan diagram blok ini disebut reduksi diagram blok. Karena diagram blok ekivalen dengan persamaan rangkaian, maka penyederhanaan diagram blok akan menuju pada diperolehnya fungsi alih.

2 1 sC Vo(s) 2 1 R V1(s) − −− − + sL 1 − −− − I4(s) I3(s) 2 1 sC Vo(s) 2 1 R I1(s) − −− − + sL 1 − −− − I4(s) I3(s) 1 1 sC + − −− − V1(s) 2 1 sC Vo 2 1 R I1(s) − −− − + sL 1 − −− − I4(s) I3(s) 1 1 sC + − −− − V1(s) 1 1 R Vi(s) + − −− −

Selain ekivalensi seri dan paralel, dalam melakukan reduksi diagram blok kita memanfaatkan juga kaidah-kaidah pemindahan titik pencabangan sebagai berikut.

Keluaran Y2(s) tidak akan berubah jika pemindahan titik

pencabangannya ke depan melampaui blok H(s) diikuti dengan penambahan satu blok seri yang ekivalen dengan blok H(s). Keluaran Y3(s) tidak akan berubah jika pemindahan titik

pencabangannya ke belakang melampauai blok H(s) diikuti dengan penambahan satu blok seri 1/H(s).

Perhatikanlah Gb.8.10. Gambar b) diperoleh dengan jalan memindahkan titik pencabangan di gambar a). Pencabangan keluaran Y2(s) di pindah ke

depan melewati blok H(s) dan pencabangan keluaran Y3(s) ke belakang

melewati blok H(s).

Gb.8.10. Pemindahan titik pencabangan.

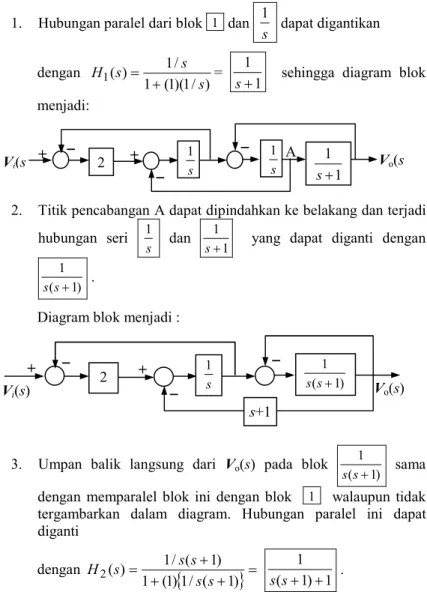

CO*TOH-8.4: Lakukanlah reduksi pada diagram blok berikut ini.

Penyelesaian : X(s) H(s) Y2(s) Y1(s) Y3(s) X(s) Y2(s) Y1(s) Y3(s) ) ( 1 s H H(s) H(s) a). b). Vo(s) − −− − + − −− − + − −− − Vi(s) + − −− − 1 s 1 s 1 s 1 2

1. Hubungan paralel dari blok 1 dan 1 s dapat digantikan dengan ) / 1 )( 1 ( 1 / 1 ) ( 1 s s s H + = = 1 1 +

s sehingga diagram blok menjadi:

2. Titik pencabangan A dapat dipindahkan ke belakang dan terjadi hubungan seri 1

s dan 1 1 +

s yang dapat diganti dengan

) 1 ( 1 + s s .

Diagram blok menjadi :

3. Umpan balik langsung dari Vo(s) pada blok

) 1 ( 1 + s s sama

dengan memparalel blok ini dengan blok 1 walaupun tidak tergambarkan dalam diagram. Hubungan paralel ini dapat diganti dengan

{

}

= + + + = ) 1 ( / 1 ) 1 ( 1 ) 1 ( / 1 ) ( 2 s s s s s H 1 ) 1 ( 1 + + s s .Diagram blok menjadi

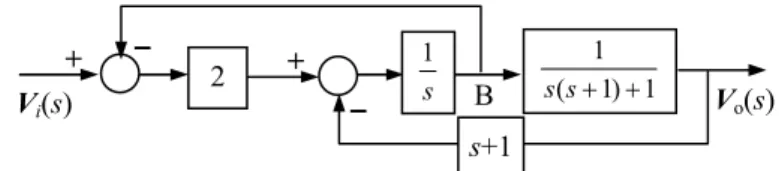

Vo(s) − −− − + − −− − Vi(s) + −−−− ) 1 ( 1 + s s s 1 2 s+1 Vo(s − −− − + − −− − Vi(s + −−− − 1 1 + s s 1 s 1 2 A

1. Titik pencabangan B dapat dipindahkan ke belakang yang akan menyebabkan terjadinya hubungan seri antara blok

1 s dan ( 1) 1 1 + + s

s yang dapat diganti dengan

s s s ( +1)+

1

2

Diagram blok menjadi :

5. Selanjutnya s+1 paralel dengan

s s s ( +1)+ 1 2 = + + + + + + = ) ) 1 ( ( ) 1 ( 1 ) ) 1 ( ( 1 ) ( 2 2 3 s s s s s s s s H ) 1 ( ) ) 1 ( ( 1 2 s+ +s + s+ s = 1 2 1 2 3+ + + s s s

dan H3(s) seri dengan 2 sehingga diagram blok menjadi :

Vo(s) + − −− − Vi(s) + −−− − 1 ) 1 ( 1 + + s s s 1 2 s+1 B Vo(s) + − −− − Vi(s) + −−− − s s s ( + )1 + 1 2 2 s+1 1 ) 1 (s+ + s

6. Diagram blok paralel terakhir ini memberikan 3 4 3 2 ) 1 2 /( ) 1 ( 2 1 ) 1 2 /( 2 ) ( 2 3 2 3 2 2 3 4 + + + = + + + + + + + + + = s s s s s s s s s s s s H

dan diagram blok menjadi

Reduksi diagram blok pada akhirnya akan memberikan fungsi alih dari sistem yaitu H4(s).

8.7. Sub-Sistem Statis dan Dinamis

Perhatikanlah bahwa dalam diagram blok yang diperoleh pada contoh 8.3. terdapat blok-blok yang berisi nilai konstan dan ada yang berisi fungsi s atau lebih tepat blok yang menggambarkan fungsi alih bernilai konstan dan blok yang menggambarkan fungsi alih yang merupakan fungsi dari peubah Laplace s. Blok yang berisi nilai konstan berasal dari elemen statis resistor, dan yang berisi fungsi s berasal dari elemen dinamik C ataupun L. Suatu sub-sistem disebut dinamis jika fungsi transfernya merupakan fungsi peubah Laplace s. Jika fungsi alihnya bernilai konstan (gain kontan) maka sub-sistem itu disebut statis. 8.8. Diagram Blok Integrator

Suatu diagram blok yang seluruh blok-blok dinamisnya berupa blok integrator disebut diagram blok integrator. Sebagaimana telah dibahas, blok integrator berasal dari elemen dinamik apabila kita mengambil peubah status sebagai keluaran. Untuk kapasitor V(s)=(1/C)(1/s)I(s)

dan untuk induktor I(s)=(1/L)(1/s)V(s).

Pembentukan diagram blok integrator dari suatu fungsi alih dapat dilakukan karena fungsi alih H(s) yang berbentuk rasio polinomial dapat kita uraikan menjadi suku-suku :

Vo(s) Vi(s) 3 4 3 2 2 3+ + + s s s Vo(s) Vi(s) + −−−− 1 2 2 2 3+s + s+ s 1 ) 1 (s+ + s

) ( ) ( ) ( ) ( ) )( ( ) ( ) )( ( ) ( 2 2 1 1 2 1 2 1 n n n m p s k p s k p s k p s p s p s z s z s z s K s H − + + − + − = − − − − − − = L L L

Hal ini telah kita lihat pada waktu kita membahas transformasi Laplace. Selanjutnya, setiap suku dari fungsi alih H(s) yang berbentuk

b s

a + dapat ditulis sebagai

) / 1 ( 1 ) / 1 ( s b s b b a +

yang diagram bloknya merupakan hubungan seri antara blok statis

b a

dengan blok berumpan balik

s

1

yang jalur umpan-balik-nya berisi blok statis b . Dengan demikian maka diagram blok dari H(s) dapat dibuat hanya terdiri dari blok statis dan blok integrator saja.

Soal-Soal

1. Susunlah diagram blok dari rangkaian-rangkaian berikut, lakukan reduksi diagram blok, tentukan fungsi alihnya.

a). b).

c). e).

f).

g).

2. Lakukan reduksi diagram blok dan carilah fungsi alih dari diagram blok berikut. a). b). 1 s 1 s + X(s) Y(s) ω2 10 1 s X (s) + Y(s) − −− − k + + + vo − iin 2µF 1kΩ 5mH + vo − iin 1kΩ 1µF 1kΩ 0.1H vin + vo − + − 1kΩ 1kΩ 1µF 1kΩ 100m + vin − 10Ω 10Ω 1H + vo − + − 1µF 10µ F 5kΩ 10k Ω 1kΩ 1kΩ + vo − vin vin + vo − + − 1µF 1kΩ 1µF 1kΩ

c). c). d). e). 1 s + X(s) Y(s) 4 − −− − 1 s + + − −− − + + − −− − 5 1 s 1 s 1 s + X(s) Y(s) 3 − −− − + + − −− − + 1 s + 4 − −− − 1 s 1 s + X(s) Y(s) 3 − −− − 4 1 s + + − −− − + + X(s) Y(s) 2 + s −−−− 1 1 + s

BAB 9

Sistem Dan Persamaan Ruang Status

Persamaan ruang status (state space equations) atau representasi ruang keadaan (state space reprentation) merupakan satu alternatif untuk menyatakan sistem dalam bentuk persamaan diferensial. Persamaan ini dapat diturunkan dari diagram blok integrator. 9.1. Blok Integrator dan Blok Statis

Kita lihat lebih dulu blok integrator X(s)→ 1

s →Y(s) yang

menunjukkan hubungan ( ) 1 (s) s

s X

Y = . Hubungan ini di kawasan t adalah

∫

= ()

) (t xt

y yang dapat kita tuliskan sebagai x(t)= y&(t) Hubungan terakhir di kawasan t ini dapat kita baca sebagai : sinyal masukan adalah turunan dari sinyal keluaran.

Sekarang blok 1

s kita pandang sebagai integrator dan bukan sebagai gambaran dari fungsi alih 1/s. Dengan pandangan ini maka jika keluaran integrator adalah q(t) masukannya adalah q&(t). Kita dapat menggambarkan hubungan keluaran dan masukan di kawasan t dari integrator sebagai

) (t

q& → 1

s →q(t)

Perhatikan: Secara teknis penggambaran di atas tidak benar. Akan tetapi kita harus mengartikan gambar tersebut sebagai diagram sub-sistem yang mempunyai sinyal masukan q&(t) dan sinyal keluarannya q(t) dan bukan q(t) sama dengan (1/s) kali

) (t

Berbeda dengan blok integrator, blok statis X(s)→ a →Y(s)

memberikan hubungan Y(s)=aX(s) yang di kawasan t memberikan hubungan ) ( ) (t axt y =

Jadi kita dapat menggambarkan hubungany(t)=ax(t)dengan menggunakan blok statis, yaitu

x(t)→ a →y(t).

9.2. Diagram Blok Integrator, Sinyal Sebagai Fungsi t

Berikut ini kita akan melihat contoh suatu diagram blok integrator yang sinyal masukan dan keluaran dari setiap integrator dinyatakan sebagai fungsi t.

CO*TOH-9.1: Dalam diagram blok di bawah ini nyatakanlah sinyal masukan dan keluaran pada setiap blok integrator sebagai fungsi t.

Penyelesaian :

Dalam diagram blok ini terdapat dua blok integrator. Jika sinyal masukan setiap blok integrator adalah q&i(t) dan sinyal

keluarannya adalah qi(t) maka diagram blok di atas dapat kita

gambarkan seperti di bawah ini, di mana masukan dua blok integrator adalah

) (

1 t

q& dan q&2(t) sedangkan keluarannya adalah

q1(t) dan q2(t). Y(s) − −− − + − −− − a s 1 s 1 b c X(s) d +

Dengan diagram ini keluaran sistem adalah ) ( ) ( ) (t q2 t dxt y = + .

9.3. Membangun Persamaan Ruang Status

Dari diagram blok di atas, kita dapat memperoleh satu set persamaan di kawasan t yang akan memberikan hubungan antara sinyal masukan dan sinyal keluaran sistem, yaitu x(t) dan y(t). Dengan perkataan lain kita dapat memperoleh persamaan sistem di kawasan t. Set persamaan tersebut kita peroleh dengan memperhatikan masukan blok-blok integrator, dan keluaran sistem. Dalam contoh ini set persamaan tersebut adalah :

) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( 2 2 1 2 2 1 t dx t q t y t aq t q t q t cx t bq t q + = − = + − = & & (9.1)

Dengan cara ini set persamaan yang kita peroleh, yaitu persamaan (9.1), akan terdiri dari dua kelompok. Kelompok pertama adalah persamaan yang ruas kirinya berisi q&(t), yang merupakan masukan blok integrator, dan kelompok kedua adalah yang ruas kirinya berisi y(t), yaitu keluaran sistem. Kelompok pertama dapat kita tuliskan dalam bentuk matriks

) ( 0 1 ) ( ) ( 1 0 ) ( ) ( 2 1 2 1 t x t q t q a b t q t q + − − = & & (9.2) ) ( ) ( ) (t q2 t dxt y = + ) ( 1t q& q1(t) − −− − + − −− − a s 1 s 1 ) ( 2 t q& q2(t) + + b c ) (t x d + + y(t)

Dengan mendefinisikan vektor = ) ( ) ( 2 1 t q t q q & & & r dan = ) ( ) ( 2 1 t q t q qr maka

(9.2) dapat kita tuliskan

[ ]

[ ]

() 0 1 ) ( 1 0 ) ( qt xt a b t q + − − = r & r (9.3) Kelompok kedua dari (9.1) adalahy

(

t

)

=

q

2(

t

)

+

dx

(

t

)

dan dengan definisi untuk vektor q(t) maka ia dapat kita tuliskan dalam bentuk matriks[

0 1][ ] [ ]

() () )(t qt d xt

y = r + (9.4)

Dengan demikian maka set persamaan (9.1) dapat kita tuliskan sebagai

[ ]

[ ]

[

0 1][ ] [ ]

() () ) ( ) ( 0 1 ) ( 1 0 ) ( t x d t q t y t x t q a b t q + = + − − = r r & r (9.5)Secara umum bentuk persamaan (9.5) dapat kita tulis sebagai

[ ]

[ ][ ] [ ]

[ ][ ] [ ]

() () ) ( ) ( ) ( ) ( t x D t q C t y t x B t q A t q + = + = r r & r (9.6)Set persamaan (9.6) ini disebut representasi ruang status dari sistem. Sebutan lain dari representasi ini adalah model ruang status atau juga persamaan peubah status atau persamaan ruang status.

CO*TOH-9.2: Carilah representasi ruang status dari sistem berikut.

2 q& q2 1 q& − −− − 3 q 3 q& 1 q + − −− − c3 s 1 s 1 ) (t y + + a1 ) (t x b + + ω2 a2 + s 1 c2 d

Penyelesaian:

Dari diagram blok di atas, masukan blok-blok integrator dan keluaran sistem memberi kita persamaan berikut.

) ( ) ( ) ( ) ( 2 2 3 3 1 3 2 2 2 3 2 1 1 t dx q c q c t y q q bq t x a q q t x a q + + = = − = ω − = & & &

Persamaan ini kita tuliskan dalam bentuk matriks, menjadi

[

]

[ ]

() ) ( ) ( ) ( 0 ) ( ) ( 0 ) ( ) ( ) ( 0 0 1 0 0 0 0 ) ( ) ( ) ( ) ( 3 2 1 3 2 2 1 3 2 1 2 3 2 1 t x d t q t q t q c c t y t x a a t q t q t q b t q t q t q t q + = + − ω − = = & & & & rInilah representasi ruang status dari sistem yang kita cari 9.4. Membangun Diagram Blok dari Persamaan Ruang Status Melalui contoh berikut ini kita akan melihat bagaimana diagram blok dari suatu sistem dapat dibangun jika persamaan ruang statusnya diketahui.

CO*TOH 9.3: Bangunlah diagram blok sistem yang persamaan ruang statusnya adalah sebagai berikut.

[

]

() ) ( 1 0 0 ) ( ) ( ) ( 1 0 0 0 1 0 ) ( 3 2 1 3 2 1 3 2 1 t q b b b t y x(t) t q t q t q a a a t q r & r = + − − − = Penyelesaian :Langkah pertama adalah melakukan pengembangan dari persamaan yang diketahui sehingga diperoleh set persamaan berikut. ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( 3 3 2 2 1 1 3 3 2 2 1 1 3 3 2 2 1 t q b t q b t q b t y t x t q a t q a t q a t q t q t q t q t q + + = + − − − = = = & & &

Langkah berikutnya adalah menggambarkan blok-blok integrator dengan masukan dan keluaran masing-masing. Langkah ini memberikan diagram blok integrator sebagai berikut

Langkah berikutnya adalah melakukan penghubungan blok-blok ini sesuai dengan persamaan yang diketahui, yaitu

persamaan q&1(t)=q2(t) berarti bahwa masukan blok

integrator nomer-1 adalah keluaran dari blok integrator nomer-2.

persamaan q&2(t) = q3(t) berarti masukan blok integrator nomer-2 adalah keluaran blok integratir nomer-3. Kita mendapatkan hubungan:

Selanjutnya kita membuat pencabangan-pencabangan dan penjumlahan dengan blok-blok statis, sesuai dengan persamaan yang diketahui, yaitu

) ( ) ( ) ( ) ( ) ( 1 1 2 2 3 3 3 t aq t a q t a q t xt q& =− − − +

Hasil yang kita peroleh adalah:

3 q& q2 q&1 q1

s

1

2 q&s

1

3 qs

1

2 q 2 q& s 1 q&3 q3 s 1 1 q& q1 s 1Satu persamaan lagi yang harus kita penuhi, yaitu persamaan keluaran ) ( ) ( ) ( ) (t b1q1 t b2q2 t b3q3 t y = + +

Dengan pencabangan dan penjumlahan persamaan ini kita penuhi. − −− − a2 ) (t x a3 3 q& q2 q&1 q1 s 1 2 q& s 1 3 q s 1 a1 − −− − − −− − + − −− − a2 ) (t x a3 3 q& q2 q&1 q1 s 1 2 q& s 1 3 q s 1 a1 − −− − − −− − + b1 b2 b3 + + + ) (t y

Soal-Soal

1. Carilah persamaan ruang status dari sistem-sistem dengan diagram blok di bawah ini.

a). b). c). d). 10 1 s X (s) + Y(s) − −− − k + + 1 s 1 s + X(s) Y(s) ω2 + X(s) Y(s) 2 + s −−−− 1 1 + s 1 s 1 s + X(s) Y(s) 3 − −− − 4 1 s + + − −− − +

e).

f).

2. Gambarkan diagram blok dari sistem dengan persamaan status berikut ini. a).

[

9

0

0

]

(

)

10

(

)

)

(

)

(

5

3

)

(

4

6

0

5

3

7

0

1

2

)

(

t

x

t

q

t

y

t

x

t

q

t

q

+

=

+

=

r

r

&

r

b).[

5

0

0

]

(

)

5

(

)

)

(

)

(

0

1

0

)

(

0

0

2

1

0

4

2

0

0

)

(

t

x

t

q

t

y

t

x

t

q

t

q

+

=

+

−

=

r

r

&

r

1 s + X(s) Y(s) 3 − −− − + + − −− − + 1 s + 4 − −− − X(s) 1 s + Y(s) 4 − −− − 1 s + + − −− − + + − −− − 5 1 s 1 sc).

[

1

1

]

(

)

)

(

)

(

1

1

)

(

)

(

t

q

t

y

t

x

t

q

t

q

r

r

&

r

=

+

σ

−

ω

−

ω

σ

−

=

d).[

1

0

]

(

)

)

(

)

(

1

0

)

(

2

1

0

)

(

2t

q

t

y

t

x

t

q

t

q

r

r

&

r

=

+

ζω

−

ω

−

=

e).[

0

1

]

(

)

)

(

)

(

1

0

)

(

2

1

0

)

(

2t

q

t

y

t

x

t

q

t

q

r

r

&

r

=

+

ζω

−

ω

−

=

Daftar Pustaka

1. Sudaryatno Sudirham, “Analisis Rangkaian Listrik”, Penerbit ITB 2002, ISBN 979-9299-54-3.

2. Sudaryatno Sudirham, “Pengembangan Metoda Unit Output Untuk Perhitungan Susut Energi Pada Penyulang Tegangan Menengah”, Monograf, 2005, limited publication.

3. Sudaryatno Sudirham, “Pengantar Rangkaian Listrik”, Catatan Kuliah El 1001, Penerbit ITB, 2007.

4. Sudaryatno Sudirham, “Analisis Harmonisa Dalam Permasalahan Kualitas Daya”, Catatan Kuliah El 6004, 2008.

5. P. C. Sen, “Power Electronics” McGraw-Hill, 3rd Reprint, 1990, ISBN 0-07-451899-2.

6. Ralph J. Smith & Richard C. Dorf : “Circuits, Devices and Systems” ; John Wiley & Son Inc, 5th ed, 1992.

7. David E. Johnson, Johnny R. Johnson, John L. Hilburn : “Electric Circuit Analysis” ; Prentice-Hall Inc, 2nd ed, 1992.

8. Vincent Del Toro : “Electric Power Systems”, Prentice-Hall International, Inc., 1992.

9. Roland E. Thomas, Albert J. Rosa : “The Analysis And Design of Linier Circuits”, . Prentice-Hall Inc, 1994.

10. Douglas K Lindner : “Introduction to Signals and Systems”, McGraw-Hill, 1999.

Daftar *otasi

v atau v(t) : tegangan sebagai fungsi waktu.

V : tegangan dengan nilai tertentu, tegangan searah. Vrr : tegangan, nilai rata-rata.

Vrms : tegangan, nilai efektif.

Vmaks : tegangan, nilai maksimum, nilai puncak.

V : fasor tegangan dalam analisis di kawasan fasor. V : nilai mutlak fasor tegangan.

V(s) : tegangan fungsi s dalam analisis di kawasan s.

i atau i(t) : arus sebagai fungsi waktu.

I : arus dengan nilai tertentu, arus searah. Irr : arus, nilai rata-rata.

Irms : arus, nilai efektif.

Imaks : arus, nilai maksimum, nilai puncak.

I : fasor arus dalam analisis di kawasan fasor. I : nilai mutlak fasor arus.

I(s) : arus fungsi s dalam analisis di kawasan s.

p atau p(t) : daya sebagai fungsi waktu. prr : daya, nilai rata-rata.

S : daya kompleks.

|S| : daya kompleks, nilai mutlak.

P : daya nyata.

Q : daya reaktif.

q atau q(t) : muatan, fungsi waktu.

w : energi. R : resistor; resistansi. L : induktor; induktansi. C : kapasitor; kapasitansi. Z : impedansi. Y : admitansi.

TV (s) : fungsi alih tegangan.

TI (s) : fungsi alih arus.

TY (s) : admitansi alih.

TZ (s) : impedansi alih.

µ : gain tegangan.

β : gain arus.

r : resistansi alih, transresistance.