Ratnalita, Affandi, Design Skematik ... 41 DESIGN SKEMATIK DAN LAYOUT ANALOG 8-BIT ADC

ASYNCHRONOUS MENGGUNAKAN TEKNOLOGI CMOS 0,35 𝝁M

Indah Rizky Ratnalita1

Hamzah Affandi2

1,2Jurusan Teknik Elektro, Fakultas Teknologi Industri, Universitas Gunadarma 1[email protected]

Abstrak

Desain 8-bit ADC (Analog to Digital Converter) pada penelitian ini dirancang untuk kamera kecepatan tinggi yang dapat mengkonversi sensor kamera analog ke dalam bentuk digital. Pemelitian ini menggunakan arsitektur dan menggunakan teknologi CMOS AMS 0,35 μm. Desain ini akan disimulasikan menggunakan software untuk mendapatkan desain yang efektif. Pada desain asynchronous analog ADC membutuhkan sirkuit sample and hold yang merupakan tempat konversi sampling sinyal analog untuk menstabilkan teganga pada saat pengambilan sample. Rangkaian sakelar kapasitor untuk umpan balik pada sinyal digital serta penyedia tegangan referensi untuk komparator, rangkaian tersebut memerlukan 8 saklar kapasitor. Langkah pertama adalah membuat desain skematis dari rangkaian sample and hold, lalu mensimulasikan skematiknya. Setelah itu, buatlah skematik desain sakelar kapasitor dan mensimulasikannya. Jika kedua rangkaian telah disimulasikan, langkah selanjutnya adalah membuat layout desain sample and hold dan layout desain sakelar kapasitor. Pada layout desain tidak ada simulasi desain, oleh karena itu harus diperiksa kembali supaya desain sudah sesuai dengan skematik desain. Kemudian, diverifikasi tata letak. Hasil asynchronous analog 8 bit ini memiliki spesifikasi kecepatan 100 MHz, menghasilkan daya sebesar 215.367 pW, area layout 92,95 μm × 188,85 μm = 17553,6 μm². ADC analog 8 bit membutuhkan 23 transistor CMOS dan 17 kapasitor.

Kata Kunci : ADC (Analog to Digital Converter), CMOS, Mentor Graphics, Sample and

Hold, Sakelar Kapasitor.

DESIGN SCHEMATIC AND ANALOG LAYOUT 8-BIT ASYNCHRONOUS ADC USING 0.35 ΜM CMOS TECHNOLOGY

Abstract

The 8-bit ADC (Analog to Digital Converter) design of this research is designed for high speed cameras that can convert analog camera sensors into digital form. This research uses architecture and uses 0.35 μm AMS CMOS technology. This design will be simulated using the software to get an effective design. In analog asynchronous design ADC requires a sample and hold circuit that is a place for analog signal sampling conversion to stabilize teganga at the time of sampling. The circuit of the capacitor switch for feedback on the digital signal as well as the reference voltage provider for the comparator, the circuit requires 8 capacitor switches. The first step is to make a schematic design of the sample and hold circuit, then simulate the schematic. After that, make a schematic design of the capacitor switch and simulate it. If both circuits have been simulated, the next step is to make layout of sample and hold design and layout of capacitor switch design. In the design layout there is no design simulation, therefore it should be checked again so that the design is in accordance with the schematic design. Then, verified the layout. Asynchronous 8-bit analogue results have a specification speed of 100 MHz, resulting in power

42 Jurnal Teknologi Rekayasa Volume 21 No.1, April 2016 of 215,367 pW, layout area 92.95 μm × 188.85 μm = 17553,6 μm². 8 bit analog ADC requires 23 CMOS transistors and 17 capacitors.

Keywords: ADC (Analog to Digital Converter), CMOS, Mentor Graphics, Sample and Hold,

Capacitor Switch.

PENDAHULUAN

Mikroelektronika adalah cabang elektronika yang berkaitan dengan minia-turisasi Integrated Circuit (IC) [Thomas Roger, 1999]. IC (Integrated Circuit) adalah komponen semikonduktor yang terdiri dari ratusan atau bahkan seribu komponen lainnya yang merupakan kom-binasi dari beberapa komponen seperti resistor, kapasitor, dioda dan transistor yang telah terintegrasi menjadi rangkaian chip kecil yang terbentuk [Allier E., Goulier J., Sicard G., and Renaudin M, 2008]. Produksi rangkaian Ultralarge Scale Integrated (ULSI) hanya dimung-kinkan karena platform teknologi CMOS (Complementary Metal Oxide Semicon-ductor) karena sifat bertenaga rendah.

ADC (Analog to Digital Converter) adalah alat yang mengubah sinyal analog menjadi sinyal digital. Di kamera berkecepatan tinggi, fungsi ADC adalah mengubah sensor kamera pixel yang dihasilkan analog menjadi bentuk digital data yang akan disimpan ke dalam piksel digital [Cheongyuen B.T, 2008]. Karena ditanam di kamera kecepatan tinggi maka harus memiliki spesifikasi untuk kecepatan tinggi, resolusi tinggi, ukuran kecil, dan konsumsi daya rendah.

Beberapa tipe ADC adalah flash, pipeline, SAR dan sigma delta. Penelitian sebelumnya yang dilakukan oleh Hamzah Afandi [Hamzah Afandi, 2009], ia merancang pipeline ADC dengan metode 1 bit / stage. Desain ADC ini merupakan bagian yang tertanam pada kamera yang memiliki kecepatan sistem sensor 80 MSPS sesuai dengan spesifikasi sensor kamera yang diciptakan oleh Jerome Dubois. Pipeline ADC yang telah diran-cang memiliki kekurangan saat konversi,

yaitu hasil sistem waktu delay sinkron sehingga jumlah konversi berkurang. Pada komponen desain menggunakan sirkuit SHA dan DAC konvensional, yang pada gilirannya membuat daya yang relatif besar karena ukuran CMOS yang besar pula.

Peneliti lainnya adalah Song B. S., La Jolla, dan Gilman merancang CMOS Analog menjadi Digital Converter [Song B. S., La Jolla, and Gilman, 2007]. Selanjutnya Yulisdin Mukhlis mendesain 4 Bit Elektrokardiograph Tertanam dengan Peubah Analog ke Digital Tipe Single Slope Berbasis Teknologi 0.35µm [Yulisdin M, 2013].

Asynchronous ADC adalah modifi-kasi dari ADC yang ada, dimana sam-plingnya tidak bersamaan namun dengan setiap clock pada masing-masing bit individu. Pada tipe asynchronous design diharapkan dapat memperbaiki sisi waktu karena akan mengurangi waktu delay.

Untuk mendapatkan ADC yang bisa diimplementasikan di area embedded system perlu dioptimalkan pada desain layout, dalam penelitian ini menggunakan teknologi CMOS 0,35 μm.

METODE PENELITIAN

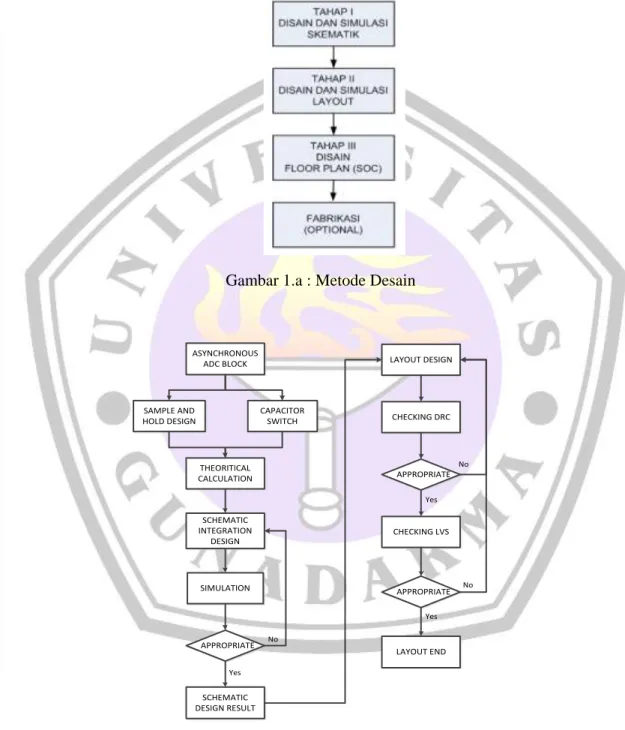

Pada penelitian 8-bit Asynchronous Analog ADC ini memerlukan beberapa tahapan untuk mencapai fabrikasi. Tahap pertama yaitu berupa skematik yang menghasilkan simulasi prototype dengan diberi masukan sinyal kecepatan tinggi. Tahap selanjutnya adalah pembuatan layout yang merupakan bentuk nyata dari hasil skematik, kemudian diolah sesuai teknologi CMOS dalam bentuk floor plan atau System On Chip (SOC). Hasil dari SOC akan diterapkan untuk fabrikasi.

Ratnalita, Affandi, Design Skematik ... 43 Pada penelitian ini dikonsentraskan

pada skematik desain dan layout desain. Software yang digunakan adalah Mentor Graphic supaya menghasilkan desain yang efektif dan bisa disimulasikan agar

terlihat output dari desain yang telah dibuat. Berikut adalah langkah-langkah untuk mendesain 8-bit analog Asyn-chronous.

Gambar 1.a : Metode Desain

ASYNCHRONOUS ADC BLOCK SAMPLE AND HOLD DESIGN CAPACITOR SWITCH THEORITICAL CALCULATION SCHEMATIC INTEGRATION DESIGN SIMULATION APPROPRIATE No LAYOUT DESIGN CHECKING DRC APPROPRIATE CHECKING LVS Yes APPROPRIATE LAYOUT END SCHEMATIC DESIGN RESULT Yes No No Yes

44 Jurnal Teknologi Rekayasa Volume 21 No.1, April 2016

HASIL DAN PEMBAHASAN

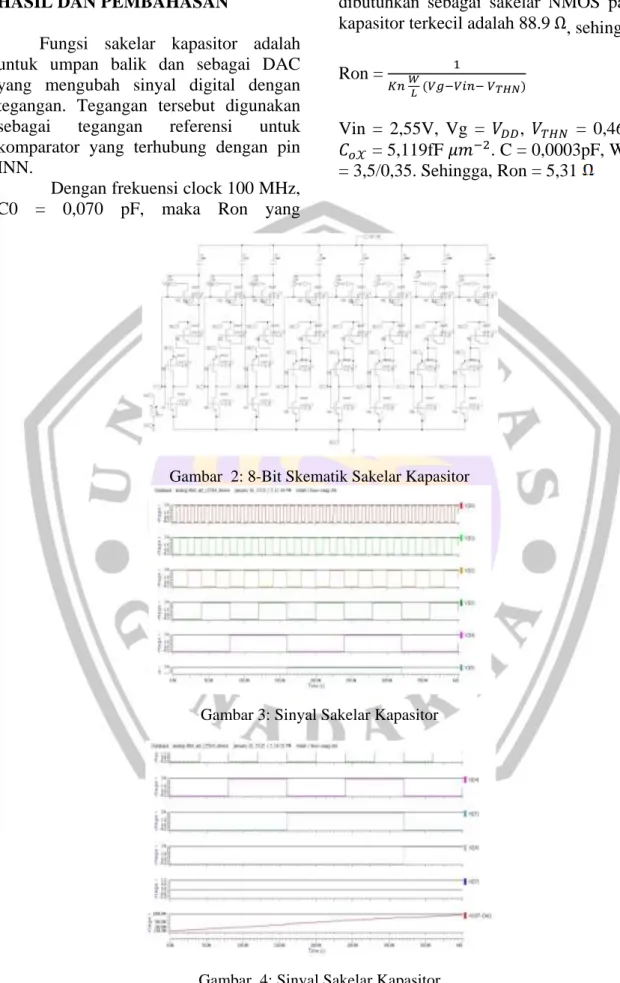

Fungsi sakelar kapasitor adalah untuk umpan balik dan sebagai DAC yang mengubah sinyal digital dengan tegangan. Tegangan tersebut digunakan sebagai tegangan referensi untuk komparator yang terhubung dengan pin INN.

Dengan frekuensi clock 100 MHz, C0 = 0,070 pF, maka Ron yang

dibutuhkan sebagai sakelar NMOS pada kapasitor terkecil adalah 88.9 Ω, sehingga

Ron = 1

𝐾𝑛 𝑊𝐿 (𝑉𝑔−𝑉𝑖𝑛− 𝑉𝑇𝐻𝑁)

Vin = 2,55V, Vg = 𝑉𝐷𝐷, 𝑉𝑇𝐻𝑁 = 0,46V, 𝐶𝑜𝒳 = 5,119fF 𝜇𝑚−2. C = 0,0003pF, W/L

= 3,5/0,35. Sehingga, Ron = 5,31

Gambar 2: 8-Bit Skematik Sakelar Kapasitor

Gambar 3: Sinyal Sakelar Kapasitor

Ratnalita, Affandi, Design Skematik ... 45 Input data yang diberikan untuk

kapasitor switch adalah data digital yaitu 0 dan 1 yang merupakan input D0 – D6. Kemudian output akan ditampilkan pada V (OUT_DAC). Masukkan data digital berupa 0 dan 1 yang diberi variasi dengan resolusi 4 bit, dan tegangan referensi (Vref) = 2,55 V. Data digital diubah kembali menjadi tegangan analog dengan perhitungan sebagai berikut:

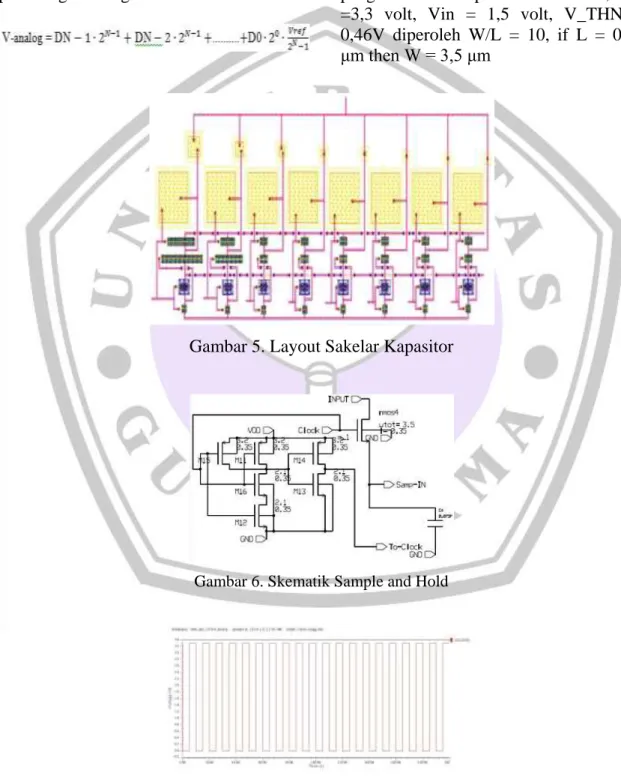

Desain Sample and Hold

Pada unit sirkuit sample and Hold adalah rangkaian saklar CMOS dengan kapasitor, sample and hold digunakan untuk menstabilkan tegangan saat pengambilan sampel apabila saklar dima-tikan dan tegangan tidak menjadi 0 namun dipertahankan oleh kapasitor sehingga besarnya arus akan tetap saat pengambilan sampel. Ron = 446, Vg =3,3 volt, Vin = 1,5 volt, V_THN = 0,46V diperoleh W/L = 10, if L = 0,35 μm then W = 3,5 μm

Gambar 5. Layout Sakelar Kapasitor

Gambar 6. Skematik Sample and Hold

46 Jurnal Teknologi Rekayasa Volume 21 No.1, April 2016

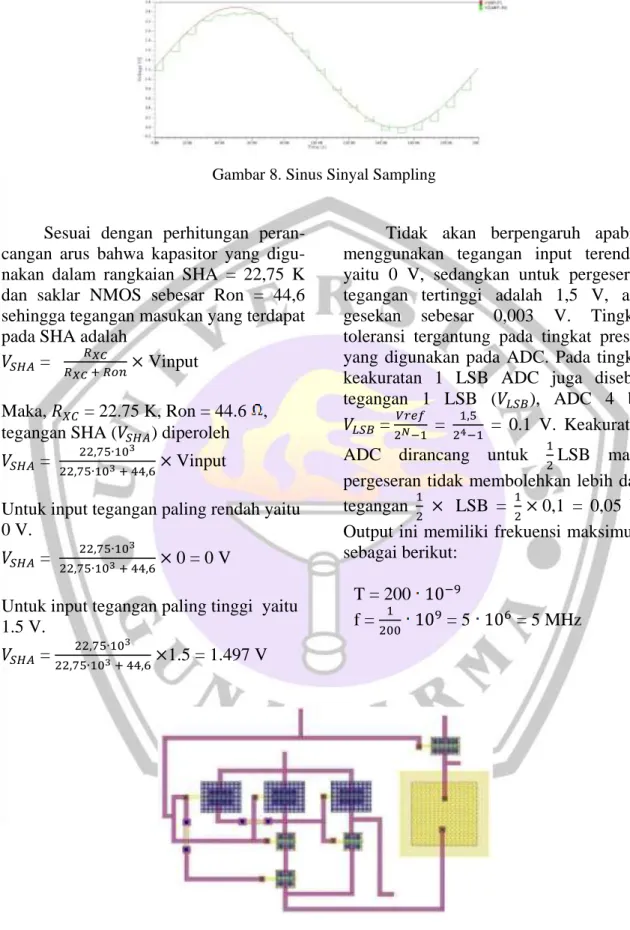

Gambar 8. Sinus Sinyal Sampling

Sesuai dengan perhitungan peran-cangan arus bahwa kapasitor yang digu-nakan dalam rangkaian SHA = 22,75 K dan saklar NMOS sebesar Ron = 44,6 sehingga tegangan masukan yang terdapat pada SHA adalah

𝑉𝑆𝐻𝐴 = 𝑅 𝑅𝑋𝐶

𝑋𝐶 + 𝑅𝑜𝑛× Vinput

Maka, 𝑅𝑋𝐶 = 22.75 K, Ron = 44.6 ,

tegangan SHA (𝑉𝑆𝐻𝐴) diperoleh

𝑉𝑆𝐻𝐴 = 22,75∙10

3

22,75∙103 + 44,6× Vinput

Untuk input tegangan paling rendah yaitu 0 V.

𝑉𝑆𝐻𝐴 = 22,75∙10

3

22,75∙103 + 44,6× 0 = 0 V

Untuk input tegangan paling tinggi yaitu 1.5 V.

𝑉𝑆𝐻𝐴 = 22,75∙10

3

22,75∙103 + 44,6×1.5 = 1.497 V

Tidak akan berpengaruh apabila menggunakan tegangan input terendah yaitu 0 V, sedangkan untuk pergeseran tegangan tertinggi adalah 1,5 V, ada gesekan sebesar 0,003 V. Tingkat toleransi tergantung pada tingkat presisi yang digunakan pada ADC. Pada tingkat keakuratan 1 LSB ADC juga disebut tegangan 1 LSB (𝑉𝐿𝑆𝐵), ADC 4 bit 𝑉𝐿𝑆𝐵 = 2𝑉𝑟𝑒𝑓𝑁−1 = 21,54−1 = 0.1 V. Keakuratan ADC dirancang untuk 1

2 LSB maka

pergeseran tidak membolehkan lebih dari tegangan 1

2 × LSB = 1

2× 0,1 = 0,05 V.

Output ini memiliki frekuensi maksimum sebagai berikut:

T = 200 10−9

f = 2001 109 = 5 106 = 5 MHz

Ratnalita, Affandi, Design Skematik ... 47

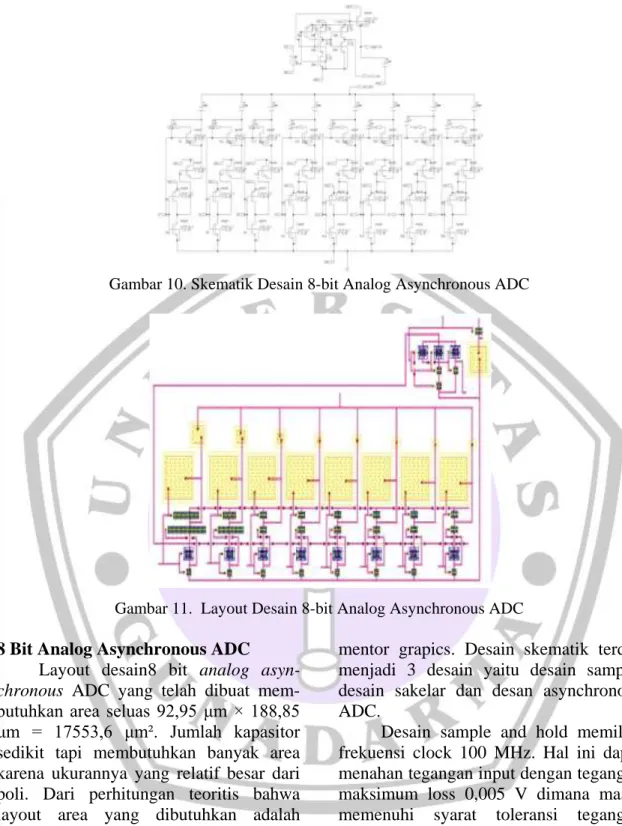

Gambar 10. Skematik Desain 8-bit Analog Asynchronous ADC

Gambar 11. Layout Desain 8-bit Analog Asynchronous ADC

8 Bit Analog Asynchronous ADC

Layout desain8 bit analog asyn-chronous ADC yang telah dibuat mem-butuhkan area seluas 92,95 μm × 188,85 μm = 17553,6 μm². Jumlah kapasitor sedikit tapi membutuhkan banyak area karena ukurannya yang relatif besar dari poli. Dari perhitungan teoritis bahwa layout area yang dibutuhkan adalah 13039,54 μm². Ada perbedaan luas di area 4514,06 μm².

SIMPULAN

Penelitian ini membahas desain skematik ADC asynchronous analog yang akan diterapkan pada desain layout. Dengan menerapkan teknologi AMS AMS 0,35 m dan menggunakan software

mentor grapics. Desain skematik terdiri menjadi 3 desain yaitu desain sample, desain sakelar dan desan asynchronous ADC.

Desain sample and hold memiliki frekuensi clock 100 MHz. Hal ini dapat menahan tegangan input dengan tegangan maksimum loss 0,005 V dimana masih memenuhi syarat toleransi tegangan terhadap akurasi LSB yaitu 0,005 V. Desain sakelar capasitor memiliki nilai kapasitor kurang dari 10 pF, yaitu 0.0003p, 0,0005p, 0,0009p, 0,002p, 0,004p, 0,009p, 0,018p, 0,035p, 0,075p. Ini mampu menghasilkan umpan balik tegangan residu linier dari konversi data digital accuracy. Desain asynchronous ADC analog memiliki spesifikasi

kece-48 Jurnal Teknologi Rekayasa Volume 21 No.1, April 2016 patan 100 MSPS, resolusi 8 bit, 215.367

pW.

Sedangkan untuk desain layout analog asynchronous mempunyai luas 17553.6 𝜇𝑚2 dan desain sample and hold

design mempunyai area layout 1314.95 𝜇𝑚2 dan sesuai skematik sample

and hold. Sedangkan Desain Sakelar Ka-pacitor mempunyai area layout 11724.59 𝜇𝑚2 area layout dan sesuai

skematik sakelar kapasitor.

DAFTAR PUSTAKA

Afandi H, 2009. “Disain Konverter Analog ke Digital Pipeline Berbasis Teknologi CMOS Tertanam Untuk Aplikasi Kamera Kecepatan Tinggi”, Universitas Gunadarma, Jakarta. Allier E., Goulier J., Sicard G., and

Renaudin M, 2008. “A 120nm Low Power Asynchronous ADC”, ISLPED. Cao Z, Yan S, and Li Y, 2009. “A 32 mW

1,25 GS/s 6b 2b Step SAR ADC in 0,13 μm CMOS”, IEEE Journal of Solid State Circuits, vol.44, no.3, pp 862-873.

Cheongyuen B.T, 2008. “Digitally Calibrated Analog-to-Digital Converters in Deep Submicron CMOS”, No.67 UCB/EECS.

Der Plas G. V., and Verbruggen B., 2008. ”A 150 ms/n 133 μW 7b ADC in 90 nm digital CMOS Using a comparator-based asynchronous binary-search sub

ADC”, Solid state circuit conference, IEEE International, pages 242-243. Kristianti V.E., 2010. “Designing

Equivalent Circuit High-Pass Filter for Circuit Broadband CMOS Frequency Triple Using Mentor Graphics”, Universitas Gunadarma, Jakarta. (chapter 1)

Mukhlis Y., 2013. “Desain 4 Bit Elektrokardiograph Tertanam dengan Peubah Analog ke Digital Tipe Single Slope Berbasis Teknologi 0.35µm Proses”, Universitas Gunadarma, Jakarta

Purnomo J, 2011. “Disain Pengubah Analog ke Digital (ADC) Jenis Asynchronous Berbasis Teknologi 0.35µm CMOS Proses”, Universitas Gunadarma, Jakarta.

Roger T., 1999. “Microelectric Design and Implementation”, Printice Hill, University of California.

Seung-Chul Lee, Young-Deuk Jeon, and Jong-Kee Kwon, 2007. “A 9-Bit 80-MS/s CMOS Pipelin Folding A/D Converter With an Offset Canceling Technique”, ETRI Journal, Volume 29, Number 3.

Song B. S., La Jolla, and Gilman, 2007. “Design CMOS Analog to Digital Converter”, ECE264C, International Workshop in University of California, San Diego. (bab 1)

Tulabandhula T., and Mitikiri Y., 2009. “A 20MS/s 5.6mW 6b Asynchronous ADC in 0.6um CMOS”, IEEE VLSI Design, 22nd, pp. 111-116.