TUGAS AKHIR

Diajukan untuk memenuhi salah satu syarat Memperoleh gelar Sarjana Teknik pada

Program Studi Teknik Elektro Fakultas Teknik Universitas Sanata Dharma

Disusun oleh:

EKO HENDRI YETNO

NIM : 005114098

PROGRAM STUDI TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

2007

FINAL PROJECT

Presented as Partial Fulfillment of the Requirements To Obtain the Sarjana Teknik Degree

in Electrical Engineering Study Program

By

:

EKO HENDRI YETNO

NIM : 005114098

ELECTRICAL ENGINEERING STUDY PROGRAM

ELECTRICAL ENGINEERING DEPARTMENT

ENGINEERING FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

2007

v

ini tidak memuat karya atau bagian karya orang lain, kecuali yang telah

disebutkan dalam kutipan dan daftar pustaka, sebagaimana layaknya karya ilmiah.

Yogyakarta, Juli 2007

Penulis

....Ku Persembahkan Karya Ilmiah ini untuk penebusku dan

penyelamatku Tuhan Yesus Kristus yang memberi anugerah

yang tak ternilai dengan apapun di dunia ini.

....Untuk Kedua orang tua kandungku dan kedua orang tua angkatku

yang telah membesarkanku dengan kasih sayangnya dan

selalu mendoakan dan memberi semangat di dalam hidupku.

....Untuk kedua adikku terimakasih atas doa dan dukungannya

sehingga saya dapat menyelesaikan karya ilmiah ini.

....Untuk nenekku yang sungguh mengasihiku

....Untuk seseorang yang menjadi inspirasiku yang mewarnai

hidupku dengan sejuta tawa dan kebahagian..

Takut akan Tuhan adalah permulaan pengetahuan, tetapi

orang bodoh menghina hikmat dan didikan.

(Amsal 1:7 )

Sesederhana apapun di kehidupan kita baik senang,

sedih, tertawa, menangis dan apapun itu juga, datangnya

dari Allah atas dasar kasih karuniaNya dan kerelaanNya

oleh karena itu kita harus senantiasa bersyukur di

dalam kehidupan kita dan bermazmur di dalam namaNya.

Takut gagal menghalangi kita untuk Mencoba Meraih

sukses, takut kalah menghalangi kita untuk mencoba

meraih kemenangan, takut apa kata orang menghalangi

kita untuk melangkah dengan berani, takut dicemooh

menghalangi kita untuk menyatakan iman kita kepada

Tuhan, diatas segalanya, ketakutan itu mencekik

pengharapan. ( Rich Devos)

All Beginning is difficult but Every Cloud has a silver

lining. Semua Permulaan adalah sulit tetapi di dalam

kesedihan/kesesakan selalu ada pengharapan akan

kebahagiaan.

viii

mampu mendeteksi kesalahan lebih dari satu bit kesalahan tetapi hanya mampu mengoreksi 1 bit data kesalahan.

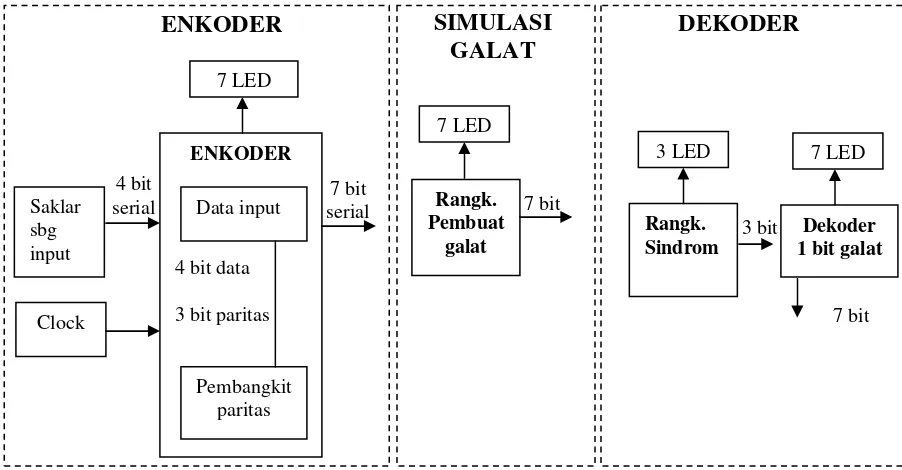

Sandi blok linear dibagi menjadi 4 bagian besar utama yaitu rangkaian penyandi ( Encoder ), Pembuat galat, rangkaian deteksi ( Sindrom ) dan rangkaian koreksi. Empat bit vektor pesan di masukkan ke dalam rangkaian penyandi secara seri melalui saklar dan selanjutnya diproses pada rangkaian penyandi sehingga menghasilkan 3 bit paritas. Hasil dari proses oleh rangkaian penyandi membentuk vektor sandi yang terdiri dari 7 bit data yang selanjutnya dikirimkan ke rangkaian sindrom melalui sebuah rangkaian pembuat galat. Bila kita menginginkan bahwa vektor sandi yang dikirimkan diberi galat, maka pemberian galat dilakukan pada rangkain pembuat galat. Rangkaian sindrom akan mendeteksi vektor sandi yang diterima, apakah ada galat atau tidak ada galat dan selanjutnya dikoreksi pada rangkaian pengkoreksi. Hasil dari rancangan ini di tampilkan dengan LED.

ix just one bit error datum.

The linear block (7,4) code consists of four main parts, that are : Encoder circuit, error generator circuit, error detector circuit or syndrome circuit and error corection. First the four bit message vector are put into the encoder circuit serially through an switch, then those codes processed by the encoder circuit produce three bit parity. The result of this procces forms a code vector consisting of seven bit data. The data will be sent to the syndrome circuit through the error generator circuit. If we want the code vector sent is given any error, it should be done in the error generator circuit. The syndrome circuit will detect the code vector received whether there is any error or not. At last the code will be corrected in the error corection circuit. The result of design is showed by LED.

x

karena kasih dan penyertaan-Nya sehingga penulis dapat meyelesaikan Tugas

Akhir yang berjudul “Enkoder Dan Dekoder Sandi Blok Linear (7,4) Berbasis

Digital”. Tugas Akhir ini disusun sebagai salah satu syarat untuk memperoleh

gelar Sarjana pada jurusan Teknik Elektro, Fakultas Teknik Universitas Sanatha

Dharma Yogyakarta. Dalam penyusunannya, banyak pihak yang telah membantu

dan memberikan dukungan pada penulis, oleh karena itu, penulis ingin

mengucapkan terima kasih kepada:

1. Ibu Ir. Th. Prima Ari Setyani, M.T. sebagai pembimbing yang membagikan

semua ilmu-ilmu elektronika dan pengalaman yang dimilikinya dalam

membantu proses penyusunan tugas akhir ini.

2. Segenap karyawan / karyawati Universitas Sanata Dharma.

3. Bapak, Ibu, dan Eyang Puti yang tidak pernah berhenti memberikan doa,

semangat dan dukungannya.

4. Adik-adikku : Sugianto dan Annisa yang tidak pernah berhenti memberikan

doa, semangat dan dukungannya.

5. Keluarga besar pelayanan Para Navigator Regu B Yogyakarta, yang

memberikan dukungan dan doanya.

6. Kel. Abu Prawoto dan Mas Nug terimakasih sekali karena terus mendukungku

tidak hanya di dalam doa tetapi sering mentraktirku dan sebagai sahabat

terbaikku di dalam susah maupun senang dan juga mengajarkan tentang

makna hidup yang sesungguhnya.

7. Untuk Saudara-saudaraku di negeri sebrang : Mas Andre di banjarmasin, Mas

marcel dan Mas udut di Mataram Dan teman-teman AL Malang 2006 Uci Lisa

dan Bu Dovi di Ambon , Cak luhu dan Mb Santi di Surabaya, Bang Nara dan

Mb Ris di Yogyakarta, Mas Hananto, Mb Tyas dan Mb Nana Di Semarang,

Mas Yudha di purwokerto dan juga Mb Martina di bandung. Terimakasih atas

xi

Ignas, Kim, Zendy, Marsel Boli, Eny, Onsha, Pak leo, Aan, Agung Greg dan

untuk semuanya yang tidak dapat disebutkan satu per satu..

9. Untuk Felik makasih atas bantuan pemikirannya untuk menyelesaikan alat TA

ini.

Dalam penyusunan Tugas Akhir ini, penulis menyadari bahwa dalam

perancanggan Tugas Akhir ini masih banyak kekurangannya karena

keterbatasan kemampuan serta pengetahuan dari penulis. Oleh karena itu,

saran dan kritik yang membangun dari semua pembaca sangat penulis

harapkan.

Akhir kata, semoga Tugas Akhir ini dapat bermanfaat dan berguna bagi

yang membutuhkan.

Yogyakarta, 25 Juli 2007

xii

HALAMAN PERSETUJUAN ... iii

HALAMAN PENGESAHAN ... iv

PERNYATAAN KEASLIAN KARYA ... v

HALAMAM PERSEMBAHAN... vi

HALAMAN MOTTO... vii

INTISARI ... viii

ABSTRACT ... ix

KATA PENGANTAR ... x

DAFTAR ISI ... xii

DAFTAR TABEL ... xv

DAFTAR GAMBAR ... xvi

DAFTAR LAMPIRAN ...xviii

BAB I PENDAHULUAN 1.1. Judul ... 1

1.2. Latar belakang ... 1

1.3. Tujuan Penelitian ... 2

1.4. Manfaat Penelitian ... 2

1.5. Perumusan Masalah ... 2

1.6. Batasan Masalah ... 3

1.7. Metodologi Penelitian ... 3

BAB II DASAR TEORI 2.1. Sandi Blok Linear ... 5

2.1.1 Enkoder ... 5

2.1.2 Matrik Generator ... 6

2.1.3 Rangkaian Pembuat galat ... 8

2.1.4 Rangkaian Sindrom ... 8

2.1.5 Rangkaian Koreksi ... 9

xiii

2.7. Pencacah Modulo 14 ... 14

2.8. Pembanding / Comparator ... 16

2.9. Penyandi BCD Ke Tujuh Segmen ... 17

2.10. Tujuh Segmen ... 19

2.11. Saklar ... 20

2.12. LED ( Light Emiting Diode) ... 21

2.13. Penambah Penuh ( Full Adder ) ... 22

BAB III RANCANGAN PENELITIAN 3.1. Saklar ... 25

3.2. Rangkaian Enkoder ... 25

3.2.1 Perancangan Matrik Generator ... 25

3.2.2. Register ... 31

3.2.3 Switch ... 32

3.2.3.1 Switch 1... 32

3.2.3.2 Switch 2 ... 33

3.2.3.3 Switch 3 ... 34

3.3. Rangkaian Pembuat Galat ... 35

3.4. Rangkaian Sindrom ... 36

3.5. Rangkaian Koreksi ... 41

3.6. Counter / Pencacah Modulo 14 ... 45

3.7. Pembanding / Comparator ... 46

3.7.1. Pembanding / Comparator 1 ... 47

3.7.2. Pembanding / Comparator 2 ... 48

3.7.3. Pembanding / Comparator 3 ... 49

3.7.4. Pembanding / Comparator 4 ... 50

3.8. Penjunlah Penuh / Full Adder ... 51

xiv

4.1. Analisa Rangkaian Sindrom ……… 56

4.1.1. Analisa Rangkaian Sindrom Dengan Data Tanpa Galat ………… 56 4.1.2. Analisa Rangkaian Sindrom Dengan Data Galat 1 Bit ………… 57

4.1.3. Analisa Rangkaian Sindrom Dengan Data Galat lebih 1 Bit …… 58

4.2. Analisa Pada Rangkain Koreksi 59

BAB V KESIMPULAN DAN SARAN

5.1. Kesimpulan ……….. 61

5.2. Saran ... 61

DAFTAR PUSTAKA...

xv

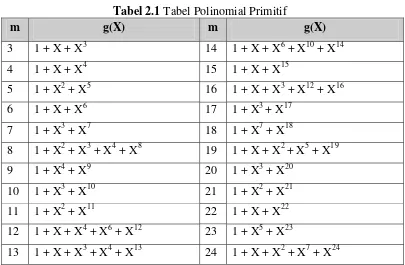

Tabel 2-1. Tabel Polinomial Primitif ...………… 6

Tabel 2-2. Tabel Kebenaran Gerbang Logika Dasar ………... 10

Tabel 2-3. Tabel Kebenaran D Flip-flop ………..…. 11

Tabel 2-4. Tabel Kebenaran JK Flip-flop …….…………... 12

Tabel 2-5. Tabel Kebenaran IC Pengunci ………. 13

Tabel 2-6. Tabel Pencacah Modulo-14 ...………... 15

Tabel 2-7. Tabel Kebenaran Pembanding / Comparator ...……... 16

Tabel 2-8. Tabel Jalur tujuh Segmen .………...…… 18

Tabel 2-9. Tabel Kebenaran Penambah Penuh ...………... 23

Tabel 3.1 Tabel Keluaran Enkoder... 29

Tabel 3-2. Tabel Kebenaran Switch 1 ... 32

Tabel 3-3. Tabel Peta Karnaugh Switch 1 ……….………... 33

Tabel 3-4. Tabel Kebenaran Switch 2 ...………...………... 33

Tabel 3-5. Tabel Peta Karnaugh Switch 2 ..……...………... 34

Tabel 3-6. Tabel Kebenaran Switch 3 ………... 34

Tabel 3-7. Tabel Peta Karnaugh Switch 3 ………...………... 35

Tabel 3-8. Tabel Pola Sindrom ...…………...………... 41

Tabel 4-1. Tabel Keluaran Enkoder ... 55

Tabel 4-2. TabelHasil Sindrom Tanpa Galat ... 56

Tabel 4-3. Tabel Hasil Sindrom Dengan Galat 1 bit ... 57

Tabel 4-4. Tabel Hasil Sindrom Dengan Galat 1 bit ... 57

Tabel 4.5. Tabel Hasil Sindrom Dengan Galat lebih dari 1 ... 58

Tabel 4-6. Tabel Rangkaian koreksi dengan galat 1 bit ... 59

xvi

Gambar 2-2. Gambar Simbol D-FF ………..…... 11

Gambar 2-3. Gambar JK-FF ...………….…… 12

Gambar 2-4. Gambar IC Pengunci 74LS75 ...………..…… 13

Gambar 2-5. Gambar Register geser SIPO ……… 14

Gambar 2-6. Gambar Pencacah Sinkrom Modulo-14 ...…..…… 15

Gambar 2-7. Gambar Rangkaian Pembanding ………... 16

Gambar 2-8. Gambar IC 74LS85 ...……... 17

Gambar 2-9. Gambar Untai Penampil Tujuh Segmen ...……... 19

Gambar 2-10. Gambar Saklar Toggle ………... 20

Gambar 2-11. Gambar Foto Saklar Toggle ...……….………... 20

Gambar 2-12. Gambar simbol LED .………....……….... 21

Gambar 2-13. Gambar Rangkaian LED ....……….………... 22

Gambar 2-14. Gambar Rangkaian Full Adder ..…………...………. 22

Gambar 2-15. Gambar IC 74LS83 .………....………... 23

Gambar 3-1. Gambar Blok Diagram Enkoder Dan Dekoder Sandi Blok Linear (7,4) ... 24

Gambar 3-2. Gambar Saklar Toggle 3 kaki ………... 27

Gambar 3-3. Gambar Blok Diagram Enkoder sandi Blok linear (7,4) ………..………... 28

Gambar 3-4. Gambar Perancangan Enkoder Sandi Blok Linear (7,4) ... 30

Gambar 3-5. Gambar SIPO IC 74LS165 ………...………... 31

Gambar 3-6. Gambar D-FF IC 74LS74 ……….………..… 31

Gambar 3-7. Gambar Rangkain Switch 1 ...………..…... 32

Gambar 3-8. Gambar Rangkaian Switch 2 ...………..…... 33

Gambar 3-9. Gambar Rangkaian Switch 3 ………..…… 34

xvii

Linear (7,4) ………... 40

Gambar 3-13. Gambar Rangkaian Koreksi ……….. 42

Gambar 3-14. Gambar Perancangan Counter Modulo 14 ……... 45

Gambar 3-15. Gambar Keluaran Simulasi Counter Modulo 14 ...

Gambar 3-16. Gambar Perancangan Pembanding 1 ...

Gambar 3-17. Gambar Keluaran Simulasi Pembanding 1 ...

Gambar 3-18. Gambar Perancangan Pembanding 2 ...

Gambar 3-19. Gambar Keluaran Simulasi Pembanding 2 ...

Gambar 3-20. Gambar Perancangan Pembanding 3 ...

Gambar 3-21. Gambar Keluaran Simulasi Pembanding 3 ...

Gambar 3-20. Gambar Perancangan Pembanding 4 ...

Gambar 3-21. Gambar Keluaran Simulasi Pembanding 4 ...

Gambar 3-24. Gambar Perancangan Full Adder ...…..………... 48

Gambar 3-25. Gambar Perancangan IC Pengunci ………….……….. 49

Gambar 3-26. Gambar Tampilan Keluaran Enkoder .……….. 49

Gambar 3-27. Gambar Tampilan Keluaran Simulasi Galat ... 50

xviii

Lampiran 1 Rangkaian Enkoder Sandi Blok Linear (7,4)

Lampiran 2 Rangkaian Galat Sandi Blok Linear (7,4)

Lampiran 3 Rangkain Sindrom Sandi Blok Linear (7,4)

Lampiran 4 Rangkaian Dekoder Sandi Blok Linear (7,4)

Lampiran 5 Data sheet

¾ 74LS04

¾ 74LS08

¾ 74LS10

¾ 74LS11

¾ 74LS32

¾ 74LS47

¾ 74LS74

¾ 74LS75

¾ 74LS76

¾ 74LS83

¾ 74LS85

BAB I

PENDAHULUAN

1.1.

Judul

Enkoder Dan Dekoder Galat Menggunakan Sandi Blok Linear ( 7,4) Berbasis

Digital

1.2.

Latar Belakang

Kemajuan teknologi komunikasi yang sangat pesat menyebabkan manusia

tidak lagi dibatasi oleh jarak. Untuk berkomunikasi, manusia menggunakan alat

bantu, diantaranya telephone, faximile, hand phone dan lain sebagainya. Semua

sistem ini melakukan proses transmisi data guna menyampaikan informasi. Data

yang dikirim oleh pengirim diharapkan sama dengan data yang diterima oleh

penerima.

Di dalam pengiriman data biasanya tidak lepas akan terjadinya error yang

disebabkan oleh banyak faktor. Terjadinya kesalahan ini tergantung pada media

transmisi yang sangat peka terhadap derau dan interferensi sehingga perlu dicari

suatu sandi yang dapat mendeteksi dan mengoreksi kesalahan tersebut sehingga

data yang dikirim dapat diterima secara benar dan sesuai.

Untuk menyelesaikan masalah tersebut telah banyak diciptakan sandi oleh

para ilmuwan, diantaranya adalah sandi blok linear. Menurut urutan terstruktur,

sandi blok linear termasuk dalam kategori penyandian blok (block coding). Di

dalam sandi blok linear, bit paritas dirancang untuk deteksi dan koreksi galat.

Penulis menggunakan sistem digital di dalam pembuatan alat simulator karena

dengan sistem digital akan memudahkan di dalam manipulasi data dan dengan

tujuan datanya lebih teliti karena mengunakan logika 0 dan 1.

1.3. Tujuan Penelitian

Karya tulis ini bertujuan untuk merancang dan mengimplementasikan suatu

alat yang digunakan sebagai simulator sistem penyandi, deteksi (sindrom) dan

juga koreksi galat 1 bit pada sandi Blok linear (7,4) yang berbasis digital.

1.4.

Manfaat Penelitian

Dengan dilaksanakannya penelitian ini maka diharapkan dapat

memberikan pengetahuan mengenai prinsip dasar dari pengkodean dengan

menggunakan sandi blok linear. Hasil penelitian ini diharapkan dapat digunakan

sebagai dasar pengembangan implementasi sandi Blok Linear.

1.5.

Perumusan Masalah

Di dalam perancangan enkoder dan dekoder Sandi Blok liniear ada beberapa

masalah yang harus di uraikan antara lain :

1. Menentukan bit sandi, bit data dan bit paritasnya pada rangkaian

enkodernya

2. Menentukan media apa yang digunakan di dalam penyimpanan datanya.

4. Menentukan berapa bit kesalahan yang dapat dikoreksi pada rangkaian

koreksi atau dekodernya.

5. Menentukan rangkaian atau basis apa yang digunakan di dalam

perancangannya rangkaian enkoder dan dekoder sandi blok linear (7,4).

1.6.

Batasan Masalah

Alat yang akan dibuat dibatasi :

1. Sebuah rangkaian penyandi blok Linear (7,4).

2. Sebuah rangkaian pembangkit galat 7 bit.

3. Sebuah rangkaian deteksi galat (sindrom) 3 bit.

4. Sebuah rangkaian koreksi galat 1 bit.

1.7.

Metodologi Penelitian

Untuk dapat merencanakan dan membuat peralatan sistem ini, diperlukan

langkah-langkah sebagai berikut :

1. Mencari dan mempelajari literatur tentang permasalahan yang ada.

2. Perancangan peralatan menggunakan teori yang di dapat dari berbagai

literatur yang ada untuk mendapatkan karakteristik yang sesuai dengan

spesifikasi yang ditentukan.

3. Pembuatan peralatan untuk setiap bagian sistem sesuai dengan fungsi

masing-masing dan diuji kesesuaiannya dengan hasil yang diharapkan.

Bagian tersebut selanjutnya disusun sebagai kesatuan yang utuh.

5. Menyusun Laporan.

1.7. Sistematika Penulisan

Penulisan laporan penelitian tugas akhir ini disusun dengan menggunakan

sistematika sebagai berikut :

BAB I PENDAHULUAN berisi judul, latar belakang masalah, tujuan, manfaat,

batasan masalah, metodologi penelitian dan sistematika penulisan.

BAB II DASAR TEORI ; berisi dasar-dasar teori yang digunakan dalam

pembuatan rangkaian digital pendeteksi dan koreksi galat menggunakan

sandi blok linear (7,4) dan penjelasan masing-masingnya.

BAB III PERANCANGAN ; berisi tentang penjelasan perancangan perangkat

keras rangkaian digital pendeteksi dan koreksi galat menggunakan sandi

blok linear (7,4) yang meliputi spesifikasi sistem dan cara kerja

rangkaian.

BAB IV HASIL DAN PEMBAHASAN ; berisi analisis dan pembahasan

mengenai hasil penelitian yang telah dilaksanakan.

BAB V KESIMPULAN DAN SARAN ; berisi kesimpulan hasil penelitian yang

telah dilakukan dan saran yang berisi ide-ide untuk perbaikan atau

pengembangan terhadap penelitian yang telah dilakukan.

DAFTAR PUSTAKA

2.1. Sandi Blok Linear

Sandi Blok Linear adalah salah satu jenis sandi uji paritas yang

mempunyai notasi (n, k). Penyandi mengubah blok k digit pesan (vektor pesan)

menjadi blok yang lebih panjang dengan n digit kata sandi (vektor sandi).

2.1.1. Enkoder

Enkoder adalah penyandian suatu data atau pesan untuk dikirimkan ke

tujuan dengan ditambahkan bit-bit data atau informasinya sebagai bit paritas

kesalahan dengan maksud data atau informasinya diterima oleh penerima lebih

handal. Untuk Enkoder pada sandi blok linier mempunyai vektor pesan ( k ) dan

di tambah bit-bit paritas (m) dan menjadi vektor sandi ( n ). Paritas di dapatkan

dari perkalian vektor pesan dengan matrik generator yang dibangkitkan dengan

polinomial pembangkit g(x). Untuk menentukan g(x) yang dipakai dengan

mengunakan tabel polinomial primitif.

blok pesan blok sandi

k-bit n = k + m Penyandi

Gambar 2.1 Gambar Blok Sandi Blok Linier

Untuk mendapatkan Vektor sandi ditentukan dengan rumus :

V = u . G... (2.1)

Dengan :

V = vektor sandi

U = Vektor pesan

G = Matrik generator.

Tabel 2.1 Tabel Polinomial Primitif

m g(X) m g(X)

3 1 + X + X3 14 1 + X + X6 + X10 + X14

4 1 + X + X4 15 1 + X + X15

5 1 + X2 + X5 16 1 + X + X3 + X12 + X16

6 1 + X + X6 17 1 + X3 + X17

7 1 + X3 + X7 18 1 + X7 + X18

8 1 + X2 + X3 + X4 + X8 19 1 + X + X2 + X5 + X19

9 1 + X4 + X9 20 1 + X3 + X20

10 1 + X3 + X10 21 1 + X2 + X21

11 1 + X2 + X11 22 1 + X + X22

12 1 + X + X4 + X6 + X12 23 1 + X5 + X23

13 1 + X + X3 + X4 + X13 24 1 + X + X2 + X7 + X24

2.1.2. Matrik Generator

Pada perancangan sandi blok ini dibahas bagaimana membuat matrik

generator dengan bentuk yang sesuai dengan kualitas penyandian yang

diinginkan. Dalam pembuatan matrik generator untuk mendapatkan sandi blok

dengan format sistematis diperlukan polinomial pembangkit, polinomial yang

dipilih adalah polinomial yang mempunyai pangkat tertinggi sama dengan

Untuk membuat matrik generator G dan matrik periksa paritas H yang

digunakan pada sandi blok linear dengan Hamming, dilakukan langkah sebagai

berikut :

1. Memilih polinomial primitif sesuai dengan panjang bit periksa

( P = bit paritas).

2. Membuat G dari polinomial primitif.

Dengan polinomial pembangkit, matrik generator dengan bentuk sistematis

dapat dibuat dengan mudah. Jika Xn-k+1 dibagi dengan polinomial pembangkit

g(X), dengan i = 0, 1, 2, … , 3 maka diperoleh :

X7-4+1 = ai (X) g(X) + Pi (X)... (2.2)

Dengan Pi (X) adalah sisa dalam bentuk :

Pi (X) = Pi0 + Pi1X + … + Pi,n-k-1X3 ... (2.3)

Dari koefisien tersebut dibentuk matrik k x n sebagai berikut :

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅ ⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ = 1 0 0 0 1 0 0 0 1 3 , 3 31 30 3 , 1 11 10 3 , 0 01 00 P P P P P P P P P G

matrik ini merupakan matrik generator dalam bentuk sistematis.

Atau G = [ P | Ik ]... (2.4)

G = Matrik Generator

P = Paritas yang dibangkitkan dari polinomial pembangkit.

Ik = Matrik identitas

2.1.3. Rangkaian Pembuat Galat

Pengiriman data dari penyandi dilakukan secara serial, oleh karena itu

diperlukan rangkaian pembuat galat. Rangkaian ini berfungsi untuk merubah data

yang dikirim dari penyandi, pada rangkaian ini data yang diterima ditampilkan

dengan menggunakan LED, dan galat diaktifkan dengan menghubungkannya

dengan keluaran Q, Setelah data diproses pada rangkaian pembuat galat, maka

data yang ke rangkaian deteksi kemudian ditampilkan melalui LED.

2.1.4. Rangkaian Sindrom

Setelah data (vektor sandi) dikirim pada rangkaian pembuat galat dari

enkoder, dengan melihat bit data dan bit paritas yang ada maka akan dibangkitkan

suatu kode (sindrom) yang akan menunjukkan ada suatu kesalahan data atau tidak

adanya kesalahan dari data yang dikirim.. Selanjutnya dengan melihat sindrom

yang ada galat akan diperbaiki oleh rangkaian pengoreksi.

Jika r = r1

,

r2,….,rn adalah vektor galat yang diterima,yang merupakan hasildari pengiriman V = V1

,

V2,….,Vk, V = vektor sandi. Maka r dapat ditulis sebagaiberikut :

dengan e = pola error yang terjadi pada kanal yaitu e = e1

,

e2,…,ek. Untukpengujian sindrom ini didapat dari persamaan :

S = rHT…....………... (2.6)

Sindrom adalah hasil uji paritas yang dilakukan pada vektor galat untuk

menentukan apakah vektor galat merupakan anggota himpunan kata sandi yang

benar. Jika vektor galat adalah anggota himpunan kata sandi, maka sindrom akan

sama dengan 0. Dan jika r mengandung galat yang dapat terdeteksi, maka sindrom

mempunyai elemen bernilai tidak nol yang dapat menandai adanya pola galat

tertentu.

Substitusi persamaan (2.5) dan (2.6), menghasilkan sindrom yang dapat

dituliskan sebagai berikut :

S = (V + e)HT

=VHT + eHT ………... (2.7)

karena VHT = 0 untuk semua himpunan kata sandi, maka :

S = eHT ...………... (2.8)

2.1.5. Dekoder

Rangkaian Koreksi (dekoder) adalah suatu rangkaian yang digunakan untuk

mengkoreksi suatu kesalahan yang didapat dari pengiriman data yang disebabkan

oleh beberapa faktor seperti resource ataupun mediumnya. Data yang mengalami

error ini pada rangkaian sindrom di dapatkan pola error untuk mendeteksi ada atau

C = r + e ... (2.9)

dengan :

C = Rangkaian koreksi

r = vektor galat

e = Pola error

2.2. Gerbang Logika

Gerbang Logika (logic gate) merupakan dasar pembentuk sistem digital.

Gerbang logika beroperasi dengan bilangan biner. Oleh karena itu gerbang

tersebut disebut gerbang logika biner. Tegangan yang digunakan dalam gerbang

logika adalah tinggi (high) atau rendah (low). Dalam hal ini tegangan tinggi

berarti biner 1 sedangkan tegangan rendah berarti biner 0. Harus kita ingat bahwa

gerbang logika merupakan rangkaian elektronika. Rangkaian ini hanya tanggap

(respon) terhadap tegangan tinggi (yang disebut satuan) atau tegangan rendah

(tegangan tanah) yang disebut nol.

Semua sistem digital disusun hanya menggunakan tiga gerbang logika

dasar. Gerbang-gerbang dasar ini disebut gerbang AND, gerbang OR dan gerbang

NOT.

Tabel 2.2 Tabel Kebenaran Gerbang Logika Dasar

INPUT OUTPUT

A B OR AND NOR NAND XOR NOT A NOT B

0 0 0 0 1 1 0 1 1

0 1 1 0 0 1 1 1 0

1 0 1 0 0 1 1 0 1

2.3. Delay Flip-flop ( D-FF )

D flip flop hanya mempunyai satu masukan data (D) dan satu masukan

detak (CLK). Keluaran dari tabel Q dan Q. D flip flop sering disebut flip flop

tunda. Kata “tunda” menggambarkan apa yang terjadi pada data, atau informasi

pada masukan D. Data (0 atau 1) pada masukan D di tunda 1 pulsa detak dari

pemasukan sampai keluaran . Gambar 2.2 merupakan simbol dari D-FF

dengan clock pinggiran positif.

Q

Tabel 2.3 Tabel Kebenaran D Flip-flop

Clock D Q

0 0 1 1

CK D

Q Q

Gambar 2.2 GambarSimbol D Flip-flop

2. 4. JK Flip Flop

JK flip-flop mempunyai tiga masukan yaitu dua masukan untuk data biner

dan satu masukan clock yang befungsi untuk memindahkan data dari masukan ke

keluaran serta satu keluaran normal (Q) dan keluaran komplementer (Q). Gambar

2.3 menunjukkan gambar JK flip flop. JK flip flop akan bekerja dengan clock

pinggiran negatif yaitu clock yang aktif pada transisi dari posisi rendah (0) ke

clock masukan

Keluaran (Q)

Keluaran (Q)

Q

K Q

masukan

CLK J

Gambar 2.3 GambarJK Flip-flop.

Tabel 2.4 Tabel Kebenaran Untuk JK Flip-flop.

Masukan Keluaran

Mode

operasi Clock J K Q Q

Tetap 0 0 Tidak berubah

Reset 0 1 0 1

Set 1 0 1 0

Togel 1 1 Keadaan

berlawanan

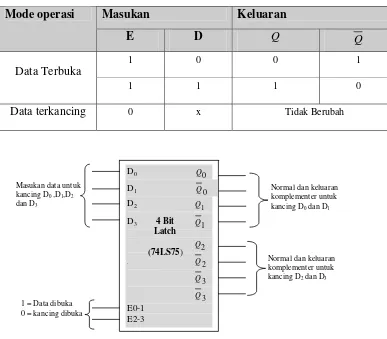

2.5. IC Pengunci

Istilah IC pengunci berhubungan dengan peralatan penyimpanan digital.

Flip-flop D merupakan contoh yang tepat dari peralatan yang digunakan untuk

mengancing data. Namun demikian, flip-flop jenis lain juga digunakan untuk

fungsi pengancing. Dari tabel 2.5 apabila kita ingin mengunci data yang kita

inginkan dengan cara enablenya di nolkan atau pada logika rendah (low) Gambar

dan tabel kebenaran yang disederhanakan untuk kancing IC 7475 diperlihatkan

Tabel 2.5 Tabel Kebenaran IC Pengunci

Masukan Keluaran

Mode operasi

E D Q Q

1 0 0 1

Data Terbuka

1 1 1 0

Data terkancing 0 x Tidak Berubah

D0 Q0

D1 Q0

D2 Q1

D3 Q1

Q2 . Q2 Q3 Q3

E0-1 E2-3

4 Bit Latch (74LS75)

1 = Data dibuka 0 = kancing dibuka Masukan data untuk kancing D0 ,D1,D2

dan D3

Normal dan keluaran komplementer untuk kancing D2 dan D3

Normal dan keluaran komplementer untuk kancing D0 dan D1

Gambar 2.4 GambarIC Pengunci 74LS75

2.6. Register Geser Serial In, Paralel Out (SIPO).

Register geser SIPO diperlihatkan pada gambar 2.5 dengan data MSB

dimasukkan terlebih dahulu. Saat pulsa clock pertama tiba, flip flop A akan terisi

data MSB dan keluarannya QA. Ketika pulsa clock kedua tiba, flip flop B akan

terisi data flip flop A dan flip flop A akan terisi oleh data masukan berikutnya dan

kelurannya QB. Ketika pulsa clock ketiga tiba, flip flop C akan terisi oleh data flip

flop B dan flip flop B akan terisi oleh data flip flop A dan flip flop A akan terisi

keempat tiba, flip flop D akan terisi data pada flip flop C, flip flop C akan terisi

data flip flop B, flip flop B akan terisi data flip flop A dan flip flop A akan terisi

data masukan berikutnya dan keluarannya QD. Jadi jika data input 4 bit, maka

pulsa clock yang dibutuhkan adalah 4 kali. Sedangkan clear berfungsi untuk

mengenolkan (me-reset) data pada setiap flip flop. Clear akan bekerja jika

berlogika 1.

D

CLK Q

CL

D

CLK Q

CL

D

CLK Q

CL

D

CLK Q

CL

Data input

QA QB QC

Clok QD

Clear

Gambar 2.5 GambarRegister Geser SIPO 4-bit.

2.7. Pencacah

Modulo 14

Dalam elektronika digital, pencacah merupakan rangkaian yang sangat

penting yang berguna sebagai logika pengurut. Pencacah digital mempunyai

karakteristik yang penting yaitu:

1. Modulus pencacah atau jumlah hitungan maksimum.

2. Menghitung ke atas atau ke bawah.

3. Operasi asinkron atau sinkron.

Pencacah digital hanya akan mencacah atau menghitung dalam kode biner

suatu pencacah adalah jumlah hitungan yang dilaluinya.Tabel 2.6 dan gambar 2.6

di bawaah ini adalah contoh pencacah modulo-14

Tabel 2.6 Tabel Pencacah modulus-14.

Keluaran Cacahan

D C B A

0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 1 0 1 0 11 1 0 1 1 12 1 1 0 0 13 1 1 0 1

U3

AND2

U1 7476

J1 CLK1 PRN1 CLRN1 K1

Q1

QN1

J2 CLK2 PRN2 CLRN2 K2

Q2

QN2

U2 7476

J1 CLK1 PRN1 CLRN1 K1

Q1

QN1

J2 CLK2 PRN2 CLRN2 K2

Q2

QN2

U4

NAND3

U5

AND2

QB

QC QA

JK Preset Clock

QD

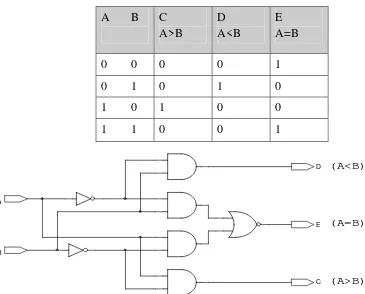

2.8. Pembanding /

Comparator

Pembanding atau komparator adalah rangkaian yang membandingkan

besaran masukan dengan suatu taraf referensi (atau dengan masukan lain) dan

menghasilkan suatu perubahan keadaan di keluaran bila salah satu masukan

melampaui yang lain. Jenis pembanding ada dua, yaitu pembanding analog dan

pembanding digital. Yang akan dibahas disini adalah pembanding digital.

Pembanding digital adalah rangkaian logika yang dipakai untuk

menentukan jika ada dua bilangan biner yang sama atau yang mempunyai besaran

yang lebih besar. Diasumsikan data yang dibandingkan adalah bit tunggal maka

dari Tabel 2.7 dibawah dapat dibandingkan masukan dari A dengan masukan

dari B.

Tabel 2.7 Tabel Kebenaran Pembanding

A B C

A>B

D A<B

E A=B

0 0 0 0 1

0 1 0 1 0

1 0 1 0 0

1 1 0 0 1

(A=B)

E

(A<B)

D

(A>B)

C B

A

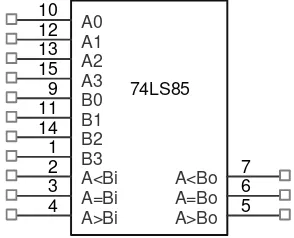

Contoh IC yang dapat membandingkan hingga 4 bit adalah 74LS85 yang ditunjukkan

pada Gambar 2.8. Pembanding yang besarnya 4-bit ini memberikan tiga keputusan

(Output) terhadap dua kata 4-bit (Input) yang dibandingkan yaitu A<B, A>B atau A=B.

Gambar rangkaian dari IC 74LS85 ini dapat dilihat pada Gambar di bawah ini.

74LS85 10

12 13 15 9 11 14 1 2 3 4

7 6 5

A0 A1 A2 A3 B0 B1 B2 B3 A<Bi A=Bi A>Bi

A<Bo A=Bo A>Bo

Gambar 2.8 Gambar IC 74LS85

2.9. Penyandi BCD ke Tujuh Segmen

Sebelum segmen dinyalakan, keluaran sistem digital harus diubah ke

dalam isyarat yang sesuai untuk menyalakan tampilan. Masukan dari sistem

digital biasanya dalam bentuk sandi biner (BCD) harus diubah menjadi isyarat

tujuh jalur untuk menyalakan masing-masing segmen. Perubahan ini dilakukan

oleh penyandi BCD ke tujuh segmen. Sebagai contoh, jika karakter 2 akan

ditampilkan maka jalur keluaran a, b, d, e, g akan di-SET berlogika satu untuk

menghidupkan LED yang sesuai dengan segmen a, b, d, e, g. Jalur yang lain tetap

berlogika nol. Tabel 2.8 di bawah menunjukkan jalur-jalur yang harus diaktifkan

Tabel 2.8 Tabel Jalur Tujuh Segmen Yang Aktif

Masukan BCD

Q3 Q2 Q1 Q0

Segmen yang diaktifkan Tampilan

0 0 0 0 a,b,c,d,e,f

0 0 0 1 b,c

0 0 1 0 a,b,d,e,g

0 0 1 1 a,b,c,d,g

0 1 0 0 b,c,f,g

0 1 0 1 a,c,d,f,g

0 1 1 0 a,c,d,e,f,g

0 1 1 1 a,b,c

1 0 0 0 a,b,c,d,e,f,g

2.10. Tujuh Segmen

Pada dasarnya penampil tujuh segmen terdiri dari tujuh buah LED (Light

Emmitting Diode). Menurut cara pemberian tegangan maka suatu tujuh segmen

terdiri dari dua macam, yaitu common anoda dan common katoda. Perbedaan

antara keduannya hanya terletak pada penyambungan antara LED yang terdapat

pada segmen yang satu dengan yang lain. Pada common anoda, anoda dari ketujuh

LED terhubung menjadi satu (Gambar a) pada gambar 2.9 sedangkan pada

common katoda, katoda dari ketujuh LED yang terhubung menjadi satu (Gambar

b) pada gambar 2.9.

Common a

b g

e c d f

Common a

b g

e c

d f

b) Common Kanoda a) Common Anoda

2.11. Saklar

Saklar merupakan perangkat yang digunakan untuk mendefinisikan suatu

masukan sebagai pemberian galat. Pada saklar apabila tombol dibiarkan off yaitu

saat posisi tombol saklar menuju ke bawah, maka nilainya adalah 0. Jika tombol

on yaitu saat tombol saklar menuju ke atas, maka terhubung ke tegangan masukan

yaitu 5 V dan bisa dikatakan bahwa saklar berlogika 1.

3 2 1

( b )

1 2 3

( a )

Gambar 2.10 GambarSaklar Toggle

Saklar pada Gambar 2.10 (a) menunjukkan bahwa saklar akan on jika kaki 3 dan

kaki 2 terhubung. Dan Gambar 2.10 (b) menunjukkan bahwa saklar akan on jika

kaki 2 dan kaki 1 terhubung. Untuk gambar foto asli saklarnya dapat dilihat dari

gambar 2.11 seperti gambar dibawah ini.

2.12. LED (

Light Emiting Diode)

LED (Light Emitting Dioda) merupakan dioda yang dapat mengeluarkan

emisi cahaya. LED merupakan produk temuan lain setelah dioda. Strukturnya juga

sama dengan dioda. Untuk mendapatkan emisi cahaya pada semikonduktor,

doping yang dipakai adalah galium, arsenic dan phosporus. Jenis doping yang

berbeda menghasilkan warna cahaya yang berbeda pula. Simbol LED ditunjukan

pada Gambar 2.11 di bawah ini.

Gambar 2.12 Simbol LED

LED sering dipakai sebagai indikator yang masing-masing warna bisa

memiliki arti yang berbeda. Menyala, padam dan berkedip juga bisa berarti lain.

LED dalam bentuk susunan (array) bisa menjadi display yang besar. Dikenal juga

LED dalam bentuk tujuh segmen atau ada juga yang 14 segmen. Biasanya

digunakan untuk menampilkan angka numerik dan alphabet. Kecerahan LED

tergantung dari arusnya. Dalam hal ini arus LED diberikan oleh :

s led cc

R V V

LED R

VCC

s Iled

Gambar 2.13 Rangkaian LED

2.13. Penambah Penuh (

Full Adder

)

Untuk menambahkan bilangan-bilangan biner dibutuhkan suatu rangkaian

yang dapat mengangani 3 angka sekaligus. Dengan menghubungkan dua buah

penambah paro serta sebuah gerbang OR, diperoleh penambah penuh (Full

Adder). Gambar dibawah menunjukkan rangkaian digital untuk penambah penuh

(FA). Kotak-kotak yang bertanda HA merupakan penambah paro.

HA HA

A

Bawaa n B

Jumla

h C

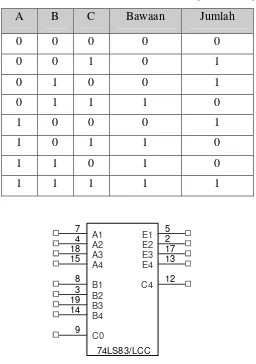

Tabel 2.9 Tabel Kebenaran Penambah Penuh (Full Adder).

A B C Bawaan Jumlah

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

74LS83/LCC 2 13 17 5

9

12

14 19 7 4 18 15 8 3

E2

E4 E3 E1

C0

C4

B4 B3 A1 A2 A3 A4

B1 B2

Pada Tugas Akhir ini penulis mencoba merancang Rangkaian enkoder,

Rangkaian sindrom dan Dekoder galat 1 bit pada Sandi Blok Linear (7,4).

Metode ini menggunakan bit - bit paritas yang dibangkitkan dari polinomial

pembangkit guna mendeteksi dan mengkoreksi galat pada bit data yang diterima.

Data masukan 4 bit dan data paritas 3 bit yang membentuk data sandi sebanyak 7

bit. Perancangan hardware Sandi Blok Linear ini terdiri dari 4 bagian inti

rangkaian yaitu Rangkaian Enkoder, Rangkaian Pembuat Galat, Rangkaian

Sindrom dan Rangkaian Dekoder seperti gambar blok diagram dibawah ini :

Rangk. Pembuat

galat

7 LED

7 bit Saklar

sbg input

7 bit serial

ENKODER

4 bit data

3 bit paritas Data input

Pembangkit paritas 7 LED

4 bit serial

Clock

ENKODER

Rangk. Sindrom

3 LED

Dekoder 1 bit galat

7 LED

3 bit

7 bit

DEKODER SIMULASI

GALAT

Gambar 3.1 Gambar Blok Diagram Enkoder Dan Dekoder Sandi Blok Linear ( 7,4 )

3.1 Saklar

Di dalam perancangan ini saklar digunakan untuk inputan baik data, Clock

maupun reset. Saklar yang digunakan memiliki 3 kaki, kaki yang tengah sebagai

output dan sedangkan kaki yang lain digunakan inputan ( + 5 V ) dan ground ( 0

V ).

2 1

3

Vcc

Gnd

Output

Gambar 3.2 Gambar Saklar Toggle Dengan 3 Kaki.

3.2. Rangkaian Enkoder

Di dalam perancangan rangkaian enkoder memerlukan beberapa

rangkaian-rangkaian dan komponen-komponen diantaranya adalah : Rangkaian pembentuk

paritas yang didapat dari matrik generator, Register, Komparator/ pembanding ,

D-latch/ IC Pengunci , Switch dan Suatu Penampil (led) atau seven segmen.

3.2.1 Perancangan Matrik Generator

Pada perancangan sandi blok ini dibahas bagaimana membuat matrik

generator dengan bentuk yang sesuai dengan kualitas penyandian yang

diinginkan. Dalam pembuatan matrik generator untuk mendapatkan sandi blok

dengan format sistematis diperlukan polinomial pembangkit, polinomial yang

dipilih adalah polinomial yang mempunyai pangkat tertinggi sama dengan

Untuk membuat matriks generator G dan matriks periksa paritas H yang

digunakan pada sandi blok linear dengan Hamming, dilakukan langkah sebagai

berikut :

1. Memilih polinomial primitif sesuai dengan panjang bit periksa

( P = bit paritas).

2. Membuat G dari polinomial primitif.

Dengan polinomial pembangkit, matriks generator dengan bentuk sistematis

dapat dibuat dengan mudah. Jika Xn-k+1 dibagi dengan polinomial pembangkit

g(X), dengan i = 0, 1, 2, … , 3 maka diperoleh :

X7-4+1 = ai (X) g(X) + Pi (X)

Dengan bi (X) adalah sisa dalam bentuk :

Pi (X) = Pi0 + Pi1X + … + Pi,n-k-1X3

Dari koefisien tersebut dibentuk matriks k x n sebagai berikut :

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅ ⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ = 1 0 0 0 1 0 0 0 1 3 , 3 31 30 3 , 1 11 10 3 , 0 01 00 P P P P P P P P P G

matriks ini merupakan matriks generator dalam bentuk sistematis.

Sebagai perhitungan dalam perancangan sandi blok linear (7,4) dengan m

= 3 (sama dengan panjang bit periksa) yang diperoleh dari n-k, maka polinomial

Maka polinomial pembangkit yang digunakan adalah g(X) = 1 + X + X3. Jika X3

X4, X5, dan X6dibagi dengan g(X), akan diperoleh :

X3 = 1 g(X) + (1 +X )

X4 = X g(X) + ( X + X2 )

X5 = X2 + 1 g(X) + ( 1+X + X2 )

X6 = X3 + X g(X) + ( 1 + X2 )

Jika P adalah sisa ditambah dengan variabel yang dibagi, maka :

P0 (X) = 1 + X

P1 (X) = X + X2

P2 (X) = 1+X +X2

P3 (X) = 1 + X2

Koefisien polinomial P di atas diambil sebagai baris-baris dari matrik G,

sehingga :

⎥ ⎥ ⎥ ⎥

⎦ ⎤

⎢ ⎢ ⎢ ⎢

⎣ ⎡

=

1 0 0 0 101

0 1 0 0 1 1 1

0100 1 1 0

0 0 0 1 0 1 1

G

Untuk mencari nilai vektor sandi ( V ) = u . G ...(3.1 )

yang nantinya akan digunakan dalam masukan data dapat dinyatakan sebagai

V = ( U0,U1, U2, U3) . sehingga di dapat rumus sbb: ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ 1 0 0 0 101 0 1 0 0 1 1 1 0100 1 1 0 0 0 0 1 0 1 1

V6 = U3

V5 = U2

V4 = U1

V3 = U0

V2 = U1 + U2 + U3

V1 = U0 + U1 + U2

V0 = U0 + U2 + U3

Di bawah ini adalah dua contoh penyelesaiannya untuk mendapatkan

vektor pesannya, misalkan vektor pesannya U adalah 0011 dan 0111.

Untuk soal yang pertama :

U = 0011

V = U . G

V = ( 0 0 1 1 ) .

⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ 1 0 0 0 101 0 1 0 0 1 1 1 0100 1 1 0 0 0 0 1 0 1 1

V = 010 0011

Dari contoh diatas didapatkan vektor sandinya adalah 010 0011 dengan

Untuk soal yang kedua :

U = 0111

V = U. G

V = ( 0 1 1 1 ) .

⎥ ⎥ ⎥ ⎥

⎦ ⎤

⎢ ⎢ ⎢ ⎢

⎣ ⎡

1 0 0 0 101

0 1 0 0 1 1 1

0100 1 1 0

0 0 0 1 0 1 1

V = 001 0111

Dari contoh di atas didapatkan vektor sandinya adalah 001 0111 sehingga

didapatkan vektor paritasnya adalah 001. Keluaran enkoder selengkapnya

ada pada tabel 3.1 seperti tabel di bawah ini.

Tabel 3.1 Tabel Keluaran Enkoder

No Pesan Vektor sandi

1 0000 000 0000

2 0001 101 0001

3 0010 111 0010

4 0011 010 0011

5 0100 011 0100

6 0101 110 0101

7 0110 100 0110

8 0111 001 0111

9 1000 110 1000

10 1001 011 1001

11 1010 001 1010

12 1011 100 1011

13 1100 101 1100

14 1101 000 1101

15 1110 010 1110

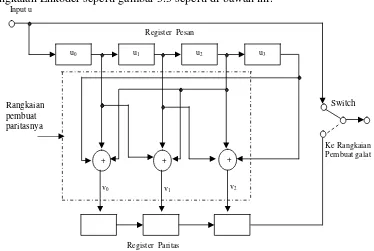

Implementasi dari persamaan 3.1 dapat dijadikan suatu perancangan

rangkaian Enkoder seperti gambar 3.3 seperti di bawah ini.

Input u

Rangkaian pembuat paritasnya

u3

u2

u1

u0

+ + +

Switch

Ke Rangkaian Pembuat galat

v0 v1 v2

Register Pesan

Register Paritas

Gambar 3.3 Gambar Blok Diagram Enkoder Blok Linear ( 7,4 )

Untuk rangkaian ini membutuhkan gerbang XOR pada IC 74LS86 dengan jumlah

input 2 dan output 1 untuk penjumlahan yang akan menghasilkan vektor

paritasnya. Untuk registernya mengunakan D-FF pada IC 74LS74, pada register

pertama D-FF di bentuk menjadi register SIPO dan pada register yang kedua di

bentuk menjadi register PISO. Untuk cara kerja dari enkoder ini adalah

memasukkan 4 data inputan melalui saklar data yang dimasukkan melalui register

yang pertama dan juga dikirim pada switch 1. Paritas didapatkan dari

penjumlahan pada gerbang X-OR. Untuk kombinasinya di dapatkan dari

perhitungan pada persamaan 3.1. setelah clock ke-4 vektor paritasnya dan vektor

datanya atau vektor sandinya sudah dapat ditampilkan melalui led sebagai

keluaran. Pengiriman vektor paritas dimanipulasi menjadi pengiriman yang serial

yang didahulukan. Untuk memanipulasi pengiriman ini diperlukan switch 2 dan

switch 3. Untuk perancangan Enkoder dapat dilihat pada gambar 3.4 seperti di

bawah ini :

Q D CP

CD

Q D CP

CD

Q D CP

CD

Q D CP

CD

2 1 3

2 1 3

2 1 3

Q D CP

CD

Q D CP

CD

Q D CP

CD

KOMPARATOR 2

KOMPARATOR 3

KOMPARATOR 1 DATA

CLOCK

CLEAR

Output (R.galat)

u0

u1 u2 u3

P0 P1 P2

Gambar 3.4 Gambar Perancangan Enkoder Sandi Blok Linear (7,4)

3.2.2. Register

Register digunakan sebagai penyimpanan sementara. Di dalam perancangan

enkoder membutuhkan 4 bit register untuk vektor pesan dan 3 bit untuk vektor

paritas. Di dalam perancangan pada vektor pesan register yang digunakan adalah

SIPO ( serial input pararel output ) mengunakan IC 74LS164 Pada Gambar 3.5

atau mengunakan D-FF pada IC 74lS74 seperti gambar 3.6.

3

4

6 2

8 9 D

CLK

PRE CLR

Q Q

18

16

14 19

13 12 D

CLK

PRE CLR

Q Q

Gambar 3.6 Gambar D-FF Pada IC 74LS74

3.2.3. Switch

Di dalam perancangan terdapat 3 switch yaitu switch1 untuk pemilihan data

atau paritas yang didahulukan didalam pengiriman ke rangkaian pembuat galat

dan 2 switch yang lain untuk pemilihan vektor paritas. Pembuatan swicth

dirancang dengan mengunakan metode SOP dengan disederhanakan mengunakan

peta karnaugh.

3.2.3.1. Switch 1 ( Pemilih Untuk Pengiriman )

Switch 1 digunakan untuk pemilihan data input atau data paritas yang

didahulukan didalam pengiriman ke rangkaian pembuat galat.

Tabel 3.2 Tabel Kebenaran Switch 1

Data ( D ) paritas ( P ) Kendali ( K ) Output

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 1

1 1 0 1

Tabel 3.3 Tabel Peta Karnaugh Untuk Switch1

K K

P

D 0 0

P

D 0 1

1 1

DP

P

D 1 0

Dari peta karnaugh diatas di dapat DK + PK yang dapat diimplementasikan

di dalam suatu rangkaian digital seperti gambar 3.7 seperti gambar dibawah ini :

P

D

Output ( Input Rangkain Pembuat Galat ) K

Gambar 3.7 Gambar Rangkaian Switch 1

3.2.3.2. Switch 2

Switch 2 digunakan untuk pemilihan data antara paritas pada P0 dan P1. pada

switch ini dirancang apabila komparator keadaan 1 maka yang didahulukan adalah

P1 untuk dikirimkan pada register berikutnya.

Tabel 3.4 Tabel Kebenaran Switch 2

P0 P1 Kendali ( K ) Output

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 0

1 1 0 1

Tabel 3.5 Tabel Kebenaran Switch 2

K K

0 0

1 0P

P

1 0P

P 1 0

1 0P

P 1 1

1 0P

P 0 1

Dari peta karnaugh di atas dapat diimplementasikan untuk pembuatan

gambar rangkaian seperti gambar 3.8:

Sw2 =P0K + P1K

P1

P0

Sw2 K

Gambar 3.8 Gambar Rangkaian Switch 2

3.2.3.3. Switch 3

Switch 3 digunakan untuk pemilihan data antara paritas pada SW2 dan P2.

pada switch ini dirancang apabila komparator keadaan 1 maka yang didahulukan

adalah U2 untuk dikirimkan pada Switch 1.

Tabel 3.6 Tabel Kebenaran Switch 3

SW2 U2 Kendali ( K ) Output

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 0

1 1 0 1

Tabel 3.7 Tabel Peta Karnaugh Untuk Switch 3

K K

2 2P

SW 0 0

2 2P

SW 1 0

2 2P

SW 1 1

2 2P

SW 0 1

Dari tabel peta karnaugh di atas dapat diimplementasikan untuk pembuatan

gambar rangkaian seperti gambar 3.9.

SW3 = SW2K + P2K

P2

Sw2

Sw3

K

Gambar 3.9 Gambar Rangkaian Switch 3

3.3. Rangkaian Pembuat Galat

Pengiriman data dari penyandi dilakukan secara serial, oleh karena itu

diperlukan rangkaian pembuat galat. Rangkaian ini berfungsi untuk merubah data

yang dikirim dari penyandi, pada rangkaian ini data yang diterima ditampilkan

dengan menggunakan LED, dan galat diaktifkan dengan menghubungkannya

dengan keluaran Q, Setelah data diproses pada rangkaian pembuat galat, maka

data yang ke rangkaian deteksi kemudian ditampilkan melalui LED.

Galat yang terjadi akan dibangkitkan melalui saklar. Ada 7 saklar,

ditampilkan pada LED yang sama ke rangkaian deteksi. Rangakaian pembuat

galat dibuat setelah sandi keluar dari penyandi, hanya saja salah satu dari keluaran

flip flop yang digunakan adalah keluaran Q yang dihubungkan oleh switch (Sw).

Switch ini harus dikembalikan lagi pada keluaran Q setelah mendapatkan clock.

Kondisi ini untuk menjaga agar bit yang berikutnya tidak terkena galat. Keluaran

Q ini yang kemudian digunakan sebagai galat. Gambar rangkain pembuat galat

dapat dilihat pada gambar 3.10. Untuk rangkaian pembuat atau penyimulasi galat

di tampilkan pada clock ke-14 dengan tampilan keluarannya adalah led.

D CP Q QCD D CP Q QCD D CP Q QCD D CP Q QCD D CP Q QCD D CP Q QCD D CP Q QCD 2 1 3 2 1 3 2 1 3 2 1 3 2 1 3 2 1 3 2 1 3 Output(ke R.Sindrom) Input (Dari Enkoder)

Clear

Clock

Gambar 3.10 Gambar Perancangan Rangkaian Pembuat Galat

3.4. Rangkaian Sindrom

Rangkaian sindrom didapat dari perkalian dari matrik HT dan Rangkaian

error yaitu :

S = r . HT ...(3.2)

dengan :

S = Sindrom

r = Bit- bit error

HT = matrik H transpos

Matrik H di dapat dari :

Dengan :

In-k = Matrik identitas

P = Transpos bit paritas

H = maka :

⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎣ ⎡ 0111 001 1110 010 1011 100

HT =

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ 101 111 011 110 001 010 100

S = ( r0,r1,r2,r3,r4,r5,r6 ) .

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ 101 111 011 110 001 010 100

S0 = r0 + r3 + r5 + r6

S1 = r1 + r3 + r4 + r5

S2 = r2+ r4 + r5 + r6

Sehingga dari pola S0, S1 dan S2 dapat diimplementasikan dengan sebuah

r

+ + +

r0 r1 r2 r3 r4 r5 r6

s2

s1

s0

Gambar 3.11 Gambar Blok Diagram Rangkaian Sindrom Pada Blok Linear (7,4 )

Dari persamaan 3.2 bisa kita buktikan dengan soal-soal dibawah ini. Untuk

semua soal diketahui V = 001 0111, kita buat untuk bit-bit errornya ( r ) menjadi

101 0111, 011 0111, 010 1111 dan 101 0110. Sehingga penyelesaiannya sebagai

berikut :

Untuk r = 101 0111

S = r . HT

Maka S = ( 1 0 1 0 1 1 1 ) .

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥

⎦ ⎤

⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢

⎣ ⎡

101 111 011 110 001 010 100

S = 100

maka didapatkan sindromnya adalah 100, bila kita lihat dari tabel pola

sindromnya sehingga dapat dideteksi ada suatu kesalahan pada bit pertama.

S = r . HT

Maka S = ( 0 1 1 0 1 1 1 ) .

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ 101 111 011 110 001 010 100

S = 010

maka didapatkan sindromnya adalah 010, bila kita lihat dari tabel pola

sindromnya sehingga dapat dideteksi ada suatu kesalahan pada bit ke-dua.

Untuk soal pertama dan kedua bit-bit errornya hanya mempunyai satu bit

error. Untuk soal yang ke-tiga dan ke-empat memiliki bit error lebih dari satu bit

errornya.

Untuk soal ke-tiga dengan :

r = 010 0111

S = r . HT

Maka S = ( 0 1 0 0 1 1 1 ) .

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ 101 111 011 110 001 010 100

Sehingga didapatkan sindromnya adalah 011, bila kita lihat dari tabel pola

sindromnya maka dideteksi ada suatu kesalahan pada bit ke-lima. Apabila kita

bandingkan antara V = 001 0111 dengan r = 010 0111, bit error tidak terletak pada

bit ke-lima melainkan pada bit ke-dua dan ke-tiga.

Soal ke-empat dengan :

r = 101 0110

S = r . HT

Maka S = ( 1 0 1 0 1 1 0 ) .

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥

⎦ ⎤

⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢

⎣ ⎡

101 111 011 110 001 010 100

S = 001

Sehingga didapatkan sindromnya adalah 001, bila kita lihat dari tabel pola

sindrom maka dapat di deteksi ada suatu kesalahan pada bit ketiga. Apabila kita

bandingkan dengan vektor sandinya V = 001 0111 dengan r = 101 0110, bit yang

error tidak terletak di bit yang tiga melainkan terletak pada bit pertama dan

ke-tujuh.

Untuk rangkain sindrom ditampilkan pada clock ke-14 dengan tampilan

Tabel 3.8 Tabel Pola Sindrom

Error pada bit Pola Error Sindrom

1 100 0000 100

2 010 0000 010

3 001 0000 001

4 000 1000 110

5 000 0100 011

6 000 0010 111

7 000 0001 101

Untuk perancangan pada rangkaian sindrom dapat dilihat pada gambar 3.12

seperti pada gambar di bawah ini.

D CP

Q Q

CD

D CP

Q Q

CD

D CP

Q Q

CD

D CP

Q Q

CD

D CP

Q Q

CD

D CP

Q Q

CD

D CP

Q Q

CD

S2 S0

S1 Clock

Clear Input(Dari pembuat galat)

r0 r1 r2 r3 r4 r5 r6

Gambar 3.12 Gambar Perancangan Rangkaian Sindrom Pada Blok Linear (7,4)

3.5. Rangkaian Koreksi

Rangkaian Koreksi adalah suatu rangkaian yang digunakan untuk

mengkoreksi suatu kesalahan yang didapat dari suatu rangkaian sindrom.

Rangkaian koreksi didapat dari :

dimana :

C = Rangkaian koreksi.

r = Rangkaian galat.

e = Pola Error.

Dengan demikian perhitungannya maka masing-masing C adalah :

C0 = r0 + e0

=r0 +(S0 •S1•S2)

C1 = r1 + e1

=r1+(S0 •S1•S2) C2 = r2 + e2

=r2 +(S0•S1•S2)

C3 = r3 + e3

=r3 +(S0 •S1•S2)

C4 = r4 + e4

=r4 +(S0•S1•S2)

C5 = r5 + e5

=r5 +(S0•S1•S2)

C6 = r6 + e6

=r6 +(S0•S1•S2)

Implementasi persamaan 3.4 adalah gambar perancangan rangkaian koreksi

S0 S1 S2

r0 r1 r2 r3 r4 r5 r6

C0 C1 C2 C3 C4 C5 C6

Gambar 3.13 Gambar Rangkaian Koreksi Pada Sandi Blok Linear (7,4)

Untuk contoh penyelesaian pada rangkaian dekoder atau rangkaian koreksi

ini melanjutkan untuk contoh soal dari rangkain sindrom. Bila rangkaian koreksi

atau dekoder C = r + e maka :

Soal pertama jika:

V = 001 0111

r = 101 0111

S = 100 jika lihat tabel pola sindrom maka nilai e = 100 0000

Maka C = r + e

C = 101 0111 + 100 000

C = 001 0111

Untuk soal yang ke-dua jika :

V = 001 0111

r = 011 0111

C = r + e

C = 011 0111 + 010 0000

C = 001 0111

Untuk soal pertama dan kedua bit-bit error dapat dikoreksi karena dengan

dibuktikan nilai V dan nilai C adalah sama yaitu 001 0111 sehingga vektor sandi

bila terdapat error satu bit maka vektor sandi tersebut dapat dikoreksi.

Untuk soal ke-tiga jika :

V = 001 0111

r = 010 0111

S = 011 jika lihat tabel pola sindrom maka nilai e = 000 0100

C = r + e

C = 010 0111 + 000 0100

C = 010 0011

Untuk soal ke-empat jika :

V = 001 0111

r = 101 0110

S = 001 jika lihat tabel pola sindrom nilai e = 001 0000

C = r + e

C = 101 0110 + 001 0000

C = 100 0110

Bila kita membandingkan antara nilai V dan nilai C untuk soal ke-tiga dan

ke-empat tidak sama. Untuk V soal ketiga = 001 0111 sedangkan untuk nilai

nilai C = 100 0110. Bila kita lihat dari perbandingan itu dapat kita ambil

kesimpulan bahwa untuk vektor sandi yang mendapat error lebih dari satu

bit dapat dideteksi galatnya tetapi tidak dapat untuk dikoreksi.

3.6.

Counter/ Pencacah Modulo 14

Dalam perancangan ini counter yang dibutuhkan adalah modulo 14.

Penentuan modulo ini berdasarkan atas jumlah clock yang dibutuhkan dalam

proses penyandian. Counter dibuat dengan J K flip flop pada IC 74LS76 yang

menggunakan metode umpan balik menggunakan gerbang NAND. Cacahan

normal setelah 1101 adalah 1110. Agar 1110 terlompati menjadi 0000 maka

keluaran dari flip flop D, flip flop C dan flip flop B diumpan balik menggunakan

gerbang NAND. Keluaran dari gerbang NAND akan terhubung dengan clear pada

masing- masing flip flop. Dengan demikian setelah clock ke – 15 tiba semua flip

flop akan direset. Untuk menampilkan keluaran dari counter tersebut

menggunakan seven segment. Karena keluaran dari counter merupakan bilangan

biner maka diubah terlebih dahulu kedalam bentuk BCD, dan sebagai dekoder

menggunakan IC 74LS47. untuk gambar perancangan dapat dilihat pada Gambar

U3 AND2 U1 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U2 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U4 NAND3 U5 AND2 QB QC QA JK Preset Clock QD

Gambar 3.14 Gambar Perancangan Counter Atau Pencacah Sinkron Modulo 14

0ns 1000ns 2000ns 3000ns

schematic Context clock Signal 'U' Value schematic Context jk Signal 'U' Value schematic Context preset Signal 'U' Value schematic Context Outputre Signal X Value

0 1 2 3 4 5 6 7 8 9 10 11 12 13 0 1

Gambar 3.15 Gambar Keluaran Simulasi Pencacah Sinkron Modulo 14

3.7.

Pembanding / Comparator

Perancangan komparator atau pembanding digunakan untuk

membandingkan dua inputan. Komparator di dalam perancanangan enkoder dan

dekoder sandi blok linear (7,4) ini dibagi menjadi 4 pembanding / komparator

3.7.1. Pembanding /

(Comparat

or) 1

Pembanding 1 digunakan untuk sebagai masukan pada IC pengunci pada

enkoder. komparator ini di set dengan A>B, dimana A diset 3 sehingga pada clok

ke-1 sampai ke-4 keluaran pada komparator akan bernilai 1 karena pencacah

dimulai dari nol. sebelum clock ke-5 akan bernilai nol sehingga pada IC pengunci

akan mengunci data terakhir pada clok ke-4. gambar komparator 1 seperti gambar

3.16 dibawah ini.

0ns 500ns 1000ns 1500ns 2000ns 2500ns 3000

schematic Context clock Signal '1' Value schematic Context jk Signal '1' Value schematic Context preset Signal '1' Value schematic Context vcc Signal '1' Value schematic Context gnd Signal '0' Value schematic Context Outputre Signal 0 Value

0 1 2 3 4 5 6 7 8 9 10 11 12 13 0

schematic Context outcomp Signal '1' Value QA QC Clock QB JK Preset QD OutComp Vcc Gnd U6 NAND3 U1 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U4 AND2 U5 AND2 U2 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U3 7485 A0 A1 A2 A3 B0 B1 B2 B3 ALBI AEBI AGBI ALBO AEBO AGBO

Gambar 3.16 Gambar Perancangan Simulasi Pembanding / Komparator 1

3.7.2. Pembanding

(Comparator)

2

Pembanding 2 digunakan untuk sebagai selektor pada switch 1. komparator

ini di set dengan A>B, dimana A diset 3 sehingga pada clok ke-1 sampai ke-4

keluaran pada komparator akan bernilai 1 karena pencacah dimulai dari nol.

Karena pada switch 1 digunakan untuk memilih data pesan yang didahulukan

daripada data paritas. Bila komparator bernilai 1 maka data pesan yang dikirim ke

rangkaian pembuat galat dan sebaliknya bila komparator bernilai 0 maka data

paritas yang akan dikirimkan ke rangkaian pembuat galat. Sehingga data pesan

akan dikirimkan pada clok ke-1 sampai clok ke-4 ke rangkaian pembuat galat dan

clok ke-5 sampai clok ke-7 data paritas yang akan dikirimkan. Gambar

komparator 2 dapat dilihat pada gambar 3.18 dibawah ini.

QA QC Clock QB JK Preset QD OutComp Vcc Gnd U6 NAND3 U1 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U4 AND2 U5 AND2 U2 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U3 7485 A0 A1 A2 A3 B0 B1 B2 B3 ALBI AEBI AGBI ALBO AEBO AGBO

0ns 500ns 1000ns 1500ns 2000ns 2500ns 3000 schematic Context clock Signal '1' Value schematic Context jk Signal '1' Value schematic Context preset Signal '1' Value schematic Context vcc Signal '1' Value schematic Context gnd Signal '0' Value schematic Context Outputre Signal 0 Value

0 1 2 3 4 5 6 7 8 9 10 11 12 13 0

schematic Context outcomp Signal '1' Value

Gambar 3.19 Gambar Keluaran Simulasi Pembanding / Komparator 2

3.7.3 Pembanding (Comparator) 3

Pembanding 3 digunakan untuk sebagai selektor pada switch 2. komparator

ini di set dengan A=B, dimana A diset 4 sehingga pada clok ke-5 keluaran pada

komparator akan bernilai 1 karena pencacah dimulai dari nol. Prinsipnya saat

clock ke-5 Komparator akan memilih data paritas ke-3 atau P2 yang akan dikirim

ke pembuat galat. Gambar perancangan komparator 3 dapat dilihat pada gambar

3.20 seperti gambar dibawah ini.

U3 7485 A0 A1 A2 A3 B0 B1 B2 B3 ALBI AEBI AGBI ALBO AEBO AGBO U2 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U1 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U4 AND2 U5 AND2 U6 NAND3 Vcc Preset QA OutCOmp QD JK Clock QB QC Gnd

0ns 1000ns 2000ns schematic Context clock Signal 'U' Value schematic Context gnd Signal 'U' Value schematic Context jk Signal 'U' Value schematic Context preset Signal 'U' Value schematic Context vcc Signal 'U' Value schematic Context Outputre Signal X Value

0 1 2 3 4 5 6 7 8 9 10 11 12 13

schematic Context outcomp Signal 'U' Value

Gambar 3.21 Gambar Keluaran Simulasi Pembanding / Komparator 3

3.7.4 Pembanding (Comparator) 4

Pembanding 4 digunakan untuk sebagai selektor pada switch 3. komparator

ini di set dengan A=B, dimana A diset 5 sehingga pada clok ke-6 keluaran pada

komparator akan bernilai 1 karena pencacah dimulai dari nol. Prinsipnya saat

clock ke-6 Komparator akan memilih data paritas ke-2 atau P1 yang akan dikirim

ke pembuat galat karena saat itu komparator 4 bernilai 1 atau komparator 3

bernilai 0 dan pada clock ke-7 akan memilih data paritas ke-1 atau P0 karena

komparator 3 dan komparator 4 bernilai nol pada saat clock ke-7. Gambar

perancangan komparator 4 dapat dilihat pada gambar 3.23 .

0ns 500ns 1000ns 1500ns 2000ns 2500ns 3000 schematic Context clock Signal '1' Value schematic Context jk Signal '1' Value schematic Context preset Signal '1' Value schematic Context vcc Signal '1' Value schematic Context gnd Signal '0' Value schematic Context Outputre Signal 3 Value

0 1 2 3 4 5 6 7 8 9 10 11 12 13 0 schematic Context outcomp Signal '0' Value

QA QC Clock QB JK Preset QD OutComp Vcc Gnd U6 NAND3 U1 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U4 AND2 U5 AND2 U2 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U3 7485 A0 A1 A2 A3 B0 B1 B2 B3 ALBI AEBI AGBI ALBO AEBO AGBO

Gambar 3.23 Gambar Perancangan Simulasi Pembanding / Komparator 3

3.10.

Penjumlah Penuh / Full Adder

Di dalam perancangan ini membutuhkan IC 74LS83 Atau IC 74LS283. Data

masukan pada input Full adder adalah A1A2A3A4 yang mendapat data masukan

dari Counter QdQcDbQa yang berbentuk bilangan biner. Full adder ini digunakan

agar bilangan ini bisa di baca kedalam bilangan BCD. Untuk angka 0-9 bilangan

biner dan bilangan BCD mengalami persamaan tetapi pada angka 10 bilangan

biner berbeda dengan bilangan biner karena didalam bilangan BCD mengunakan

nibel misalnya biner 10 adalah 1010 sedangkan bilangan BCD adalah untuk nibel

puluhan adalah 0001 sedangkan untuk nibel satuan adalah 0000 bila kita

bandingkan bilangan biner perlu ditambahkan 6 atau kalau dalam bentuk biner

dirancang sedemikian agar memperoleh nilai yang sama dan dari penjumlahan

penuh ini apabila ada carry akan dimasukkan pada dekoder puluhan sedangkan

hasilnya dimasukkan ke nilai satuan pada dekoder. Untuk penambahan angka 6

dapat dilihat pada gambar 3.24 seperti gambar dibawah ini.

U3 7 4LS8 3 10 8 3 1 11 7 4 16 13 9 6 2 15 14 5 12 A1 A2 A3 A4 B1 B2 B3 B4 C0 S1 S2 S3 S4 C4 VC C GN D 1 2 3 14

7 5 4

6 14 7 1 2 3 14 7 1 2 3 4 1 2 GND Vcc Dekoder Dekoder 7-Segmen 7-Segmen Puluhan Satuan a b c d e f g Common a b c d e f g Common A B C D

Gambar 3.24 Gambar Perancangan Penjumlah Penuh / Full Adder

3.10.

IC Pengunci.

Perancangan IC pengunci membutuhkan IC 74LS75. kerja dari IC pengunci

ini adalah apabila enable mendapat input nol dari komparator maka data terakhir

yang ditampilkan akan terkunci sampai direset kembali. Untuk vektor sandi yaitu

antara vektor data dan vektor paritas membutuhkan dua IC pengunci karena setiap

IC 74LS75 mempunyai 4 data input dan 4 data output. Untuk Rangkaian pembuat

galat membutuhkan dua IC 74LS75. Pada rangkaian sindrom hanya membutukan

koreksi ( Dekoder ) membutuhkan 2 IC 74LS75 karena data yang ditampilkan

sebanyak 7 data. Untuk gambar perancangan D-latc atau IC pengunci dapat dilihat

seperti gambar 3.25 dibawah ini.

330

330 330 330 2

3

6

7

13 4

16 1 15 14 10 11 9 8

D1 D2 D3 D4 C12 C34

Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4

Output

Komparator

Yg Disimpan Data

Gambar 3.25 Gambar Perancangan IC Pengunci Atau D-latch

3.10.

Tampilan Keluaran Enkoder, Simulasi Galat Dan Dekoder.

Pada tampilan keluaran alat ini semua data keluaran ditampilkan dengan Led

dan tujuh segmen ( seven Segment) sedangkan inputan data, Clock dan reset

melalaui saklar 3 kaki. Gambar tampilan keluaran u