Memori Hirarki

Pertanyaan

¾

Tahukah anda Tipe-tipe Prosesor dari awal

sampai sekarang ?

sampai sekarang ?

¾

Tahukah anda Kategori Sistem Hardware dari

masing-masing tipe ?

Prosesor Lebar Data Kategori Lebar Registermasing-masing tipe ?

Prosesor Lebar Data Kategori Lebar Register8088 8-bit 8-bit 16-bit

8086 16-bit

Pentium Pro/Celeron/II/III 64-bit 32-bit AMD Duron/Athlon/Athlon XP 64-bit 32-bit

Pentium 4 64-bit 32-bit

Itanium 64-bit 64-bit

Problem Identification Possible Cause Resolution

System is dead, no cursor, no beeps, no fan. Power cord failure. Plug in or replace power cord. Power cords can fail even though they look fine

Troubleshooting CPU

?

they look fine.

Power supply failure. Replace the power supply. Use a known-good spare for testing. Motherboard failure. Replace motherboard. Use a known-good spare for testing. Memory failure. Remove all memory except 1 bank and retest. If the system still

won't boot replace bank 1.

System is dead, no beeps, or locks up before POST begins. All components either incorrectly installed. Check all peripherals, especially memory and graphics adapter. Reseat all boards and socketed components.

System beeps on startup, fan is running, no cursor on screen. Improperly seated or failing graphics adapter. Reseat or replace graphics adapter. Use known-good spare for testing.

System powers up, fan is running, no beep or cursor. Processor not properly installed. Reseat or remove/reinstall processor and heatsink.

Locks up during or shortly after POST. Poor heat dissipation. Check CPU heatsink/fan; replace if necessary, use one with higher capacity.

Improper voltage settings. Set motherboard for proper core processor voltage. Wrong motherboard bus speed. Set motherboard for proper speed.

Wrong CPU clock multiplier. Jumper motherboard for proper clock multiplier. Improper CPU identification during POST. Old BIOS. Update BIOS from manufacturer.

Board not configured properly. Check manual and jumper board accordingly to proper bus and multiplier settings.

System won't start after new processor is installed. Processor not properly installed. Reseat or remove/reinstall processor and heatsink.

BIOS doesn't support new processor. Update BIOS from system or motherboard manunew facturer. Motherboard can't use new processor. Verify motherboard support.

Operating system will not boot. Poor heat dissipation. Check CPU fan; replace if necessary; it might need a higher-capacity heatsink or heatsink/fan on the North Bridge chip. Improper voltage settings. Wrong motherboard bus speed. Jumper motherboard for proper core voltage. Jumper motherboard

for proper speed.

Pendahuluan

¾

Kapan materi COA ‘terasa’ bermanfaat ?

Sebagai dasar pengetahuan, Bila anda bekerja di suatu

h d d di i t t k

perusahaan dan anda diminta untuk :

Memilih spesifikasi komputer yang akan digunakan dengan

spesifikasi sesuai kebutuhan dan harga kompetitif

M b k di di b dd d

Membuat program yang akan ditanam di embedded system

Melakukan debug terhadap program yang telah terinstall pada

embedded system (sensor mesin, sistem pengapian elektronik, dll)

dll)

Pendahuluan

Processor Devices

Control

Memory Input

Processor-Memory Performance Gap

e • Kapasitas chip meningkat “Moore’s Law”

2x 1tiap 18-24 bln

• Cost per bit turun secara

10

Cost per bit turun secara exponensial

Tujuan Hirarki Memori

¾

Fakta :

¾

Fakta :

“Large memories are slow and fast memories

are small”

are small

¾

Bagaimana membuat memori yang dapat

menggambarkan bahwa Memori memiliki

Kapasitas yang besar, murah dan cepat ?

Berhirarki

Hirarki Memori

z Masing-masing memori pada level hirarki memiliki teknologi yang beda

z Kecepatan ukuran dan bahkan cost nya

On-Chip Components

z Kecepatan, ukuran dan bahkan cost nya

Æ Locality principle

Size (bytes): 100’s K’s 10K’s M’s G’s to T’s

Size (bytes): 100 s K s 10K s M s G s to T s

Hirarki

4-8 bytes (word)

Memori

1 to 4 blocks

8-32 bytes (block)

Hirarki Memori

Æ Biaya per bit

ki h Registers

makin murah

Æ Kapasitas makin

besar

Disk cache (pure S/W) makin lama

ÆFrekuensi

diakses oleh

(p )

Disk (Harddisk)

Optical (CD DVD) d akses oleh

prosesor makin jarang

Optical (CD, DVD)

Karakteristik Memori

(1)

Memory

diklasifikasikan berdasarkan:

(1)

Lokasi

(2)

Kapasitas

(3)

Satuan transfer

(4)

C

k e

(4)

Cara akses

(5)

Performansi

(6)

Jenis fisik

(6)

Jenis fisik

(7)

Karakteristik fisik

(8)

Organisasi memori

Karakteristik Memori

(2)

(1) Lokasi:

Internal

: dapat diakses oleh prosesor tanpa melalui I/O?

Register

Cache memory

Main memory (RAM)

l

k k h l l i /O

External

: untuk mengaksesnya harus melalui I/O Harddisk, Diskette, Magnetic Tape

Flashdisk

CDROM dll

CDROM, dll

(2) Kapasitas:

Adalah kemampuan menampung data dalam

p

p

g

satuan tertentu (byte atau word)

Satu byte = 8 bit

Satu word = 8, 16, atau 32 bit (tergantung pada pembuat

Karakteristik Memori

(3)

(3) Satuan transfer:

Memori internal:

Adalah banyaknya bit yang dapat dibaca/ditulis dari/ke memori dalam setiap detik

Adalah setara dengan banyaknya jalur data yang terhubung ke

memori (lebar bus) memori (lebar bus)

Biasanya sebanyak satu word, tetapi dapat lebih banyak lagi

(misal: 32, 64, atau 128 bit)

Memori eksternal

Memori eksternal

Digunakan satuan

block

yang ukurannya lebih dari satu word Satuan alamat: (

minimum addressable unit

) Satuan alamat: (

minimum addressable unit

) Adalah ukuran memori terkecil yang dapat diberi alamat tersendiri

Besarnya tergantung pembuat prosesor (Intel: 1 byte atau 8 bit),Besarnya tergantung pembuat prosesor (Intel: 1 byte atau 8 bit),

Karakteristik Memori

(4)

(4) Cara akses:

Sequential access

Akses ke memori dilakukan secara berurutan (searching

Akses ke memori dilakukan secara berurutan (searching,

passing, rejecting)

Digunakan mekanisme shared read/write

Waktu akses sangat variabel, bergantung pada lokasi data yang g , g g p y g akan dituju dan data sebelumnya

Contoh: Magnetic tape

Direct access

Akses ke memori langsung menuju ke lokasi terdekat, diteruskan

dengan sedikit pencarian dan perhitungan

Setiap blok/record mempunyai alamat unik berdasarkan lokasi

fisik fisik

Digunakan mekanisme shared read/write

Waktu aksesnya variabel (berbeda-beda) dan bergantung pada

Karakteristik Memori

(5)

Random access

Akses ke memori dilakukan secararandom

langsungk l t dit j

ke alamat yang dituju

Setiap alamat memori mempunyai alamat unik

Waktu aksesnya konstan dan tidak bergantung padaWaktu aksesnya konstan dan tidak bergantung pada urutan akses sebelumnyaContoh:

main memory

, beberapa sistem cache

A

i ti

Associative

Pencarian data di memori dilakukan denganmembandingkan seluruh word secara bersamaan,

membandingkan seluruh word secara bersamaan, tidak berdasarkan alamat

Waktu akses konstan dan tidak bergantung pada lokasi dan urutan akses sebelumnyaKarakteristik Memori

(6)

(5) Performansi Æ Latency : Time to access one word

Waktu akses (access time)

Waktu antara perintah akses (baca atau tulis) sampai didapatkannya data di MBR atau data dari MBR telah disalin ke lokasi memori tertentu

di MBR atau data dari MBR telah disalin ke lokasi memori tertentu (time between the request and when the data is available or written)

Waktu siklus memori (cycle time)

Waktu dimulainya suatu operasi memori sampai memori siap l k k i b ik t (l bih ti )

melaksanakan operasi berikutnya (lebih penting) (time between requests)

Waktu akses + waktu untuk perubahan signal jalur data sebelum akses kedua

cycle time > access time

Karakteristik Memori

(7)

Transfer rate

Adalah waktu rata-rata perpindahan datap p

RAM: 1/waktu siklus

Non-RAM:T

N= T

A+ N/R

TN = Waktu rata-rata untuk baca/tulis sejumlah N bit

T R t t kt k

TA = Rata-rata waktu akses N = jumlah bit

Karakteristik Memori

(8)

(6) Jenis fisik:

Semikonduktor : RAM, flashdisk

Magnetik : harddisk,

magnetic tape

Optik : CD, DVD

(7) Karakteristik fisik:

(7) Karakteristik fisik:

Volatile

: nilainya hilang bila tegangan listrik tidak ada Æ Semua internal memory ???

Non volatile

: nilainya TIDAK hilang (tetap ada) meskipun TIDAK ada

Non-volatile

: nilainya TIDAK hilang (tetap ada) meskipun TIDAK ada tegangan listrik

Erasable

: nilainya dapat dihapus (semikonduktor, magnetik)

Non erasable

: nilainya tidak dapat dihapus (ROM)

Non-erasable

: nilainya tidak dapat dihapus (ROM)(8) Organisasi memori:

Tugas Anda

¾

Yang dimaksud SRAM dan DRAM ?

¾

Apa yang dimaksud dengan SIMM DIMM dan

¾

Apa yang dimaksud dengan SIMM, DIMM dan

RIMM ?

¾

M

RAM ?

¾

Macam-macam RAM ?

EDO,

SDRAM,

DDR SDRAM,

DDR2 SDRAM,

SRAM

¾

SRAM dan DRAM adalah tipe chip memori.

¾

Static RAM (SRAM) jauh lebih cepat dan tidak

(

) j

p

memerlukan refresh daripada DRAM dan mampu

mengimbangi kecepatan Processor

¾

Menggunakan desain cluster yang memiliki 6

¾

Menggunakan desain cluster yang memiliki 6

transistor untuk setiap bit penyimpanannya.

¾

Menggunakan transistor tanpa kapasitor

¾

Menggunakan transistor tanpa kapasitor

¾

Kerapatan jauh lebih rendah daripada DRAM dan

DRAM

¾ Dynamic RAM, tipe chip memory yang digunakan pada kebanyakan memori utama.

¾ Keunggulannya adalah sangat padat sehingga dapat dimasukkan banyak bit ke dalam chipn a ang sangat kecil

bit ke dalam chipnya yang sangat kecil.

¾ Sel-sel nya terdiri dari kapasitor tipis yang memiliki charge untuk mengindikasikan bit.

¾ DRAM harus terus di refresh. Karena jika tidak direfresh menyebabkan

¾ DRAM harus terus di refresh. Karena jika tidak direfresh menyebabkan beban listrik pada kapasitor akan habis dan data akan hilang.

¾ Refresh dilakukan ketika controller memory siap berhenti untuk

mengakses semua baris data pada chip. Kecepatan refresh standar nya adalah 15 microsecond

adalah 15 microsecond.

¾ Menggunakan 1 transistor & sepasang kapasitor per bit yang menjadikan sangat padat.

¾ Jika densitas mencapai 512MB ini berarti chip DRAM memiliki 512 juta transistor.

SIMM, DIMM dan RIMM

¾ SIMM , DIMM dan RIMM adalah Tipe-tipe Modul chip

memory. Dimana masing-masing tipe memiliki jumlah pin, memory row width yang berbeday y g

¾ SIMM = Single Inline Memory Module, DIMM = Dual Inline Memory Module, RIMM = Rambus Inline Memory Module.

¾ SIMM ada 2-tipe yaitu 30-pin (8-bit plus 1 bit paritas) dan

¾ SIMM ada 2 tipe yaitu 30 pin (8 bit plus 1 bit paritas) dan 72-pin (32 bit plus 4 bit paritas).

¾ DIMM ada 2 versi, dengan chip SDRAM atau DDR SDRAM yang dibedakan dengan karakteristik fisik.

y g g

¾ DIMM SDRAM memiliki 168-pin, sedangkan DDR DIMM memiliki 184-pin.

¾ Perbedaan utama dengan SIMM, DIMM memiliki pin-pin

¾ Perbedaan utama dengan SIMM, DIMM memiliki pin pin

sinyal yang berbeda di setiap sisi modul. DIMM memiliki lebih banyak pin daripada SIMM. Memiliki lebar data path 64-bit (non-paritas) atau 72-bit dengan paritas atau ECC (error

SIMM, DIMM dan RIMM

¾

SIMM ada 2-tipe,30-pin (8-bit plus 1 bit paritas) dan

72-pin (32 bit plus 4 bit paritas).

p

(

p

p

)

¾

DIMM ada 2 versi, chip SDRAM atau DDR

¾

SDRAM Memiliki 168-pin, DDR DIMM memiliki 184-

p ,

pin.

¾

Perbedaan utama dengan SIMM, pin-pin sinyal yang

g

, p

p

y

y

g

berbeda di setiap sisi modul.

¾

DIMM memiliki lebih banyak pin daripada SIMM.

SIMM, DIMM dan RIMM

¾

RIMM memiliki pin-pin di 2 sisi modul nya

¾

Jumlah pin-nya : 184-pin (16/18-bit) 232-pin

¾

Jumlah pin-nya : 184-pin (16/18-bit), 232-pin

(32/36-bit), 326-pin (64/72-bit).

¾

RIMM d

16 bit di

k

t k

lik

i

¾

RIMM dengan 16-bit digunakan untuk aplikasi

non-ECC

¾

Masing-masing memiliki kecepatan yang

berbeda. Baik DRAM SIMM, DIMM, dan RIMM

Organisasi Memori

Organisasi Memori

Sel Memori

(1)

¾

Setiap memori tersusun dari rangkaian sel-sel

Sel Memori

(2)

¾

Sifat-sifat sel memori:

Dapat memberikan 2 kondisi (1 atau 0)p ( )

Dapat ditulisi (minimal satu kali) dengan cara mengubah kondisi sel memori

dib

Dapat dibaca

¾

Tiap sel terdiri dari 3 terminal:

S l t t k ilih l i k

Select: untuk memilih sel memori yang akan dibaca/ditulisi

Control: untuk menentukan jenis operasi write/read

Control: untuk menentukan jenis operasi write/read

Data:

Write: untuk mengubah kondisi sel dari 1 ke 0 atau sebaliknya

Sel Memori

(3)

¾

Apa

syarat

device

dapat digunakan untuk menyimpan

data biner ?

Hanya dapat menyimpan 2 macam nilai/kondisi (

true false

Hanya dapat menyimpan 2 macam nilai/kondisi (

true-false

atau 1-0) yang stabil

Mempunyai pembatas yang lebar yang dapat memisahkan kedua nilai/kondisi secara tegas

kedua nilai/kondisi secara tegas

Mampu menangani perubahan nilai/kondisi dalam waktu yang tidak terbatas

Nilai/kondisinya tidak rusak pada saat dibaca

Nilai/kondisinya tidak rusak pada saat dibaca

Apakah saklar/switch memenuhi syarat ???

¾

Implementasinya dengan apa ?

¾

Implementasinya dengan apa ?

Magnetic core

Semikonduktor:

G b t t i t d k it

Gabungan antara transistor dan kapasitor

Sel Memori

(4)

Magnetic core

Ferric oxide coating

Ferric oxide coating

+ Bahan yang mudah bersifat magnet

Selection wire

:+ Untuk menentukan nilai medan magnet

+ Untuk menentukan nilai medan magnet

+ Jika arah arus berbeda Æ medan

magnet berbeda

Sense wire

:

Sense wire

:+ Untuk membaca nilai bit yang disimpan

Cara kerja:+ Simpan data (

write

):o Aliri select wire dengan arah arus

Sel Memori

(5)

Cara kerja: (cont’d)+ Baca data (

read

):+ Baca data (

read

):o Selection wire dialiri arus yang menghasilkan bit bernilai 0

o Jika bit yang sedang disimpan:

0 Æ Tid k d t i d k i d i

= 0 Æ Tidak ada tegangan induksi pada sense wire

Æ Bit bernilai 0

= 1 Æ Medan magnet berubah

Æ Data yang disimpan berubah dari 1 menjadi 0

Æ Sense wire terinduksi berarti data yang sedang disimpan bernilai 1

disimpan bernilai 1

Æ Kembalikan nilai bit ke nilai semula (1) dengan cara

aliri select wire dengan arus yang menghasilkan bit

b il i 1

Sel Memori

(6)

Gabungan antara transistor dan kapasitor

(memori dinamis)

(memori dinamis)

Capasitor

+

Untuk menyimpan nilai data

Address line

:

+

Untuk mengaktifkan sel

memori (transistor)

Bit line

:

Sel Memori

(7)

Gabungan antara transistor dan kapasitor

(memori dinamis)

(cont’d)

2

(memori dinamis)

(cont d)

Cara kerja

+

Simpan data (

write

):

3

+

Simpan data (

write

):

1. Signal yang akan ditulis

dihubungkan ke bit line (high

voltage = 1 low voltage = 0)

4

voltage = 1, low voltage = 0)

2. Signal diberikan ke address line Æ

transistor on

3. Untuk simpan bit 1 Æ arus

1

3. Untuk simpan bit 1 Æ arus

mengalir masuk ke kapasitor

Ækapasitor diisi muatan

4. Untuk simpan bit 0 Æ arus

Sel Memori

(8)

Cara kerja

:

(cont’d)B

d t (

d

)

1

+

Baca data (

read

):

1. Address line diberi signal Æ transistor on

4 2. Muatan kapasitor dialirkan ke bit

line/sense amplifier

3. Sense amplifier membandingkan

3

p g

muatan kapasitor dengan tegangan reference untuk menentukan

apakah data bernilai 1 atau 0

2 4. Muatan kapasitor berkurang Æ

perlu di-refresh Æ disebut

Sel Memori

(9)

Gabungan antara beberapa transistor (

memori statis)

Status T1 selalu berlawanandengan T3 tetapi selalu sama dengan T3, tetapi selalu sama dengan T4

Status T2 selalu berlawanan dengan T4 tetapi selalu sama dengan T4, tetapi selalu sama dengan T3

Nilai bit line berlawanan dengan nilai bit line BB

dengan nilai bit line B

Sel Memori

(10)

¾

Magnetic core

vs Semikonduktor

M

ti

S

ik

d kt

Magnetic core

Semikonduktor

(-) Lambat (

switching

: 0.5-3 µS) (+) Cepat (switching

: 10-200 nS) ( ) Unt k l n ng m jml (+) Unt k l n ng m jml (-) Untuk luasan yang sama jml (+) Untuk luasan yang sama jmlmemori lebih sedikit memori jauh lebih banyak (+)

Non-volatile

(-)Volatile

Organisasi Memori

(1) - rev

¾

Bagaimana sel-sel memori disusun ?

Organisasi Memori

(2)

- rev

¾

Memori dapat digambarkan seperti sebuah matriks

berukuran m kali n, dimana:

l b i j l h bi d l l

m = lebar memori = jumlah bit dalam satu alamat =minimum addressable unit

n = ukuran memori = jumlah alamat

n ukuran memori jumlah alamat

¾

Setiap bit pada setiap alamat yang mempunyai posisi yang

sama disusun ke dalam sebuah

memory plane

¾

Memory plane

merupakan array 2 dimensi

Æ

dibutuhkan 2

buah

select line

(x dan y)

¾

Setiap satu

memory plane

terdiri dari

sebuah

sensor line

¾

Setiap satu

memory plane

terdiri dari

sebuah

sensor line

Organisasi Memori

(3)

- rev

¾

Contoh soal:

Sebuah memori terdiri dari 32 alamat dan setiap

p

alamat terdiri dari 16 bit.

Berapakah jumlah jalur untuk setiapselect line ?

B k h j l h

l

di l k ?

Berapakah jumlahmemory plane

yang diperlukan ?

Berapakah kapasitas memori ?Jawab:

Jawab:

Jumlah jalur setiapselect line

= 32, 2 dan 16, 4 dan 8, atau 8 dan 4, atau 16 dan 2, ,Jumlah

memory plane

= jumlah bit setiap alamat = 16memory plane

K it i 32 16 bit 512 bit 64 b t

Organisasi Memori

(4)

- rev

¾

Memory bank

Merupakan memori yang tersusun dari sejumlah memory plane

Sebuah memory bank tersusun dari beberapa chip

Pada gambar di bawah ini, berapakah:

Jumlah bit setiap alamat ?

Jumlah bit setiap alamat ?

Organisasi Memori

(5)

- rev

¾

Contoh soal:

Sebuah RAM berkapasitas 128 MB dipasang pada sebuah komputer dengan prosesor Intel dan menggunakan format komputer dengan prosesor Intel dan menggunakan format instruksi yang terdiri dari 32 bit. Setiap satu

memory plane

dikemas ke dalam sebuah chip.

Berapakah jumlah chip dalam RAM tersebute apa a ju a c p da a te sebut ?

Berapakah jumlah alamat yang tersedia ?

Berapakah jumlah jalur untuk select line ?

Jawab:

- Jumlah bit dalam setiap alamat untuk komputer dengan prosesor Intel adalah 8 bit Æ diperlukan 8 buah

memory

plane

Æ terdapat 8 chipp

p p- Jumlah alamat yang tersedia = kapasitas setiap

memory

plane

/chip yaitu (128 x 8/8) M = 128 M alamatPengaksesan Memori

(1)

Pengaksesan Memori

(2)

¾ MAR (

Memory Address Register

): Memuat alamat dari lokasi memori yang akan diakses (baca/tulis)

Jumlah bit MAR menentukan jumlah maksimum dari memori fisik

Jumlah bit MAR menentukan jumlah maksimum dari memori fisik yang dapat dipasang dalam suatu komputer

Jika MAR terdiri dari n bit Æ alamat memori yang valid adalah 0 hingga 2n 1

hingga 2n - 1

¾ MBR (

Memory Buffer Register

): Memuat isi informasi yang akan dituliskan ke memori atau baru saja dibaca dari memori pada alamat yang ditunjukkan oleh isi MAR

MBR dapat berukuran m bit, 2m bit, 4m bit, dst dimana m =

jumlah bit minimal dalam satu alamat (minimum addressable unit )

¾

Memory Decoder

: Untuk menerjemahkan alamat yang disimpan dalam MAR

Pengaksesan Memori

(3)

¾

Urutan

baca

dari memori:

Taruh alamat memori yang akan dibaca (dalam unsigned binary) ke MAR (range 0 hingga 2n – 1)

binary) ke MAR (range 0 hingga 2 1)

Kirim READ signal melalui READ control line

Decode isi MAR sehingga diperoleh nilai x dan y (nilai MAR tidak berubah)

tidak berubah)

Taruh isi alamat yang ditunjuk ke dalam MBR

¾

Urutan

tulis

ke memori:

Taruh alamat memori yang akan ditulisi (dalam unsigned binary) ke MAR (range 0 hingga 2n – 1)

Taruh data yang akan ditulis ke MBRy g

Kirim signal WRITE melalui WRITE control line

Decode isi MAR sehingga diperoleh nilai x dan y (nilai MAR tidak berubah)

tidak berubah)

Pen-

decode

-an Memori

(1)

Bagaimana cara men-

decode

alamat memori ?¾ Contoh:

S b h i i 128 l t ( k i ) ti

Sebuah memori mempunyai 128 alamat (maksimum) yang setiap alamat terdiri dari 8 bit. Memori tersebut tersusun dari 8 memory bank , maka:

D t ti b k 128/8 16 l t

Daya tampung setiap memory bank = 128/8 = 16 alamat

16 alamat = 24 alamat Æ diperlukan 4 jalur untuk setiap select line

128 alamat = 27 alamat Æ jumlah bit MAR = 7 bit

M b k Al t D l bi

Memory bank Alamat Dalam biner

ke-0 0 – 15 0000000 – 0001111

ke-1 16 – 31 0010000 – 0011111

... ... ...

ke-7 112 – 127 1110000 – 1111111

+Bit ke-4, 5, 6 nilainya tetap untuk setiap memory bank dan

b b d t k b k b b d Æ Bit k 4 5 6

Pen-decode-an Memori

(2)

Bit 7 (plane ke-7) Bit 0 (plane ke-0)

(0,7) (1,7)

(memory bank ke-0) sebanyak 128 alamat

. . .

(16,7) (17,7) (16,0) (17,0)

Location 16 – 31 (memory bank ke-1)

Location 112 – 127 (memory bank ke-7)

(112,0) (113,0)

Pen-decode-an Memori

(3)

Bagaimana cara menentukan nilai x dan y ?

Alamat ke-0, 1, 2, dan 3 terletak pada baris pertama pada plane

ke-0 dan pada bank ke-0 adalah sbb:

Alamat Dalam biner

Alamat ke-4, 5, 6, dan 7 terletak pada baris kedua pada plane

ke-0 dan pada bank ke-0 adalah sbb:

ke 0 dan pada bank ke 0 adalah sbb:

Pen-decode-an Memori

(4)

Alamat yang terletak pada kolom pertama pada plane ke-0 dan

pada bank ke-0 adalah sbb:

Alamat Dalam biner

Alamat yang terletak pada kolom kedua pada plane ke-0 dan

pada bank ke-0 adalah sbb:

p

Pen-decode-an Memori

(5)

Arti/fungsi setiap bit pada MAR adalah sbb:

ROM

ROM dan

dan RAM

RAM

“Read”

Only Memory (ROM)

¾

ROM (Read Only Memory)

Æ

PROM (

Æ

PROM (

Programmable ROM)

Æ

EP

ROM (Erasable PROM)

Æ

EEP

ROM (Electrically EPROM)

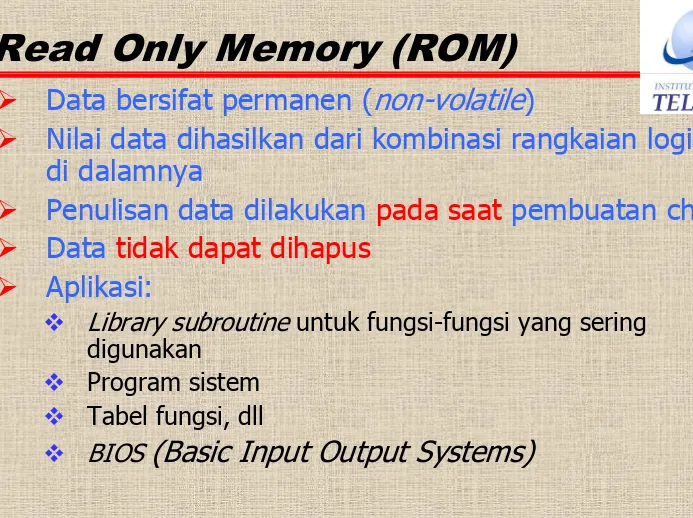

Read Only Memory (ROM)

¾

Data bersifat permanen (

non-volatile

)

¾

Nilai data dihasilkan dari kombinasi rangkaian logika

g

g

di dalamnya

¾

Penulisan data dilakukan

pada saat

pembuatan chip

¾

Data

tidak dapat dihapus

¾

Aplikasi:

Lib

b

ti

t k f i f i i

Library subroutine

untuk fungsi-fungsi yang sering digunakan Program sistem

Tabel fungsi, dll

Programmable ROM (PROM)

¾ Data ditulis

sesudah

chip dibuat¾ Digunakan bila jumlahnya tidak terlalu besar (bukan mass d t) d t d t kh

product) dan memuat data khusus

¾ Non-volatile

¾ Hanya dapat ditulisi

satu kali

¾ Hanya dapat ditulisi

satu kali

¾ Penulisan data dilakukan secara elektrik dengan PROM programmer

¾ Sel memori “dibakar” (burning in) dengan arus listrik yang cukup besar

¾ Sel memori dibakar (burning-in) dengan arus listrik yang cukup besar, lokasi bit akan terbakar dan menunjukkan sebuah nilai (0 atau 1)

¾ Data tidak dapat dihapus

¾ Lebih fleksibel daripada ROM

Erasable PROM (EPROM)

¾

Data ditulis

sesudah

chip dibuat

¾

Non volatile

¾

Non-volatile

¾

Proses baca dan tulis secara elektrik

¾

Data dapat dihapus dan ditulisi

berulang-ulang

¾

Data dapat dihapus dan ditulisi

berulang ulang

dengan radiasi ultraviolet

¾ Sinar tersebut melewati celah di kumpulan chip

¾

Data dihapus dalam satuan

chip

(

semua data dihapus

)

Electrically EPROM (EEPROM)

¾

Data ditulis

sesudah

chip dibuat

¾

Non volatile

¾

Non-volatile

¾

Data dapat ditulis dan dihapus

kapan saja

secara

elektrik, data tidak perlu dihapus terlebih dahulu

elektrik, data tidak perlu dihapus terlebih dahulu

¾

Data dihapus dalam satuan

byte

¾

Lebih mahal daripada EPROM

Flash Memory

¾

Non-volatile

¾

Biaya dan fungsionalitas berada diantara EPROM dan

¾

Biaya dan fungsionalitas berada diantara EPROM dan

EEPROM

¾

Data dihapus dalam satuan

p

blok memori

¾

Lebih rapat dibanding EEPROM

¾

Contoh aplikasi:

¾

BIOS

Æ

i i

l bih

d h di b h

k l h

Hirarki Memori

Æ Biaya per bit

ki h Registers

makin murah

Æ Kapasitas makin

besar Disk cache (pure S/W)

Disk (Harddisk)

O ti l ( ) d akses oleh prosesor makin

jarang Optical (CD, DVD)

RAM (Random Access Memory)

(1)¾

Dynamic RAM (DRAM)

Sel DRAM:

Data berupa muatan listrik yang disimpan di kapasitor

Mengapa disebut

dynamic RAM ?

Muatan listrik yang

Muatan listrik yangdisimpan di kapasitor cenderung mengalami kebocoran sehingga kebocoran, sehingga harus selalu di-

refresh

DRAM digunakan

RAM (Random Access Memory)

(2)¾

Static RAM (SRAM)

Sel SRAM:

Sel SRAM:

Disusun dari beberapa transistor (flip-flop

)

Mengapa disebut static

RAM ?

Selama masih adalistrik, maka data yang disimpan tidak hilang disimpan tidak hilang, sehingga tidak perlu

di-refresh

DRAM vs SRAM

DRAM SRAM

(+) sederhana (-) lebih kompleks

(+) dimensi lebih kecil (-) dimensi lebih besar (+) murah (-) lebih mahal

(+) kapasitas besar ( ) kapasitas kecil

(+) kapasitas besar (-) kapasitas kecil

(-) perlu rangkaian

refresh

(+) tidak perlu di-refresh

(-) biaya rangkaian

refresh

(+) tidak perlu rangkaianrefresh

( ) y g ( ) p g

memori berukuran besar lebih mahal daripada biaya

i i di i

memori itu sendiri

(-) lebih lambat (-) lebih cepat ¾ Apa kesamaannya ???

Chip Logic DRAM 16 Mbit (4Mx4)

(2)¾

Dalam satu saat dapat dibaca/ditulis data 4 bit (1 bit

tiap memori plane)

tiap memori plane)

¾

Terdiri dari 4 buah

array

berukuran 2048 x 2048

¾

Alamat tiap sel ditentukan oleh alamat baris dan kolom

p

¾

Pin alamat baris paralel dengan alamat kolom

Æ

hemat jumlah pin

Æ

digunakan RAS dan CAS

¾

Terdapat 4 pin untuk data

in (write)

dan

out (read)

l l

Æ

di

k

WE d

OE

secara paralel

Æ

digunakan WE dan OE

¾

Refresh

dilakukan dengan membaca data dan

menuliskannya kembali

Contoh

Chip Packaging

(1)¾

EPROM 8 Mbit:

Alamat = 20 bit (pin) = A0-(p ) A19 = 1 M alamat

1 alamat = 8 bit Æ kapasitas = 8 x 1 Mbit = 8 Mbit

8 x 1 Mbit 8 Mbit

Chip Enable (CE) untuk

memilih chip yang aktif bila di k l bih d i t hi digunakan lebih dari satu chip

D0-D7 = data keluar (8 jalur)

Vss = ground

Contoh

Chip Packaging

(2)¾

DRAM 16 Mbit:

Alamat = 11 pin = A0-A10

Di k l h b i d k l

Digunakan oleh baris dan kolom secara bergantian Æ setara dengan 2x11 pin = 22 pin = 222 alamat = 4 M

alamat

1 alamat = 4 bit Æ kapasitas = 4 M x 4 bit = 16 bit

CAS untuk mengaktifkan kolom

RAS untuk mengaktifkan kolom

D0-D3 = data keluar (4 jalur)

OE = Output Enable (memungkinkan d t dib )

data dibaca)

WE = Write Enable =

memungkinkan data disimpan ke memori

Organisasi Modul

(1)¾

Organisasi memori

256 Kbyte

Terdiri dari 8

memori

plane

berukuran

512 x 512 bit

Alamat terdiri dari

18 bit (9 b i

9

18 bit (9 baris, 9

kolom)

Organisasi Modul

(3)

¾

Organisasi memori 1 Mbyte

Terdiri dari 4 buah bank memori masing-masing

Terdiri dari 4 buah bank memori masing masing

berukuran 256 KByte (4 kolom A, B, C, D)

Alamat terdiri dari 20 bit (2 bit MSB digunakan

untuk memilih group chip A B C atau D)

Advanced DRAM

(1)

¾

Synchronous DRAM (SDRAM)

Pertukaran data didasarkan pada

signal clock

t

eksternal

tanpa

wait state

Kecepatan

sesuai

dengan kecepatan prosesor

atau bus memori

atau bus memori

Selama proses pencarian data, CPU dapat

Advanced DRAM

(2)

Contoh: SDRAM read timing

Burst length = 4 = T3-T6, CAS latency = 2 = T1-T2

Burst length = banyaknya clock untuk mengirimkan data (1, 2, 4, 8, full page)

Latency = banyaknya clock yang diperlukan untuk persiapan sebelum

Latency = banyaknya clock yang diperlukan untuk persiapan sebelum data dikirimkan

¾

Double Data Rate – SDRAM (DDR-SDRAM)

(

)

Advanced DRAM

(3)

Contoh

Advanced DRAM

(4)

¾

Rambus DRAM (RDRAM)

Diadopsi oleh Intel untuk Pentium dan Itanium

Pesaing model SDRAM

Bus alamat support s.d. 320 chip RDRAM

Transfer data s.d. 1,6 GBps (2 x 800 MBps), p ( p )

Impedance, clock, dan signal didefinisikan secara tepat

Jalur data sebanyak 18 bit (16 data, 2 parity)

Jalur RC (8 bit) digunakan untuk alamat dan signal control

Jalur RC (8 bit) digunakan untuk alamat dan signal control

Memory request

tidakmenggunakan RAS, CAS, R/W atau

CE,

tetapi melaluihigh speed bus

yang memuat informasi: alamat yang diinginkan

alamat yang diinginkan

jenis operasi

jumlah byte dalam operasi

Pengiriman data secara