LAPORAN PRAKTIKUM

“HALF ADDER DAN FULL ADDER”

Disusun oleh:

Nama : Yuli Julaila

NIM : K2315064

Kelas : B

PROGRAM STUDI PENDIDIKAN FISIKA

FAKULTAS KEGURUAN DAN ILMU PENDIDIKAN

UNIVERSITAS SEBELAS MARET

HALF ADDER DAN FULL ADDER I. TUJUAN

Mengamati keluaran dari rangkaian half adder sehingga keluaran dapat disusun kembali persamaan aljabarnya.

Membuat rangkaian yang dapat mengoperasikan perkalian dua bit bilangan biner.

Mengamati keluaran dari rangkaian half adder sehingga keluaran dapat disusun kembali persamaan aljabarnya.

Membuat rangkaian yang dapat mengoperasikan perkaliantiga bit dengan dua bit bilangan biner.

II. DASAR TEORI

Fungsi terpenting dari hampir semua computer dan kalkulator adalah melakukan operasi-operasi aritmetik. Operasi-operasi ini semuanya dilaksanakan di dalam unit aritmetik computer, di dalam unit ini gate-gate logika dan flip-flop dikombinasikan sedemikian rupa sehingga dapat melakukan operasi penjumlahan, pengurangan, perkalian dan pembagian bilangan-bilangan biner.

Dalam dunia elektronika, sebuah adder atau summer (penjumlah) merupakan suatu rangkaian digital yang melakukan proses penjumlahan dari bilangan-bilangan yang ada. Dalam banyak komputer dan berbagai jenis processor, adder tidak hanya digunakan dalam ALU (Arithmetic Logic Unit), tapi juga digunakan dalam bagian processor lainnya, dimana digunakan untuk menghitung alamat, tabel, dan berbagai operasi lainnya.Meski adder dapat dirangkai untuk berbagai keperluan representasi bilangan, semisal BCD (Binary Coded Decimal) atau Excess-3, yang mana kebanyakan adder digunakan untuk operasi bilangan biner.

bilangan biner dapat memiliki beberapa digit biner. Gambar berikut menunjukkan penjumlahan dari dua bilangan 4-bit.

Gambar 2.1 Contoh Proses penjumlahan Biner

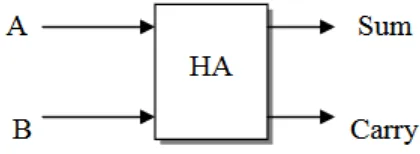

Half adder adalah suatu rangkaian penjumlah sistem bilangan biner yang paling sederhana. Rangkaian ini hanya dapat digunakan untuk operasi penjumlahan data bilangan biner sampai 1 bit saja. Rangkaian half adder mempunyai 2 masukan dan 2 keluaran yaitu Summary out (Sum) dan Carry out (Carry). Secara blok diagram dapat digambar sebagai berikut :

Gambar 2.2 Blok Diagram Half Adder

Prinsipnya adalah OUTPUT Sum itu menyatakan hasil penjumlahan input A dan B, sedangakan Carry adalah menyatakan MSB (most significant bit atau carry bit) dari penjumlahan tersebut.

Dimana A dan B merupakan data-data Input.

Operasi dari HA dapat ditunjukkan pada tabel kebenaran berikut:

Persamaan logikanya adalah :

Sum = (A’ . B) + (A . B’) serta Carry = A. B

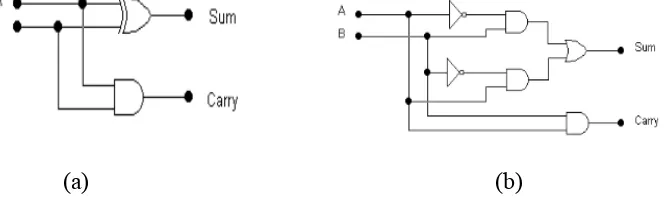

Half Adder dapat diimplementasikan dengan menggunakan EX-OR gate atau susunan gate yang membentuk fungsi EX-OR untuk sum dan AND gate untuk carry.Rangkaian HA dapat ditunjukkan pada gambar 2.3.

(a) (b)

Gambar 2.3.(a). untuk HA yang disusun dari EX-OR dan AND dan (b) untuk HA yang disusun dari AND, OR dan NOT gate

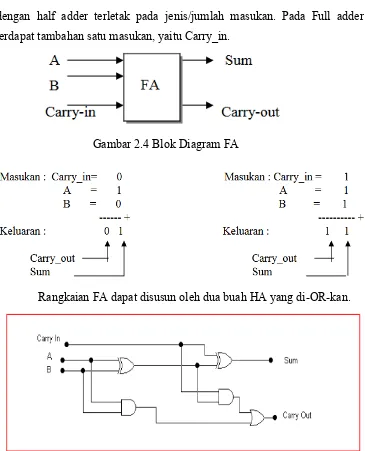

dengan half adder terletak pada jenis/jumlah masukan. Pada Full adder terdapat tambahan satu masukan, yaitu Carry_in.

Gambar 2.4 Blok Diagram FA

Rangkaian FA dapat disusun oleh dua buah HA yang di-OR-kan.

Tabel Kebenaran Full Adder

Dari tabel kebenaran dapat dituliskan ekspresi logika untuk Sum dan carry :

Sum = A’B’Cin + A’B Cin’ + A B’Cin’ + A B Cin Carry = A’B Cin + A B’ Cin + A B Cin’ + A B Cin

III. METODE EKSPERIMEN

III.1 Alat dan Bahan

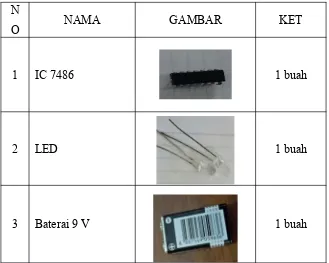

N

O NAMA GAMBAR KET

1 IC 7486 1 buah

2 LED 1 buah

4 Papan Percobaan 1 buah

1. Alat dan bahan disiapkan

2. Alat dan bahan disusun pada protoboard sesuai dengan skema yang telah diberikan,

a. Half Adder (IC 7408 dan IC 7486) 1) Kaki 1 dan 2 IC 7408 sebagai input.

2) Kaki 1 IC 7408 dihubungkan pada kaki 2 IC 7485. 3) Kaki 2 IC 7408 dihubungkan pada kaki 1 IC 7486.

5) Kaki 3 IC 7486 dihubungkan ke kaki positif LED lainnya sebagai output Sum.

6) Kaki 7 IC 7408 dihubungkan ke kaki 7 IC 7486 dan dihubungkan ke ground, lalu dihuuingkan ke negatif baterai.

7) Kaki 14 IC 7408 dihubungkan ke kaki 14 IC 7486 dan dihubungkan ke positif baterai.

b. Full Adder (IC 7408, IC 7432 dan IC 7486)

1) Kaki 1, kaki 5 dan kaki 5 IC 7486 sebagai input 2) Kaki 1 IC 7486 dihubungkan ke kaki 5 IC 7408. 3) Kaki 2 IC 7486 dihubungkan ke kaki 4 IC 7408.

4) Kaki 3 IC 7486 dihubungkan ke kaki 4 IC 7486, lalu dihubungkan ke kaki 1 IC 7408.

5) Kaki 5 IC 7486 dihubungkan ke kaki 2 IC 7408. 6) Kaki 3 IC 7408 dihubungkan ke kaki 1 IC 7432. 7) Kaki 6 IC 7408 dihubungkan ke kaki 2 IC 7432. 8) Kaki 3 IC 7432 dihubungkan ke positif LED.

9) Kaki 7 semua IC dihubungkan, lalu dihubungkan ke kaki negatif LED dan negatif baterai.

10)Kaki 14 semua IC dihubungkan, lalu dihubungkan ke positif baterai.

3. Data yang diperoleh dianalisis.

Gambar 3.1. Skema rangkaian Half Adder

Gambar 3.2. Skema rangkaian Full Adder

1. Half Adder

V. ANALISA HASIL DAN PEMBAHASAN

1. Half Adder

Pada rangkaian Half Adder digunakan dua IC yakni IC 7408 (AND) dan IC 7486 (XOR), lalu membuat tabel kebenaran dengan memasukkan input yang akan di cek menggunakan tabel tersebut. Input yang digunakan ada 2 yakni input A dan input B . Dengan menggunakan input tersebut maka selanjutnya mencari harga dari keluaran Y atau S (Sum) dan Cr (carry) atau bawaan .

Sedangkan Cr merupakan hasil keluaran AND yakni sesuai dengan teoriu bahwa yaitu ”Jika Input A dan B salah satunya High, maka output akan High dan jika Input A atau B keduanya berharga sama maka output akan Low”.

Penambaha half adder merupakan rangkain dasar dan langah awal menuju rankaian-rangkaian yang mampu melakukan proses aritmatika yang lebih sulit.Dalam menjumlahkan dua bilngan biner, mungkin terdapat bawaan (carry) dari satu kolom ke kolom berikutnya sesuai dengan :

2. Full Adder

input A dan C bernilai 0 (LOW), input B bernilai 1 (HIGH) maka output yang dihasilkan berupa 1 (HIGH) pada keluaran S (Sum) dan berharga 0 (LOW) pada bawaan Cr (Carry). Jika input B dan C bernilai 1 (HIGH), input A bernilai 0 (LOW) maka output yang dihasilkan berupa 0 (LOW) pada keluaran S (Sum) dan berharga 1 (HIGH) pada bawaan Cr (Carry) yang akan ditambahkan pada penambahan 3 bit bilangan biner selanjutnya. Jika input B dan C bernilai 0 (LOW), input A bernilai 1 (HIGH) maka output yang dihasilkan berupa 1 (HIGH) pada keluaran S (Sum) dan berharga 0 (LOW) pada bawaan Cr (Carry). Jika input A dan C bernilai 1 (HIGH), input B bernilai 0 (LOW) maka output yang dihasilkan berupa 0 (LOW) pada keluaran S (Sum) dan berharga 1 (HIGH) pada bawaan Cr (Carry) yang akan ditambahkan pada penambahan 3 bit bilangan biner selanjutnya. Jika input A dan B bernilai 1 (HIGH), input C bernilai 0 (LOW) maka output yang dihasilkan berupa 0 (LOW) pada keluaran S (Sum) dan berharga 1 (HIGH) pada bawaan Cr (Carry) yang akan ditambahkan pada penambahan 3 bit bilangan biner selanjutnya. Jika input A, B dan C bernilai 1 (HIGH), maka output yang dihasilkan berupa 1 (HIGH) pada keluaran S (Sum) dan berharga 1 (HIGH) pada bawaan Cr (Carry).

Pada rangkaian Full Adder digunakan 3 IC yakni IC 7408 (AND),IC 7432 (OR) dan IC 7486 (XOR), lalu membuat tabel kebenaran dengan memasukkan input yang akan diuji menggunakan tabel tersebut. Input yang akan digunakan ada 3 yakni input A, input B , dan input C. Dengan menggunakan input tersebut akan dicari S (Sum) dan Cr (carry) .

Dari tabel di atas dapat diturunkan persamaan Boolean � = �̅�

Adder digital yang dapat mengoperasikan proses perkalian 3 bit x 2 bit dengan menggunakan gerbanggerbang yang digunakan.

VI. KESIMPULAN

1. Half adder adalah suatu rangkaian penjumlah dua bit bilangan biner yang hasil penjumlahan biner tersebut terdiri dari jumlahan (sum) keluaran dari XOR dan bawaan (carry out) hasil keluaran dari AND. Carry harus ditambahkan pada posisi penjumlahan berikutnya, yaitu dijumlahkan menjadi satu dengan augend dan addend pada posisi tersebut.

2. Full Adder adalah suatu rangkaian yang digunakan untuk menambahkan tiga bit dengan dua bilangan biner, sehingga dapat dilakukan penambahan penuh (full adder),sehingga diturunkan

persamaan Boolean � = �̅� ̅� + �̅��̅ + �� ̅�̅ + ��.

VII. DAFTAR PUSTAKA

Aminah, Nonoh Siti. 2013. Logika Biner dan Pencacah. Surakarta : UNS Press.

http://staff.uny.ac.id/sites/default/files/Rang%20Aritmetik.pdf (diakses pada 2 Maret 2017, pukul 20.00 WIB)

VIII. LAMPIRAN Lampiran 1

Lampiran 2.