PELINDUNG

Dekan FAKULTAS TEKNIK ELEKTRO Dr. Ir. Rina Pudji Astuti M.T.

Kepala Bidang Keahlian Achmad Rizal, Ssi., MT

Koordinator Dosen Rangkaian Logika Denny Darlis, Ssi., MT

Dosen Pembimbing Laboratorium Estananto, M.Sc

PELAKSANA Koordinator Asisten Gede Teguh Laksana

Sekretaris dan Bendahara Clara Amanda

Administrasi Rizka Fadhilla

Divisi Praktikum Muhammad Aditya Taufik

Ridwan Pratama Garizah Ganih Pranoto

Divisi Hardware Widi Tama Salman Wahyu Yanuar Arifin

Divisi Riset and Development Faisal Arifin

Riandanu Aldy Sadewo Hannan Aulia Mardhiah Harahap

Dwi Kurniawan

Divisi RNS Fujitson Simamora Fista Monica Deswanti

TATA TERTIB PELAKSANAAN PRAKTIKUM LABORATORIUM TEKNIK DIGITAL

FAKULTAS TEKNIK ELEKTRO 1. ATURAN UMUM

a. Semua praktikan wajib menggunakan seragam sesuai peraturan resmi seragam Universitas Telkom dan wajib memakai sepatu.

b. Praktikan laki – laki : Baju wajib dimasukkan untuk hari Senin – Rabu. c. Praktikan perempuan : Bawahan rok berwarna biru dongker atau hitam.

d. Tidak diperbolehkan memakai bawahan selain celana / rok bahan biru dongker atau hitam sesuai dengan aturan kampus Universitas Telkom.

e. Rambut harus rapi (untuk laki-laki, rambut tidak boleh menyentuh kerah).

f. Kelengkapan praktikum meliputi kartu praktikum (Kartu praktikum wajib diberi foto dan distempel oleh Laboratorium Teknik Digital).

g. Praktikan diberikan waktu sampai tes awal berakhir untuk melengkapi segala kelengkapan praktikum yang tidak dibawa.

h. Apabila praktikan tidak membawa kelengkapan praktikum, maka praktikan wajib melapor ke asisten. i. Segala bentuk pelanggaran yang dilakukan oleh praktikan akan diberikan sanksi berupa tugas tambahan yang

diberikan di akhir praktikum oleh Laboratorium Teknik Digital.

j. Praktikan tidak diperbolehkan melakukan bentuk intimidasi. Segala bentuk intimidasi akan ditindaklanjuti oleh Fakultas Teknik Elektro.

2. PELAKSANAAN PRAKTIKUM

Praktikum dimulai sesuai waktu yang telah ditentukan.

Praktikan sebaiknya datang 15 menit sebelum praktikum dimulai.

Apabila praktikan terlambat lebih dari 20 menit tanpa alas an yang jelas, maka praktikan tidak diijinkan mengikuti praktikum untuk modul tersebut dan harus mengulang di tahun depan.

Praktikum diselenggarakan selama 2,5 jam.

Kartu praktikum wajib dibawa oleh praktikan dimana diserahkan dan ditandatangani oleh asisten yang menjaganya pada saat itu.

Praktikan dapat melaksanakan praktikum setelah mendapatkan instruksi dari asisten praktikum. Selama praktikum berlangsung, praktikan dilarang:

Membuat kegaduhan di dalam ruangan. Mengubah konfigurasi Software/Hardware.

Meninggalkan ruangan praktikum tanpa izin asisten. Makan, minum, dan merokok.

Telepon/SMS tanpa izin asisten.

3. KEHADIRAN

Praktikan berkewajiban mengikuti semua modul praktikum. Ketidakikutsertaan pada satu modul, maka modul tersebut mendapatkan nilai nol dan tidak lulus praktikum Rangkaian Logika. Praktikan yang sakit harus memberikan surat keterangan sakit dari Rumah Sakit dan ditandatangani oleh dokter yang memeriksa dan dibawa ke Laboran (Maksimal 1 modul praktikum). Tidak ada Praktikum susulan bagi Praktikan.

4. PROSEDUR TUKAR JADWAL

a. Pertukaran jadwal praktikum paling lambat 1 hari sebelum praktikum dimulai yang bersangkutan dilaksanakan dan atas persetujuan asisten kemudian kedua praktikan tersebut wajib mengisi formulir tukar jadwal yang harus dibawa pada saat melaksanakan praktikum dengan jadwal yang baru dan diserahkan kepada asisten yang menjaga saat itu.

b. Tukar jadwal hanya bisa dilakukan 1 kali sesama praktikan dengan modul yang sama dalam 1 periode praktikum

c. Praktikan dilarang menyusup pada jadwal praktikum yang lain, bila hal tersebut terjadi maka praktikan dianggap gugur pada modul tersebut.

5. PENILAIAN PRAKTIKUM a. Tugas Pendahuluan

Tugas pendahuluan akan dikeluarkan setiap dua minggu sekali oleh Fakultas.

Tugas Pendahuluan bersifat optional untuk dikerjakan. Jika tidak mengerjakan, maka nilai TP = 0. Format penulisan TP : soal-jawaban.

Praktikan yang mengerjakan TP wajib mengerjakan SEMUA soal TP. Jika ada salah satu atau lebih soal TP yang tidak dikerjakan, maka nilai TP=0

.

Tidak boleh masteran. Jika terbukti masteran, maka nilai TP=0.

Tugas Pendahuluan ditulis tangan dalam buku TP sesuai ketentuan yang ditetapkan.

Penulisan Tugas Pendahuluan menggunakan alat tulis bolpoint (pensil tidak boleh), termasuk gambar dan hitungan

Tugas pendahuluan dikeluarkan oleh Fakultas Teknik Elektro pada H-4 pelaksanaan praktikum

Tugas pendahuluan dikumpulkan di Laboratorium Teknik Digital pada hari senin pukul 07.00 - 09.00 WILTD. Jika melebihi waktu yang ditentukan nilai TP sama dengan NOL.

Praktikan yang tidak mengerjakan TP hanya menulis soal maka nilai TP sama dengan NOL. TP bersifat

Optional, tapi jika tidak mengerjakan TP sama dengan NOL.

Tugas pendahuluan dikumpulkan tiap-tiap kelompok secara bersamaan dalam sebuah amplop coklat yang telah diberi nomor kelompok dan stempel Laboratorium Teknik Digital

Praktikan yang tidak mengumpulkan TP kedalam amplop kelompok masing-masing maka nilai TP mendapat diskon 50%

Pengumpulan Tugas Pendahuluan boleh diwakilkan dengan ketentuan apabila TP yang dititipkan ternyata tidak ada maka praktikan yang menitip mendapatkan nilai TP sama dengan NOL .

b. Tes Awal

Tes awal akan dilaksanakan pada saat praktikum.

Waktu untuk mengerjakan tes awal berkisar 15 – 20 menit.

Asisten berhak menentukan sifat Tes Awal (lisan atau tulisan) tanpa memberikan pemberitahuan terlebih dahulu.

Tidak ada penambahan waktu pengerjaan tes awal bagi praktikan yang datang terlambat saat praktikum. c. Jurnal Praktikum

Jurnal diberikan sebelum praktikum.

Jurnal dikerjakan dengan izin asisten yang menjaga saat itu. Jurnal harus dikerjakan seluruhnya.

Jurnal praktikum dikerjakan setelah pelaksanaan praktikum berakhir selama 30 menit dan dikumpulkan pada hari yang sama dengan praktikum modul tersebut.

Praktikan yang tidak mengumpulkan jurnal dianggap gugur pada praktikum modul tersebut. Pengumpulan jurnal harus dilaksanakan di laboratorium dan tidak dapat diwakilkan.

Isi jurnal harus ditulis dengan bolpoin, kecuali untuk gambar dapat menggunakan pensil dan menggunakan penggaris.

d. Tes Akhir

Tes akhir bersifat fleksibel. e. Penilaian

Tugas Pendahuluan : 20 % Tes Awal : 20 %

Praktikum : 40 % Jurnal Praktikum : 20 %

Batas nilai kelulusan minimum 60 % per modul. 6. KELULUSAN PRAKTIKUM

a. Memenuhi semua kelengkapan praktikum (mengikuti semua modul praktikum). b. Nilai akhir suatu mata praktikum dihitung dengan cara :

NMP =

c. Suatu mata praktikum dinyatakan lulus apabila indeks mata praktikum minimal C dan semua mata percobaan/modul pada mata praktikum tersebut lulus.

d. Apabila nilai mata praktikum tidak lulus maka praktikan wajib mengulang semua mata percobaan/modul dalam mata praktikum tersebut.

Jumlah nilai masing – masing modul Jumlah Modul

7. LAIN – LAIN

a. Selama berlangsungnya praktikum, asisten berhak untuk menegur atau mengeluarkan praktikan yang dianggap belum siap mengikuti praktikum.

MODUL I

PENGENALAN IC DAN REALISASI RANGKAIAN KOMBINASIONAL

A. Tujuan Praktikum

a. Mengenal dan memahami macam – macam IC dan alat pendukung lainnya.

b. Memahami metode perancangan rangkaian logika yang dibentuk dari gerbang logika dasar. c. Mengenal dan memahami prinsip kerja decoder, adder, dan multiplexer.

d. Mengetahui dan dapat mengaplikasikan konsep perancangan rangkaian decoder dan multiplexer. e. Mengetahui dan memahami aplikasi rangkaian driver seven segment.

B. Peralatan Praktikum a. Digiboard

b. IC 74LS00, IC 74LS02, IC 74LS04, IC 74LS08, IC 74LS32, IC 74LS138, IC 74LS47, 7-Segment anode/ Cathode C. Pengenalan IC

Intergrated Circuit (IC) adalah suatu komponen elektronik yang terbuat dari bahan semikonduktor, dimana IC merupakan gabungan dari komponen seperti Resistor, Kapasitor, Dioda, dan Transistor yang telah terintegrasi menjadi sebuah rangkaian berbentuk chip kecil. IC digunakan untuk beberapa keperluan pembuatan peralatan elektronik agar mudah dirangkai menjadi peralatan yang berukuran relative kecil.

Pada umumnya, IC gerbang logika dasar memiliki 14 pin, dengan pin 1

ditandai dengan tanda dot atau lekukan setengah lingkaran. Untuk gerbang logika dasar pada pin 14 diberi catuan ke VCC dan pin 7 di-ground-kan. Untuk penomoran IC, pin 2,3,4, dan seterusnya berurutan berlawanan arah jarum jam.

Dalam praktikum, yang akan digunakan adalah IC TTL (Transistor-Transistor Logic). IC TTL bekerja pada supply tegangan 5V. Berikut adalah teknik penomoran atau penamaan IC untuk tipe TTL:

Keterangan :

A = SN = Perusahaan atau Pabrik Pembuat IC B = 74 = Kelompok IC

C = LS = Sub Family IC D = 08 = Tipe dari chip E = N = Kemasan

(T untuk rangkap dua jalur keramik dan untuk bahan metal datar. N untuk rangkap dua jalur egativ). D. Perancangan Rangkaian

a. Penyederhanaan

Penyederhanaan dilakukan untuk penghematan ruang kerja dan biaya. Penyederhanaan dapat dilakukan dengan banyak metode, diantaranya K-Map dan Aljabar Boolean.

Aljabar Boolean

Penyederhanaan dengan aljabar Boolean dilakukan berdasarkan hokum Aljabar Boolean. Berikut adalah Hukum Aljabar Boolean:

Pada dasarnya ada dua bentuk standar fungsi Boolean, yaitu: 1. Sum of Product (SOP) / Sum of Minterm

2. Product of Sum (POS) / Product of Maxterm NOT Law

0 = 1̅ 1 = 0̅ X = x̅̅

AND Law OR Law x . 0 = 0 x + 0 = x x . 1 = x x + 1 = 1 x . x = x x + x = x x . x = 0̅ x + x = 1̅

Commutative Law Associative Law Absorptive Law x . y . z = y . z . x = z . x . y (x . y) . z = x . (y . z) = x . y . z x . (x + y) = x . y x + y + z = y + z + x = z + y + x (x + y) + z = x + (y + z) = x + y + z x + (x . y) = x + y Distributive Law De Morgan Law

x . y + x . z = x . (y + z) (x + y) ‘ = x̅ . y̅ (x + y) . (x + z) = x + (y . z) (x . y) ‘ = x̅ + y̅

Pada modul ini, kita hanya akan mempelajari tentang Sum of Product / Sum of Minterm.

Sum of Product / Minterm

Minterm adalah suatu kondisi dimana semua egative dari suatu fungsi yang di-AND, serta egative tersebut bias dalam kondisi komplemen atau tidak.

Contoh :

F(a,b,c,d) adalah sebuah fungsi dengan 4 variabel (a,b,c,d) a.b’.c’.d adalah salah satu dari 24 minterm fungsi F.

Ciri-ciri dari SOP adalah:

1. Dalam setiap suku operasi variabelnya adalah perkalian (operasi AND). 2. Setiap suku (term) dijumlahkan (operasi OR).

3. Setiap suku mengandung semua egative. Contoh:

f(x,y) = xy + x’y

g(x,y,z) = x’yz + xyz + x’y’z’ Cara membaca:

Variabel tanpa komplemen dianggap bernilai 1. Variabel dengan komplemen dibaca 0.

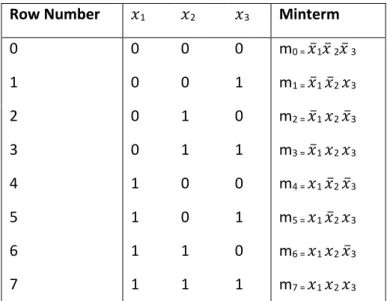

Row Number 𝑥1 𝑥2 𝑥3 Minterm

0 0 0 0 m0 = 𝑥̅1𝑥̅ 2𝑥̅ 3 1 0 0 1 m1 = 𝑥̅1 𝑥̅2 𝑥3 2 0 1 0 m2 = 𝑥̅1 𝑥2 𝑥̅3 3 0 1 1 m3 = 𝑥̅1 𝑥2 𝑥3 4 1 0 0 m4 = 𝑥1 𝑥̅2 𝑥̅3 5 1 0 1 m5 = 𝑥1 𝑥̅2 𝑥3 6 1 1 0 m6 = 𝑥1 𝑥2 𝑥̅3 7 1 1 1 m7 = 𝑥1 𝑥2 𝑥3

K – Map

Karnaugh Map (disingkat K-map) adalah sebuah peralatan grafis yang digunakan untuk menyederhanakan persamaan logika atau mengkonversikan sebuah Tabel Kebenaran menjadi sebuah rangkaian Logika.Blok diagram sebuah K-map seperti gambar di bawah ini. AB dan C adalah egative input, output-output berupa minterm-minterm bernilai 1 diisikan pada sel K-map. Jumlah sel K-map adalah 2jumlah variable input.

F = ………

Contoh SOP pada K – Map disamping : m0 = A̅B̅C̅

m5 = AB̅C

F = B̅C + A̅BC̅

Rangkaian Pengganti

Sistem ini dilakukan ini dilakukan karena adanya keterbatasan bahan.Tidak semua IC tersedia di pasaran. Jadi kita dapat memanfaatkan gerbang-gerbang logika yang ada untuk membentuk gerbang yang lainnya. Sebagai contoh gerbang NOR dapat dibuat dari gerbang OR yang outputnya diberi gerbang NOT.

BC

A

00 01 11 10

0

m

0m

1m

3m

21

m

4m

5m

7m

6BC

A

00 01 11 10

0 0

1

0

1

1 0

1

0

0

Gerbang Logika Dasar

Setiap gerbang logika dasar memiliki tabel kebenaran tersendiri yang memberikan karakteristik tertentu. Pada dasarnya hanya terdapat tiga gerbang logika dasar, yaitu gerbang AND, OR, dan NOT. Dari ketiga gerbang tersebutlah dikembangkan menjadi gerbang NAND, NOR, XOR, dan XAND.

A B Y A B Y A B Y 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 1 1 1 0 0 1 0 0 1 0 1 1 1 1 1 1 0 1 1 0 A B Y A B Y A B Y 0 0 0 0 0 1 0 0 1 0 1 1 0 1 0 0 1 0 1 0 1 1 0 0 1 0 0 1 1 1 1 1 0 1 1 1

AND (7408) NAND (7400) XOR (7486)

OR (7432) NOR (7402) XNOR A . B = Y (A . B)' = Y A B = Y A + B = Y (A + B)' = Y A B = Y A Y 0 1 1 0 NOT (7404) A = A̅ E. Rangkaian Kombinasional

Rangkaian Kombinasional adalah rangkaian yang terdiri dari rangkain gerbang logika yang kondisi keluarannya (output) hanya tergantung oleh kondisi masukan (input) saat itu dan tidak tergantung pada kondisi output sebelumnya.

Rangkaian kombinasional tidak memiliki memori sebagai media penyimpanan, seperti: decoder, priority encoder, multiplexer, adder, subtractor, multiplier, divider dan lain sebagainya.

F. Kegunaan Rangkaian Kombinasional

Untuk beberapa keperluan pembuatan peralatan elektronik yang membutuhkan rangkaian kombinasional dengan sifat tertentu. Misalnya multiplexer yang dapat memilih bit select untuk memilih input yang akan diteruskan ke output, sehingga multiplexer banyak digunakan pada perangkat telekomunikasi.

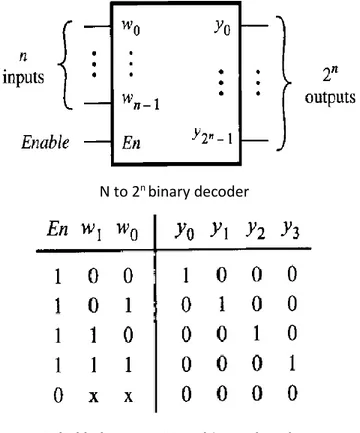

1. Decoder

Rangkaian decoder merupakan rangkaian kombinasional yang berfungsi untuk mendekode informasi (data) yang terkode. Salah satu contoh decoder adalah binary decoder.

Karakteristik Binary Decoder :

a. Mempunyai N masukan data dan 2N keluaran.

Misal : binary decoder 3 masukan mempunyai 8 jalur keluaran.

b. Hanya satu keluaran yang diaktifkan dalam satu waktu (one-hot encoded).

Assert : ke nilai ‘1’ (logika positif / output active-high) atau ‘0’ (logika egative / output active-low). Tiap keluaran diaktifkan oleh satu kombinasi nilai masukan.

c. Masukan ENABLE (En) digunakan untuk mematikan keluaran. Asumsi keluaran active-high, enable active-high :

Jika En = 0, tidak ada keluaran decoder yang di-assert (diaktifkan).

Jika En = 1, satu keluaran di-assert (diaktifkan) sesuai kombinasi masukan.

N to 2n binary decoder

Tabel kebenaran 2 to 4 binary decoder dengan enable active-high dan output active-high

Logic Circuit

2. Aplikasi decoder Pada 7 Segment

Contoh lain dari decoder adalah BCD-to-7-Segment decoder. Dekoder tersebut dapat merubah BCD digit pada input menjadi informasi (7 bit) yang sesuai untuk mengaktifkan digit-oriented display atau 7-segment. BCD-to-7-Segment dekoder dapat diimplementasikan menjadi driver seven 7-segment.

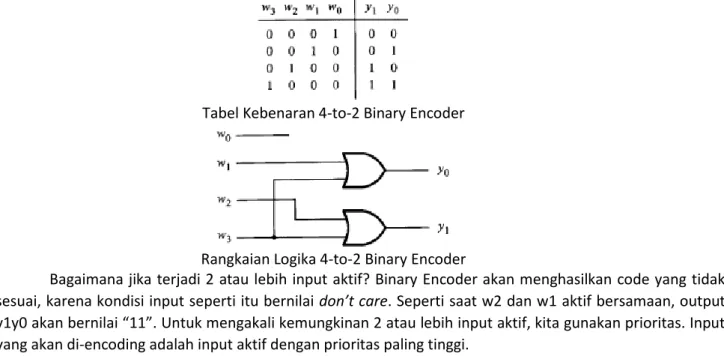

3. Encoder

Encoder memiliki fungsi kebalikan dari decoder, yaitu merubah suatu informasi ke kode tertentu. Salah satu contohnya Binary Encoder yang merubah satu input yang aktif menjadi kombinasi output unik untuk setiap input. Binary Encoder hanya bisa melayani 1 input aktif.

Tabel Kebenaran 4-to-2 Binary Encoder

Rangkaian Logika 4-to-2 Binary Encoder

Bagaimana jika terjadi 2 atau lebih input aktif? Binary Encoder akan menghasilkan code yang tidak sesuai, karena kondisi input seperti itu bernilai don’t care. Seperti saat w2 dan w1 aktif bersamaan, output y1y0 akan bernilai “11”. Untuk mengakali kemungkinan 2 atau lebih input aktif, kita gunakan prioritas. Input yang akan di-encoding adalah input aktif dengan prioritas paling tinggi.

Tabel Kebenaran 4-to-2 Binary Encoder with Priority

Fungsi Output

Dengan prioritas input, saat w2 dan w1 aktif bersamaan, w2 akan di-encoding menjadi y1y0 bernilai “10”. Z adalah sinyal yang menunjukkan bahwa minimal 1 input aktif.

4. Multiplexer

Multiplexer adalah suatu rangkaian kombinasional yang fungsinya untuk memilih salah satu dari 2n bit

sinyal input untuk diteruskan ke satu jalur output. Multiplexer disebut juga sebagai data selector, karena memiliki bit select sebanyak n yang berfungsi untuk memilih data dan sebagai pengontrol input. Multiplexer ini banyak digunakan dalam bidang telekomunikasi.

Contoh implementasi multiplexer:

Multiplexer 4-to-1

Simbol mux 4-to-1 Tabel kebenaran

Rangkaian Logika mux 4-to-1 5. Half Adder dan Full Adder

Kedua rangkaian ini merupakan contoh rangkaian aritmatika dasar yang sama-sama berfungsi menjumlahkan bilangan. Half Adder merupakan rangkaian yang menjumlahkan 2 bilangan yang masing-masing selebar 1 bit dan menghasilkan 1 bilangan selebar 2 bit, sedangkan Full Adder menjumlahkan 3 bilangan selebar 1 bit dan tetap menghasilkan 1 bilangan selebar 2 bit. Seperti penjumlahan bilangan satuan yang menghasilkan bilangan puluhan.

a. Half Adder A B C S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 INPUT OUTPUT

Dari tabel kebenaran diatas, dapat disederhanakan bahwa Sum dan Carry berasal dari dua persamaan berikut :

b. Full Adder

Pada Full Adder, rangkaian dapat bekerja dengan menampung carry sebelumnya sehingga inputnya ada 3, yaitu A, B, dan Cin.

A B Cin Cout S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 INPUT OUTPUT S = A B Cin Cout = ((A B) . Cin) + (A . B) = (A . B) + (B . Cin) + (Cin . A)

Jika diperhatikan, operasi pada full adder dapat direpresentasikan dengan menggunakan half adder sesuai dengan gambar berikut :

Sedangkan untuk melakukan operasi penjumlahan bilangan dengan lebar data lebih dari satu bit dibutuhkan sebuah rangkaian Full Adder Parallel. Full Adder Parallel tersusun atas rangkaian Full Adder sebanyak n yang dapat menjumlahkan 2 bilangan selebar n bit dan menghasilkan 1 bilangan selebar n+1 bit. Seperti penjumlahan bilangan ratusan yang menghasilkan bilangan ribuan. Rangkaian ini mempunyai prinsip menggunakan cout pada perhitungan bit sebelumnya menjadi cin.

6. Half Subtractor dan Full Subtractor

Kedua rangkaian ini melakukan operasi pengurangan biner. Half subtractor untuk pengurangan 2 bilangan selebar 1 bit menghasilkan sebuah bilangan selebar 2 bit, sedangkan full subtractor untuk pengurangan 3 bilangan selebar 1 bit menghasilkan sebuah bilangan selebar 2 bit. Dalam hal ini, Full Subtractor dapat terdiri dari 2 Half Subtractor.

a. Half Subtractor A B Bout D 0 0 0 0 0 1 1 1 1 0 0 1 1 1 0 0 INPUT OUTPUT D = A B Bout = A̅ . B = A – B b. Full Subtractor A B Bin Bout D 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 INPUT OUTPUT D = A B Bin C = ((A B)’ . Bin) + (A̅ . B)

Seperti halnya pada full adder 1 bit yang terdiri dari 2 buah half adder, pada rangkaian full subtractor 1 bit juga terdiri dari 2 buah half subtractor.

G. Langkah Praktikum

a. Gerbang Logika dan IC Dasar

GERBANG AND (74LS08)

GERBANG NOT (74LS04)

GERBANG NAND (74LS00)

1) Siapkan peralatan praktikum 2) Tempatkan IC di Digiboard

3) Hubungkan Input 1 (Kaki 1; Kaki 2 pada 74LS02) ke salah satu input toggle switch di Digiboard 4) Hubungkan Input 2 (Kaki 2; Kaki 3 pada 74LS02) ke salah satu input toggle switch di Digiboard 5) Hubungkan Output (Kaki 3; Kaki 1 pada 74LS02) ke salah satu pin LED di Digiboard

6) Hubungkan VCC dengan sumber tegangan di Digiboard 7) Hubungkan GND dengan grounding di Digiboard

8) Ubah input dengan toggle switch sesuai dengan jurnal, catat outputnya. 9) Ulangi langkah 2 – 6 diatas untuk semua IC

a. Rangkaian Kombinasional

1) Siapkan peralatan praktikum 2) Tempatkan IC di Digiboard

3) Hubungkan kaki 1(A) dan 2(B) ke input toggle switch Digiboard, kaki 3(C) di-ground-kan atau diberi input 0 karena tidak digunakan

4) Kaki 4(G2A) dan 5(G2B) di paralel, kemudian dihubungkan dengan input toggle switch Digiboard 5) Kaki 6(G1) dihubungkan dengan salah satu input toggle switch Digiboard

6) Kaki 15(Y0) sampai kaki 12(Y3) masing-masing dihubungkan ke output LED Digiboard 7) Kaki 16(VCC) dihubungkan dengan sumber VCC Digiboard

8) Kaki 8(GND) dihubungkan dengan grounding Digiboard

9) Agar bekerja, Enable G2 (G2A dan G2B) harus 0 sedangkan G1 harus bernilai 1 10) Ubah input sesuai dengan jurnal kemudian catat outputnya

BCD to 7-Segment Decoder

1) Siapkan peralatan praktikum

2) Tempatkan IC dan Seven Segment di Digiboard

3) Hubungkan kaki 7(A), 1(B), 2(C), 6(D) dengan input toggle switch Digiboard 4) Hubungkan kaki 3(LT) dan 5(RBI) dengan VCC agar selalu bernilai 1

5) Hubungkan kaki 4(RBO) dengan ground atau salah satu input tetapi diberi masukan 0 6) Kaki 9 sampai 15 dihubungkan ke Seven Segment sesuai dengan huruf nya masing-masing 7) Kaki 16(VCC) dihubungkan ke sumber tegangan Digiboard

8) Kaki 8(GND) dihubungkan ke grounding Digiboard

9) Kaki Common (Gnd atau Vcc) pada Seven Segment dihubungkan ke Vcc atau Ground sesuai dengan tipe Seven Segment yang digunakan, Anoda atau Katoda

MODUL II

FLIP – FLOP DAN RANGKAIAN SEKUENSIAL A. Tujuan Praktikum

a. Memahami dasar rangkaian memori.

b. Memahami karakteristik dan fungsi dari flip – flop dan rangkaian sekuensial. c. Memahami perancangan rangkaian sekuensial menggunakan flip – flop. B. Peralatan Praktikum

a. Digiboard

b. IC 74LS74, IC 74LS76 C. Flip – Flop

Flip-flop adalah rangkaian logika yang digunakan untuk menyimpan satu bit secara semi permanen sampai ada suatu perintah untuk menghapus atau mengganti isi dari bit yang disimpan. Flip-flop bekerja berdasarkan control dari sinyal clock. Prinsip dasar dari flip-flop adalah suatu komponen elektronika dasar seperti transistor, resistor dan dioda yang di rangkai menjadi suatu gerbang logika yang dapat bekerja secara sekuensial.

Flip-flop merupakan bentuk dasar dari rangkaian logika sekuensial. Pada dasarnya flip-flop berasal dari basic cell NAND atau basic cell NOR, yang sering disebut RS-flip-flop (SET RESET flip-flop). Berikut gambar rangkaian, dan table kebenaran dari RS flip-flop:

S R Q Q̅ 0 0 NC NC 0 1 0 1 1 0 1 0 1 1 0 0 Invalid Condition INPUT OUTPUT COMMENT No Chance, Hold Reset Set S R Q Q̅ 1 1 NC NC 0 1 1 0 1 0 0 1 0 0 1 1 Invalid Condition INPUT OUTPUT COMMENT No Chance, Hold Set Reset

Tidak seperti gerbang logika, flip-flop mempunyai dua keluaran komplementer. Keluaran tersebut diberi lambang Q dan𝑄̅. Keluaran Q merupakan keluaran normal dan paling sering digunakan pada kondisi normal dan 𝑄̅ merupakan komplemen dari Q.

MODE OPERASI FLIP – FLOP Qt → Qt+1 0 → 0 1 → 0 0 → 1 1 → 1 0 → 1 1 → 0 0 → 0 1 → 1 Mode Operasi Reset Set Toggle Hold

D. Macam Macam Flip – Flop a. Data Flip – Flop (D – FF)

D-FF adalah sebuah flip-flop yang memiliki satu data input dimana operasi dari flip-flop ini dikontrol oleh sebuah sinyal clock, sehingga saat clock aktif terus tanpa mengalami perubahan logic level maka noise logic dapat terkunci dan diteruskan ke output next state. D-FF disusun dengan menambahkan gerbang NOT antara masukkan S dan R.

Qt adalah present state, atau kondisi flip-flop sebelum clock aktif.

b. Universal Flip – Flop (JK – FF)

JK-FF memliki dua input yang mempengaruhi keluaran. Operasi flop JK sama dengan operasi flip-flop SR, kecuali pada masukkan, JK diperbolehkan kondisi J=K=1. Bila kondisi seperti itu maka keadaan Q akan berubah tanpa memperhatikan keadaan Q sebelum ada detak. Sifat master slave terlihat pada output table operasi yang selalu sama dengan masternya (J ).

c. Toggle Flip – Flop (T – FF)

T-FF mempunyai sifat “Toggle”, artinya saat input T = 1 maka output = complement output sebelum clock aktif. karena output selalu berlawanan dengan kondisi awalnya, sehingga saat Clock aktif terus dan input T=1 maka output akan berosilasi.

T Q 0 Hold 1 Toggle Qt → Qt+1 T 0 → 0 0 0 → 1 1 1 → 0 1 1 → 1 0

E. Merancang Flip – Flop dari Flip – Flop Lain

Suatu Flip–Flop dengan karakteristik yang tidak umum, tetap dapat diimplementasikan dalam rangkaian. Flip-flop tersebut dibuat dengan memanfaatkan Flip-flop yang ada. Langkah-langkah perancangan Flip-Flip-flop dari flip-flop lain adalah sebagai berikut:

Misal : Merancang T-FF dari JK-FF a. Buatlah tabel operasi T – FF

T Q

0 Hold 1 Toggle

b. Definisikan mode operasi pada T – FF

T Q

0 Hold 1 Toggle

c. Bandingkan dengan tabel operasi JK – FF dengan mode operasi yang sama

T Q 0 Hold 1 Toggle J K Q 0 0 Hold 0 1 Reset 1 0 Set 1 1 Toggle Q T J K Hold 0 0 0 Toggle 1 1 1

Dari tabel persamaan mode operasi antara T – FF dan JK – FF diatas, didapatkan persamaan sebagai berikut : T = J

T = K

d. Buatlah rangkaian penggantinya

F. Clock

Clock adalah sinyal pewaktu yang akan memicu rangkaian untuk aktif. Kondisi clock yang memicu rangkaian dibagi 4, yaitu:

a. Rising Edge Trigger (RET)

Clock akan aktif saat terjadi transisi dari bit 0 ke bit 1 (0 → 1). b. Falling Edge Trigger (FET)

Clock akan aktif saat terjadi transisi dari bit 1 ke bit 0 (1 → 0). c. Positive Pulse Trigger (PPT)

Kondisi aktif clock dibaca saat rising (0 → 1), tapi ditulis saat falling (1 → 0). d. Negative Pulse Trigger (NPT)

G. Rangkaian Sekuensial

Rangkaian sekuensial adalah rangkaian logika yang outputnya dipengaruhi oleh input saat ini dan output sebelumnya. Rangkaian sekuensial dapat dikatakan pula sebagai rangkaian logika yang bekerja berdasarkan urutan waktu. Ciri dari sistem rangkaian logika sekuensial adalah adanya jalur umpan balik (feedback) di dalam rangkaiannya. Adapun contoh dari rangkaian sekuensial yaitu flipflop, counter, register, dan detector sekuensial.

a. Counter

Counter merupakan rangkaian logika pengurut, karena counter membutuhkan karakteristik memori,

dan pewaktu memegang peranan yang penting. Counter digital mempunyai karakteristik penting yaitu sebagai berikut:

• Jumlah hitungan maksimum (modulus N – counter).

• Menghitung keatas atau kebawah (up atau down – counter). • Operasi asinkron atau sinkron.

• Bergerak bebas atau berhenti sendiri.

Sebagaimana dengan rangkaian sekuensial yang lain, untuk menyusun counter digunakan flip-flop.

Counter dapat digunakan untuk menghitung banyaknya clock-pulsa dalam waktu yang tersedia (pengukuran

frekuensi), Counter dapat juga digunakan untuk membagi frekuensi dan menyimpan data.

Ada dua macam counter, yaitu Asinkronous Counter dan Sinkronous Counter. Asinkronous Counter disebut juga Ripple Through Counter atau Counter Serial (Serial Counter), karena output masing-masing

flip-flop yang digunakan akan berubah kondisi dari “0” ke “1” dan sebaliknya secara berurutan, hal ini disebabkan

karena flip-flop yang paling ujung dikendalikan oleh sinyal clock, sedangkan sinyal clock untuk flip-flop lainnya berasal dari masing-masing flip-flop sebelumnya. Sedangkan pada counter sinkron, output flip-flop yang digunakan bergantian secara serempak. Hal ini disebabkan karena masing-masing flip-flop tersebut dikendalikan secara serempak oleh sinyal clock. Oleh karena itu Counter Sinkron dapat pula disebut sebagai

Contoh Perancangan Counter Up-Down 2-bit D-FF 1. Buat Diagram State Counter 2-Bit yang dirancang

2. Buat Table State

3. Tentukan persamaan logika D1 dan D2 dengan K-MAP

4. Buat Rangkaian Counter tersebut

b. Shift Register

Register merupakan sekelompok flip-flop yang dapat menyimpan dan menggeser data yang terdiri dari bit majemuk. Register dengan n flip-flop mampu menyimpan sebesar n bit. Ada dua cara untuk menyimpan dan membaca data ke dalam register, yaitu seri dan paralel. Dalam operasi paralel, penyimpanan atau pembacaan dilakukan secara serentak oleh semua tingkat register dan hanya membutuhkan 1 clock saja untuk menyimpan atau membaca semua data. Sedangkan untuk operasi seri, diterapkan secara sequential bit demi bit sampai semua tingkat register terpenuhi dan jumlah clock tergantung pada jumlah data yang akan disimpan.

Ada 4 mode operasi register : i. Serial In Serial Out (SISO)

ii. Serial In Parallel Out (SIPO)

Pada mode ini, data masuk secara seri (berurutan) dan keluar secara paralel (serentak).

iii. Parallel In Serial Out (PISO)

Pada mode ini, data masuk secara paralel (serentak) dan keluar secara seri (berurutan).

iv. Parallel In Parallel Out (PIPO)

Pada mode ini, data masuk dan keluar secara paralel (serentak).

c. Detektor Sekuensial

Detektor sekuensial merupakan suatu jenis rangkaian sekuensial yang dapat mendeteksi urutan bit dengan pola tertentu dari rangkaian data yang diinputkan. Jika data yang dideteksi sesuai dengan pola yang diinginkan, maka output akan mengeluarkan suatu harga tertentu.

Ada 2 model dalam perancangan rangkaian detector sekuensial, yaitu model moore dan model mealy. Perbedaan antara keduanya adalah pada jumlah state dan variable pembentuk outputnya:

i. Model Mealy

Model Mealy → Jumlah State = Jumlah Bit

Contoh : Perancangan detektor sekuensial dengan urutan bit 011 menggunakan model mealy. Flip – flop yang digunakan adalah D – FF.

Untuk mendeteksi urutan 011 ada 3 state yang dilewati yaitu : • State A , yaitu ketika detektor belum mendeteksi apa-apa • State B , yaitu ketika detektor mendeteksi 0

• State C , yaitu ketika detektor mendeteksi 0 1

Lalu nilai keluaran Z akan bernilai 1 ketika detektor berada pada state C dan mendapat input bernilai 1 sehingga detektor mendeteksi 011, lalu dapat dibuat diagram state nya seperti dibawah ini :

Dari diagram state diatas lalu kita buat tabel state-nya.

X = 0 X = 1 X = 0 X = 1

A B A 0 0

B B C 0 0

C B A 0 1

PS NS Z

Kondisi state dapat direpresentasikan sebagai berikut : A = 00

B = 01 C = 11

Maka, tabel state akan menjadi seperti ini :

X = 0 X = 1 X = 0 X = 1

00 01 00 0 0

01 01 11 0 0

11 01 00 0 1

PS NS Z

Untuk mencari nilai input pada rangkaian detector (input masing – masing flip – flop), dibutuhkan tabel transisi sesuai flip – flop yang digunakan, karena pada contoh ini memakai D – FF, maka yang digunakan adalah tabel transisi milik D – FF.

Qt → Qt+1 D

0 → 0 0

0 → 1 1

1 → 0 0

1 → 1 1

Dengan melihat kondisi present state (PS) dan next state (NS) lalu dihubungkan dengan tabel transisi, maka diperoleh tabel eksitasi sebagai berikut :

Q1 Q2 Q1 Q2 Q1 Q2 D1 D2 D1 D2 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 1 1 0 1 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 Z PS NS X = 0 X = 1 X = 0 D X = 1 X = 0 X = 1

Dengan melihat tabel eksitasi, kita dapat mencari persamaan input di masing – masing flip – flop, karena pada rangkaian detektor sekuensial yang kita buat ini menggunakan 2 flip – flop, maka ada 2 persamaan input dan sebuah persamaan output.

x Q1 Q2 0 1 0 0 0 0 0 1 0 1 1 1 0 0 1 0 X X D1 = Q͞1 . Q2 . X x Q1 Q2 0 1 0 0 1 0 0 1 1 1 1 1 1 0 1 0 X X D2 = X̅ + Q͞1 . Q2 x Q1 Q2 0 1 0 0 0 0 0 1 0 0 1 1 0 1 1 0 X X Z = Q1 . X

Dengan menggunakan persamaan input dan output yang telah didapat, maka gambar rangkaian detektor sekuensialnya adalah :

ii. Model Moore

Model Moore → Jumlah State = Jumlah Bit + 1

Contoh : Perancangan detektor sekuensial dengan urutan bit 011 menggunakan model moore. Flip – flop yang digunakan adalah D – FF.

Untuk mendeteksi urutan 011 ada 4 state yang dilewati yaitu : • State A , yaitu ketika detektor belum mendeteksi apa-apa

• State B , yaitu ketika detektor mendeteksi 0 dengan nilai output 0 • State C , yaitu ketika detektor mendeteksi 0 1 dengan nilai output 0 • State D , yaitu ketika detektor mendeteksi 0 1 1 dengan nilai output 1

Nilai output telah didefinisikan pada masing – masing state, maka bentuk state diagram-nya adalah :

Dari diagram state diatas lalu kita buat tabel state-nya.

X = 0 X = 1 A B A 0 B B C 0 C B D 0 D B A 1 PS NS Z

Kondisi state dapat direpresentasikan sebagai berikut : A = 00

B = 01 C = 11 D = 10

X = 0 X = 1 00 01 00 0 01 01 11 0 11 01 10 0 10 01 00 1 PS NS Z

Untuk mencari nilai input pada rangkaian detector (input masing – masing flip – flop), dibutuhkan tabel transisi sesuai flip – flop yang digunakan, karena pada contoh ini memakai D – FF, maka yang digunakan adalah tabel transisi milik D – FF.

Qt → Qt+1 D

0 → 0 0

0 → 1 1

1 → 0 0

1 → 1 1

Dengan melihat kondisi present state (PS) dan next state (NS) lalu dihubungkan dengan tabel transisi, maka diperoleh tabel eksitasi sebagai berikut :

Q1 Q2 Q1 Q2 Q1 Q2 D1 D2 D1 D2 0 0 0 1 0 0 0 1 0 0 0 0 1 0 1 1 1 0 1 1 1 0 1 1 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 0 0 1 PS NS X = 0 X = 1 X = 0 D X = 1 Z

Dengan melihat tabel eksitasi, kita dapat mencari persamaan input di masing – masing flip – flop, karena pada rangkaian detektor sekuensial yang kita buat ini menggunakan 2 flip – flop, maka ada 2 persamaan input dan sebuah persamaan output.

x Q1 Q2 0 1 0 0 0 0 0 1 0 1 1 1 0 1 1 0 0 0 D1 = Q2 . X x Q1 Q2 0 1 0 0 1 0 0 1 1 1 1 1 1 0 1 0 1 0 D2 = X̅ + Q͞1 . Q2 x Q1 Q2 0 1 0 0 0 0 0 1 0 0 1 1 0 0 1 0 1 1 Z = Q1 . Q͞2

Dengan menggunakan persamaan input dan output yang telah didapat, maka gambar rangkaian detektor sekuensialnya adalah :

H. Langkah Praktikum a. FLIP FLOP

D-FF

1) Siapkan peralatan praktikum 2) Tempatkan IC di Digiboard

3) Hubungkan kaki 1(1CLEAR) ke input toggle switch 4) Hubungkan kaki 2(1D) ke input toggle switch

5) Hubungkan kaki 3(CLOCK) ke sumber Clock Digiboard 6) Hubungkan kaki 4(PRESET) ke input toggle switch 7) Hubungkan kaki 5(1Q) ke output LED Digiboard

8) Hubungkan kaki 14(VCC) ke sumber tegangan di Digiboard 9) Hubungkan kaki 7(GND) ke sumber ground di Digiboard 10) Ubah input sesuai dengan jurnal, catat outputnya JK-FF

1) Siapkan peralatan praktikum 2) Tempatkan IC di Digiboard

3) Hubungkan kaki 1(1CK) ke sumber Clock Digiboard 4) Hubungkan kaki 2(1PR) ke input toggle switch

5) Hubungkan kaki 3(CLR) ke input toggle switch 6) Hubungkan kaki 4(1J) ke input toggle switch 7) Hubungkan kaki 16(1K) ke input toggle switch 8) Hubungkan kaki 15(1Q) ke output LED Digiboard

9) Hubungkan kaki 5(VCC) ke sumber tegangan di Digiboard 10) Hubungkan kaki 13(GND) ke sumber ground di Digiboard 11) Ubah input sesuai dengan jurnal, catat outputnya b. SHIFT REGISTER

1) Siapkan peralatan praktikum

2) Rangkailah peralatan praktikum seperti rangkaian diatas 3) Ubah input sesuai dengan jurnal, catat outputnya

MODUL III

SINTESIS RANCANGAN RANGKAIAN LOGIKA MENGGUNAKAN VHDL A. Tujuan Praktikum

a. Memperkenalkan penggunaan VHDL dalam perancangan rangkaian digital. b. Memperkenalkan penggunaan software Quartus.

c. Mengenal dan memahami prinsip kerja rangkaian aritmatika dasar yaitu adder, subtractor, divider dan multiplier dalam VHDL.

B. Peralatan Praktikum a. Personal Computer

b. Software Quartus II version 12.1 C. Pengenalan VHDL

Very High-Speed Integrated Circuit Hardware Description Language(VHDL) adalah salah satu bahasa pemrograman yang digunakan untuk memodelkan sistem digital dengan pemodelan dataflow, behavioral dan struktural serta menggabungkan sinyal sistem sama seperti FPGA dan Integrated Circuit(IC). Dalam perancangan rangkaian dengan menggunakan VHDL, sering digunakan software Modelsim atau Quartus untuk simulasi dan sintesis.

Keuntungan perancangan menggunakan VHDL adalah:

• Mampu mendesain hardware sampai level tertinggi ( sistem yang kompleks ). • mendukung metodologi top-down dan bottom-up.

• testbench dapat dituliskan menggunakan bahasa ini. • tipe data baru dapat dideklarasikan.

• Dapat mencari dan mendeteksi kesalahan dengan lebih mudah dalam simulasi.

• Proses implementasi program independen sehingga memungkinkan untuk melakukan beberapa perubahan sampai menit – menit terakhir.

• Hardware untuk implementasi sangat flexibel, sehingga dapat digunakan untuk berbagai perancangan dan dapat dipilih sesuai kebutuhan.

• Bahasa pemrograman mudah dimengerti dan dipelajari dengan cepat.

Dua aplikasi utama dari VHDL adalah pada FPGA (Field Programmable Gate Arrays) dan ASIC (Aplication Specific Integrated Circuits). Namun yang akan kita gunakan dalam praktikum Tekdig adalah pengaplikasian pada FPGA. Ketika code VHDL telah ditulis, kita bisa mengimplementasikan rangkaian yang telah kita buat melalui FPGA atau langsung dipabrikasi menjadi ASIC chip.

VHDL berbeda dengan program computer pada umumnya yang berjalan sequential (berurut), statement yang ada dieksekusi secara pararel (bersamaan). Karena itu VHDL biasanya disebut sebagai code dibandingkan program.

Susunan dasar program VHDL

a. Library

Library merupakan kumpulan modul-modul perintah yang digunakan dalam program. Sebelum

digunakan di dalam program, modul yang berada di dalam library perlu diinisialisasi terlebih dahulu. Jika tidak diinisialisasi terlebih dahulu, perintah-perintah yang tertulis tidak dapat dijalankan.

LIBRARY nama_library;

USE nama_library.package_name.package_parts; b. Entity

Spesikfikasi pin input dan output pada desain bentuk rangkaian yang dibuat. Berfungsi untuk menggambarkan port pada input ataupun output pada rangkain yang ingin dibuat, entity juga dapat berisi parameter yang akan digunakan di dalam desain.

ENTITY nama_entity IS PORT ( nama_port :mode_sinyaltipe_sinyal; nama_port :mode_sinyaltipe_sinyal; ...); END nama_entity; c. Architecture

Architecture merupakan deskripsi kerja dari system / entity yang akan kita rancang. Pada architecture

terdapat satu set komponen yang saling berhubungan. Dalam pendeskripsiannya, architecture dapat di desain secara behaviour ( secara perinsip kerja alat ), structural (terstuktur dalam port map), dataflow (RTL : Register

Transfer Level, yaitu secara rangkaian logika) ataupun campuran ketiga cara tersebut.

ARCHITECTURE myarch OF nand_gate IS BEGIN x <= a NAND b; END myarch;

LIBRARY

ENTITY

ARCHITECTURE

• Process

Process merupakan bagian dari suatu architecture. Di dalam suatu architecture bisa terdapat satu atau lebih proses yang saling independen ataupun berhubungan. Contoh dari suatu proses:

architecture nama_architecture of nama_entity is signal nama_signal : tipe;

begin proses1 : process begin ... end process; proses2 : process begin ... end process; end nama_architecture; • Signal dan Variabel

Signal dapat dianalogikan sebagai kabel, yang menjadi penghubung antar bagian di dalam sistem yang di desain. Signal dideklarasikan di dalam architecture. Nilai logika dari suatu signal baru berubah setelah seluruh proses dieksekusi. Apabila dalam suatu signal nilainya diubah beberapa kali dalam suatu proses, nilai yang terakhir yang akan dipakai pada eksekusi selanjutnya. Nilai suatu variable langsung berubah, tanpa harus menunggu selesainya suatu proses eksekusi. Variabel hanya dapat dideklarasikan didalam suatu proses. Contoh deklarasi signal dan variabel:

architecture kerja of nama_entity is signal kabel1 : std_logic;

signal bus : std_logic_vector(7 downto 0); begin

proses1 : process variable var1 : std_logic; variable var2 : std_logic; begin

...

• Entity, Architecture dan Signal

Entity adalah jenis port-port yang digunakan di dalam suatu rangkaian. Pada gambar rangkaian

di atas, entity adalah port A,B,C dan D(sebagai input) dan Y (sebagai output). Sedangkan yang dinamakan

Architecture adalah bentuk dari rangkaian di dalamnya. Signal adalah kabel atau connector yang

menghubungkan antar gerbang logika.

• Komponen

Komponen adalah cara untuk partisi kode, menyediakan berbagi kode, dan penggunaan kembali kode tersebut dalam program lain yang lebih komplek. Misalnya, yang biasa digunakan flip-flops,

multiplexers,adders, basic gates. COMPONENT declaration: COMPONENT component_name IS PORT ( port_name :signal_modesignal_type; port_name :signal_modesignal_type; ...); END COMPONENT; COMPONENT instantiation:

• Test Bench

Test bench adalah proses pengujian suatu rancangan rangkaian. Dalam proses perancangan rangkaian, test bench akan menguji design rangkaian apakah sudah sesuai atau belum. Test bench ini dilakukan dengan menggunaan file HDL (berbentuk kode, baik VHDL maupun Verilog). Sehingga berbeda dengan bentuk diagram yang menggunakan gambar sebagai tampilannya, test bench menggunakan kode-kode tulisan sebagai tampilannya.

Test bench biasanya ditulis dengan kode bahasa VHDL maupun Verilog. Bentuk test bench ini terbilang lebih sukar dibandingkan dengan bentuk timing diagram. Hal ini disebabkan karena untuk melakukan test bench, diperlukan kemampuan untuk menulis dan mengerti kode-kode VHDL maupun verilog. Sehingga bentuk test bench pada umumnya sering dipakai oleh pengguna FPGA tingkat mahir. VHDL Test Bench File: myadder_tb.vhd

library IEEE;

use IEEE.std_logic_1164.ALL; ENTITY myadder_tb is END myadder_tb;

ARCHITECTURE simulate OF myadder_tb IS ---

--- The parent design, myadder8_top, is instantiated --- in this testbench. Note the component

--- declaration and the instantiation. --- COMPONENT myadder8_top PORT ( AP : IN std_logic_vector(7 downto 0); BP : IN std_logic_vector(7 downto 0); CLKP: IN std_logic ; C_INP: IN std_logic;

QP: OUT std_logic_VECTOR (8 downto 0)); END COMPONENT;

SIGNAL a_data_input :std_logic_vector(7 DOWNTO 0); SIGNAL b_data_input :std_logic_vector(7 DOWNTO 0); SIGNAL clock : std_logic;

SIGNAL sum :std_logic_vector (8 DOWNTO 0); BEGIN uut: myadder8_top PORT MAP ( AP =>a_data_input, BP =>b_data_input, CLKP => clock, C_INP=>carry_in, QP => Q); stimulus: PROCESS BEGIN ---

---Provide stimulus in this section. (not shown here) ---

wait;

end process; -- stimulus END simulate;

Contoh – contoh implementasi VHDL: • Sebuah Program AND 3 input

library IEEE;

use IEEE.STD_LOGIC_1164.ALL; entity AND3input is

port (A,B,C : in std_logic; Z : out std_logic);

End AND3input;

Architecture behavioral of AND3input is Begin

Z <= A AND B AND C; End behavioral;

• Program Half Adder library ieee; use ieee.std_logic_1164.all; entity half_adder is port ( a_input : in std_logic; b_input : in std_logic; cout : out std_logic;

sum : out std_logic); End entity half_adder;

Architecture half_adder_bhv of half_adder is Begin

Sum <= a_input xor b_input ; Cout<= a_input and b_input; End half_adder_bhv;

• Implementasi Full Adder dengan component Half Adder library ieee; use ieee.std_logic_1164.all; --nama entity entity full_adder is port ( a_input : in_std_logic; b_input : in std_logic; cin : in std_logic; cout : out std_logic; sum : out std_logic ); --port dari entity end entity full_adder;

--nama architecture --nama entity architecture full_adder_bhv of full_adder is component half_adder is

a_input : in std_logic; b_input : in std_logic; sum : out std_logic; cout : out std_logic);

end component half_adder; signal sum0 : std_logic; signal cout0 : std_logic; signal cout1 : std_logic; begin

FA0 : half_adder

port map (a_input =>a_input , b_input => b_input , sum => sum0 , cout => cout0); FA1 : half_adder

port map (a_input => cin , b_input => sum0 , sum => sum , cout => cout1); cout<= cout0 or cout1;

end full_adder_bhv;

• Implementasi Counter Up- Down 2bit library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Counter_VHDL is

port( Clock: in std_logic; Reset: in std_logic; Updown: in std_logic;

Output: out std_logic_vector(0 to 3) ); end Counter_VHDL;

architecture Behavioral of Counter_VHDL is signal a: std_logic_vector(0 to 3);

begin

begin

if Reset='1' then a <= "0000";

elsif ( Clock'event and Clock='1') then if Updown='0' then a <= a + 1; else a <= a - 1; end if; end if; end process; Output <= a; end Behavioral;

• Shift Register 4-bit Library ieee;

Use ieee.std_logic_1164.all; Entity shift4 is

Port (w, clock : in std_logic; Q : out std_logic_vector (1 to 4)); end shift4;

architecture behavior of shift4 is signal sreg: std_logic_vector (1 to 4); begin

process (clock) begin

if clock ‘event and clock = ‘1’ then sreg (4) <= w;

sreg (3) <= sreg(4); sreg (2) <= sreg (3);

sreg (1) <= sreg (2); end if;

end process; Q <= sreg; End behavior;

• Detektor Sekuensial (mealy 011, D-FF) o D-FF Library IEEE; Use IEEE.STD_LOGIC_1164.ALL; Entity dataFF is Port ( clk, rst, d : in std_logic; q : out std_logic); end dataFF;

architecture behav of dataFF is begin baca : process (clk, rst) begin if (rising_edge (clk)) then if rst = ‘1’ then q <= d; end if; end process; end behav; o Detektor Sekuensial library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity mealy011 is port ( clk, rst, x : in std_logic; z : out std_logic); end mealy011;

architecture behav of mealy011 is component dataFF is

port (

clk, rst, d : in std_logic; q : out std_logic); end component dataFF; signal q1 : std_logic; signal q2 : std_logic; signal d1 : std_logic; signal d2 : std_logic;

begin

DFF1 : dataFF

port map (d => d1, clk => clk, q => q1, rst => rst); DFF2 : dataFF

port map (d => d2, clk => clk, q => q2, rst => rst); d1 <= (not q1) and q2 and x;

d2 <= (not x) or ((not q1) and q2); z <= q1 and x;

end behav; D. Pengenalan Quartus

Software Quartus merupakan salah satu program untuk melakukan proses synthesis dan implementasi desain rangkaian yang telah dibuat dalam VHDL, menjadi file konfigurasi FPGA (*.vhd). Dalam praktikum ini digunakan Quartus II version 12.1.

Sintesis HDL merupakan proses pembangunan rangkaian secara skematik yang tersusun atas gerbang logika atau komponen lain dari suatu rangkaian yang telah dibuat menggunakan bahasa VHDL. Sintesis rangkaian bertujuan untuk memperlihakan bagaimana bentuk rancangan secara skematik dari suatu scipt VHDL.

Setelah script disintesis, barulah rangkaian ini dapat diload ke kit FPGA. Tahapannya dimulai dari perutean pin – pin pada FPGA yang dihubungkan dengan rangkaian digital yang telah dibuat, lalu dilakukan inisiasi tipe FPGA yang dipakai, setelah itu barulah dilakukan load rangkaian digital ke FPGA.

b. Penggunaan Software Quartus 1. Membuat project baru

a) Buat project baru dengan memilih file > New Project Wizard.

c) Pilih tempat penyimpanan project yang ingin dibuat dan tentukan nama project yang ingin dibuat, lalu klik Next.

e) Pilih Cyclone II pada sub menu device family lalu pada sub menu target device pilih Specific device selected in ‘Available device’ list, kemudian pilih device dengan nama EP2C20F484C7 setelah itu klik Next.

g) Klik Finish.

2. Membuat lembar kerja baru

a) Untuk membuat lembar kerja baru pilih file > New…

3. Meng-compile program rangkaian digital a) Contoh hasil pengkodean (Half Adder).

Berikut contoh scriptnya :

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.all;

ENTITY Belajar1 IS

PORT (X1,X2 : INSTD_LOGIC; Y1,Y2 : OUTSTD_LOGIC);

END Belajar1;

ARCHITECTURE LogicFunction OF Belajar1 IS

BEGIN

Y1 <= X1 XOR X2; Y2 <= X1 AND X2;

END LogicFunction;

b) Cari tool pada bagian atas interface software Quartus, lalu klik tool tersebut.

d) Berikut hasil program yang telah berhasil di-compile.

4. Melihat hasil sintesis rangkaian digital

a) Hasil rangkaian dapat dilihat dengan dua metode. Yaitu, Technology Map Viewer dan RTL Viewer. b) Ikuti langkah berikut untuk melihat hasil rangkaian logika dengan Technology Map Viewer.

d) Ikuti langkah berikut untuk melihat hasil rangkaian logika dengan RTL Viewer.

e) Berikut adalah contoh hasil menggunakan RTL Viewer.

5. Melakukan simulasi rangkaian digital a) Klik tools RTL Simulation.

b) Pada bagian library cari sub library work lalu pilih entity file yang sama dengan program sintesis rangkaian yang dibuat.

c) Pada bagian object pilih semua variable yang ada pada rangkaian untuk dimasukkan ke jendela simulasi.

d) Buka jendela simulasi.

e) Pada variable input masukkan nilai yang diinginkan dan ubah selang waktu yang dibutuhkan sesuai keinginan.

E. Prosedur Praktikum a. Program Full Subtractor

1. Buat sebuah program Half Subtractor 2. Simulasikan semua kemungkinan input

3. Buat sebuah program Full Subtractor dari program Half Subtractor yang sebelumnya anda buat 4. Simulasikan semua kemungkinan input

5. Isi Jurnal Praktikum b. Program Multiplier

simulasikan, dan catat hasilnya pada jurnal ! ket : Black box merupakan komponen full adder F. Contoh Program

a. FULL SUBSTRACTOR library IEEE;

use IEEE.STD_LOGIC_1164.ALL; entity FullSubs is

Port ( Borin : in STD_LOGIC; A : in STD_LOGIC; B : in STD_LOGIC; D : out STD_LOGIC;

Borout : out STD_LOGIC); end FullSubs;

architecture Behavioral of FullSubs is component HalfSubs is

port (a_input : in STD_LOGIC; b_input : in STD_LOGIC; bor : out STD_LOGIC; diff : out STD_LOGIC); end component HalfSubs;

signal d0, b0, b1 : std_logic; begin

FA0 : HalfSubs

port map (a_input => A, b_input => B, bor => b0, diff => d0); FA1 : HalfSubs

port map (a_input => Borin, b_input => d0, bor => b1, diff => D); Borout <= b0 or b1; end Behavioral; b. HALF SUBSTRACTOR library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity HalfSubs is

Port ( a_input : in STD_LOGIC; b_input : in STD_LOGIC; bor : out STD_LOGIC; diff : out STD_LOGIC); end HalfSubs;

architecture Behavioral of HalfSubs is begin

bor<= (not(b_input)) and a_input ; diff<= a_input xor b_input;

end Behavioral; c. MULTIPLIER library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Multiply is Port ( A0 : in STD_LOGIC; A1 : in STD_LOGIC; B0 : in STD_LOGIC; B1 : in STD_LOGIC; C0 : out STD_LOGIC; C1 : out STD_LOGIC; C2 : out STD_LOGIC; C3 : out STD_LOGIC); end Multiply;

architecture Behavioral of Multiply is begin

C0 <= A0 and B0;

C1 <= (A0 and B1) xor (A1 and B0);

C2 <= ((A0 and B1) and (A1 and B0)) xor (A1 and B1); C3 <= ((A0 and B1) and (A1 and B0)) and (A1 and B1); end Behavioral;

MODUL IV

SINTESIS RANCANGAN RANGKAIAN MENGGUNAKAN VHDL A. Tujuan Praktikum

a. Dapat memahami arsitektur FPGA.

b. Memperkenalkan FPGA untuk implementasi rangkaian digital yang didesain menggunakan VHDL. c. Melakukan proses sintesis rangkaian digital menggunakan software Quartus.

B. Peralatan Praktikum a. Personal Computer

b. Software Quartus II version 12.1 c. Board DE 1 FPGA

C. Arithmetic Logical Unit (ALU)

Arithmatic Logical Unit (ALU) adalah salah satu bagian/ komponen dalam sistem di dalam sisitem computer yang berfungsi melakukan operasi/ perhitungan aritmatika dan logika, contoh operasi aritmatika adalah operasi penjumlahan dan pengurangan, sedangkan contoh operasi logika adalah logika AND dan OR. ALU bekerja bersama – sama memori, dimana hasil dari perhitungan di dalam ALU disimpan ke dalam memori.

Perhitungan dalam ALU menggunakan kode biner yang merepresentasikan instruksi yang akan dieksekusi (opcode) dan data yang diolah (operand). ALU biasanya menggunakan sistem bilangan biner two’s complement. ALU mendapat data dari register. Kemudian data tersebut diproses dan hasilnya akan disimpan dalam register tersendiri yaitu ALU output register, sebelum disimpan dalam memori.

Pada saat sekarang ini sebuah chip/ IC dapat mempunyai beberapa ALU sekaligus yang memungkinkan untuk melakukan kalkulasi secara paralel. Salah satu chip ALU yang sederhana (terdiri dari 1 buah ALU) adalah IC 74LS382/ HC 382ALU (TTL). IC ini terdiri dari 20 kaki dan beroperasi dengan 4 x 2 pin data input (pin A dan pin B) dengan 4 pin keluaran (pin F).

Arithmatic Logical Unit (ALU), fungsi unit ini adalah untuk melakukan suatu proses data yang berbentuk angka dan logika, seperti data matematika dan statistika. ALU terdiri dari register – register untuk menyimpan

informasi. Tugas utama dari ALU adalah melakukan perhitungan aritmatika (matematika) yang terjadi sesuai dengan instruksi program. Rangkaian pada ALU yang digunakan untuk menjumlahkan bilangan dinamakan dengan adder. Adder digunakan untuk memproses operasi aritmatika, adder juga disebut rangkaian kombinasional aritmatika.

Ada 3 jenis adder :

1. Rangkaian adder dengan menjumlahkan dua bit disebut half adder. 2. Rangkaian adder dengan menjumlahkan tiga bit disebut full adder. 3. Rangkaian adder dengan menjumlahkan banyak bit disebut paralel adder. Fungsi Arithmatic Logical Unit (ALU) :

1. Bertugas membentuk fungsi – fungsi pengolahan data computer.

2. ALU sering disebut mesin bahasa (machine language) karena bagian ini mengerjakan instruksi – instruksi bahasa mesin yang diberikan padanya.

3. ALU terdiri dari dua bagian, yaitu unit aritmatika dan unit logika Boolean, yang masing – masing memiliki spesifikasi dan tugas tersendiri.

Fungsi – fungsi yang didefinisikan pada ALU adalah add (penjumlahan), addu (penjumlahan tidak bertanda), sub (pengurangan), subu (pengurangan tidak bertanda), and, or, xor, sll (shift left logical), srl (shift right logical), sra (shift right arithmetic), dan lain – lain.

D. Control Unit

Pada computer modern, bagian pengendali adalah unit kendali (control unit) yang berfungsi mengatur seluruh jalannya komponen. Pada setiap tahap atau siklus tidak semua komponen aktif. Semuanya ditentukan oleh keluaran dari bagian pengendali/ pengurut ini. Keluaran kendali lebarnya 12 bit, yang masing – masing bit-nya mengendalikan seluruh register dalam sebuah computer. Setiap tahap dari T1 sampai T6, pengendali mengeluarkan sinyal kendali sebanyak 6 buah. Sinyal kendali yang keluar dari pengendali/ pengurut dinamakan mikro instruksi.

Diantara ke-12 jalur kendali terdapat jalur yang aktif high dan ada juga yang aktif low. Jalur yang aktif low ditandai dengan garis diatas nama jalurnya, jalur tersebut akan aktif jika nilainya = 0. Sementara jalur yang aktif

high akan aktif jika nilainya = 1.

Keluaran register pengendali/ pengurut tergantung 4 bit kode operasi (opcode) dari register instruksi. Setiap instruksi memiliki kode operasi yang berbeda – beda, seperti yang telah dijelaskan sebelumnya. Lebih jauh lagi bagaimanakah kode operasi diproses oleh pengendali/ pengurut sehingga menghasilkan 12 bit mikro instruksi. Kita bisa perhatikan lebih detail lagi.

ROM Alamat 16 x 4

Pencacah Presettable

Pencacah presettable akan mencacah dari 0000 sampai dengan 0011. Selanjutnya tergantung dari kode operasi yang masuk dari ROM alamat. Jika instruksinya LDA maka nilai pencacah berikutnya adalah 0011, jika instruksinya OUT maka nilai pencacah berikutnya 1100.

ROM Kendali 16 x 12

Mikro instruksi adalah isi ROM kendali 16 x 12 yang lebarnya 12 bit. Makro instruksi adalah instruksi dalam bahasa assembly seperti LDA, ADD, SUB, dan OUT sering juga disebut Mnemonik, secara singkat instruksi SAP-1 :

Mikroprogram adalah program yang disimpan dalam ROM kendali. Isi (CON) merupakan mikroprogram yang secara permanen disimpan dalam ROM kendali.

E. Field Programmable Gate Array (FPGA)

Field Programmable Gate Array (FPGA) merupakan suatu Integrated Circuit (IC) yang dibuat agar dapat

deprogram sesuai dengan kebutuhan pengguna. Untuk memprogram FPGA umumnya menggunakan Hardware

description language (HDL). Di dalam FPGA terdapat komponen-komponen logika yang disebut “logic blocks”

dan blok-blok tersebut dapat deprogram menjadi suatu rangkaian sesuai dengan kebutuhan pengguna. FPGA memiliki kemampuan untuk deprogram ulang kembali, seperti breadboard yang terdapat dalam satu chip. Blok-blok logika dapat dikonfigurasi untuk melakukan fungsi- fungsi kombinasi komplek atau gerbang-gerbang logika, seperti AND dan OR.Pada sebagian besar FPGA, blok-blok logika juga memuat elemen-elemen memory, seperti flip-flop atau yang lebih kompleks.

FPGA mempunyai kelebihan sebagai berikut: Dikonfigurasi oleh End User.

Kemampuan desain sistem yang dapat beroperasi pada frekuensi yang semakin tinggi.

Kemampuan meningkatkan integrasi system, penempatan lebih banyak system di dalam sebuah chip, dan penggunaan seluruh gate yang ada di dalam FPGA yang membuat keefektifan harga perancangan.

Tidak memerlukan proses Fabrikasi.

Tersedia solusi yang mendukung chip customized VLSI.

Kemampuan software yang mudah digunakan untuk perancangan dan kemampuan untuk menambahkan desain baru pada sistem di FPGA yang sama pada saat yang berbeda.

Lebih murah dan dapat diprogram kembali jika terjadi bugs.

Perkembangan FPGA pada saat ini berlangsung dengan cepat dan dewasa ini terdapat bermacam- macam keluarga FPGA dengan kebutuhan perancangan dan perangkat perancangan (design tools) yang berbeda. Untuk mempermudah pengguna, FPGA tidak hanya dapat deprogram dengan menggunakan HDL. Desain schematic memungkinkan FPGA dapat diprogram oleh pengguna yang kesulitan meggunakan HDL. Untuk menyedehanakan desain dari fungsi komplek, disediakan beberapa library.

Setiap vendor memiliki arsitektur FPGA yang berbeda-beda namun secara umum arsitektur bagian dalam dari IC FPGA terdiri atas tiga elemen utama yaitu Input/Output Block ( IOB), Configurable Logic

Block (CLB) dan Interkoneksi.

1. Configurable Logic Block (CLB)

CLB adalah tempat logika terprogram pada FPGA. Beberapa komponen yang terdapat pada CLB diantaranya RAM, Flip-Flop, dan Multiplekser.

2. Interkoneksi

Ada beberapa jenis koneksi yang terdapat FPGA, diantaranya Short Lines, Routing, dan Long Lines. Short Lines adalah suatu interkoneksi dimana setiap CLB dihubungkan dengan CLB terdekat. Sedangkan untuk Routing adalah suatu interkoneksi yang terdapat jalur-jalur yang melewati sebuah CLB sebelum menuju Matriks Switch. Fungsi Matriks Switch adalah menghubungkan CLB yang relatif jauh. Kerugian Interkoneksi jenis ini adalah adanya delay yang cukup besar. Dan yang terakhir adalah long lines, dimana designer menghubungkan CLB yang cukup jauh tapi dengan delay minimum, yaitu dengan menghilangkan Matriks Switch. 3. Input/ Output Block (IOB)

Fungsi bagian ini adalah menyalurkan sinyal ke dalam switch dan mengeluarkannya kembali. Bagian ini terdiri dari buffer input dan buffer output.

Arsitektur FPGA

Board FPGA DE 1 keluaran dari ALTERA yang digunakan dalam praktikum

F. Sintesis hasil rangkaian digital ke FPGA

a. Cari sub-menu assignment lalu pilih tools pin planner.

b. Masukkan konfigurasi pin yang diinginkan.

d. pilih Hardware lalu pilih USB Blaster dan klik start.

Pastikan Hardware setup telah mengidentifikasi USB-Blaster. G. Lampiran

a. Tabel konfigurasi pin untuk Toogle Switch.

b. Tabel konfigurasi pin untuk Pushbutton Switch.

Signal Name FPGA Pin No. Description SW[0] PIN_L22 Toogle Switch [0] SW[1] PIN_L21 Toogle Switch [1] SW[2] PIN_M22 Toogle Switch [2] SW[3] PIN_V12 Toogle Switch [3] SW[4] PIN_W12 Toogle Switch [4] SW[5] PIN_U12 Toogle Switch [5] SW[6] PIN_U11 Toogle Switch [6] SW[7] PIN_M2 Toogle Switch [7] SW[8] PIN_M1 Toogle Switch [8] SW[9] PIN_L2 Toogle Switch [9]

Signal Name FPGA Pin No. Description KEY[0] PIN_R22 Pushbutton [0] KEY[1] PIN_R21 Pushbutton [1] KEY[2] PIN_T22 Pushbutton [2] KEY[3] PIN_T21 Pushbutton [3]