=== PERANCANGAN RANGKAIAN KOMBINASIONAL ===

Rangkaian logika atau digital dapat dibagi menjadi 2 bagian yaitu:

1. Rangkaian Kombinasional, adalah suatu rangkaian logika yang keadaan keluarannya hanya dipengaruhi oleh keadaan masukannya saja.

2. Rangkaian Sekuensial, adalah rangkaian logika yang keadaan keluarannya dipengaruhi oleh kondisi masukan dan kondisi rangkaian saat itu.

Beberapa rangkaian kombinasional yang biasa digunakan adalah multiplexer, demultiplexer, encoder, decoder, half adder, full adder, half substractor, full substractor, comparator, driver, converter, dan lain-lain.

Langkah-langkah dalam perancangan rangkaian kombinasional: 1. Penjabaran ide.

2. Menentukan jumlah variabel masukan dan keluaran yang dibutuhkan. 3. Mengimplementasikan ide ke dalam tabel kebenaran.

4. Penyederhanaan fungsi Boolean.

5. Implementasikan ke dalam rangkaian logika.

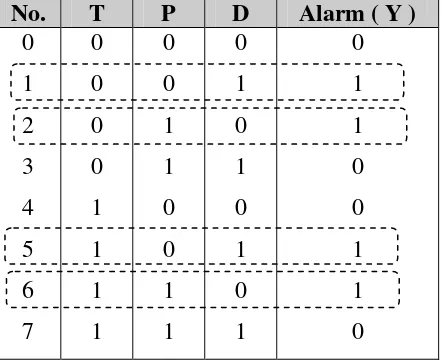

Contoh 1: Perancangan pengatur suhu pada suatu ruangan produksi. Langkah 1: Penjabaran ide

Untuk menjaga suhu suatu ruangan produksi di suatu industri diperlukan sistem alarm. Kondisi normal temperatur (T) dalam ruangan tersebut adalah 120 C, tekanan (P) 5 atm dan kelembaban (D) 10%. Sistem alarm akan berbunyi bila temperatur < 120 C dan tekanan < 5 atm serta kelembaban > 10%, atau < 120 C dan tekanan > 5 atm serta kelembaban < 10%, atau > 120 C dan tekanan < 5 atm serta kelembaban > 10%, atau > 120 C dan tekanan > 5 atm serta kelembaban < 10%. Sistem alarm tersebut digunakan oleh komputer sebagai sinyal masukan untuk mengembalikan kondisi ruangan menjadi kondisi normal kembali.

Langkah 2: Jumlah variabel masukan dan keluaran yang dibutuhkan

Nampak bahwa masukan ada 3 variabel yaitu temperatur (T), tekanan (P), kelembaban (D) dan 1 variabel keluaran yaitu kondisi alarm untuk sistem alarm. Sehingga dibutuhkan 3 sensor sebagai masukan untuk mendeteksi keadaan 3 variabel tersebut.

Langkah 3: Mengimplementasikan ide ke dalam tabel kebenaran Dimisalkan tabel kebenaran untuk sensor yaitu:

a). Y = 0 yang berarti alarm diam. b). Y = 1 yang berarti alarm menyala.

Rangkaian Kombinasi

Masukan Keluaran

Rangkaian Sekuensial

Variabel Masukan Keluaran

Kondisi sensor bekerja

Nilai Logika

0 1

Temperatur ( T ) < 12 0C 12 0C Tekanan ( P ) < 5 atm 5 atm Kelembaban ( D ) < 10 % 10 %

Syarat agar alarm berbunyi:

Kondisi Alarm ( Y )

Temperatur ( T )

Selain kondisi di atas, nilai logika alarm ( Y ) adalah “0”, maka tabel kebenaran dapat dibuat untuk 3 variabel masukan dan 1 variabel keluaran.

Tabel kebenaran:

Langkah 4: Penyederhanaan fungsi alarm

Langkah 5: Implementasikan ke dalam rangkaian logika

Blok Diagram 1

Alat Kendali Suhu Ruangan

Produksi P

D

Contoh 2: Perancangan fungsi matematik F(x) = 3x +1 ; x = {0,1,2,3}. Langkah 1: Penjabaran ide

Akan dirancang sebuah fungsi matematik F(x) = 3x +1, dengan nilai x dibatasi pada x = 0, 1, 2, dan 3 saja, maka ide tersebut dapat dibuat dalam sebuah tabel sebagai berikut:

x F (x)

0 1

1 4

2 7

3 10

Langkah 2: Jumlah variabel masukan dan keluaran yang dibutuhkan

Nampak pada tabel bahwa nilai x dan F(x) menggunakan sistem bilangan desimal, karena itu dibutuhkan konversi sistem bilangan desimal ke sistem bilangan biner. Nilai masukan x maksimum 3, dapat diwakili oleh 2 variabel biner x1 dan x2 (karena 22 = 4) sedangkan nilai keluaran F(x) maksimum 10 dapat diwakili oleh 4 variabel ABCD (karena 24 = 16 > 10), jadi 2 variabel masukan x1 dan x2 serta empat variabel keluaran ABCD yang dibutuhkan.

Langkah 3: Mengimplementasikan ide ke dalam tabel kebenaran

Berdasarkan data pada kedua langkah di atas, maka dapat dibuat tabel kebenaran yang baru, yaitu sebagai berikut:

Desimal Masukan Biner Keluaran Biner

x x1 x2 F(x) A B C D

0 1 2 3

0 0 1 1

0 1 0 1

1 4 7 10

0 0 0 1

0 1 1 0

0 0 1 1

1 0 1 0

Langkah 4: Penyederhanaan fungsi

Dalam bentuk SOP (setelah disederhanakan).

A = x1 x2 ; B = x x1 2 + x1x ; 2 C = x1x + x2 1 x2 ; D = x1 x + x2 1x 2

Langkah 5: Implementasi ke dalam rangkaian logika

Blok Diagram A

B

C D x1 x2

F(x) = 3x + 1

x2 A

B C x1 D

Komparator

Komparator adalah rangkaian logika yang berfungsi untuk membandingkan keadaan logika input-inputnya.

Jenis komparator biner terdiri dari: 1). Non-Equality Comparator

Rangkaian logika yang memberikan keadaan keluarannya tinggi jika keadaan masukan-masukannya berbeda.

Tabel Kebenaran:

Berdasarkan tabel kebenaran dapat dibuat persamaan keluarannya: a). Bentuk SOP X = A B + A B atau X(A,B) = m (1,2) b). Bentuk POS X = (A + B) ( A + B ) atau X(A,B) = M (0,3)

Apabila dilakukan operasi komplemen ganda dan memberlakukan teorema de Morgan, maka dapat diperoleh suatu bentuk gerbang NAND dan NOR.

a). Bentuk NAND didapat dengan cara sebagai berikut:

X = A B + A B XABAB XAB.AB

b). Bentuk NOR didapat dengan cara sebagai berikut:

X = (A + B) ( A + B ) X(AB)(AB) X(AB)(AB)

Rangkaian non-equality comparator dapat diimplementasikan pula dengan gerbang EX-OR, dengan persamaan logikanya X = A B

Simbolnya:

2). Equality Comparator

Rangkaian logika yang memberikan keadaan keluarannya tinggi jika keadaan masukan-masukannya sama.

Tabel Kebenaran:

A B X = A B + A B 0

1 0 1 0 0 1 1

0 1 1 0

B A

X = A B + A B

A B X = AB + A B 0

1 0 1 0 0 1 1

Berdasarkan tabel kebenaran dapat dibuat persamaan keluarannya: a). Bentuk SOP X = A B + AB atau X(A,B) = m (0,3) b). Bentuk POS X = (A + B ) ( A + B) atau X(A,B) = M (1,2)

Apabila dilakukan operasi komplemen ganda dan memberlakukan teorema de Morgan, maka dapat diperoleh suatu bentuk gerbang NAND dan NOR.

a). Bentuk NAND didapat dengan cara sebagai berikut:

X = A B + AB XABAB XAB.AB

b). Bentuk NOR didapat dengan cara sebagai berikut:

X = (A + B ) ( A + B) X(AB)(AB) X(AB)(AB)

Rangkaian equality comparator dapat diimplementasikan pula dengan gerbang EX-NOR, dengan persamaan logikanya X = A B

Simbolnya:

Setengah Penambah (Half Adder)

Setengah penambah (Half Adder) merupakan suatu rangkaian penambah biner 1-bit atau rangkaian penjumlah yang tidak menyertakan bawaan sebelumnya (previous carry) pada masukannya.

Untuk merancang rangkaian Half Adder (HA) diperlukan tabel kebenaran penjumlahan 1-bit, sebagai berikut:

Masukan Keluaran

A B = A + B C0 = simpan

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Berdasarkan tabel kebenaran dan gerbang X-OR, maka = A Bdan C0 = AB.

Rangkaian Half Adder dan blok diagramnya sebagai berikut: X = AB + A B

B A

X = AB + A B B

A

Perlu diingat gerbang X-OR,

keluarannya bernilai “1” bila

jumlah logika bernilai “1” pada

masukannya ganjil.

Half Adder

A

B C0

B A

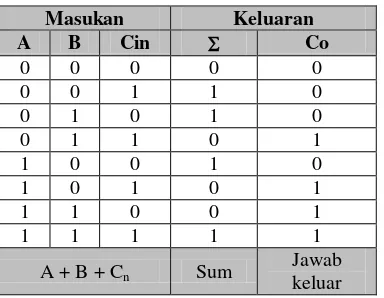

Penambah Penuh (Full Adder)

Sekarang perhatikan persoalan penambah biner berikut:

a)

b)

Pada contoh (a) masih bisa diselesaikan dengan HA untuk menambah biner. Tetapi

pada contoh (b), sudah tidak bisa diselesaikan dengan HA. Karena itu pula aturan lagi

khususnya untuk hal 1 + 1 + 1. Hal ini menyatakan bahwa suatu HA tidak akan bekerja

bila muncul keadaan bawaan masuk. Karena itu diperlukan rangkaian baru yang

disebut dengan Full Adder (penambah penuh). Rangkaian FA mempunyai tiga

masukan yang ditambahkan dan dua keluaran yaitu ∑ dan Co seperti pada tabel

kebenaran berikut:

Tabel Kebenaran Full Adder

Masukan Keluaran

A B Cin Co

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

A + B + Cn Sum Jawab keluar

Kolom keluaran jumlah ( ∑ ) dapat ditulis sebagai berikut:

∑ = A B Cin Cin = bawaan masuk

AB

Cin AB

1

Cin 1 1 1

Co =

=

=

Rangkaian FA dan simbol Blok FA ditunjukkan oleh gambar di bawah ini menunjukan

rangkaian FA yang dibuat dari dua buah HA.

Rangkaian FA

Simbol Blok Rangkaian FA

Rangkaian FA yang dibuat dari dua buah HA

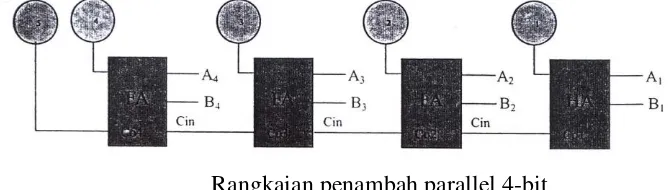

Penjumlahan Paralel

Penambahan biner dapat dikerjakan dengan dua teknik yang berbeda. Yaitu dengan

cara menambah seri (HA dan FA) atau penambahan paralel (yang rangkaiannya akan

dibuat) perhatikan proses penambahan berikut: Cin

Jadi semula A1 + B1→ ∑1 dan bawaan keluar C01

C01 menjadi bawaan masuk pada proses penambahan kedua

C01 + A2 + B2→ ∑2 dan C02

C02 menjadi bawaan masuk pada proses penambahan ketiga

C03 + A3 + B3→ ∑3 dan C03

C03 menjadi bawaan masuk pada proses penambahan keempat

C03 + A4 + B4→ ∑4 dan C04

C04 menjadi suatu overflow (luapan)

Berdasarkan proses tersebut dapat dbuat rangkaian penambah parallel 4-bit yang

diilustrasikan pada gambar dibawah ini.

Rangkaian penambah parallel 4-bit

Rangkaian ini menggunakan sebuah HA dan untuk melakukan perhitungan aritmatik

menstandarkan rangkaian dan untuk melakukan perhitungan aritmatik yang kompleks,

rangkaian tersebut diperbaharui dengan menggunakan empat buah FA. Untuk membuat

FA pertama beroperasi seperti HA, maka masukan Cin pada FA pertama dibumikan

(logika O). rangkaian yang baru ini akan beroperasi secara tepat seperti model lama.

Gambar berikutnya adalah rangkaian penambah parallel 4-bit yang baru yaitu yang

terbuat dari empat buah FA.

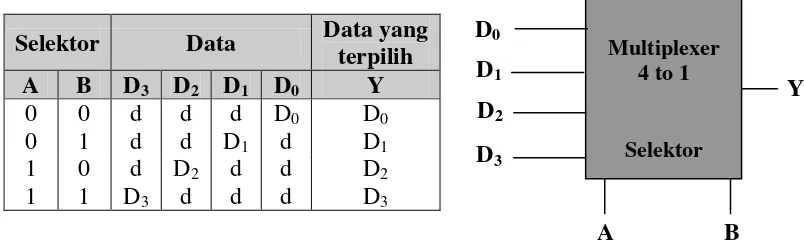

Multiplexer

Multiplexer adalah rangkaian logika yang berfungsi untuk memilih salah satu data masukan dari beberapa (n) data, guna dikirimkan dengan hanya melalui satu saluran keluaran saja.

Multiplexer disebut juga sebagai “DATA SELECTOR”, karena pemilihan informasi

dilakukan oleh selektor (1, 2, …, n). Bila banyaknya selektor yang digunakan adalah n- buah, maka jumlah maksimal data yang akan dipilih adalah 2n buah.

Blok diagram dari multiplexer sebagai berikut:

Contoh: Pada multiplexer 4 to 1, untuk 4 data yang akan dipilih diperlukan 2 selektor, karena 22 = 4.

Tabel kebenaran dan blok diagramnya sebagai berikut:

Selektor Data Data yang terpilih A B D3 D2 D1 D0 Y

0 0 d d d D0 D0 0 1 d d D1 d D1 1 0 d D2 d d D2 1 1 D3 d d d D3

Berdasarkan tabel kebenaran maka dapat diperoleh persamaan Booleannya sebagai berikut: Y ABD0ABD1ABD2 ABD3, untuk implementasi rangkaian logikanya adalah sebagai berikut:

Multiplexer

Selektor

Y D0

D1

D2n

1 2 n

A B

Y

Multiplexer 4 to 1

Selektor

D0

D1

D2

D3

A B

D0

D1

D2

D3

Multiplexer Enable

Jenis multiplexer ini mempunyai masukan enable yang berguna untuk mengatur kerja dari unit.

Bila enable ( E ) = 1, maka multiplexer bekerja normal. Bila enable ( E ) = 0, maka multiplexer tidak bekerja.

Cara kerja multiplexer ini nampak pada tabel kebenaran sebagai berikut:

Enable Selektor Data Data yang terpilih E A B D3 D2 D1 D0 Y

0 d d d d d d 0

1 0 0 d d d D0 D0 1 0 1 d d D1 d D1 1 1 0 d D2 d d D2 1 1 1 D3 d d d D3

Berdasarkan tabel kebenaran maka dapat diperoleh persamaan Booleannya sebagai berikut: Y ABED0ABED1ABED2ABED3, untuk implementasi rangkaian logikanya adalah sebagai berikut:

Demultiplexer

Demultiplexer adalah rangkaian logika yang berfungsi untuk menyalurkan satu data biner ke beberapa keluaran, tetapi hanya satu keluaran yang terpilih yang dapat menampung isi data tersebut.

Demultiplexer merupakan kebalikan dari multiplexer.

A B

Y

Multiplexer Enable

4 to 1

Selektor

D1

D2

D3

E

A B

D0

D1

D2

D3

Contoh: Pada demultiplexer 1 to 4.

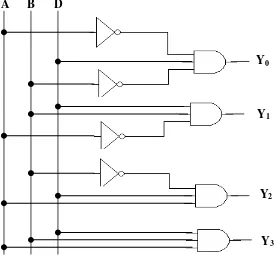

Tabel kebenaran dan blok diagramnya sebagai berikut:

Selektor Data Keluaran

A B D Y3 Y2 Y1 Y0

0 0 D 0 0 0 D

0 1 D 0 0 D 0

1 0 D 0 D 0 0

1 1 D D 0 0 0

Berdasarkan tabel kebenaran maka dapat diperoleh persamaan Booleannya sebagai berikut: Y0 ABD , Y1ABD , Y2 ABD , Y3 ABD untuk implementasi rangkaian logikanya adalah sebagai berikut:

Dekoder

Dekoder adalah rangkaian logika yang mengubah masukan kode n-bit ke m saluran,

sehingga “keluaran yang diaktifkan” hanya satu. (2n > m).

Blok diagramnya sebagai berikut:

A B

D

Demultiplexer 4 to 1

Selektor

Y0

Y1

Y2

Y3

A B D

Y0

Y1

Y2

Y3

Dekoder

D0

D1

Dm

A0

A1

An

n - masukan m – keluaran yang

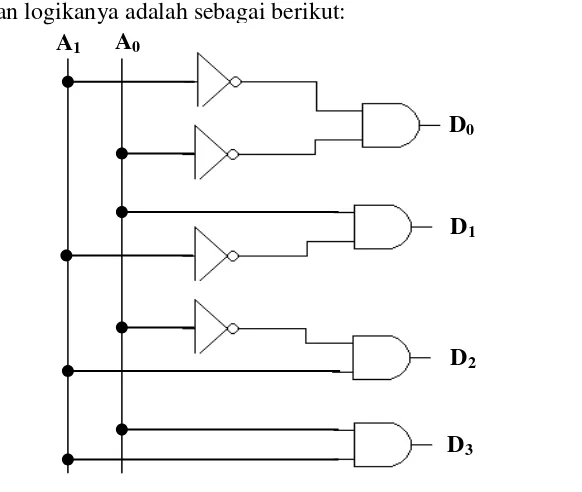

Contoh: Pada dekoder 2 to 4.

Tabel kebenaran dan blok diagramnya sebagai berikut:

Masukan Keluaran A1 A0 D3 D2 D1 D0

0 0 0 0 0 1

0 1 0 0 1 0

1 0 0 1 0 0

1 1 1 0 0 0

Berdasarkan tabel kebenaran maka dapat diperoleh persamaan Booleannya sebagai berikut: D0 A1.A0; D1A1.A0; D2 A1.A0; D3 A1.A0 untuk implementasi rangkaian logikanya adalah sebagai berikut:

Dekoder Enable

Dekoder enable adalah dekoder yang dilengkapi masukan enable yang berguna untuk mengatur kerja dari dekoder.

Bila enable ( E ) = 1, maka dekoder diaktifkan. Bila enable ( E ) = 0, maka dekoder tidak aktif.

Contoh: Pada dekoder enable 2 to 4.

Tabel kebenaran dan blok diagramnya sebagai berikut:

Masukan Keluaran

E A1 A0 D3 D2 D1 D0

0 d d 0 0 0 0

1 0 0 0 0 0 1

1 0 1 0 0 1 0

1 1 0 0 1 0 0

1 1 1 1 0 0 0

Dekoder 2 to 4

D0

D1

D3

A0

A1

D2

D0

D1

D2

D3

A0

A1

Dekoder Enable

2 to 4

D0

D1

D3

A0

A1

D2

Berdasarkan tabel kebenaran maka dapat diperoleh persamaan Booleannya sebagai berikut: D0 A1.A0.E; D1A1.A0.E; D2 A1.A0.E; D3 A1.A0.E, implementasi rangkaian logikanya adalah sebagai berikut:

Gabungan Beberapa Dekoder

Beberapa dekoder dapat digabung sehingga menjadi dekoder baru yang mempunyai jumlah keluaran lebih besar. Penggabungan ini dapat dilakukan bila dekodernya memiliki enable.

Contoh: Pada sebuah dekoder 3 to 8, yang terbuat dari 2 buah dekoder 2 to 4.

Untuk membuat dekoder 3 to 8 diperlukan 3 buah masukan, maka tabel kebenarannya sebagai berikut:

A2 A1 A0

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

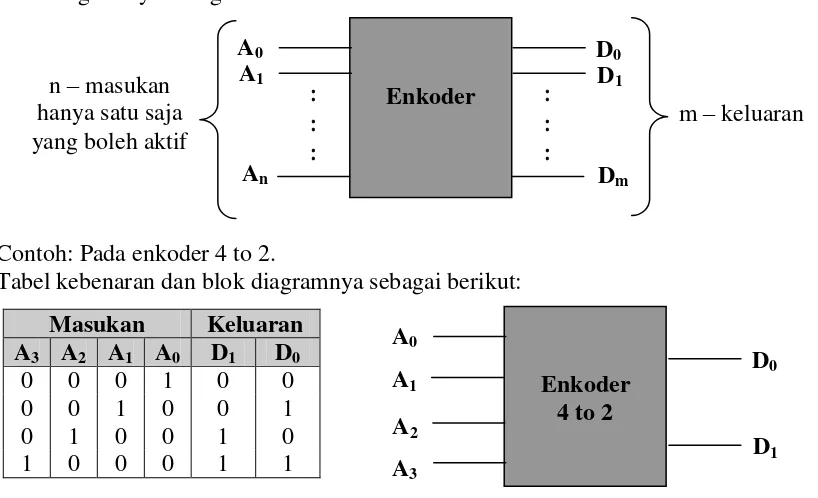

Enkoder

Enkoder adalah rangkaian logika yang menerima “n” masukan dan m keluaran, sehingga “hanya satu masukan saja yang diaktifkan” pada setiap

saat hanya satu. (2n < m).

.

D0

D1

D2

D3

A0

A1

E

Dekoder A2 = 0

Dekoder A2 = 1

A0

A1

A2

D1

E1

D0

D3

D2

D5

E2

D4

D7

Blok diagramnya sebagai berikut:

Contoh: Pada enkoder 4 to 2.

Tabel kebenaran dan blok diagramnya sebagai berikut:

Masukan Keluaran A3 A2 A1 A0 D1 D0

0 0 0 1 0 0 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 0 1 1

Berdasarkan tabel kebenaran maka dapat diperoleh persamaan Booleannya sebagai berikut: D0 = A1 + A3 dan D1 = A2 + A3, untuk implementasi rangkaian logikanya adalah sebagai berikut:

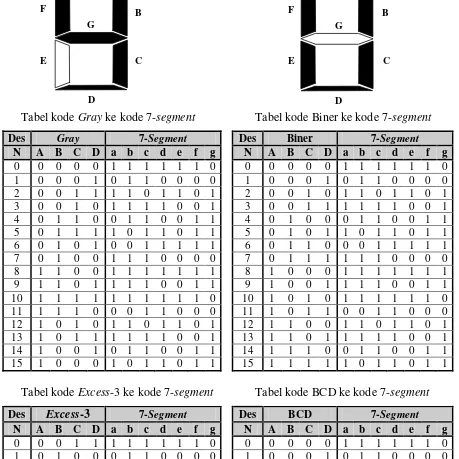

Driver

Rangkaian driver adalah rangkaian yang mengubah dari sebuah kode (kode BCD, kode Gray, kode Biner atau yang lainnya) ke sebuah kode 7-segment.

Kode 7-segment adalah suatu kode yang terdiri dari 7 ruas berupa Led yang dirangkai untuk dapat digunakan sebagai peraga bilangan desimal. Gambar dan penamaan setiap ruas dari kode 7-segment.

Enkoder

D0

D1

Dm

A0

A1

An

n – masukan hanya satu saja yang boleh aktif

m – keluaran

Enkoder 4 to 2

D0

A0

A1

D1

A2

A3

D0

A0

A1

D1

A2

A3

A

B

C

D E

F

a) Sebagai peraga bilangan 1, b) Sebagai peraga bilangan 2, Led yang menyala : B, C Led yang menyala : A, B, D, E, G

c) Sebagai peraga bilangan 3, d) Sebagai peraga bilangan 4, Led yang menyala : A, B, C, D, G Led yang menyala : B, C, F, G

e) Sebagai peraga bilangan 5, f) Sebagai peraga bilangan 6, Led yang menyala : A, C, D, F, G Led yang menyala : C, D, E, F, G

g) Sebagai peraga bilangan 7, h) Sebagai peraga bilangan 8,

Led yang menyala : A, B, C Led yang menyala : A, B,C, D, E, F, G

i) Sebagai peraga bilangan 9, j) Sebagai peraga bilangan 0,

Led yang menyala : A, B, C, D, F, G Led yang menyala : A, B,C, D, E, F A

B

C

D E

F

G

A

B

C

D E

F

G

A

B

C

D E

F

G

A

B

C

D E

F

G

A

B

C

D E

F

G

A

B

C

D E

F

G

A

B

C

D E

F

G

A

B

C

D E

F

Tabel kode Gray ke kode 7-segment Tabel kode Biner ke kode 7-segment

Des Gray 7-Segment Des Biner 7-Segment

N A B C D a b c d e f g N A B C D a b c d e f g

0 0 0 0 0 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 0

1 0 0 0 1 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 0 0

2 0 0 1 1 1 1 0 1 1 0 1 2 0 0 1 0 1 1 0 1 1 0 1

3 0 0 1 0 1 1 1 1 0 0 1 3 0 0 1 1 1 1 1 1 0 0 1

4 0 1 1 0 0 1 1 0 0 1 1 4 0 1 0 0 0 1 1 0 0 1 1

5 0 1 1 1 1 0 1 1 0 1 1 5 0 1 0 1 1 0 1 1 0 1 1

6 0 1 0 1 0 0 1 1 1 1 1 6 0 1 1 0 0 0 1 1 1 1 1

7 0 1 0 0 1 1 1 0 0 0 0 7 0 1 1 1 1 1 1 0 0 0 0

8 1 1 0 0 1 1 1 1 1 1 1 8 1 0 0 0 1 1 1 1 1 1 1

9 1 1 0 1 1 1 1 0 0 1 1 9 1 0 0 1 1 1 1 0 0 1 1

10 1 1 1 1 1 1 1 1 1 1 0 10 1 0 1 0 1 1 1 1 1 1 0

11 1 1 1 0 0 0 1 1 0 0 0 11 1 0 1 1 0 0 1 1 0 0 0

12 1 0 1 0 1 1 0 1 1 0 1 12 1 1 0 0 1 1 0 1 1 0 1

13 1 0 1 1 1 1 1 1 0 0 1 13 1 1 0 1 1 1 1 1 0 0 1

14 1 0 0 1 0 1 1 0 0 1 1 14 1 1 1 0 0 1 1 0 0 1 1

15 1 0 0 0 1 0 1 1 0 1 1 15 1 1 1 1 1 0 1 1 0 1 1

Tabel kode Excess-3 ke kode 7-segment Tabel kode BCD ke kode 7-segment

Des Excess-3 7-Segment Des BCD 7-Segment

N A B C D a b c d e f g N A B C D a b c d e f g

0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 0

1 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 0 0

2 0 1 0 1 1 1 0 1 1 0 1 2 0 0 1 0 1 1 0 1 1 0 1

3 0 1 1 0 1 1 1 1 0 0 1 3 0 0 1 1 1 1 1 1 0 0 1

4 0 1 1 1 0 1 1 0 0 1 1 4 0 1 0 0 0 1 1 0 0 1 1

5 1 0 0 0 1 0 1 1 0 1 1 5 0 1 0 1 1 0 1 1 0 1 1

6 1 0 0 1 0 0 1 1 1 1 1 6 0 1 1 0 0 0 1 1 1 1 1

7 1 0 1 0 1 1 1 0 0 0 0 7 0 1 1 1 1 1 1 0 0 0 0

8 1 0 1 1 1 1 1 1 1 1 1 8 1 0 0 0 1 1 1 1 1 1 1

9 1 1 0 0 1 1 1 0 0 1 1 9 1 0 0 1 1 1 1 0 0 1 1

Contoh:

1. Pengubahan kode Excess-3 ke kode 7-segment

Berdasarkan tabel kode Excess-3 ke kode 7-segment di atas, maka dapat dibuat peta Karnaugh dan persamaan Boolean- nya sebagai berikut:

A

B

C

D E

F

G

A

B

C

D E

F

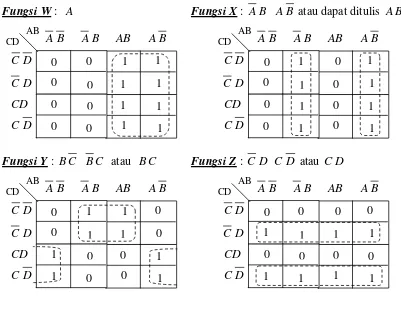

Fungsi a : AD BC CD BCD Fungsi b : B C

Fungsi c : A C D Fungsi d : BD CD BC BCD

Fungsi e : BD CD Fungsi f : AC CD

Fungsi g : BC CD AC AD

2. Pengubahan kode BCD ke kode 7-segment

Berdasarkan tabel kode BCD ke kode 7-segment di atas, maka dapat dibuat peta Karnaugh dan persamaan Boolean- nya sebagai berikut:

Fungsi a : A BD CD BD Fungsi b : B CD CD

Fungsi c : B C D Fungsi d : BC CD BD BCD

Fungsi e : CD BD Fungsi f : A BC BD CD

Fungsi g : A CD BC BC

Konverter

Konverter adalah rangkaian yang mengubah dari suatu kode ke kode yang lainnya. Contoh pengubahan kode Biner ke kode Gray.

TEKNIK DIGITAL Tabel kebenaran :

Des Biner Gray

N A B C D W X Y Z peta Karnaugh dan persamaan Boolean- nya sebagai berikut: