(a)

(a) Flash ADCFlash ADC Flash

Flash ADCADC juga juga dikenal dikenal sebagai sebagai parallelparallel A/D A/D ConverterConverter sebagasebagai rangkai rangkaianian ADC ADC yang palingyang paling mudah dipelajar

mudah dipelajari. i. DibentDibentuk uk dari sekumpulan komparatdari sekumpulan komparator or yang membandingkayang membandingkan n sinyasinyal l inputinput de

dengangan n tetegagangngan an rerefefererensnsi i memengnggungunakakanan op-ampop-amp. . ReResisiststor or yayang ng didigugunanakan kan didisisini ni haharuruss menggunakan resistor bertoleransi tinggi agar lebih akurat. Keluaran output dihubungkan ke menggunakan resistor bertoleransi tinggi agar lebih akurat. Keluaran output dihubungkan ke inp

input dari ut dari sebsebuahuah priority priority encoder encoder , yang akan menghasilkan output biner. Gambar 7.2. adalah, yang akan menghasilkan output biner. Gambar 7.2. adalah contoh rangkaian Flash D! " bit.

contoh rangkaian Flash D! " bit.

Gambar 7.2 Rangkaian flash D! " bit Gambar 7.2 Rangkaian flash D! " bit #ri

#rinsinsip p kerkerja ja ranrangkagkaian ian flaflash sh DD! ! " " bitbit,$r,$ref ef adaadalah lah tegtegangangan an ststabiabil l yanyang g disdisediediakaakan n oleolehh regulator tegangan presisi sebagai bagian dari rangkaian con%erter. &ika input analog melebihi regulator tegangan presisi sebagai bagian dari rangkaian con%erter. &ika input analog melebihi teg

tegangaangan n refrefereerensinsi, , outoutput put komkomparparatoator r akaakan n menmenghasghasilkilkan an kondkondisi isi tintinggi ggi secsecara ara berberuntuntun.un. 'edangkan priority encoder akan menghasilkan kondisi tinggi secara beruntun. #riority encoder 'edangkan priority encoder akan menghasilkan kondisi tinggi secara beruntun. #riority encoder akan membangkitkan bilangan biner berdasarkan input yang diterima.

akan membangkitkan bilangan biner berdasarkan input yang diterima.

Rangkaian D!ideal secara unik dapat mereprestasikan seluruh rentang masukan analog tertentu Rangkaian D!ideal secara unik dapat mereprestasikan seluruh rentang masukan analog tertentu de

dengangan n sejsejumlumlah ah kokode de kekelualuaran ran digdigitaital. l. KeKenyanyataataannynnya a karkarena ena sinsinyal yal anaanalolog g bebesifsifat at konkontintinuu sedangkan sinyal digital bersifat diskrit, maka ada proses kuantisasi yang menimbulkan kekeliruan. sedangkan sinyal digital bersifat diskrit, maka ada proses kuantisasi yang menimbulkan kekeliruan.

pabila jumlah sinyal diskritnya (yang me)akili rentang masukan analog* ditambah, maka lebar undak ( step width* akan semakin kecil dan fungsi transfer akan mendekati garis lurus ideal.

+ebar satu undak ( step* didefinisikan sebagai satu LSB ( Least Significant Bit * dan unit ini digunakan sebagai unit rujukan kon%ersi. 'atu unit LSB itu juga digunakan untuk mengukur resolusi kon%erter karena dapat menggambarkan jumlah bagian atau unit dalam rentang analog penuh. Gambar 7.". menunjuk proses kon%ersi rangkaian flash ADC .

Gambar 7.". #roses kon%ersi rangkaian flash D!.

Resolusi ADC selalu dinyatakan sebagai jumlah bit dalam sinyal keluaran digitalnya. isalnya, ADC dengan resolusi n-bit memiliki 2n tingkat undak ( step level *. eskipun demikian, karena undak pertama dan undak terakhir hanya setengah dari lebar penuh, maka rentang skala penuh ( FSR,

(b) Successive approximation ADC

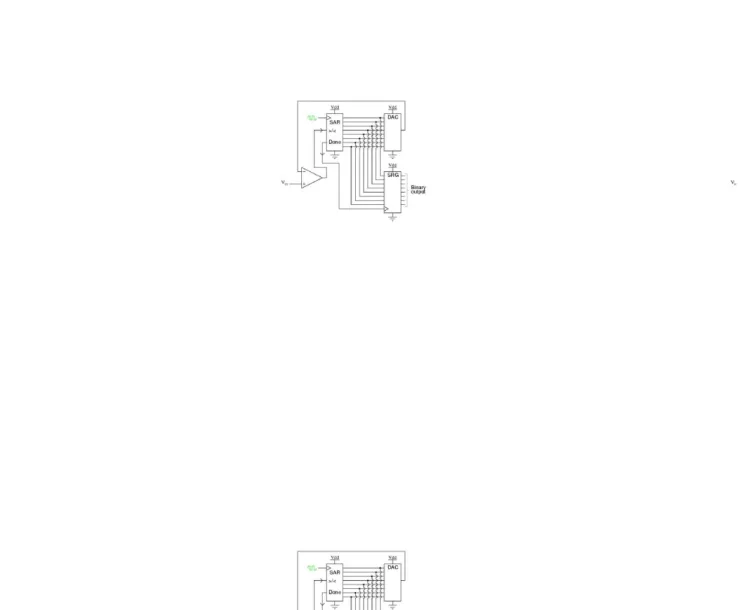

Rangkaian menggunakan sccessive appro!imation ADC proses kon%ersinya menggunakan rangkaian counter yang dikenal sebagai sccessive-appro!imation register , yaitu melalui pendekatan berturut-turut untuk mencari nilai yang paling tepat. Disamping menghitung naik

deretan data biner, register ini menghitung seluruh nilai bit dimulai dari "SB dan diakhiri LSB.Gambar 7./. menunjuk contoh rangkaian sccessive appro!imation ADC .

Gambar 7./. !ontoh rangkaian sccessive appro!imation ADC .

'elama proses perhitungan, register akan memonitor otpt komparator untuk melihat jika hitungan biner kurang atau lebih besar dari input sinyal analog. #erlu diingat bah)a SAR dapat mengeluarkan bilangan biner dalam format serial, sehingga dapat meniadakan penggunaan shift register. &ika diplot, cara kerja SAR dapat digambarkan sepertiGambar 7.0.

Digital Ramp ADC

Digital Ramp D! merupakan jenis D! 1nalog to Digital !on%erter yang bekerja berdasarkan prinsip kerja counter.

input signal analog dibandingkan dengan input lain pada komparator digital.

output dari komparator digital diumpankan ke +3D counter dan ke 4DG4 5R6GG4R 4G56$4 latches.

output dari counter diumpankan ke input D! 1D! yang digunakan adalah jenis 8inary 9eight Resistor juga diumpankan ke input +atches.

3utput dari D! diumpankan ke input negati%e komparator.

penjelasan mengenai komparator digital, counter, latches, dan D! akan dijelaskan dengan penggunaan D! pada aplikasi high temperature thermometer.

Komparator Digital [digital comparator] adalah komparator khusus yang hanya memiliki 2 kondisi output. dua kondisi yang dimaksud adalah logik 1 atau nol.

Logik 1 berarti tegangan keluaran komparator berkisar 5 volt. Logik 0 berarti tegangan keluaran komparator berkisar 0 volt.

output komparator akan berlogik 1 ika hanya tegangan pada input positive komparator lebih besar dari tegangan input negative komparator.

output komparator akan berlogik 0 ika tegangan pada input positive ! tegangan pada input negative" atau tegangan input negative lebih besar dari tegangan input positive.

input output

#$ % &$ logik 1 [5 volt] #$ ! &$ logik 0 [0 volt] #$ ' &$ logik 0 [0 volt]

counter adalah komponen yang melakukan pencacahan ( penghitungan. counter yang digunakan yaitu counter dengan L)*D. input dari counter di groundkan [diberi tegangan 0 volt]" clock diberi pulsa [pulsa maksimum yang diperbolehkan adalah 50+,-]. L)*D dihubungkan ke output komparator. ketika L)*D logik 1" maka counter melakukan penghitungan dari mulai 0. ketika L)*D berlogik 0" maka

counter menghentikan penghitungan. D* [enis binary /eight resistor] adalah pengkonversi signal digital menadi analog dengan menggunakan beberapa resistor [tergantung umlah bit yang akan dikonversi]. misalkan input D* 0010" tegangan reerensi D* ! 5 $" maka tegangan output [signal analognya] adalah L* D34+*L D* 63 dibagi D7* 8*9K*: n&1 dikali :39*9* 3;334. adi $out ! [2(2<=] > 5 ! 2.5 volt. tegangan maksimum dari D* ini adalah ?.=@5 volt. Latches adalah bagian yang menahan sementara data dari counter untuk selanutnya diproses untuk dimunculkan pada display [@ segment atau LD]. latches bekera berdasarkan prinsip bistable multivibrator" yaitu multivibrator yang memiliki kondisi 2 kondisi output yaitu 0 dan 1. data dari counter akan ditahan oleh latches" ketika 3D93 :993 39*:$3 dari latches mendapat transisi turun [perubahan dari logik 1 ke logik 0]" maka latches akan melanutkan data dari counter ke display.

gambar diatas adalah aplikasi penggunaan digital ramp *D untuk termometer suhu tinggi.

suhu tinggi dikonversi oleh sensor bimetal dengan reerensi suhu es cair 0 deraat celcius. lalu tegangan keluaran dari bimetal diperkuat menggunakan op& dengan gain sesuai yang diinginkan. misalkan output maksimum dari op&

sensor adalah ? volt. maka ketika suhu maksimum tercapai [misalkan 1000 deraat celcius]" maka keluaran op& adalah ? volt" lalu masuk ke input positi

komparator. komparator membandingkan input # dan &" karen #$ % & $" ?v % 0v" maka output komparator berlogik 1. logik 1 ini digunakan pada L)*D counter" sehingga counter mulai mencacah ( menghitung. pencacahan yang dilakukan counter dikonversi oleh D* menadi tegangan. ketika input biner tertentu masuk ke D*" maka D* akan mengeluarkan tegangan sampai ? volt. ketika output D* ? volt" input # ! input & komparator" sehingga output komparator berlogik 0. counter berhenti mencacah karena L)*D berlogik 0. latches bekera karena teradi

tadi dimunculkan pada display.

Dengan tegangan reerensi D* sebesar 5 volt" input D* A bits" maka resolusinya res ! [1 ( 2<@] > 5 volt ! 0.0=? v. perubahan terkceil dari D* adalah 0.0=? v" setiap perubahan bilangan biner yang menadi input D* menghasilkan perubahan tegangan 0.0=? v. 0 v 0.0=? v 0.0@A v . . . ?.>>> v

untuk mendapatkan tegangan output sebesar ? volt" maka D* melakukan sampling sebanyak 25B kali. sehingga input negative komparator mendapat tegangan ? volt dan outputnya menadi logik 0.

data pada counter yang tersimpan pada latches [11111111] di munculkan pada LD sebagai display.