PEMBANGKIT GELOMBANG SINUS, SEGITIGA

DAN KOTAK MENGGUNAKAN CPLD/FPGA

Diajukan Untuk Memenuhi Salah Satu Syarat

Memperoleh Gelar Sarjana Teknik

Program Studi Teknik Elektro

Disusun oleh:

NENDAR WIBARASTA

NIM : 035114037

PROGRAM STUDI TEKNIK ELEKTRO

FAKULTAS SAINS DAN TEKNOLOGI

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

2010

WAVEFORM GENERATOR OF SINE, TRIANGLE

AND SQUARE WAVE USING CPLD/FPGA

Presented as Partial Fulfillment of the Requirements

To Obtain the Sarjana Teknik Degree

In Electrical Engineering Study Program

NENDAR WIBARASTA

NIM : 035114037

ELECTRICAL ENGINEERING STUDY PROGRAM

SCIENCE AND TECHNOLOGY FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

2010

“

If we knew what we were doing, it wouldn't be called research, would

it? "

(Albert Einstein)

"Security is mostly a superstition... Life is either a daring adventure, or

nothing."

(Hellen Keller)

“Try to keep everything simple, since we don’t need to exaggerate

anything”

Kupersembahkan Tugas Akhir ini untuk :

<

Allah Bapa di Surga atas kasih dan karunia-Nya.

<

Bapak, ibu dan adikku tercinta.

<

Almamaterku Teknik Elektro USD

DAN KOTAK MENGGUNAKAN CPLD/FPGA

Nendar Wibarasta

035114037

INTISARI

Kemampuan untuk membangkitkan bentuk gelombang seperti gelombang sinus,

gelombang segitiga dan gelombang kotak sudah menjadi hal yang sangat penting dalam dunia

medis, telekomunikasi, dan industri. Namun sinyal analog memiliki resiko sangat rentan

terhadap derau, sehingga pembangkitan gelombang secara digital yang tahan derau menjadi

sangat penting.

Pembangkitan sinyal atau gelombang secara digital pada penelitian ini dirancang

menggunakan teknik Direct Digital Synthesis atau DDS. Sederetan bilangan biner 8 bit

digunakan sebagai tuning word. Tuning word ini yang akan menentukan frekuensi keluaran

gelombang keluaran. Pengubahan nilai tuning word akan merubah nilai frekuensi keluaran

pada semua jenis gelombang yang dibangkitkan. Pengubahan nilai amplitudo dilakukan secara

analog pada bagian Digital to Analog Converter.

Penelitian ini belum selesai dan hanya berhasil sampai pada tahap simulasi. Simulasi

dari aplikasi pembentuk gelombang ini membuktikan bahwa frekuensi keluaran dapat

diubah-ubah secara digital. Pengujian amplitudo gelombang tidak dapat dilakukan dikarenakan blok

DAC belum dibuat.

Kata kunci : Direct Digital Synthesis, gelombang , frekuensi.

WAVEFORM GENERATOR OF SINE, TRIANGLE

AND SQUARE WAVE USING CPLD/FPGA

Nendar Wibarasta

035114037

ABSTRACT

The ability to generate the waveforms such as sinewave, triangle wave and square

wave has become an important subject in the field of medication, telecommunication and

industry. But the analog signal is fragile of noise, so it is important to generate digital

waveforms which are persistent of noise.

The waveform generator in this research is designed using Direct Digital Synthesis

method, which is usually abbreviated to DDS. The 8 bits of binary numbers are used as tuning

word. This tuning word will determine the frequency of the output waveforms. The changing

value of tuning word will change the value of the output frequency of the waveform, while the

the changing the waveform’s amplitude is operated in Digital to Analog Converter (DAC).

This research is not completed yet, and only proceeds until the simulation session. It is

proved from the simulation that the waveform’s frequency can be changed digitally. The test

of amplitude of the analog waveform could not be completed due to the DAC part that has not

been built yet.

Key words: Direct Digital Synthesis, waveform, frequency.

Halaman

HALAMAN JUDUL DALAM BAHASA INDONESIA………..…...

i

HALAMAN JUDUL DALAM BAHASA INGGRIS...

ii

LEMBAR PENGESAHAN OLEH PEMBIMBING ………...

iii

LEMBAR PENGESAHAN OLEH PENGUJI ………...

iv

LEMBAR PERNYATAAN KEASLIAN KARYA ……….……...

v

MOTTO DAN PERSEMBAHAN ……….….……...

vi

LEMBAR PERNYATAAN PERSETUJUAN PUBLIKASI KARYA ILMIAH

UNTUK KEPENTINGAN AKADEMIS...

vii

INTISARI ………...

viii

ABSTRACT ………...

ix

KATA PENGANTAR ……… ...

x

DAFTAR ISI ………...

xi

DAFTAR GAMBAR ……….………...

xiv

BAB I

PENDAHULUAN

………..………...

1

1.1. Latar Belakang Masalah ………..………..

1

1.2. Tujuan dan Manfaat Penelitian………..……….

2

1.3. Batasan Masalah ………....

2

1.4. Metodologi

Penelitian...

………..…………...

2

1.5. Sistematika Penulisan ………....

2

BAB II

DASAR TEORI

……….…………...

3

2.1. Metode

Direct Digital Synthesis………..…………..

3

2.1.1. Akumulator...

………...

4

2.1.2. ROM

Look Up Table... ………..……...

4

2.1.3 Register

Parallel In Parallel Out...

...

5

2.1.6

Digital to Analog Converter...

7

2.2. Konsep Perancangan Sistem Digital dengan Menggunakan Perangkat

Lunak Altera Max+Plus II ……...

8

2.3.

Complex Programmable Logic Device

9

BAB III PERANCANGAN PEMBANGKIT BENTUK GELOMBANG...

10

3.1. Perancangan Arsitektur Pembangkit Gelombang...

11

3.1.1. Perancangan

Register

Input ...

11

3.1.2. Perancangan Blok Akumulator Fasa...

11

3.1.3. Perancangan Blok ROM Gelombang Sinus...

12

3.1.4. Perancangan

Pengontrol

Gelombang

Segitiga...

13

3.1.5. Perancangan

Pengontrol

Gelombang Segi Empat...

14

3.1.6. Perancangan

Pengontrol

Output...

14

3.1.7. Perancangan

Register

Output...

14

3.1.8 Perancangan

Blok Digital to Analog Converter...

14

3.2. Metode Pembentukan Gelombang Sinus...

15

3.3. Metode Pembentukan Gelombang Segitiga ...

17

3.4. Metode Pembentukan Gelombang Kotak...

19

3.5. Pin Pengontrol, Pin Masukan, dan Pin Keluaran Pada UP1 Board

20

3.6. Penggunaan

Flex Switch Pada Papan UP1 Board... ..

21

3.7. Perancangan Pembagi Frekuensi...

21

3.8. Perancangan Saklar Pengontrol Gelombang Segitiga dan Kotak...

21

3.9. Pengimplementasian

Perancangan...

22

BAB IV HASIL DAN PEMBAHASAN

………... 23

4.1. Pengujian Blok-Blok Penyusun Konfigurasi Pembentuk Gelombang

23

4.1.1. Pengujian Blok Register Input ….…... 24

4.1.2. Pengujian Blok Akumulator……...

25

4.1.3. Pengujian Blok Register Adder/Register Fasa…...………...

26

4.1.4. Pengujian Blok ROM……….……...

27

4.1.5 Pengujian Blok Pengontrol Gelombang Segitiga...

30

4.1.8 Pengujian Blok Register Output... 34

4.2. Pengujian Gelombang Sinus...

34

4.2.1. Pengujian Gelombang Sinus dengan Tuning Word 00000010

238

4.2.2. Pengaruh

Nilai

Tuning Word Pada Bentuk Gelombang Sinus

40

4.2.3. Karakteristik Gelombang Sinus Pada Rentang Frekuensi Audio 42

4.3. Pengujian Gelombang Segitiga...

44

4.3.1. Kesalahan Pada Simulasi Gelombang Segitiga...

45

4.3.2. Analisa Kesalahan Pada Port Sub...

48

4.4. Pengujian Gelombang Kotak/Segi Empat...

50

4.5. Pengujian Blok DAC dan Pengubahan Amplitudo Gelombang...

52

BAB V

KESIMPULAN DAN SARAN

……….……... 55

5.1. Kesimpulan

………..……..……...

53

5.2. Saran

………..……….…………...

53

DAFTAR PUSTAKA

………..………... 55

LAMPIRAN KONFIGURASI PEMBANGKIT GELOMBANG

LAMPIRAN HASIL SIMULASI PEMBANGKIT GELOMBANG PADA

SIMULATOR ALTERA MAX+PLUS II

LAMPIRAN GRAFIK GELOMBANG PADA BEBERAPA NILAI

TUNING WORD

LAMPIRAN CONTOH TABEL UNTUK PEMBANGKITAN GELOMBANG SINUS

PADA

TUNING WORD

00000001

2LAMPIRAN LIST PROGRAM PER MODUL/SUB PROYEK

LAMPIRAN DATASHEET DAC0832

LAMPIRAN DATASHEET LF351

Halaman

Gambar 2.1. Diagram blok dari arsitektur DDS...

3

Gambar 2.2. Contoh blok rangkaian register PIPO………..…...

5

Gambar 2.3. Rangkaian penambah/pengurang komplemen 2………..………..…

5

Gambar 2.4. Teknik pengubahan laju frekuensi ………..…...

7

Gambar 2.5. Rangkaian DAC model R-2R Ladder ...

7

Gambar 3.1. Diagram detail rancangan arsitektur pembangkit gelombang….…...

10

Gambar 3.2. Sintaks pada MATLAB untuk mendapatkan nilai fungsi sinus ……

12

Gambar 3.3. Nilai heksadesimal bagi nilai amplitudo gelombang sinus ..……….

13

Gambar 3.4. Skema rangkaian DAC ………...

15

Gambar 3.5. Diagram alir utama pembentukan gelombang sinus …...…………..

16

Gambar 3.6. Diagram alir dari proses looping ……….………..…………....

17

Gambar 3.7. Diagram alir pengontrolan dalam pembentukan gelombang segitiga

18

Gambar 3.8. Diagram alir dari pembentukan gelombang kotak ………….……....

19

Gambar 3.9. Blok diagram dari UP1 Board ……….……...

20

Gambar 3.10. Skema dari pin keluaran dan pin kontrol...

20

Gambar 3.11. Bagian Flex-Switch yang akan digunakan sebagai input tuning word

21

Gambar 3.12. Rangkaian saklar pengontrol...

22

Gambar 4.1. Blok Register Input ………..…...

24

Gambar 4.2. Hasil simulasi dari blok register input...

24

Gambar 4.3. Rangkaian blok akumulator ……….….

25

Gambar 4.4. Hasil simulasi dari proses penambahan ………..……...

25

Gambar 4.5. Hasil simulasi dari proses pengurangan ……….………... .

26

Gambar 4.6. Blok register adder/register fasa……….……...

27

Gambar 4.7. Hasil simulasi dari cara kerja register adder ………..………....

27

Gambar 4.8. Blok ROM ………...………...

28

Gambar 4.9. Hasil simulasi dari blok ROM dengan alamat desimal 1

10….…….... 28

Gambar 4.10. Hasil simulasi blok ROM dengan nilai alamat desimal 173

10... 29

Gambar 4.13. Hasil simulasi blok pengontrol segitiga dengan nilai satu pada port control 31

Gambar 4.14. Blok pengontrol gelombang segiempat ……….….………...

31

Gambar 4.15. Hasil simulasi pengontrol segiempat dengan nilai nol pada port control

32

Gambar 4.16. Hasil simulasi pengontrol segiempat dengan nilai satu pada port control

32

Gambar 4.17. Blok pengontrol output ………...

33

Gambar 4.18. Hasil simulasi pengontrol output dengan nilai nol pada port control

33

Gambar 4.19. Hasil simulasi pengontrol output dengan nilai satu pada port control

33

Gambar 4.20. Gambar blok register output ……….…...

34

Gambar 4.21. Hasil simulasi dari blok register output………... 34

Gambar 4.22. Hasil simulasi pembangkitan gelombang sinus ……….…

35

Gambar 4.23. Hasil simulasi pembangkitan gelombang sinus pada rentang frekuensi 0 µS

250 µS dengan nilai tuning word 00000001

2………

36

Gambar 4.24. Representasi grafis dari bentuk gelombang sinus dengan tuning word sebesar

00000001

2.………... 37

Gambar 4.25. Hasil simulasi pembangkitan gelombang sinus dengan kenaikan frekuensi

sebesar nilai biner 10 atau setara dengan desimal dua...

38

Gambar 4.26. Representasi grafis dari bentuk gelombang sinus dengan tuning word sebesar

00000010

2... 39

Gambar 4.27. Representasi grafis bentuk gelombang sinus pada tuning word 00010000

240

Gambar 4.28. Representasi grafis bentuk gelombang sinus pada tuning word 00100000

241

Gambar 4.29. Representasi grafis bentuk gelombang sinus pada tuning word 10000000

241

Gambar 4.30. Rangkaian pencacah biner 8 bit...

42

Gambar 4.31. Titik awal dalam satu periode clock keluaran dari pembagi frekuensi

42

Gambar 4.32. Titik akhir dalam satu periode clock keluaran dari pembagi frekuensi

43

Gambar 4.33. Titik awal pada satu periode gelombang sinus dengan nilai tuning word

00000001

2... 43

Gambar 4.34. Titik akhir dalam satu periode gelombang sinus dengan nilai tuning word

00000001

2...43

Gambar 4.35. Hasil simulasi pembangkitan gelombang segitiga...

45

heksadesimal... 46

Gambar 4.38. Hasil simulasi gelombang segitiga saat proses penambahan...

46

Gambar 4.39. Hasil simulasi gelombang segitiga saat proses pengurangan………..

47

Gambar 4.40. Kesalahan pada nilai sub saat proses pembentukan gelombang segitiga... 48

Gambar 4.41. Perbesaran gambar dari hasil simulasi pada gambar 4.40………

48

Gambar 4.42. Representasi grafis gelombang segitiga dengan tuning word 00000010

2... 49

Gambar 4.43. Hasil simulasi pembentukan gelombang kotak………....

50

Gambar 4.44 Hasil simulasi pembentukan gelombang kotak dengan tuning word sebesar

00000010

2……… 51

Gambar 4.5

Hasil simulasi ulang terhadap pembentukan gelombang kotak……..

51

BAB I

PENDAHULUAN

1.1 Latar Belakang Masalah

Kemampuan untuk membangkitkan dan mengendalikan bentuk gelombang dalam

berbagai nilai frekuensi sudah menjadi kebutuhan yang sangat penting dalam berbagai

bidang dan aplikasi, seperti bidang medis, telekomunikasi maupun industri.

Pembentukan sinyal secara analog memiliki banyak kekurangan, diantaranya

adalah sifatnya yang sangat rentan terhadap derau. Masalah ini dapat ditangani dengan

pembentukan sinyal secara digital. Pembentukan sinyal secara digital memiliki beberapa

keunggulan, diantaranya adalah ketahanan sinyal

output

terhadap derau, dan proses

switching

frekuensi

output

yang cepat [4].

Salah satu metode pembentukan sinyal secara digital yang cukup banyak

diaplikasikan adalah metode

Direct Digital Synthesis

(DDS). Ini dikarenakan metode DDS

dapat dikembangkan pada sebuah IC (

Integrated Circuit

) tunggal yang dapat menghasilkan

gelombang

output

analog terpogram dengan sederhana dan dengan tingkat ketepatan dan

resolusi yang tinggi [4].

Dengan metode DDS, dapat dibangkitkan fungsi gelombang keluaran yang

bermacam-macam selain sinus, sehingga DDS dapat dimanfaatkan dalam suatu generator

fungsi yang membangkitkan bermacam-macam fungsi [7].

1.2

Tujuan dan Manfaat Penelitian

Tujuan yang akan dicapai, yaitu merancang pembangkit gelombang sinus, segitiga

dan kotak secara digital menggunakan metode

Direct Digital Synthesis

, dengan berbasis

CPLD.

Manfaat yang dapat dicapai, yaitu:

a.

pengembangan pengetahuan mengenai metode pembangkitan sinyal secara

digital

b.

sebagai bahan untuk pengembangan dan aplikasi pembangkitan sinyal dalam

1.3

Batasan Masalah

Dalam perancangan dan simulasi ini memiliki batasan sebagai berikut:

a.

Bentuk gelombang yang dibangkitkan adalah gelombang sinus, kotak dan

segitiga

b.

Nilai frekuensi gelombang dapat diubah secara digital dan amplitudo

gelombang dapat diubah secara analog.

c.

Perancangan dan simulasi menggunakan perangkat lunak Altera Max+plus

II 10.2.

1.4

Metodologi Penelitian

a.

Metodologi yang digunakan penulis dalam penelitian adalah sebagai

berikut:

b.

Mengumpulkan referensi dan literatur dari buku-buku perpustakaan dan

sumber dari internet.

c.

Menyusun referensi dari literatur yang ada.

d.

Perancangan dan pembuatan simulasi menggunakan perangkat lunak.

e.

Pengujian simulasi bentuk gelombang

f.

Penyusunan laporan

1.5

Sistematika Penulisan

Penulis menggunakan sistematika penulisan sebagai berikut:

BAB I

Berisi latar belakang masalah, tujuan dan manfaat dari penelitian,

batasan masalah, metodologi penelitian, dan sistematika penulisan.

BAB II

Berisi dasar teori tentang blok dasar dari arsitektur

Direct Digital

Synthesis

, mekanisme pengubahan frekuensi pada DDS, dan konsep

perancangan sistem digital menggunakan Altera Max+Plus II.

BAB III

Berisi rancangan simulasi yang dibuat, meliputi blok diagram, bagan alir

program (

flow chart

), dan penjelasan singkat tentang cara kerjanya.

BAB IV

Bab ini berisi data hasil perancangan dan simulasi dan pengamatan

terhadap hasil rancangan.

BAB II

DASAR TEORI

2.1 Metode

Direct Digital Synthesis

Direct Digital Synthesis

adalah metode pembentukan gelombang secara digital [5].

Dinamakan

Direct Digital Synthesis

atau disingkat dengan nama DDS, karena metode ini

membangkitkan sinyal digital secara langsung, tanpa memerlukan proses

sampling

dan

kuantisasi dari masukan sinyal analog [5].

Metode DDS dapat membangkitkan bentuk gelombang yang nilai frekuensi

maupun amplitudonya dapat diubah-ubah, dengan menerapkan sinyal

clock

yang

berfrekuensi tetap. Blok diagram dari arsitektur

Direct Digital Synthesis

tampak seperti di

bawah ini.

Gambar 2.1

Diagram blok dari arsitektur DDS

∑

regist

er

input

sine

look

up

table

regi

ster

out

put

Clock

Tuning

Word

M

Output/

DAC

Rangkaian penambah

Komponen pokok dari arsitektur DDS terdiri dari sebuah akumulator fasa atau

rangkaian penjumlah, sebuah konverter amplitudo (

look up table

untuk pembangkitan

gelombang sinus),

clock, tuning word

, dan sejumlah register [4] seperti yang tampak pada

gambar 2.1.

Dalam hal pembangkitan gelombang sinus, DDS menghasilkan gelombang sinus

pada frekuensi yang ditetapkan. Nilai frekuensi ini tergantung pada dua variabel, yaitu

frekuensi

clock

referensi dan bilangan biner yang diprogram ke dalam register pengatur

frekuensi (

tuning word

M).

Bilangan biner pada register frekuensi memberikan masukan ke akumulator fasa

sebuah alamat bagi

look-up table

, yang mana akan menghasilkan nilai digital dari

amplitudo gelombang keluaran.

Untuk menghasilkan gelombang sinus pada frekuensi tertentu, sebuah nilai konstan

(kenaikan nilai fasa pada register masukan) ditambahkan ke akumulator pada setiap siklus

clock

[4]. Bila kenaikan nilainya besar, akumulator akan melakukan

step

yang sangat cepat

melalui

look-up table

gelombang sinus, dan kemudian menghasilkan gelombang sinus

berfrekuensi tinggi. Sebaliknya, bila kenaikan bilangannya kecil, maka akumulator akan

melakukan

step

yang lebih banyak, sehingga akan menghasilkan gelombang sinus dengan

besar frekuensi yang lebih lambat [4].

2.1.1 Akumulator

Akumulator di sini sebenarnya merupakan sebuah rangkaian penambah/pengurang

komplemen 2 yang menaikkan/menurunkan nilai yang disimpannya setiap saat ia

menerima masukan. Besarnya nilai kenaikan ditentukan oleh nilai sebuah

word

digital M

yang berada pada register masukan yang dijumlahkan dengan

output

dari pencacah itu

sendiri.

Word

digital pada register masukan membentuk ukuran langkah pada setiap

clock

-nya. Sebagai contoh, untuk akumulator dengan lebar data N=32 bit, sebuah nilai M

0000....00001 (ekivalen dengan nilai satu) akan menghasilkan akumulator yang mengalami

overflow

setelah 2

32siklus

clock

referensi (kenaikan). Bila nilai M diubah menjadi

0111....1111, akumulator akan mengalami

overflow

setelah hanya 2

1siklus

clock

, atau dua

siklus

clock

referensi. Pengontrolan dari ukuran langkah ini membentuk sebuah pengaturan

frekuensi dari arsitektur DDS.

Hubungan dari akumulator dengan register masukan membentuk persamaan dasar

dari pengaturan frekuensi pada DDS:

F

OUT=(M(CLKreferensi))2N (2.1)

Dengan: F

OUT= frekuensi keluaran dari DDS

M =

word

biner pengatur frekuensi

CLK referensi = frekuensi

clock

internal (

system clock

)

N = panjang bit dari akumulator

2.1.2

ROM

Look Up Table

ROM

Look Up Table

merupakan ROM (

Read Only Memory

) yang menyimpan

akan dibangkitkan [4]. Besar kecilnya langkah fungsi sinus yang diprogram pada ROM

Look Up Table

ini akan memiliki pengaruh besarnya frekuensi gelombang keluaran.

2.1.3

Register

Parallel In Parallel Out

Register

Parallel In Parallel Out

atau disingkat dengan nama PIPO adalah register

yang memasukkan data biner pada setiap pin

inpu

t-nya secara bersamaan pada satu

clock

[3]. Dan mengeluarkan data biner pada pin

output

-nya secara bersamaan pula pada satu

clock

. Contoh skema register PIPO empat bit ditunjukkan pada gambar 2.2.

FF1

FF2

FF3

FF4

clock

input

1

input

2

input

3

input

4

output

1

output

2

output

3

output

4

Gambar 2.2

Contoh blok rangkaian register PIPO

2.1.4 Penambah/Pengurang Komplemen 2

Rangkaian dari penambah/pengurang yang didasarkan pada komplemen 2

ditunjukkan pada gambar 2.3.

FA

FA

FA

FA

INV

INV

INV

INV

SUBA1

A2

A3

A4

B1 B2 B3 B4

C

S1 S2 S3 S4

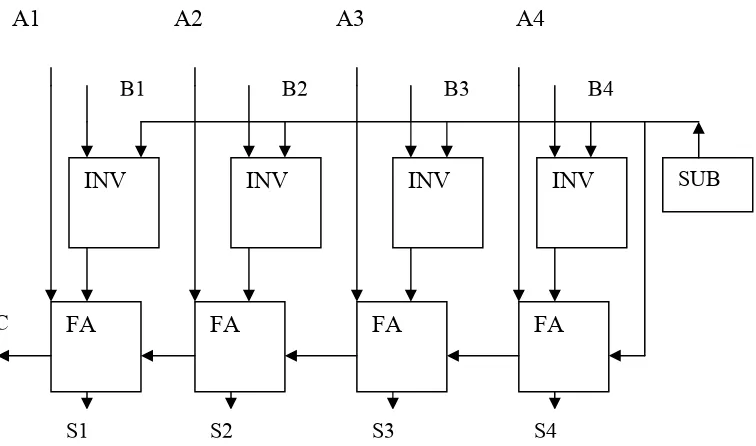

Pada gambar2.3, terdapat beberapa blok. Blok A1-A4 merupakan bilangan biner

yang akan ditambahkan. Blok B1-B4 adalah bilangan penambah. Blok FA merupakan blok

Full Adder

atau penambah penuh. Blok S1-S4 adalah blok bilangan biner

output

. Blok

INV adalah blok

inverter

atau pembalik. blok INV ini dapat diaplikasikan menggunakan

sebuah gerbang XOR dua masukan [3].

Bila nilai Sub berlogika rendah, maka bit-bit B lewat melalui

inverter

terkendali ke

penambah penuh. Nilai Sub di sini merupakan pengendalinya. Oleh karenanya, penambah

penuh menghasilkan jumlah A dan B. Sebagai contoh, jika A=1001 (nilai desimal = 9), dan

B=0011 (nilai desimal = 3), jumlah desimal dan binernya adalah 1100 (nilai desimal = 12).

Sebaliknya, bila Sub berlogika tinggi, maka bit-bit B akan dibalik sebelum

mencapai penambah penuh. Di samping itu, Sub yang bernilai tinggi menambahkan 1

kepada penambah pertama. Penambahan 1 ini membentuk komplemen 2 bagi B. Dengan

kata lain,

inverter

terkendali menghasilkan komplemen 1, dan menambahkan nilai satu

pada

full adder

LSB sehingga menghasilkan komplemen 2. Dengan demikian, keluaran

penambah penuh merupakan selisih antara A dan B. Sebagai contoh, dengan A dan B yang

sama seperti yang digunakan pada contoh sebelumnya, dengan menggunakan penjumlahan

komponen 2, akan dilakukan penambahan. Namun sebelumnya B=0011 diubah ke

komplemen 2-nya menjadi 1101. Hasil penambahan A (1001) dan komplemen 2 dari B

(1101) adalah 0110, yang setara dengan nilai desimal 6. Hasil penambahan komplemen 2

tersebut ekivalen dengan proses pengurangan antara A dengan B.

2.1.5 Mekanisme Pengubahan Frekuensi

Frekuensi keluaran DDS tergantung pada tiga hal yaitu: frekuensi

clock

acuan,

besarnya langkah sinus yang diprogram pada LUT, dan nilai pengubah frekuensi (

tuning

word

). Frekuensi keluaran dapat diubh dengan metode pengubahan laju

sampling

yang

dilakukan dengan cara mengubah-ubah nilai

tuning word

[4].

Pada teknik pengubahan laju

sampling

, sebagian atau seluruh isi LUT dialamati

dengan frekuensi

clock

acuan yang konstan dengan langkah pengalamatan yang berubah.

Gambar 2.4 menunjukkan laju

sampling

. Langkah pengalamatan LUT tergantung pada

nilai dari data pengatur frekuensi

tuning word

. Frekuensi keluaran memiliki hubungan

yang linear terhadap data pengatur.

Bagian dari skema pengubahan frekuensi dengan metode pengubahan laju

sampling

Akumulator Fasa

Look Up Table

Clock Acuan

Tuning

Word

(M)

Gambar 2.4

Teknik pengubahan laju frekuensi

2.1.6

Digital To Analog Converter

Pengubahan nilai digital ke nilai ekivalen analognya dilakukan menggunakan

Digital to Analog Converter

. Salah satu model DAC yang banyak digunakan adalah model

R-2R

Ladder

, seperti yang ditunjukkan pada gambar 2.2.

Masukan b(1) sampai b(n) adalah bit digital dengan b(1) sebagai

Least Significant

Bit

(LSB) dan b(n) sebagai

Most Significant Bit

(MSB). Masukan data digital diubah

menjadi nilai tegangan sebagai keluaran. Rangkaian ini hanya membutuhkan dua nilai

resistor

dimana salah satunya adalah dua kali nilai

resistor

lainnya.

Pengubahan nilai digital ke analog pada metode R-2R

Ladder

direpresentasikan

dengan persamaan (2.2)

∑

=⎟

⎠

⎞

⎜

⎝

⎛

−

+

−

+

+

=

+

−

=

n in

b

n

b

n

b

Vr

n

i

n

b

Vr

Vout

12

)

1

(

...

8

)

2

(

4

)

1

(

2

)

1

(

(2.2)

Dengan V

r= nilai tegangan referensi

n = jumlah bit nilai digital

V

out= nilai tegangan keluaran

2.2 Konsep Perancangan Sistem Digital dengan Menggunakan Altera

Max+PlusII

Dalam suatu konsep perancangan sistem digital terdapat dua konsep perancangan,

yaitu konsep

top-down

dan

bottom-up

[2].

Konsep perancangan

top-down

dimulai dengan deskripsi fungsi rangkaian secara

keseluruhan. Kemudian rangkaian secara keseluruhan ini dibagi-bagi menjadi rangkaian

yang lebih kecil.

Konsep perancangan

bottom-up

dimulai dari pendefinisian fungsi rangkaian secara

global, tapi dalam mempartisi rangkaian, perancang berpedoman pada komponen yang

tersedia, sehingga kebebasan perancangan menjadi terbatas.

Pada perancangan menggunakan dengan menggunakan HDL (

Hardware

Description Language

), pada tahap pembuatan program agar memenuhi deskripsi

spesifikasi yang ditentukan, sistem yang akan dibuat dibagi-bagi menjadi modul-modul

yang lebih kecil. Pada tahapan ini, perancangan yang dilakukan menggunakan pendekatan

top-down

. Pada saat implementas ukuran PLD membatasa kebebasan pemilihan komponen

yang digunakan. Pada tahap ini, perancangan yang dilakukan harus disesuaikan dengan

komponen yang tersedia, sehingga sesuai dengan uraian sebelumnya, pendekatan yang

digunakan pada tahap ini adalah

bottom-up

.

Altera Max+Plus II dipakai untuk perancangan logika dengan divais target yang

dapat diprogram dari Altera, meliputi keluarga divais Classic, MAX 5000, MAX 7000,

MAX 9000, FLEX 6000, FLEX 8000, dan FlEX 10K. Max+Plus II menyediakan

kemampuan perancangan logika: metoda

design entry

yang bermacam-macam untuk

simulasi fungsional dan pewaktuan, simulasi untuk multi divais, analisis pewaktuan, lokasi

kesalahan otomatis, dan pemrograman dan verifikasi.

Max+Plus II bisa membaca dan menulis berkas AHDL dan berkas netlist EDIF

standar, berkas HDL Verilog, VHDL, dan berkas skematik ORCAD.

Tahap-tahap perancangan dengan Max+Plus II adalah:

design entry, compilation,

simulation, timing analysis, dan device programming.

2.3

Complex Programmable Logic Device

CPLD atau

Complex Programmable Logic Device

adalah salah satu kelas dari

Programming Logic Device

(PLD). PLD sendiri terdiri dari beberapa kelas, yaitu FPGA

(

Field Programmable Gate Arrays

), PLA (

Programmable Array Logic

), PROM

(

Programmable Read Only Memories

), PAL (

Programmable Logic Array)

, GAL (

Generic

Array Logic

) dan yang terakhir adalah CPLD.

PLD adalah devais yang memiliki arsitektur yang sudah di pre-definisi secara

umum dimana pengguna dapat memprogram sebuah desain ke dalamnya menggunakan

seperangkat tool. Arsitektur umumnya dapat bermacam-macam namun terdiri dari satu

atau lebih term AND dan OR untuk mengimplementasikan fungsi logika. Banyak devais

yang juga memiliki kombinasi dari flip-flop dan

latch

(pengunci) yang dapat digunakan

sebagai elemen penyimpan untuk

input

dan

output

bagi devais tersebut. Devais yang lebih

kompleks terdiri dari

macrocell

.

Macrocell

memungkinkan pengguna untuk

mengkonfigurasi tipe

input

dan output yang dibutuhkan desain.

CPLD dikategorikan sebagai PAL yang sangat besar yang memiliki karakteristik

dari PLA. Arsitektur dasarnya bnyak memilikia kemiripan dengan PAL. CPLD memiliki

tingkat kompleksitas di antara PAL dan FPGA, namun secara arsitektural, CPLD memiliki

BAB III

PERANCANGAN PEMBANGKIT BENTUK

GELOMBANG

3.1 Perancangan Arsitektur Pembangkit Gelombang.

Pembangkit bentuk gelombang yang akan dirancang adalah rangkaian elektronika

yang dapat menghasilkan bentuk gelombang keluaran yang memiliki frekuensi dan

amplitudo yang dapat diatur. Pengaturan frekuensi dilakukan secara digital melalui

pengubahan

tuning word

pada bagian masukan awal dari konfigurasi pembangkit

gelombang..

DDS digunakan sebagai metoda untuk membangkitkan gelombang keluaran.

Diagram blok dasar dari metoda DDS sudah ditunjukkan pada gambar 2.1

Diagram blok yang lebih detail dari arsitektur pembangkit bentuk gelombang

dengan metoda

Direct Digital Synthesis

ditunjukkan pada gambar 3.1

Register

input

pada gambar 3.1 merupakan bagian masukan utama. Register

input

ini berfungsi sebagai penyimpan

tuning word

yang nantinya akan difungsikan sebagai

pengatur frekuensi gelombang keluaran. Keluaran dari register

input

akan dimasukkan ke

rangkaian akumulator.

Bagian akumulator dan register fasa bisa dianggap sebagai satu blok, karena dua

bagian ini sangat berperan penting dalam proses pembentukan gelombang. Bila

akumulator tidak memiliki register fasa, akan terjadi kekeliruan perhitungan karena tidak

ada media penyimpan yang bekerja berdasarkan siklus

clock

sumber.

Keluaran akumulator kemudian akan diteruskan ke pengontrol gelombang segitiga

terlebih dahulu. Pada pengontrol inilah ditentukan kemana sinyal akan dilewatkan. Bila

diteruskan ke ROM, maka proses selanjutnya adalah pembangkitan gelombang sinus. Bila

diteruskan ke pengontrol gelombang segi empat, maka ada dua kemungkinan yang akan

terjadi. Bila pengontrol gelombang segi empat dalam keadaan tidak aktif, maka sinyal akan

diteruskan ke pengontrol

output

. Bila pengontrol segi gelombang empat aktif, maka

sebagian sinyal akan ditahan, dan MSB dari keluaran akumulator akan diambil untuk

membangkitkan bentuk gelombang segi empat.

Pengontrol

output

berfungsi untuk memilih sinyal yang akan diteruskan ke register

output

. Bila pengontrol gelombang segitiga aktif, pengontrol

output

pun ikut aktif,

sehingga isi alamat ROM tidak akan diteruskan ke register

output

. Sebaliknya bila

pengontrol segitiga aktif, maka pengontrol

output

pun tidak akan aktif, sehingga proses

pembentukan gelombang sinus dapat dikerjakan.

3.1.1 Perancangan Register

Input

Perancangan Register

Input

dilakukan dengan menggunakan VHDL. Bentuk

deskripsi yang akan digunakan pada perancangan register

input

adalah deksripsi

behavioral,

bukan deskripsi struktural.

Masukan dari register input adalah DIP

switch

yang

terdapat pada papan UP1 Board. Jumlah DIP

switch

yang tersedia adalah sebanyak 8 buah.

Jumlah itu sudah sesuai dengan perancangan

tuning word

yang juga sebanyak 8 bit.

3.1.2 Perancangan Blok Akumulator Fasa

Bagian akumulator fasa terdiri dari

adder

/penambah dan register fasa.

Adder

di sini

rangkaian penambah lagi untuk membangkitkan bentuk gelombang segitiga dan kotak.

Bagian

adder

dan register fasa juga memiliki lebar data sebesar 8 bit. Penentuan lebar data

yang juga sebesar 8 bit ini berkaitan dengan proses untuk menentukan frekuensi

gelombang keluaran.

Penentuan frekuensi gelombang keluaran yang diinginkan ditentukan dengan

perumusan seperti yang sudah ditunjukkan pada persamaan (2.1)

Pada penelitian ini,

word

biner pada persamaan (2.1) pengatur frekuensi M

memiliki panjang bit yang sama dengan panjang bit dari akumulator fasa, di mana

keduanya memiliki panjang sebesar 8 bit.

3.1.3 Perancangan Blok ROM Sinus

Bagian ROM sinus memiliki lebar data sebesar 8 bit. Hal ini berarti bahwa jumlah

data yang akan dikonversikan untuk membentuk gelombang sinus dengan frekuensi

terkecil adalah sebanyak 256 buah.

Untuk memperoleh nilai desimal dari fungsi sinus dengan jumlah data sebanyak

256 buah ini, dapat dilakukan perhitungan dengan menggunakan rumus:

⎟

⎠

⎞

⎜

⎝

⎛

+

⎟

⎠

⎞

⎜

⎝

⎛

Π

⎟

⎠

⎞

⎜

⎝

⎛

=

2

*

256

*

2

sin

*

2

_

data

referece

step

reference

DEC

(3.1)

Nilai desimal yang dihasilkan oleh persamaan (3.2) di atas kemudian dikonversikan ke

nilai heksadesimalnya dengan bantuan

software

MATLAB. Sintaks dalam MATLAB

untuk mengkonversikan nilai desimal ke-256 data tadi ke nilai heksadesimalnya

ditunjukkan pada gambar 3.3.

Sintaks pada gambar 3.2 tersebut menghasilkan nilai heksadesimal yang ekivalen dengan

nilai desimalnya. Nilai-nilai heksadesimal hasil dari konversi tersebut ditunjukkan pada

gambar 3.3

Gambar 3.3

Nilai heksadesimal bagi nilai amplitudo gelombang sinus

Nilai-nilai heksadesimal yang disimpan pada ROM merupakan nilai ekivalen dari

amplitudo analog gelombang sinus yang akan dibangkitkan. Nilai-nilai ini diakses sesuai

dengan keluaran dari akumulator fasa.

3.1.4 Perancangan Pengontrol Gelombang Segitiga

Blok ini merupakan persimpangan sinyal sebelum sinyal mengalami proses lebih

lanjut. Keadaan nol pada

port

control

pada pengontrol segitiga akan mengakibatkan

pengontrol melewatkan sinyal menuju ROM. Sebaliknya, bila nilai

port control

adalah

satu, maka pengontrol segitiga akan memproses sinyal masukan untuk membentuk sinyal

segitiga. Sama halnya dengan bagian register

input,

bagian inipun akan dirancang dengan

3.1.5 Perancangan Pengontrol Gelombang Segi Empat

Bagian ini menentukan cara pembentukan gelombang segi empat atau kotak. Bila

keadaan

port

pengontrol dalam taraf nilai nol, maka pengontrol akan melewatkan bit-bit

sinyal dari pengontrol segitiga menuju pengontrol

output

. Sebaliknya bila keadaan

port

pengontrol dalam taraf nilai satu, maka MSB dari keluaran pengontrol segitiga saja yang

akan dilewatkan, sehingga bit-bit lainnya selain bit MSB tak akan dilewatkan. Bagian

pengontrol gelombang segi empat inipun akan dirancang secara

behavioral

.

3.1.6 Perancangan Pengontrol

Output

Bagian ini akan menentukan apakah keluaran dari ROM sinus ataukah keluaran

dari pengontrol segiempat yang akan dilewatkan. Dengan demikian, bagian pengontrol

output

ini akan memiliki 16

port

masukan, yang terdiri dari 8

port

masukan dari ROM, dan

8

port

lainnya dari pengontrol gelombang segitiga.

Bila pengontrol

output

dalam keadaan aktif, maka sinyal yang akan dilewatkan

adalah sinyal dari pengontrol segitiga. Sedangkan bila pengontrol dalam keadaan tidak

aktif, maka nilai-nilai yang ada di alamat-alamat di dalam ROM lah yang akan diberi akses

ke register

output.

Bagian pengontrol output inipun akan dirancang menggunakan deskripsi

behavioral.

3.1.7 Perancangan Register

Output

Perancangan

bagian

register

output

ini sama persis dengan perancangan register

input

maupun register fasa. Perbedaan hanyalah ada di

port-port

yang akan dipasang, yang

berfungsi sebagai ujung keluaran proses pembangkitan gelombang.

3.1.8 Perancangan Blok

Digital to Analog Converter

Devais DAC yang digunakan pada perancangan ini adalah DAC0823. Pengaturan

amplitudo dari gelombang keluaran dilakukan pada bagian DAC ini dengan cara

mengubah-ubah V referensi pada DAC tersebut. DAC0832 adalah DAC 8 bit. Rentang

nilai V

ref

DAC0832 adalah ±10V. Pengubahan nilai amplitudo gelombang keluaran

dilakukan dengan melakukan pengubahan nilai V

ref

dalam rentang nilai tersebut.

Pengubahan nilai amplitudo dengan cara mengubah-ubah nilai Vref ini seseuai dengan

teori pengubahan nilai digital ke analog dengan menggunakan metode R-2R

Ladder

yang

Pengubahan nilai amplitudo dengan cara mengubah-ubah V

ref

pada metode R-2R

Ladder

ini didasarkan pada fakta bahwa rangkaian DAC internal pada

chip

DAC0832

merupakan rangkaian DAC R-2R

Ladder

.

Gambar 3.4

Skema rangkaian DAC

Keluaran dari DAC0832 masih berupa besaran arus, maka perlu ditambahkan

op-amp pada keluarannya. Gambar rangkaian DAC top-ampak seperti di gambar 3.4.

Penggambaran blok DAC pada gambar 3.4 disesuaikan dengan petunjuk yang

tertera pada

datasheet

-nya. Pada gambar ini hanya ditambahkan sebuah potensiometer

sebagai pembagi tegangan, yang akan difungsikan sebagai pengatur amplitudo bentuk

gelombang keluaran.

Data masukan DAC0832 merupakan keluaran dari register

output

, yang berjumlah

8 bit. Potensiometer yang digunakan sebagai pembagi tegangan adalah potensiometer

10K

Ω

. Dan opamp yang digunakan adalah dari seri LF351. Penggunaan op-amp seri

LF351 juga disesuaikan dengan

datasheet

DAC0832.

RFB pada gambar blok DAC0832 merupakan resistor

on-chip

. Resistor RFB

tersebut sudah tersedia secara internal pada keping DAC0832, dan bukan merupakan

resistor eksternal. RFB ini merupakan resistor feedback yang digunakan untuk aplikasi

op-amp eksternal mengeluarkan tegangan keluaran dari DAC.

3.2 Metode Pembentukan Gelombang Sinus

Langkah pertama dalam pembentukan gelombang sinus adalah pemberian dan

menjadi masukan bagi

adder

/penambah dan register fasa yang merupakan bagian

pembentuk akumulator fasa.

Loop

terjadi di dalam akumulator fasa ini. Aktifitas yang

terjadi pada loop ini adalah penambahan bilangan biner yang akan mengalamati ROM

Look Up Table

. Alamat-alamat yang dituju pada ROM tersebut memberikan nilai

ekuivalen bagi amplitudo bentuk gelombang yang akan dibangkitkan. Diagram alir utama

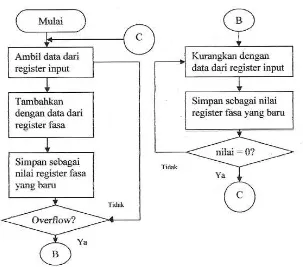

dari metode pembentukan gelombang sinus tampak pada gambar 3.6

Gambar 3.5

Diagram alir utama pembentukan gelombang sinus

Penjelasan dari proses keseluruhan yang terjadi dalam diagram alir tersebut sudah

dijelaskan sebelumnya.

Dari diagram alir yang menggambarkan proses secara umum pada gambar 3.5,

terdapat suatu proses looping.

Looping

ini adalah proses yang terjadi di dalam blok

akumulator fasa. Langkah awal dari proses looping ini adalah pengambilan data dari

register

input

. Data biner dari register

input

tadi dimasukkan ke dalam

adder

/penambah.

Keluaran dari penambah tersebut kemudian diberikan kepada register fasa. Seperti yang

yaitu blok adder/penambah, ROM

Look Up Table

, dan register

output

. Dalam

hubungannya dengan proses looping ini pada pembentukan gelombang sinus, ini, tujuan

dari keluaran fasa adalah ROM

Look Up Table

dan blok

adder

. Nilai keluaran dari register

fasa ditambahkan dengan nilai keluaran dari register

input

. Hasil penambahan dikrimkan

ke ROM dan sekaligus juga dimasukkan kembali menjadi

input

dari

adder

. Proses ini terus

berulang sampai proses penambahan mengalami

overflow

. Saat terjadi

overflow

, satu siklus

gelombang sinus telah terbentuk. Saat

overflow

, akumulator sudah mencapai nilai data

maksimum yang dapat dihasilkan. Langkah selanjutnya adalah akumulator kembali

melakukan proses penambahan dengan memulai dari nilai data terkecil pada register fasa.

Dan register fasa kembali mengalamati ROM dari nilai biner terkecil untuk membangkit

siklus selanjutnya.

Diagram alir dari proses looping yang terjadi pada blok akumulator fasa

ditunjukkan pada gambar 3.6

Gambar 3.6

Diagram alir dari proses looping

3.3 Metode Pembentukan Gelombang Segitiga

Untuk

membangkitkan

gelombang

segitiga, tidak diperlukan ROM khusus. Proses

pembentukan gelombang segitiga ini memanfaatkan keluaran akumulator fasa. Namun

sebelumnya, akumulator fasa perlu dimodifikasi supaya bisa membangkitkan gelombang

Yang perlu dilakukan adalah penambahan kontrol supaya akumulator fasa dapat

melakukan proses pengurangan. Jadi setiap saat proses penambahan mencapai kondisi

overflow

, akumulator fasa tidak langsung kembali melaukan penambahan dari nilai biner

terkecil, namun ia melakukan proses pengurangan sampai nilai data biner pada keluaran

akumulator fasa kembali ke nilai terkecilnya.

Seperti yang sudah dijelaskan, rangkaian

adder

yang digunakan pada arsitektur ini

adalah rangkaian penambah/pengurang komplemen2. Sehingga tidak memerlukan

rangkaian pengurang lagi. Diagram alir dari pengontrolan akumulator fasa ditunjukkan

pada gambar 3.7.

Gambar 3.7

Diagram alir pengontrolan dalam pembentukan gelombang segitiga

Seperti yang tampak pada gambar, siklus dalam proses penambahan dan

pengurangan dalam pembentukan sinyal segitiga terus berulang.

Keluaran dari akumulator fasa pada proses ini tidak diarahkan ke ROM, melainkan

nantinya akan langsung ditujukan ke register

output

sebelum terlebih dahulu dilewatkan

melalui pengontrol segitiga dan pengontrol segi empat. Hal ini dikarenakan hasil

penambahan dan pengurangan pada akumulator fasa akan berbentuk garis naik linier saat

Penentuan frekuensi pada proses pembentukan gelombang segitiga ini tetap

mengandalkan nilai

tuning word

yang dimasukkan pada awal konfigurasi aristektur

pembentuk gelombang.

3.4 Metoda Pembentukan Gelombang Kotak

Untuk membangkitkan gelombang kotak, prosesnya sama saja dengan cara

pembentukan gelombang segitiga. Hanya saja, pada proses ini ditambahkan pengontrol lagi

supaya nilai biner dari keluaran akumulator fasa tidak semuanya dikirimkan ke register

output

. Yang perlu diambil dari keluaran akumulator fasa hanyalah bagian MSB dari

bilangan biner yang dihasilkan. Diagram alir dari pembentukan sinyal kotak ditunjukkan

pada gambar 3.8.

Gambar 3.8

Diagram alir dari pembentukan gelombang kotak

Pada pembentukan gelombang kotak ini, nilai MSB dari bilangan biner yang

dihasilkan oleh akumulator fasa otomatis sudah membentuk nilai ekuivalen bagi

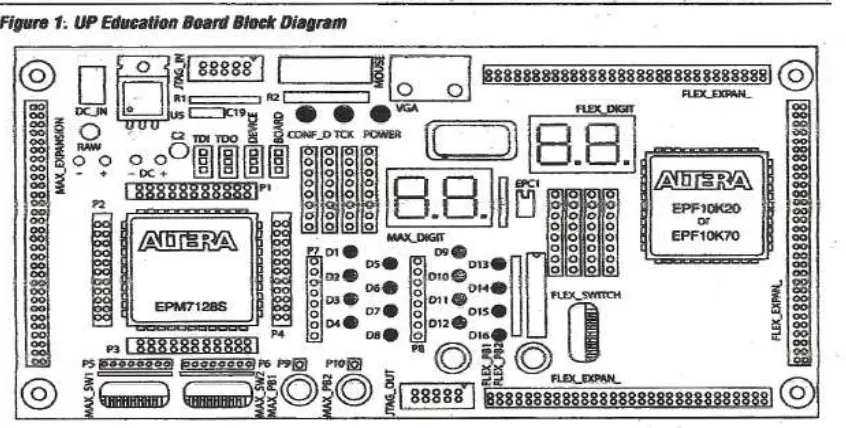

3.5 Pin Pengontrol, Pin Masukan dan Pin Keluaran pada

UP1 Board

Flex_Expan_B yang memiliki jumlah total 60

pin

akan dimanfaatkan sebagai

keluaran register

output,

dan sebagai

port

masukan dari pengontrol gelombang segitiga dan

gelombang kotak. Gambar dari

UP1 Board

ditunjukkan pada gambar 3.9

Gambar 3.9

Blok diagram dari UP1 Board

Tidak semua port dari Flex_Expan_B akan digunakan. Keluaran dari register

output berjumlah 8 bit, maka untuk keperluan ini hanya akan digunakan 8 pin dari

Flex_Expan_B. Dan untuk keperluan pengontrol bentuk gelombang kotak dan segitia,

diperlukan 2 pin lagi sebagai masukan dari sakral pengontrol. Gambar 3.10 memberikan

detail skema pin keluaran dan pin pengontrol.

Pin-pin yang akan digunakan adalah pada bagian FLEX_EXPAN_B. Pin dengan nomor

15, 17, 19, 21, 23, 25, 27, 29 digunakan sebagai pin keluaran, yang terhubung pada kaki

input dari IC DAC0832. Sementara pin dengan nomor 31, dan 33 akan digunakan sebagai

pin masukan yang terhubung dengan saklar pengatur gelombang segitiga.

3.6 Penggunaan

Flex_Switch

Pada Papan

UP1 Board

Untuk memasukkan nilai tuning word pada blok DDS, maka digunakan flex switch

yang sudah terdapat pada papan

UP1 Board

. Gamar dari flex switch yang akan digunakan

ditunjukkan pada gambar 3.11

.

Gambar 3.11

Bagian

Flex-Switch

yang akan digunakan sebagai input

tuning word

3.7 Perancangan Pembagi Frekuensi.

Untuk mendapatkan frekuensi dasar pada kisaran frekuensi audio, maka akan

dibangun pembagi frekuensi menggunakan serangkaian JK-Flip-Flop. Frekuensi

clock

dasar simulator adalah 5MHz. Dan frekuensi on-board pada UP1 Board bernilai 25,175

MHz.

Besarnya

clock

tersebut masih harus diperkecil. Nilai

clock

referensi yang

diinginkan bagi blok sistem adalah pada frekuensi maksimal

audio

, yaitu 20KHz.

Perancangan modul pembagi frekuensi ini nantinya akan dideskripsikan menggunakan

VHDL, sama halnya dengan perancangan pada blok utama DDS.

3.8 Perancangan Saklar Pengontrol Gelombang Segitiga dan Kotak

Untuk membentuk gelombang segitiga dan kotak, diperlukan kontrol pada blok

saklar akan mengaktifkan kontrol, dan logika rendah akan mematikan kontrol. Gambar

3.12 menunjukkan skematik rangkaiannya.

Gambar 3.12

Rangkaian saklar pengontrol

3.9

Pengimplementasian Perancangan.

Perancangan darn simulasi akan dilakukan menggunakan VHDL. Hasil dari

perancangan menggunakan VHDL ini akan di-

download

ke devais CP:D dari keluarga

BAB IV

HASIL DAN PEMBAHASAN

Dari hasil perancangan menggunakan perangkat lunak, telah dihasilkan suatu

pembentuk gelombang. Seperti yang telah dipaparkan dalam batasan masalah, yaitu bahwa

gelombang yang akan dibuat dalam penelitian ini adalah gelombang dalam bentuk sinus,

kotak, dan segitiga.

Pengujian simulasi dilakukan menggunakan

simulator

yang terdapat pada Altera

Max+Plus II yang digunakan untuk membuat pembangkit gelombang. Hampir semua hasil

perancangan berjalan dengan baik, karena masih ditemukan beberapa hal yang tampak

tidak sesuai dengan perancangan.

Hasil dari gelombang keluaran bisa diuji, baik dari bentuk gelombang itu sendiri,

maupun efek perubahan nilai frekuensinya. Hal ini bisa dilakukan bila aplikasi pembangkit

gelombang yang dibuat menggunakan VHDL ini, diunduh terlebih dahulu ke dalam divais

CPLD, yang kemudian bentuk gelombangnya dideteksi pada osiloskop.

Cara lain dalam upaya pengujian bentuk gelombang berikut nilai frekuensinya

adalah dengan meng-

copy

tabel hubungan antara waktu dengan nilai-nilai biner pembentuk

gelombang ke sebuah aplikasi pengolah data. Dari tabel tersebut, maka kemudian dapat

dibangkitkan sebuah grafik yang merepresentasikan korespondensi antara nilai-nilai

pembentuk amplitudo gelombang dalam hubungannya dengan waktu.

Namun pengunduhan aplikasi pembangkit gelombang ke dalam divais CPLD

belum dapat dilakukan, sehingga dalam pembahasan ini, akan dibahas hasil-hasil pengujian

pada simulator dari masing-masing bentuk gelombang.

4.1 Pengujian

Blok-blok

Penyusun Konfigurasi Pembentuk

Gelombang

Sebelum membahas hasil simulasi dari masing-masing bentuk gelombang, terlebih

dahulu akan dibahas kinerja dari setiap blok penyusun konfigurasi pembangkit

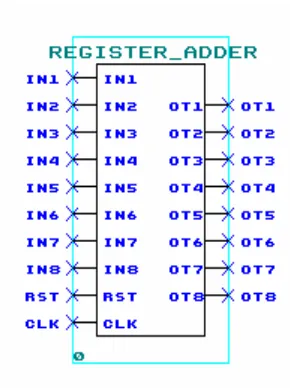

4.1.1 Pengujian Register

Input

Gambar 4.1 merupakan gambar dari blok register

input

. Di dalam blok register

input

ini terdapat deskripsi register

input

dalam bentuk deskripsi

behavioral

.

Gambar 4.1

Blok Register

Input

Blok

register

input

ini berfungsi sebagai penyimpan nilai-nilai

input

, yang

kemudian akan mengeluarkan

output

yang bersesuaian dengan

input

yang dimasukkan

pada setiap terjadi siklus

clock

.

Port

IN1

merupakan bagian LSB (

Least Significant Bit

),

sementara

port

IN8

merupakan bagian MSB (

Most Significant Bit

). Model penamaan port

ini juga berlaku pada blok lainnya.

Port input/output

dengan label ‘8’ merupakan MSB,

dan

port input/output

dengan label ‘1’ merupakan LSB. Perkecualian ada pada blok ROM,

yang akan dijelaskan pada sub bab berikutnya.

Blok register

input

ini sudah bekerja dengan baik sesuai dengan perancangan.

Gambar 4.2 menunjukkan hasil simulasi dari blok register

input

.

Gambar 4.2

Hasil simulasi dari blok register

input

Dalam gambar 4.2, ditunjukkan nilai

input

heksadesimal bernilai E0

16. Saat siklus

clock

terjadi dan

clock

bernilai satu,

port

output

mengeluarkan nilai yang sesuai dengan

masukannya, yaitu E0

16. Dengan demikian, blok register

input

sudah bekerja sesuai

4.1.2 Pengujian Blok Akumulator

Seperti yang telah dipaparkan dalam BAB III, yaitu bahwa blok akumulator dalam

konfigurasi pembentuk gelombang ini terdiri dari rangkaian penambah/pengurang

komplemen 2. Gambar 4.3 menunjukkan rangkaian dari blok akumulator.

Gambar 4.3

Rangkaian blok akumulator

Dalam gambar 4.3, ditunjukkan bahwa masukan

b8

sampai

b1

disalurkan terlebih

dahulu ke blok gerbang XOR, yang kemudian akan di-XOR-kan dengan Sub. Sementara

masukan

a8

sampai

a1

langsung dimasukkan ke blok

full-adder

. Port

b8

dan

a8

masing-masing merupakan bagian MSB, dan bagian

b1

dan

a1

masing-masing merupakan bagian

LSB. Konfigurasi yang ditampilkan dalam gambar 4.3 sudah sesuai dengan dasar teori dan

perancangan. Hasil simulasi dari cara kerja blok akumulator ditampilkan dalam gambar 4.4

dan 4.5

Gambar 4.4 menunjukkan hasil simulasi dari proses penambahan. Nilai Sub

ditetapkan pada nilai 0 supaya blok akumulator melakukan penambahan. Nilai

input

a[8..1]

ditetapkan pada nilai heksadesimal 05

16. Nilai

input

b[8..1]

yang bernilai 01

16berlaku sebagai bagian penambah. Dengan demikian, nilai input a

[8..1]

ditambah oleh

nilai input b

[8..1],

dimana nilai 05

16ditambah dengan nilai 01

16,sehingga menghasilkan

nilai

output

out

[8..1]

sebesar 06

16,dengan nilai keluaran bawaan (

carry

) sebesar 0. Gambar

4.4 menunjukkan bahwa cara kerja proses penambahan pada blok akumulator sudah

bekerja sesuai dengan perancangan.

Untuk melakukan proses pengurangan, nilai Sub ditetapkan pada nilai 1, seperti

yang telah dibahas pada ulasan perancangan pada BAB III. Gambar 4.5 menunjukkan hasil

simulasi untuk proses pengurangan.

Gambar 4.5

Hasil simulasi dari proses pengurangan

Gambar 4.5 menunjukkan bahwa proses pengurangan pada blok akumulator sudah

bekerja sesuai perancangan. Nilai

port

a

[8..1]

dengan besar bilangan heksadesimal 05

16dikurangi dengan nilai

port

b

[8..1]

dengan besar bilangan heksadesimal 01

16, yang

menghasilkan nilai

output

out

[8..1]

dengan besar bilangan heksadesimal 04

16, dan nilai

biner keluaran bawaan (

carry

)

sebesar 1

2. Proses ini sudah sesuai dengan perancangan.

Dengan demikian, blok akumulator sudah bekerja sesuai perancangan baik pada proses

penambahan maupun pada proses pengurangan.

4.1.3 Pengujian Blok Register

Adder

/Register Fasa

Register fasa berfungsi sebagai penyimpan dan penyalur nilai-nilai biner yang

dihasilkan dari tiap-tiap

port

keluaran blok

full-adder

. Prinsip kerjanya sama persis dengan

prinsip kerja register

input

, yaitu menyimpan setiap nilai biner masukan, dan menghasilkan

keluaran yang bersesuaian dengan nilai masukkannya pada setiap terjadi siklus

clock

.

Gambar 4.6

Blok register

adder

/register fasa

Register

fasa/register

adder

pada gambar 4.6 berfungsi sebagai penyimpan

nilai-nilai biner yang dikirim dari blok akumulator, yang kemudian akan disalurkan ke blok

ROM dan blok pengontrol gelombang segitiga. Gambar 4.7 menunjukkan hasil simulasi

dari cara kerja register

adder

.

Gambar 4.7

Hasil simulasi dari cara kerja register

adder

Pada gambar 4.7, ditunjukkan bahwa nilai

input

heksadesimal

in[8..1]

adalah

sebesar 55

16. Saat

clock

terjadi dan

clock

bernilai satu,

port

keluaran

ot[8..1]

menghasilkan

nilai

output

sebesar 55

16. Ini berarti bahwa proses kerja register

adder

sudah bekerja sesuai

dengan perancangan.

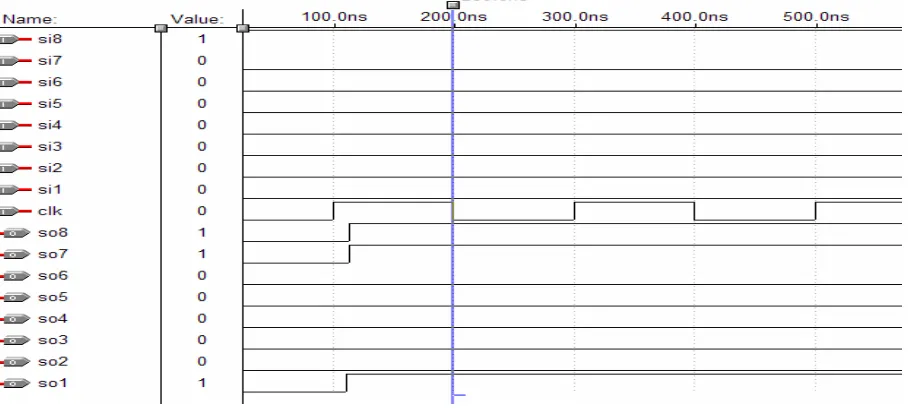

4.1.4 Pengujian Blok ROM

ROM pada konfigurasi pembentuk gelombang ini berfungsi sebagai penyimpan

nilai-nilai data yang akan membentuk gelombang sinus. Gambar 4.8 menunjukkan gambar

Gambar 4.8

Blok ROM

Pada gambar 4.8, ditunjukkan bahwa blok ROM bernama SINELUT. Hal ini

dimaksudkan bahwa ROM di sini (

Read Only Memory

) sama dengan LUT (

Look Up

Table

). Dinamakan demikian karena ROM ini adalah tempat dimana terjadi proses

pencarian nilai-nilai biner pembentuk gelombang sinus yang bersesuaian dengan nilai biner

alamat yang dikirimkan pada port

input

blok ROM. Gambar 4.9 dan 4.10 menunjukkan

hasil simulasi dari cara kerja ROM ini.

Gambar 4.9

Hasil simulasi dari blok ROM dengan alamat desimal 1

10Terdapat kesalahan penempatan letak

port

MSB dan LSB pada blok ROM.

Port

si8

dan

so8

merupakan p

ort

LSB, sedangkan

port

si1

dan

s1

merupakan

port

MSB.

Keterbalikan penempatan ini tidak menjadi masalah, karena bisa diatasi dengan

pengubahan hubungan jalur-jalur masukan dan keluaran pada blok ROM ini. MSB dari

dihubungkan dengan

si8

dan

so8

. Urutan bit di antara MSB dan LSB juga disesuaikan.

Dengan pengubahan hubungan jalur-jalur masukan dan keluaran pada blok ROM ini, maka

blok ROM ini tetap bekerja sebagaimana mestinya seperti yang diharapkan pada

perancangan.

Hasil simulasi ditunjukkan pada gambar 4.9. Ditunjukkan bahwa nilai

input

(port

si1-si8 dengan MSB si1) adalah sebesar 00000001

2atau setara dengan nilai heksadesimal

01

16. Nilai tersebut merupakan alamat yang dituju pada ROM. ROM kemudian

menampilkan data keluaran yang bersesuaian dengan alamat yang dikirim. Kelompok

port

output

menunjukkan nilai 10000011

2atau setara dengan nilai heksadesimal 83

16. Ini adalah

nilai data yang bersesuaian dengan nilai alamat yang dituju pada ROM.

Penampilan hasil simulasi pada blok ROM ini tidak dapat direpresentasikan dengan

grouping output seperti yang ditunjukkan pada gambar 4.7. Hal ini dikarenakan simulator

akan membaca urutan MSB ke LSB secara default dari so8 ke so1. Dengan demikian

pembacaan urutan MSB ke LSB pada hasil simulasi pada gambar 4.9 dan 4.10 dibalik

urutannya dari si1 ke si8. Contoh lebih lanjut ditunjukkan pada gambar 4.10.

Gambar 4.10

Hasil simulasi blok ROM dengan nilai alamat desimal 173

10.

Gambar 4.10 menunjukkan hasil simulasi ROM dengan nilai alamat yang dituju

sebesar 173

10(10101101

2). Hal ini berarti bahwa dicari nilai data pada alamat ke-173. Nilai

port

keluaran menunjukkan nilai biner sebesar 00001101

2(0D

16). Proses ini sudah

bersesuaian dengan perancangan ROM yang terdapat pada gambar 3.3.

Dengan dua contoh yang ditampilkan pada gambar 4.9 dan gambar 4.10, maka

dapat dinyatakan bahwa blok ROM sudah bekerja sebagaimana mestinya, sesuai dengan

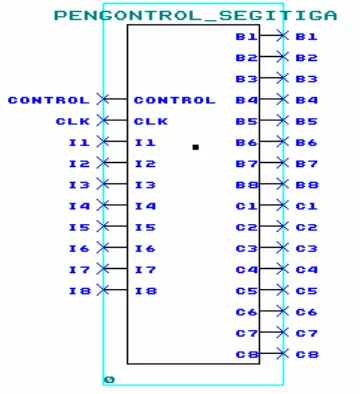

4.1.5 Pengujian Blok Pengontrol Gelombang Segitiga

Prinsip kerja blok pengontrol gelombang segitiga telah dipaparkan di bagian

perancangan pada BAB III. Sub bab ini membahas hasil simulasi blok pengontrol

gelombang segitiga. Gambar 4.11 menunjukkan gambar blok pengontrol gelombang

segitiga, sedangkan gambar 4.12 dan gambar 4.13 menunjukkan hasil simulasi dari cara

kerja blok pengontrol gelombang segitiga.

Gambar 4.11

Gambar blok pengontrol gelombang segitiga

Gambar blok pengontrol gelombang segitiga tersebut terdiri dari 8

port input

, dan

dua kelompok

port output

, yaitu kelompok

port

c8-c1, dan kelompok

port

b8-b1. Dengan

tambahan

port control

untuk mengendalikan keadaan aktif/non-aktif, dan juga

port

clk

untuk

clock

. Gambar 4.12 menunjukkan hasil simulasi untuk

port control

bernilai nol

(non-aktif).

Gambar 4.12

Hasil simulasi blok pengontrol segitiga dengan nilai nol pada

port control

Ditunjukkan pada gambar 4.12, bahwa dengan

port control

bernilai nol, maka saat

pada gambar 4.12, bahwa nilai

port output

b[8..1] bernilai sama dengan nilai

input

i[8..1],

yaitu 55

16. Sementara kelompok

port output

c8-c1 tidak menyalurkan nilai keluaran selain

nilai 00

16. Gambar 4.13 menunjukkan hasil simulasi dengan nilai satu pada

port control

.

Gambar 4.13

Hasil simulasi blok pengontrol segitiga dengan nilai satu pada port control

Gambar

4.13

menunjukkan

hasil simulasi untuk

port control

bernilai satu.

Ditunjukkan pada gambar tersebut bahwa dengan nilai satu pada

port control

, kelompok

port output

c8-c1 akan menyalurkan nilai

input

, sementara kelompok

port output

b8-b1

tidak mengeluarkan

output

selain nilai 00

16.

Dengan dua contoh hasil simulasi seperti yang ditunjukkan pada gambar 4.12 dan

gambar 4.13, di mana blok pengontrol segitiga akan memilih jalur keluaran yang

bergantung pada

port control

apakah bernilai nol atau satu, maka blok pengontrol

gelombang segitiga telah bekerja sesuai perancangan.

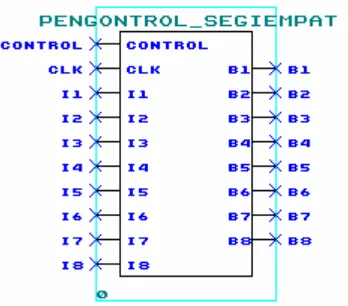

4.1.6 Pengujian Blok Pengontrol Gelombang Kotak

Gambar blok pengontrol gelombang kotak ditunjukkan pada gambar 4.14,

sementara hasil simulasi blok pengontrol segiempat ditunjukkan pada gambar 4.15 dan

gambar 4.16.

Prinsip kerja blok pengontrol gelombang segiempat telah dipaparkan pada bab

perancangan, maka penulis akan langsung membahas hasil simulasinya.

Gambar 4.15

Hasil simulasi blok pengontrol segiempat dengan nilai nol pada

port control

Gambar 4.15 menunjukkan bahwa dengan nilai nol pada

port control

, maka input

bernilai 10111011

2(BB

16) akan disalurkan seluruhnya ke kelompok

port output

b8-b1

.

Sementara Gambar 4.16 akan menunjukkan efek dari pengubahan nilai

port control

menjadi satu, yaitu bahwa blok pengontrol segiempat hanya akan melewatkan MSB

input

ke

port

keluaran.

Port

MSB pada blok ini adalah

i8

dan

b8.

Gambar 4.16

Hasil simulasi blok pengontrol segiempat dengan nilai satu pada

port

control

Gambar 4.15 dan gambar 4.16 menunjukkan bahwa proses kerja blok pengontrol

4.1.7 Pengujian Blok Pengontrol

Output

Prinsip kerja blok pengontrol

output

telah dijelaskan pada bab perancangan. Maka

penulis akan langsung membahas hasil simulasi cara kerja blok pengontrol

output

. Gambar

4.17 menunjukkan gambar blok pengontrol

output

. Pada gambar 4.17, blok pengontrol

output

dinamakan

kontrol_reg_output

. Hal ini dikarenakan blok tersebut akan mengatur

data mana saja yang nantinya akan dikirimkan oleh register

output

ke DAC.

Gambar 4.17

Blok pengontrol

output

Gambar 4.18 menunjukkan hasil simulasi dengan nilai nol pada

port control

,

sementara gambar 4.19 menunjukkan hasil simulasi dengan nilai satu pada

port control

.

Gambar 4.18

Hasil simulasi pengontrol

output

dengan nilai nol pada

port control

Pada gambar 4.18, ditunjukkan bahwa dengan nilai nol pada

port control

, maka

port-port output

o[8..1] akan melewatkan input dari kelompok

input

i8-i1 yang bernilai

CB

16. Sementara bila

port control

bernilai satu, maka kelompok

port output

o[8..1] akan

melewatkan input dari kelompok

input

l8-l1 yang bernilai FA

16. Dua contoh yang

ditampilkan pada gambar 4.18 dan 4.19 memperlihatkan bahwa proses kerja blok

pengontrol

output

sudah bekerja sesuai perancangan.

4.1.8 Pengujian Blok Register

Output

Prinsip

kerja

blok register

output

ini sama persis dengan prinsip kerja register

input

maupun register fasa/register

adder.

Gambar 4.20 menunjukkan simbol blok register

output

, dan gambar 4.21 menunjukkan hasil simulasi dari cara kerja blok register

output.

Gambar 4.20

Gambar blok register

output

Gambar 4.21

Hasil simulasi dari blok register

output

Gambar 4.21 menunjukkan bahwa register

output

menyalurkan apa yang

dimasukkan ke

port input

saat terjadi siklus

clock

. Dengan demikian penulis menyatakan

bahwa cara kerja blok register

output

sudah sesuai seperti perancangan.

4.2. Pengujian Gelombang Sinus

.

Karena bagian DAC belum dibuat, maka tampilan analog gelombang sinus dan

sub bab ini hanya akan membahas kesesuaian antara perancangan nilai ROM sinus dengan

hasil yang ditampilkan pada simulasi.

Pada gambar 3.3 di bab perancangan, telah ditampilkan nilai-nilai data pembentuk

amplitudo gelombang sinus, yang didapat dari hasil perhitungan menggunakan MATLAB.

Berikut ini adalah gambar dari hasil simulasi gelombang sinus dengan nilai

tuning

word

00000001

2atau setara dengan bilangan desimal satu.

Gambar 4.22

. Hasil simulasi pembangkitan gelombang sinus dengan nilai

tuning

word

00000001

2Pada gambar 4.22 (atas), ditunjukkan keluaran dari kelompok

port output

out_1

sampai

out_8

, yaitu nilai-nilai biner yang merepresentasikan nilai pembentuk amplitudo

gelombang sinus pada setiap siklus

clock

yang terjadi. Gambar 4.22 (bawah) menunjukkan