PEMBUATAN DAN KARAKTERISASI

FIELD EFFECT

TRANSISTOR

(FET) BERBASIS

CADMIUM SULFIDE

(CdS)

UNTUK DETEKTOR CAHAYA TAMPAK

ROYNIZAR

DEPARTEMEN FISIKA

FAKULTAS MATEMATIKA DAN ILMU PENGETAHUAN ALAM

INSTITUT PERTANIAN BOGOR

ABSTRAK

ROYNIZAR. Pembuatan dan Karakteristik

Field Effect Transistor

Berbasis

Cadmium Sulfide

(CdS) untuk Detektor Cahaya Tampak. Dibimbing oleh

Dr.AKHIRUDDIN MADDU dan HERIYANTO SYAFUTA, M.Si

Sensor cahaya dapat dibuat dari logam, oksida logam, polimer konduktif

organic,semikonduktor. Sensor cahaya dari bahan semikonduktor memiliki

kelebihan dalam menunjukkan sensitivitas serta dapat digunakan pada suhu ruang.

Cadmium sulfide

sebagai lapisan aktif dari sensor

field effect transistor

(FET)

sensitif dalam merespon cahaya. Terdapat 3 lapisan utama pada sensor sensor

FET yaitu lapisan silikon tipe-p, lapisan SiO

2, dan lapisan aktif CdS. Setiap

lapisan mempunyai karakteristik dan fungsi yang berbeda-beda. Lapisan SiO

2terbentuk saat dipanaskan pada suhu 1000

oC dengan pemberian gas oksigen. Hasil

ini dapat terlihat secara kasat mata, yaitu terjadi perubahan warna pada subtrat

dari warna abu-abu menjadi kuning keemasan. Deposisi lapisan CdS yang dibuat

dengan metode

chemical bath deposition

(CBD) pada suhu 70

oC menghasilkan

lapisan berwarna kuning di atas subtrat silikon yang telah dioksidasi. Pemilihan

waktu dan suhu saat deposisi sangat mempengaruhi sifat dan morfologi lapisan

CdS yang dihasilkan. Daerah serapan cahaya dari lapisan CdS berada pada kisaran

panjang gelombang 450-550 nm dengan nilai selah energi sebesar 2,46 eV. Pada

karakteristik I-V sensor FET, arus

drain-source

dipengaruhi oleh tegangan

gate

yang diberikan. Semakin besar tegangan

gate

yang diberikan maka semakin besar

pula arus

drain-source

yang dihasilkan. Respon sensor FET terhadap cahaya

memperlihatkan bahwa apabila sensor diberikan cahaya maka terjadi peningkatan

arus

drain-source

akibat adanya penurunan resistansi lapisan CdS. Respon

dinamik sensor FET memperlihatkan adanya perubahan tegangan

output

saat

diberikan cahaya. Terjadi penurunan tegangan

output

saat diberikan cahaya pada

setiap peningkatan intensitas. Sensor FET memiliki waktu respon sekitar 0,9 detik

dan waktu pemulihan sekitar 1,3 detik.

iii

PEMBUATAN DAN KARAKTERISASI

FIELD EFFECT

TRANSISTOR

(FET) BERBASIS

CADMIUM SULFIDE

(CdS)

UNTUK DETEKTOR CAHAYA TAMPAK

ROYNIZAR

Skripsi

sebagai salah satu syarat untuk memperoleh gelar

Sarjana Sains pada

Departemen Fisika

DEPARTEMEN FISIKA

FAKULTAS MATEMATIKA DAN ILMU PENGETAHUAN ALAM

INSTITUT PERTANIAN BOGOR

LEMBAR PENGESAHAN

Judul

: Pembuatan dan Karakterisasi

Field Effect Transistor

(FET) Berbasis

Cadmium Sulfide

(CdS) untuk Detektor Cahaya Tampak

Nama

: Roynizar

NIM

: G74080038

Menyetujui,

Dr. Akhiruddin Maddu

Pembimbing I

Heriyanto Syafutra, M.Si

Pembimbing II

Mengetahui,

Dr. Akhiruddin Maddu

Ketua Departemen Fisika

v

KATA PENGANTAR

Puji syukur penulis panjatkan kehadirat Allah SWT atas segala rahmat dan

karunia-Nya, penulis dapat menyelesaikan skripsi

yang berjudul “Pembuatan dan

Karakterisasi

Field effect transistor

(FET) Berbasis

Cadmium Sulfide

(CdS) untuk

Detektor Cahaya Tampak

”.

Pada kesempatan ini, penulis juga ingin mengucapkan terimakasih kepada:

1.

Kedua orang tua penulis yang selalu mendoakan, membimbing,

menasehati, dan memotivasi penulis untuk menyelesaikan studi

2.

Kakak dan adik penulis yang telah memberikan motivasi, doa dan materi

kepada penulis

3.

Bapak Dr. Akhiruddin Maddu selaku pembimbing I yang telah memberi

bimbingan, motivasi, kritik dan saran

4.

Bapak Heriyanto syafutra,M.Si selaku pembimbing II yang telah memberi

bimbingan, motivasi, kritik dan saran

5.

Bapak Dr. Toni Ibnu Sumaryada selaku penguji atas masukan dan saran

6.

Bapak Ir. Hanedi Darmasetiawan M.S selaku dosen editor yang

telahmemberikan masukan dan saran dalam penulisan skripsi

7.

Beasiswa BUMN yang telah membantu penulis menyelesaikan studi S1

8.

Seluruh Dosen pengajar, staf dan karyawan di Departemen Fisika FMIPA

IPB

9.

Desty Putri Amungkasi yang telah menemani dan motivasi penulis dalam

menyelesaikan studi S1

10.

Teman

–

teman Fisika 45 yang telah bersama-sama penulis dalam

menempuh studi S1

11.

Teman

–

teman angkatan 44, 45, 46, dan lainya atas kebersamaan selama

di IPB

Akhir kata, semoga tulisan ini dapat memberikan manfaat untuk kita

semua. Kritik dan saran yang membangun sangat penulis harapkan untuk

kemajuan dari aplikasi material yang dikembangkan ini. Semoga Allah SWT

senantiasa melimpahkan rahmat dan karunianya untuk kita semua. Aamiin.

Bogor, Februari 2013

RIWAYAT HIDUP

Penulis dilahirkan di Nanga Merakai, Kabupaten

Sintang pada tanggal 24 Ferbruari 1991 dari pasangan

Elvizar dan Mawarni. Penulis merupakan anak kedua dari

empat bersaudara.

i

DAFTAR ISI

Halaman

DAFTAR GAMBAR ... viii

DAFTAR LAMPIRAN ... ix

BAB I PENDAHULUAN

1.1 Latar Belakang ... 1

1.2 Tujuan Penelitian ... 1

1.3 Rumusan Masalah ... 1

1.4 Hipotesis ... 1

BAB II TINJAUAN PUSTAKA

2.1 Semikonduktor ... 1

2.2 Semikonduktor

Cadmium Sulfide

(CdS) ... 3

2.3 Transistor ... 4

2.4

Field Effect Transistor

(FET) berbasis CdS... 4

BAB III BAHAN DAN METODE PENELITIAN

3.1 Waktu dan Tempat Penelitian ... 5

3.2 Alat dan Bahan Penelitian ... 5

3.3 Prosedur Penelitian ... 5

3.3.1 Penumbuhan lapisan SiO

2... 5

3.3.2 Penumbuhan lapisan tipis CdS ... 5

3.3.3 Karakterisasi lapisan tipis CdS ... 6

3.3.4 Pembuatan sensor FET

…………..

... 6

3.3.5 Karakterisasi I-V sensor FET ... 6

3.3.6 Pengujian respon dinamik sensor FET ... 7

BAB IV HASIL DAN PEMBAHASAN

4.1 Pembuatan Lapisan SiO

2... 7

4.2 Proses Pembuatan Lapisan Tipis CdS ... 7

4.3 Karakteristik Lapisan Tipis CdS ... 8

4.4 Karakteristik I-V Sensor FET ... 8

4.5 Respon Sensor FET terhadap cahaya ... 9

4.6 Respon Dinamik Sensor FET terhadap Cahaya ... 10

4.7 Stabilitas dan Waktu Respon Sensor FET ... 11

BAB V KESIMPULAN DAN SARAN

5.1 Kesimpulan ... 11

5.2 Saran ... 12

DAFTAR PUSTAKA ... 12

LAMPIRAN ... 14

iii

DAFTAR GAMBAR

Halaman

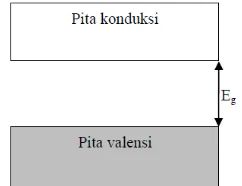

Gambar 1 Pita energi semikonduktor ... 1

Gambar 2 Perpindahan elektron dari pita valensi ke pita konduksi ... 2

Gambar 3 (a) Struktur kristal silikon, (b) lepasnya elektron dari struktur ikatan

kovalen silikon ... 2

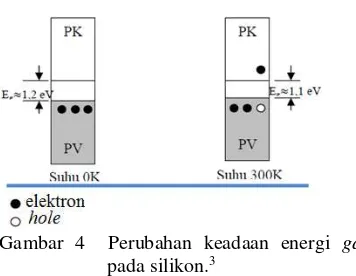

Gambar 4 Perubahan keadaan energi

gap

pada silikon ... 2

Gambar 5 (a) Struktur kristal silikon dengan sebuah atom pengotor valensi tiga

menggantikan posisi salah satu atom, (b) struktur pita energi

semikonduktor tipe-p ... 3

Gambar 6 (a) Struktur kristal silikon dengan sebuah atom pengotor valensi lima

menggantikan posisi salah satu atom, (b) struktur pita energi

semikonduktor tipe-n ... 3

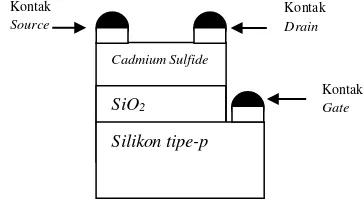

Gambar 7 Struktur piranti FET ... 4

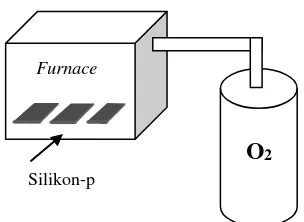

Gambar 8 Skema penumbuhan lapisan SiO

2... 5

Gambar 9 Skema deposisi CBD ... 6

Gambar 10 Struktur piranti

field effect transistor

(FET) ... 6

Gambar 11 Rangkaian karakterisasi I-V sensor FET ... 6

Gambar 12 Rangkaian pengujian respon dinamik sensor FET ... 7

Gambar 13 Lapisan SiO

2di permukaan atas subtrat silikon ... 7

Gambar 14 Kurva absorbansi lapisan tipis CdS ... 8

Gambar 15 Karakteristik I-V sensor FET ... 9

Gambar 16 Kurva hubungan I

d-sterhadap V

gpada V

d-s= 10 V ... 9

Gambar 17 Karakteristik I-V sensor FET terhadap cahaya dengan V

g= 0 V ... 9

Gambar 18 Karakteristik I-V sensor FET terhadap cahaya dengan V

g= 5 V ... 9

Gambar 19 Respon dinamik sensor FET terhadap variasi intensitas cahaya ... 10

Gambar 20 Kurva hubungan antara intensitas cahaya terhadap tegangan ... 10

Gambar 21 Respon dinamik variasi V

gpada kondisi terang dan gelap ... 10

Gambar 22 Stabilitas sensor FET ... 11

Gambar 23 Waktu respon sensor FET ... 11

DAFTAR LAMPIRAN

Halaman

Lampiran 1 Diagram alur kerja penelitian ... 15

Lampiran 2 Perhitungan nilai celah energi pada kurva absorbansi CdS ... 16

BAB I

PENDAHULUAN

1.1 Latar BelakangPengembangan teknologi piranti fotonik mengalami kemajuan yang sangat pesat dalam beberapa dekade terakhir ini. Hal ini dipicu oleh perkembangan teknologi optoelektronik yang meningkat. Teknologi optoelektronik saat ini telah dimanfaatkan dalam banyak bidang, seperti dalam bidang komunikasi optik, pengukuran optik dan sebagainya.

Piranti optoelektronik terdiri dari sumber cahaya seperti LED, LASER, detektor dan komponen-komponen optik lainnya. Detektor optik merupakan salah satu bagian vital dalam teknologi optoelektronik. Detektor pada piranti optoelektronik ini pada umumnya merupakan bahan semikonduktor yang memiliki efek optoelektronik. Contoh penerapan teknologi optoelektronik terdapat pada Video Compact Disc (VCD), karena pada VCD dapat ditemukan sumber cahaya dan juga detektor yang terbuat dari bahan semikonduktor.

Detektor optik semikonduktor dapat merespon berbagai macam bentuk radiasi elektromagnetik. Silikon, Germanium, Gallium Arsenida dan Cadmium Sulfida (CdS) adalah bahan yang sifat kelistrikannya dapat merespon cahaya sehingga bahan itu disebut bahan yang memiliki efek optoelektronik (optik). Sifat listrik-optik ini yang menyebabkan banyak ilmuwan-ilmuwan tertarik untuk meneliti bahan semikonduktor CdS.

Sifat listrik-optik bahan semikonduktor meliputi fotoresistif atau fotokonduktif, yaitu sifat listriknya (resistansi atau konduktansi) bervariasi terhadap respon cahaya. Detektor optik juga dapat dibuat dalam bentuk piranti dioda dan transistor, yang sifat listrik-optiknya disebut fotodioda dan fototransistor. Dalam penelitian ini akan dikembangkan

field effect transistor (FET) dengan bahan aktif yaitu CdS. Bahan semikonduktor CdS termasuk dalam bahan semikonduktor yang memiliki sifat fotoresistif yang cukup baik dan pembuatan relatif mudah dan murah. FET berbasis CdS ini dapat dikembangkan untuk pembuatan piranti elektronik dan optoelektroni, seperti fotodetektor UV, dioda laser dan dioda pengemisi cahaya yang beroperasi pada panjang gelombang tampak, piranti-piranti transistor, display, memori penyimpan data yang memiliki mobilitas

tinggi yang dapat beroperasi pada suhu tinggi, frekuensi tinggi dan daya tinggi.

1.2 Tujuan Penelitian

Penelitian ini bertujuan untuk membuat piranti field effect transistor (FET) berbasis

Cadmium Sulfide (CdS) sebagai lapisan aktif untuk detektor cahaya tampak.

1.3 Rumusan Masalah

1. Apakah cadmium sulfide (CdS) dapat dijadikan lapisan aktif pada field effect transistor (FET) sebagai fotodetektor? 2. Bagaimana karakteristik field effect

transistor (FET) berbasis CdS dapat digunakan sebagai fotodetektor?

1.4 Hipotesis

1. Semakin besar tegangan gate yang diberikan pada sensor FET maka semakin besar pula arus drain-source yang dihasilkan.

2. Semakin besar intensitas cahaya yang diberikan pada sensor FET maka semakin kecil resistansi dari lapisan aktif CdS.

BAB II

TINJAUAN PUSTAKA

2.1 SemikonduktorSemikonduktor adalah material zat padat yang memiliki konduktivitas listrik diantara konduktor dan isolator. Resistivitas semikonduktor berkisar antara 10-5 sampai 105 Ωm.1 Pada semikonduktor terdapat pita energi yang memperbolehkan keberadaan elektron, yaitu pita valensi berenergi rendah yang terisi penuh oleh elektron dan pita konduksi berenergi tinggi yang kosong.2 Celah energi yang memisahkan kedua pita tersebut disebut sebagai pita terlarang atau disebut juga energi gap (Eg). Celah energi pada material semikonduktor ditunjukkan pada Gambar 1.

Salah satu sifat penting semikonduktor adalah memiliki celah energi 0.2-2.5 eV. Nilai celah energi tersebut lebih kecil dari nilai celah energi isolator. Sifat ini memungkinkan suatu elektron memasuki tingkatan energi yang lebih tinggi. Beberapa faktor yang mempengaruhi elektron untuk berpindah dari pita valensi ke pita konduksi ialah suhu dan penyinaran.2 Perpindahan elektron terjadi apabila elektron pada pita valensi menyerap energi sama dengan atau lebih besar dari nilai celah energi antara pita valensi dan pita konduksi seperti terlihat pada Gambar 2. Elektron dan hole inilah yang menjadi pembawa muatan listrik pada material semikonduktor.1

Sifat listrik kristal semikonduktor yang mempunyai ikatan kovalen dapat juga diterangkan dengan memperhatikan keadaan ikatannya. Kristal semikonduktor yang murni atau tidak ditambahkan bahan pengotor dalam pembuatannya disebut semikonduktor

intrinsic, sedangkan yang ditambahkan bahan pengotor disebut semikonduktor ektrinsic.3

Gambar 2 Perpindahan elektron dari pita valensi ke pita konduksi2

Gambar 3 (a) Struktur kristal silikon, (b) lepasnya elektron dari struktur ikatan kovalen silikon2

Gambar 4 Perubahan keadaan energi gap

pada silikon.3

Semikonduktor intrinsic, pada suhu 0 K semua elektron berada pada ikatan kovalen. Pada suhu tersebut, tidak ada elektron bebas atau tidak ada pembawa muatan sehingga bersifat isolator. Struktur ikatan pada semikonduktor dapat dilihat pada Gambar 3. Saat semikonduktor intrinsic berada pada suhu 300K, celah energi antara pita valensi dan pita konduksi berkurang sehingga beberapa elektron valensi dapat keluar dari ikatan kovalen menjadi elektron bebas sebagai pembawa muatan negatif. Berkurangnya celah energi pada semikonduktor dapat dilihat pada Gambar 4. Munculnya elektron bebas diikuti dengan terbentuknya hole sebagai pembawa muatan positif.10

Semikonduktor ektrinsic dapat diperoleh dengan menambahkan (doping) atomatom asing dalam pembuatannya. Tujuan dari pemberian doping ini ialah untuk memperoleh elektron valensi bebas dalam jumlah yang lebih banyak dan permanen dan diharapkan dapat menghantarkan listrik.2Semikonduktor

3

netral. Karena atom pengotor menerima elektron, maka atom pengotor ini disebut atom aseptor.4 Penambahan atom aseptor ini akan menimbulkan tambahan tingkat energi sedikit di atas pita valensi. Peningkatan energi pada semikonduktor tipe-p dapat dilihat pada Gambar 2.5 (b).3

Semikonduktor tipe-n dapat diperoleh dengan cara yang sama seperti semikonduktor tipe-p, dengan menambahkan atom pengotor pentavalen (golongan VA, seperti arsenik, fosfor, atau antimon ) pada silikon murni. Atom pentavalen yang menempati posisi atom silikon dalam kristal, lima elektron valensi dari atom pengotor akan membentuk empat ikatan kovalen lengkap dan tersisa satu elektron yang tidak berpasangan. Sisa elektron ini akan menjadi elektron bebas dan menjadi pembawa muatan dalam proses hantaran listirk. Struktur semikonduktor tipe-n dapat dilihat pada Gambar 6 (a).2

Gambar 5 (a) Struktur kristal silikon dengan sebuah atom pengotor valensi tiga menggantikan posisi salah satu atom silikon, (b) struktur pita energi semikonduktor tipe-p

Gambar 6 (a) Struktur kristal silikon dengan sebuah atom pengotor valensi lima menggantikan posisi salah satu atom silikon, (b) struktur pita energi semikonduktor tipe-n5

Material dari proses pengotoran ini disebut semikonduktor tipe-n karena menghasilkan pembawa muatan negatif. Karena atom pengotor memberikan elektron, maka atom pengotor ini disebut atom donor.4 Penambahan atom donor ini akan menambah satu tingkat energi baru di bawah pita konduksi.3 Penambahan energi pada semikonduktor tipe-n dapat dilihat pada Gambar 6 (b).

2.2 Semikonduktor Cadmium Sulfide (CdS)

Cadmium sulfide (CdS) merupakan bahan semikonduktor dalam kelompok senyawa golongan II-VI dengan struktur kristal Zinc Blende dan Wurtzite sebagiamana bahan semikonduktor dari senyawa-senyawa yang lain. Senyawa II-VI yakni CdS memiliki sifat optik dan listrik yang cocok untuk fotodetektor, disamping untuk piranti-piranti optoelektronik lainnya.

Cadmium sulfide (CdS) miliki koefisien absorbansi yang tinggi sehingga sebagian besar cahaya dapat diabsorbansi pada CdS dalam bentuk lapisan tipis sehingga sangat efektif untuk dijadikan field effect transistor

(FET). Cadmium sulfide memiliki lebar celah pita (bandgap) dalam kisaran 2.3-2.5 eV serta memiliki jenis celah pita semikonduktor

direct bandgap dengan n= ½ (untuk yang indirect,n=2). Cadmium sulfide juga memiliki fotokonduktansi yang tinggi sehingga sangat cocok untuk piranti fotodetektor.6-8

Ada beberapa teknik pendeposisian yang digunakan untuk menumbuhkan lapisan CdS sehingga sifat optik, listrik dan strukturnya sesuai dengan yang diinginkan. Diantaranya menggunakan pendeposisian secara kimia,

physical vapour deposition, spray pyrolysis8 ,

electro deposition, chemical bath deposition

10-14, teknik brush plating 15, hidrotermal 16dan lain-lain. Dari semua teknik di atas, chemical bath deposition (CBD) merupakan teknik yang biasanya digunakan untuk menumbuhkan lapisan tipis CdS. Teknik CBD memiliki banyak keuntungan seperti sederhana, tidak membutuhkan peralatan yang canggih, bahan yang terbuang sedikit, merupakan cara yang ekonomis teknik pendeposisian pada area yang luas untuk semikonduktor golongan II–VI seperti CdS, dan tidak menghasilkan gas yang beracun.13

memiliki stoikiometri yang tinggi dan resistansi gelap yang tinggi.

Teknik deposisi yang digunakan untuk menumbuhkan CdS telah banyak dilakukan dengan metode yang beragam. Penggunaan setiap metode ini akan mempengaruhi sifat optik, listrik dan struktur CdS yang dihasilkan. Menurut beberapa literatur, struktur lapisan tipis CdS yang dibuat dengan menggunakan metode CBD dapat bermacam-macam tergantung pada kondisi deposisi. Strukturnya dapat berbentuk kubik, hexagonal atau campuran kedua fasa tersebut.17-18 Banyak juga peneliti mencatat bahwa terjadi pengotoran oleh oksigen dan nitrogen pada lapisan tipis CdS jika menggunakan metode penumbuhan dengan CBD. Selain itu, penggunaan complexing agent juga dapat mempengaruhi sifat fisis CdS. Penambahan

complexing agent ammonium dapat memperbesar jumlah Cadmium Sulfida yang terbentuk dibanding molekul pengotor lainnya. 18

2.3 Transistor

Pada tahun 1951, William Schockley menemukan transistor sambungan pertama, komponen semikonduktor yang dapat menguatkan sinyal elektronik seperti sinyal radio dan televisi. Kumpulan transistor telah banyak menghasilkan rangkaian semikonduktor lain termasuk rangkaian terpadu (IC), suatu komponen kecil yang mengandung ribuan transistor miniatur.19

Pada keadaan normal, arus yang dialirkan melalui kolektor dan emitor disekat oleh basis sehingga arus tidak bisa mengalir. Untuk membuka katup basis, maka harus memberikan arus pada basis. Semakin besar arus yang diberikan maka katup basis terbuka semakin lebar dan arus yang mengalir dari kolektor menuju emitor semakin besar.

Ada dua jenis transistor yaitu transistor sambungan bipolar (bipolar junction transistor, BJT) dan transistor efek medan (field effect transistor, FET), yang karakteristik kerja dan konsrtuksinya berbeda.20 Transistor efek medan (FET) adalah piranti terkendali tegangan, yang berarti karakteristik output dikendalikan oleh tegangan masukan.

Pada dasarnya terdapat dua jenis transistor efek medan yaitu transistor efek medan tipe-hubungan (JFET) dan transistor efek medan tipe MOS (MOSFET). Field effect transistor (FET) merupakan salah satu bentuk dari MOSFET. Konfigurasi FET

biasanya dibuat dengan menggunakan teknik deposisi lapisan tipis seperti evaporation, sputtering, chemical vapor deposition, dan

spin-coating. FET terdiri dari tiga terminal dengana pengisian konduksi antara dua terminal, sumber dan drain, dikendalikan oleh modulasi potensial listrik dari terminal ketiga yaitu gate. 21

2.4 Field Effect Transistor (FET) Berbasis CdS

Dalam beberapa dekade terakhir ini, bahan semikonduktor cadmium sulfide (CdS) telah banyak menyita perhatian para peneliti karena sifatnya yang menarik untuk dikembangkan pada aplikasi teknologi tinggi. Salah satu aplikasi yang penting pada bahan CdS yaitu menjadi bahan aktif pada field effect transistor (FET). CdS berbasis FET telah banyak dipelajari untuk aplikasi dalam perangkat fotodetektor, biosensor dan flat panel display. Dalam pembuatan FET kualitas tiap lapisan sangat peting untuk menunjukkan kerja dari FET. FET memiliki 3 lapisan yaitu lapisan substrat, lapisan insulator dan lapisan aktif CdS.

Lapisan subtrat menjadi kontak gate yang berfungsi sebagai pengatur arus source-drain. Kontak gate diberi tegangan (Vgs) menimbulkan peningkatan arus source-drain

secara eksponensial, dengan daerah linier mendefinisikan nilai tegangan ambang. Lapisan insulator berfungsi untuk mereduksi arus source-drain. Sedangkan lapisan CdS berfungsi sebagai bahan aktif yang sensitif terhadap cahaya tampak.

Prinsip kerja FET yaitu dengan mengontrol distribusi pembawa elektron dalam semikonduktor dengan mempergunakan medan listrik-dalam. Jika bahan aktif yang digunakan tipe-n, dengan demikian memberikan tegangan positif pada gerbang (gate) akan menghasilkan akumulasi muatan negatif pada lapisan aktif disekitar permukaan dielektrik. Ketika muatan pembawa sudah cukup terakumulasi konduktivitas daerah akumulasi muatan meningkat secara signifikan.22

5

BAB III

METODE PENELITIAN

3.1 Waktu dan Tempat Penelitian

Penelitian ini dilakukan mulai bulan Februari 2012 hingga Oktober 2012 diLaboratorium Biofisika, Laboratorium Fisika Material, Laboratorium Spektroskopi Departemen Fisika IPB, Pusat Penelitian dan Pengembangan (PUSLITBANG) Kehutanan, Laboratorium MOCVD (Metalorganic Chemical Vapor Deposition) ITB, BATAN. 3.2 Alat dan Bahan Penelitian

Alat yang digunakan dalam penelitian ini adalah furnce, X-Ray Diffraction (XRD), spektroskopi UV-VIS, I-V meter,gunting, selotip, double tip, hot plate, magnetic stirrer, stirrer, pipet, tabung reaksi, gelas kimia, gelas ukur, pengaduk, dan neraca analitik sedangkan wafer silikon, cadmium klorida (CdCl2), thiourea (H2NCSNH2), aceton, etanol, gas oksigen O2, NH4Cl, H2SO4, H2O2, pasta perak dan akuades.

3.3 Prosedur Penelitian

3.3.1 Penumbuhan lapisan SiO2

Lapisan tipis SiO2 ditumbuhkan dengan metode wet thermal. Substrat yang digunakan adalah silikon wafer tipe-p (Si-p). Silikon dimasukan ke dalam larutan aseton lalu dicuci dalam ultrasonic bath selama 30 menit. setelah itu dibersihkan di dalam asam

peroxymonosulphuric selama 15 menit kemudian silikon dicuci kembali dengan asam HF. Substrat Si-p tersebut dioksidasi untuk menghasilkan lapisan SiO2 di atas substrat Si-p. Lapisan SiO2 dibuat dengan memanaskan substrat Si-p di dalam furnace hingga mencapai suhu sekitar 10000 C, gas oksigen murni (O2) dialirkan ke dalam furnace selama pemanasan berlangsung. Variasi volume O2 yang diberikan berbeda-beda. Gas O2 mulai diberikan pada suhu 600oC, dengan volume 2.5 mL selama 5 menit. Pada saat suhu

furnace telah mencapai 1000oC, maka volume O2 yang diberikan bertambah menjadi 5 mL selama 10 menit. keadaan 1000oC ini akan dipertahankan selama 2 jam, sehingga akan terbentuk lapisan SiO2 pada subtrat.

Gambar 8 Skema penumbuhan lapisan SiO2

3.3.2 Pembuatan lapisan tipis CdS

Lapisan tipis CdS (bahan semikonduktor tipe-p) dibuat dengan metode CBD (chemical bath deposition). Dengan metode ini, lapisan terdeposisi pada substrat dengan mencelupkan subtrat ke dalam larutan yang mengandung ion-ion Cd+ dan ion-ion sulfida S2- sambil dipanaskan serta diaduk. Bahan-bahan yang digunakan adalah CdCl2 sebagai sumber ion kadmuim (Cd+), Thiourea sebagai sumber ion sulfur (S2-), larutan amonia sebagai agen pengkompleks (complexing agent), air destilasi dan amonium klorida (NH4Cl) sebagai stabiliser agar larutan tidak cepat mengendap.

Skema metode CBD ditunjukkan pada Gambar 9, terdiri dari dua gelas piala dengan ukuran berbeda. Salah satunya berukuran kecil sehingga dapat dimasukkan ke dalam gelas yang lebih besar. Gelas yang kecil diisi larutan deposisi, kemudian dimasukkan ke dalam gelas lebih besar yang diisi air. Sebelumnya, pada dinding sebelah dalam gelas kecil ditempel beberapa substrat kaca dengan ukuran tertentu (misalnya 1 x 2 cm2). Selanjutnya, kedua gelas diletakkan di atas pemanas (hot plate) yang dilengkapi pengaduk magnetik (magnetic stirrer).

Mula-mula dibuat larutan campuran 20 ml CdCl2 (0.1 M) dengan 20 ml Thiourea (1 M) di dalam gelas piala 100 ml. Larutan tersebut diletakkan di atas hot plate

dipanaskan pada suhu 30oC dan diputar pada kelajuan 300 rpm selama 30 menit. Sebanyak 10 mL NH4OH (0.1 M) dan 5 ml NH4Cl ditambahkan ke dalam larutan campuran tersebut. Larutan campuran tersebut dipanaskan pada suhu 70oC dan diputar pada kelajuan 300 rpm selama 2 jam. Optimasi suhu dan waktu perlu dilakukan untuk mengatur morfologi baik struktur, sifat dan ketebalan lapisan yang dihasilkan.

O

2 Silikon-pGambar 9 Skema deposisi CBD

3.3.3 Karakterisasi lapisan tipis CdS Agar ketebalan lapisan yang dihasilkan sesuai dengan yang diinginkan untuk membuat field effect transistor (FET), maka perlu dilakukan optimasi dalam proses deposisi. Optimasi yang harus dilakukan pada kondisi deposisi, meliputi konsentrasi larutan-larutan yang digunakan, suhu deposisi dan waktu deposisi. Optimasi dalam hal suhu dapat menentukan struktur dan sifat lapisan CdS yang terbentuk. Sedangkan, waktu deposisi ditujukan untuk mendapatkan ketebalan lapisan CdS yang dihasilkan.

Sampel-sampel lapisan tipis CdS yang berhasil ditumbuhkan dengan metode CBD selanjutnya dikarakterisasi dengan spektroskopi UV-Vis. Uji Spektroskopi UV-VIS ditujukan untuk mengetahui sifat optik lapisan CdS yaitu menentukan nilai celah energinya. Sifat Optik lapisan tipis CdS yang dibuat dengan metode CBD diukur pada

suhu ruang dengan menggunakan

Spektrofotometer UV-VIS dengan range panjang gelombang 200-1000 nm.

3.3.4 Pembuatan sensor FET

Pembuatan sensor FET dilakukan dengan membuat lapisan tipis SiO2 di atas lapisan Si

tipe-p sebagai bahan dielektriknya. Lapisan dielektrik tersebut kemudian dilapisi dengan CdS sebagai bahan aktifnya. Untuk mengkarakterisasi sensor FET maka dilakukan pemasangan kontak prototipe

sensor FET seperti pada Gambar 10.

Lapisan CdS merupakan bagian paling penting pada sensor FET. Metode yang digunakan untuk membuat lapisan CdS yaitu metode CBD (chemical bath deposition). Dengan menggunakan metode ini, diharapkan dapat menghasilkan lapisan CdS yang tipis.

Pemasangan kontak dilakukan dengan memberikan lapisan metal di atas lapisan aktif CdS. Pemasangan kontak (metalisasi) pada lapisan CdS menggunakan logam emas. Metasisasi dilakukan di BATAN atau di ITB. Lapisan metal tersebut digunakan untuk memudahkan dalam pemasangan pasta perak pada lapisan CdS dan terbentuk kontak ohmik. Pada saat pemasangan kabel, pasta perak akan merekatkan antar kontak emas dengan kabel.

3.3.5 Karakterisasi I-V sensor FET

Karakterisasi FET dilakukan dengan cara menghubungkan piranti FET. Kontak

gate dihubungkan dengan tegangan dari

power supply sebesar 0 V, 2 V, 4 V, 8 V, 10 V. Pada setiap tegangan gate (Vg) yang digunakan arus drain (Id) diukur dengan menggunakan Keithley 2400 dengan tegangan

drain (Vd) yang digunakan bervariasi dari 0 sampai 10 volt.

Karakteristik I-V FET divariasikan terhadap kondisi terang dan gelap. Kondisi awal sensor dikarakterisasi saat keadaan gelap dengan tegangan gate 0 V, kemudian diberi cahaya pada sensor tersebut. Kondisi selanjutnya, sensor diberi tegangan gate 5 V dalam keadaan gelap, setelah itu diberikan cahaya dengan intensitas yang sama seperti pada kondisi yang pertama.

Gambar 10 Struktur piranti field effect transistor (FET) berbasis CdS

7

3.3.6 Pengujian respon dinamik sensor FET

Pengujian respon dinamik dilakukan dengan memvariasikan kondisi saat terang dan gelap. Sensor FET disusun secara seri dengan resistor, seperti pada Gambar 12. Rangkaian dihubungkan dengan baterai 9 volt dan variasi tegangan gate yaitu 0 V, 5 V, dan 10 V. sensor FET dihubungkan denga sensor tegangan yang terkoneksi langsung dengan komputer.

Sensor akan diuji pada kondisi tegangan

gate 0 V dengan memvariasikan intensitas cahaya yaitu pada 0 watt/m2, 14 watt/m2, dan 85 watt/m2 dengan menggunakan lampu optik sebagai sumber cahayanya. Setelah itu diberikan tegangan gate saat 0 V, 5 V, dan 10 V dengan kondisi terang-gelap. Hal ini bertujuan untuk melihat perbandingan tegangan gate saat kondisi terang dan gelap.

Dilakukan juga pengujian kestabilan dari sensor FET yaitu dengan memberikan tegangan gate 0 V saat kondisi terang dan gelap. Hal ini dilakukan untuk melihat kemampuan sensor apakah dapat balik (reversible) atau tidak.

Gambar 12 Rangkaian pengujian respon dinamik sensor FET

Gambar 13 Lapisan SiO2 di permukaan atas substrat silikon

BAB IV

HASIL DAN PEMBAHASAN

4.1 Pembuatan Lapisan SiO2

Pembuatan lapisan silikon dioksida (SiO2) dilakukan menggunakan metode termal, dengan perlakuan subtrat silikon dipanaskan di dalam furnace pada suhu 1000oC selama 3 jam. Kemudian gas oksigen (O2) dialirkan ke dalam furnace selama pemanasan berlangsung. Gas oksigen akan berikatan dengan silikon yang membentuk lapisan SiO2. Lapisan SiO2 akan menjadi lapisan dielektrik yang berfungsi untuk mereduksi elektron yang menglir pada lapisan aktif sensor FET. Hasil lapisan SiO2 yang terbentuk dapat dilihat pada Gambar 13. Pada Gambar 13 terlihat perbedaan warna antara substrat silikon dengan lapisan SiO2. Warna lapisan SiO2 yang dihasilkan adalah kuning keemasan, sedangkan warna subtrat silikon adalah perak.

4.2 Proses Pembuatan Lapisan Tipis CdS Metode CBD digunakan untuk menumbuhkan lapisan tipis CdS dengan menggunakan cadmium klorida (CdCl2) sebagai sumber ion cadmium (II) (Cd+2) dan thiourea sebagai sumber ion sulfur (S2-). Selain itu, NH4OH digunakan sebagai buffer untuk mempertahankan pH selama pendeposisian dilakukan dan untuk mengontrol kecepatan reaksi. Selain itu, konsentrasi NH4OH juga dapat mempengaruhi seberapa banyak CdCl2 yang terhidrolisis dalam air. Sedangkan NH4Cl digunakan agar CdS dapat menempel pada subtrat.

Tahapan pembentukan CdS terbagi dalam 3 tahapan yaitu proses nucleation center,

pembentukan ion per ion (mekanisme heterogen) dan pembentukan kluster per kluster (mekanisme homogen). Proses

nucleation center merupakan proses pembentukan ion Cadmium dan ion Sulfur baik pada substrat maupun pada larutan bath. Pada permukaan CdS ion per ion dapat menghasilkan CdS dengan morfologi yang lebih baik dibandingkan jika yang terjadi adalah kluster per kluster.25

Dalam penelitian ini, terlihat pembentukan CdS terjadi pada mekanisme homogen yang ditandai dengan banyak terbentuknya koloid berwarna kuning di dalam larutan bath sehingga mempengaruhi struktur kristal CdS yang terbentuk.

dihasilkan. Jika deposisi dilakukan selama kurang dari 2 jam maka lapisan yang dihasilkan sangat tipis. Sebaliknya jika deposisi dilakukan selama lebih dari 2 jam maka lapisan yang dihasilkan akan semakin tebal. Lapisan yang tebal tidak cocok digunakan sebagai window layer dalam fotodetektor karena dapat menyebabkan aliran elektron di dalam lapisan tidak tersebar merata. Oleh sebab itu, dalam penelitian ini digunakan pendeposisian selama 2 jam. Berkaitan dengan dua mekanisme yang dijelaskan sebelumnya, jika deposisi dilakukan dalam jangka waktu yang lama maka semakin banyak kluster CdS yang menempel pada permukaan sampel sehingga akan menghasilkan morfologi lapisan yang kurang baik.

Pada penelitian ini, suhu deposisi dilakukan pada suhu 70oC. Jika deposisi dilakukan pada suhu dibawah 70oC maka butuh waktu yang sangat lama untuk menumbuhkan lapisan pada substrat. Selain itu, lapisan yang dihasilkan akan sangat tipis akibat terbentuknya kluster-kluster pada permukaan sampel. Ketika suhu deposisi dinaikan di atas 100oC maka lapisan yang dihasilkan tidak merata dan banyak terbentuk koloid pada larutan bath yang kadang menempel pada permukaan lapisan CdS.

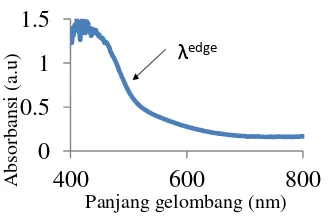

4.3 Karakteristik Lapisan Tipis CdS Secara umum sifat optik bahan semikonduktor CdS dapat diamati dengan menggunakan spektrofotometer UV-VIS yang meliputi absorbansi, transmitansi dan reflektansi. Nilai absorbansi lapisan CdS yang dideposisi dengan suhu 70oC dan di suhu aneling 200oC pada beberapa panjang gelombang dapat dilihat pada Gambar 14. Dari Gambar 14, pita absorbansi berada pada panjang gelombang 400-550 nm, hal ini sesuai dengan beberapa literatur yang memperlihatkan bahwa pita absorbansi CdS terjadi pada rentang panjang gelombang 350-550 nm.26

CdS merupakan material semikonduktor yang memiliki celah energi khas. Pola absorbansi dapat digunakan untuk memperkirakan nilai celah energi (Eg) yang dimiliki oleh sampel CdS berdasarkan persamaan (1) :

Eg = hc/λedge (1)

Keterangan :

- Eg = energi gap - h = konstanta planck

(6,6261x10-34 Js)

- c = kecepatan cahaya ( 3x108 m/s) - λedge = panjang gelombang tepi absorbs

sampel CdS

Berdasarkan kurva absorbansi CdS diketahui nilai λed sekitar 503 nm sehingga

diperoleh nilai celah energi (Eg) dari CdS sekitar 2.46 eV. Nilai ini sesuai dengan beberapa literatur dengan nilai celah energi CdS sekitar 2.3 – 2.5 eV. Celah energi CdS sangat mempengaruhi sifat konduktivitas listrik CdS. Semakin besar celah energi, maka akan semakin kecil konduktivitas listriknya.

Gambar 14 Kurva absorbansi lapisan tipis CdS

4.4 Karakteristik I-V Sensor FET

Karakterisasi I-V sensor FET dilakukan dengan memberikan tegangan bias maju (Vd-s) sambil mengukur arus drain-source (Id-s). Gambar 15 memperlihatkan hubungan antara Id-s (arus drain-source) terhadap Vd-s (tegangan drain-source) dengan memvariasikan Vg (tegangan gate) yakni 0 V, 2 V, 4 V, 6 V , 8 V, 10 V. Tegangan bias maju (Vd-s) diberikan mulai dari 0 V hingga 10 V.

Berdasarkan kurva I-V sensor FET terlihat bahwa tegangan gate yang diberikan mempengaruhi arus drain-source. Tegangan

gate yang diberikan yaitu positif karena lapisan aktif CdS merupakan semikonduktor tipe-n. Semakin positif tegangan gate yang diberikan maka semakin kecil nilai resistasi dari CdS sehingga membuat semakin banyak arus drain-source yang dapat dilewatkan. Hal inilah yang menyebabkan rasio antara tegangan dan arus menjadi semakin mengecil.

0

0.5

1

1.5

400

600

800

A b so rb an si (a .u )

9

Gambar 15 Karakteristik I-V sensor FET

Gambar 16 Kurva hubungan Id-s terhadap Vg pada Vd-s = 10 V

Untuk melihat pengaruh tegangan gate

(Vg), maka dibuat kurva hubungan antara arus

drain-source (Id-s) dengan tegangan gate (Vg) pada Vd-s = 10 V, seperti ditunjukan pada Gambar 16. Gambar 16 memperlihatkan kurva hubungan antara arus drain-source (Id-s) dengan tegangan gate (Vg) pada Vd-s = 10 V, yang diperoleh dari Gambar 15. Terlihat jelas bahwa tegangan gate berpengaruh terhadap arus drain-source. Semakin besar tegangan

gate yang diberikan maka semakin besar pula arus drain-source yang dihasilkan.

Pada penelitian ini, tegangan gate yang diberikan kecil. Hal ini bertujuan untuk mencegah terjadinya kebocoran pada lapisan SiO2. Apabila telah terjadi kebocoran pada lapisan SiO2 maka sensor FET tidak bias berfungsi dengan baik.

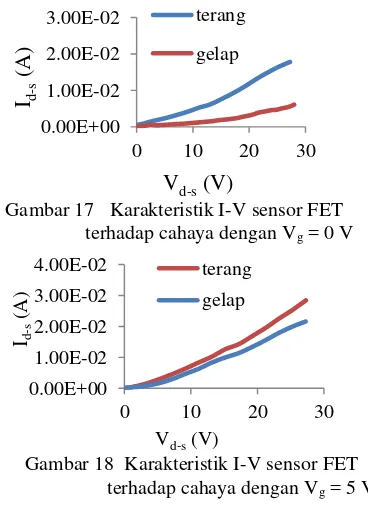

4.5 Respon sensor FET terhadap Cahaya Pengukuran I-V menggunakan alat I-V meter (sourcemeter, Keithley 2400). Pengukuran tersebut dilakukan denga perlakuan yaitu kondisi tanpa cahaya (gelap) dan dengan cahaya (terang). Terdapat dua variasi tegangan gate yang diberikan yaitu 0 V dan 5 V. Gambar 17 dan 18 menunjukkan kurva karakteristik arus-tegangan untuk tegangan gate 0 V dan 5 V. Karakteristik

arus-tegangan sangat diperlukan untuk mengetahui apakah sensor yang dapat berfungsi sebagai fotodetektor atau tidak. Distribusi arus-tegangan pada gambar menunjukkan bahwa sensor FET bersifat fotodetektor, karena terlihat dari kurva I-V terjadi perubahan arus yang signifikan saat kondisi terang.

Pengukuran kuva I-V dilakukan dengan menghubungkan elektroda negatif pada gerbang source, elektroda positif pada gerbang drain dan gate. Kedua variasi tegangan gate tersebut menunjukkan kenaikan arus ketika diberikan tegangan bias maju, kenaikan arus ini terjadi karena resistansi pada lapisan CdS semakin mengecil dengan meningkatnya tegangan bias maju. Penyinaran pada lapisan aktif CdS, akan meningkatkan pasangan elektron-hole didaerah lapisan CdS. Pasangan elektron-hole akan terpisah oleh medan listrik yang kemudian akan berkontribusi terhadap peningkatan arus, sehingga pada kurva terlihat adanya peningkatan arus ketika lapisan CdS disinari dibandingkan dengan gelap.

Kenaikan arus selain dipengaruhi oleh cahaya, juga dipengaruhi oleh tegangan gate

yang diberikan. Semakin besar tegangan gate

yang diberikan maka akan semakin besar arus yang dihasilkan. Hal ini disebabkan semakin mengecilnya resistasi dari lapisan CdS.

Gambar 17 Karakteristik I-V sensor FET terhadap cahaya dengan Vg = 0 V

Gambar 18 Karakteristik I-V sensor FET terhadap cahaya dengan Vg = 5 V 0.00E+00

1.00E-02 2.00E-02 3.00E-02

0 10 20 30

I

d-s(A

)

V

d-s(V)

terang gelap 0.00E+00 1.00E-02 2.00E-02 3.00E-02 4.00E-02

0 10 20 30

Id-s

(A ) Vd-s(V) terang gelap 0.0E+00 5.0E-04 1.0E-03 1.5E-03 2.0E-03 2.5E-03

0 5 10

Id-s

(A)

Vd-s(V)

Vg= 0 V

Vg= 2 V Vg= 4 V Vg= 6 V Vg= 8 V Vg= 10 V

0 50 100 150 200 250

0 5 10

Terlihat pada Vg = 0 V, terjadi kenaikan arus yang signifikan bila dibandingkan dengan Vg = 5 V. Pada saat Vg = 0 V terjadi kenaikan arus drain-source sebesar 1,31x10-2 A dengan V

d-s = 27 V. Sedangkan saat Vg = 5 V, hanya terjadi kenaikan arus

drain-source sebesar 6,88x10-3A dengan Vd-s = 27 V. Hasil ini menunjukkan bahwa saat Vg = 0 V memiliki respon yang lebih baik terhadap cahaya.

4.6 Respon Dinamik sensor FET terhadap cahaya.

Gambar 19 menunjukkan respon dinamik sensor FET terhadap variasi intersitas cahaya yaitu pada 0.02 watt/m2; 14.78 watt/m2; 85.53 watt/m2. Sensor FET dihubungkan seri dengan resistor yang berfungsi untuk membagi tegangan. Pada saat intensitas cahaya 0.02 watt/m2, tegangan yang dihasilkan sebesar 2.55V. Namun setelah intensitas cahaya diperbesar menjadi 14.78 watt/m2, nilai tegangan yang dihasilkan menjadi berkurang yaitu sebesar 2.3V. Begitu juga saat intensitas cahaya diperbesar lagi menjadi 85.53 watt/m2, nilai tegangan yang dihasilkan menjadi semakin berkurang menjadi 2.15V.

Untuk melihat pengaruh intensitas cahaya, maka dibuat kurva hubungan antara intensitas terhadap tegangan output yang diperoleh dari kurva pada Gambar 19. Gambar 20 memperlihatkan kurva hubungan antara intensitas terhadap tegangan output, semakin besar intensitas cahaya yang diberikan maka semakin kecil tegangan output

yang dihasilkan. Hal ini disebabkan, adanya interaksi antara cahaya yang diberikan dengan lapisan CdS, sehingga menyebabkan akan meningkatkan pasangan elektron-hole

didaerah lapisan CdS. Pasangan elektron-hole

akan terpisah oleh medan listrik yang kemudian akan berkontribusi terhadap penurunan resistansi dari CdS.

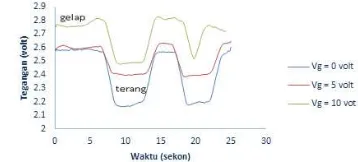

Gambar 21 memperlihatkan respon dinamik sensor FET terhadap cahaya pada tegangan gate berbeda. Semakin besar tegangan gate yang diberikan, maka tegangan

output yang dihasilkan pada sensor akan semakin meningkat. Hal ini berbeda ketika sensor diberi cahaya, akan terjadi penurunan tegangan output yang diakibatkan adanya penurunan resistansi dari sensor.

Gambar 19 Respon dinamik sensor FET terhadap variasi intersitas cahaya

Gambar 20 Kurva hubungan antara intensitas cahaya terhadap tegangan

Gambar 21 Respon dinamik variasi Vg pada kondisi terang dan gelap

Pada data ini divariasikan tegangan gate

yaitu 0 V, 5 V, dan 10 V. Terlihat pada Vg = 0 V, respon sensor terhadap cahaya lebih besar bila dibandingkan dengan Vg = 5 V dan 10 V. Terlihat pada gambar, saat Vg = 0 V maka terjadi perubahan tegangan output

sebesar 0.4 V. sedangkan saat Vg = 5 V hanya terjadi perubahan tegangan output sebesar 0.2 V dan saat Vg = 10 V terjadi perubahan sebesar 0.3 V. Hal ini menujukan bahwa saat Vg = 0 V, sensor dapat bekerja dengan lebih baik dikarenakan perubahan tegangan output

11

4.7 Stabilitas dan Waktu respon sensor FET

Stabilitas sensor FET yang telah dibuat dapat diketahui berdasarkan Gambar 22. Sensor FET diberi perlakuan tanpa cahaya (gelap) dan dengan cahaya (terang) secara berulang. Hal ini bertujuan untuk mengetahui kemampuan sensor apakah dapat kembali ke keadaan semula setelah digunakan. Gambar 22 memperlihatkan perlakuan sensor saat tanpa cahaya (gelap) menghasilkan tegangan

output sebesar 2.6 V, sedangkan saat diberi cahaya, tegangan output menurun hingga 2.2 V. Namun setelah dikembalikan ke kondisi semula (gelap), maka tegangan output

kembali menjadi 2.6 V. Hal ini terlihat bahwa sensor memiliki resistansi yang dapat balik (reversible) sehingga sensor FET dapat digunakan secara berulang.

Waktu respon merupakan waktu yang dibutuhkan sensor untuk berubah dari keadaan awal ke keadaan stasioner. Sedangkan waktu pemulihan yaitu waktu yang diperlukan oleh sensor untuk menghasilkan suatu output yang dapat kembali ke keadaan semula. Gambar 23 meperlihatkan sensor FET memiliki waktu respon sekitar 0.9 detik merupakan waktu yang dibutuhkan sensor berubah dari 2.6 V (tanpa cahaya) menjadi 2.2V (keadaan stasioner saat diberi cahaya). Sedangkan Gambar 24 memperlihatkan waktu pemulihan (recovery) pada sensor FET. Hasil menunjukkan sensor memiliki waktu pemulihan selama 1.3 detik merupakan waktu yang dibutuhkan sensor berubah dari 2.2 V (keadaan stasioner saat diberi cahaya) menjadi kembali kekeadaan semula yaitu 2.6 V (tanpa cahaya). Hasil ini menunjukkan bahwa sensor FET memiliki waktu respon yang lebih cepat dari pada waktu pemulihannya.

Gambar 22 Stabilitas sensor FET

Gambar 23 Waktu respon sensor FET

Gambar 24 Waktu pemulihan sensor FET

BAB V

KESIMPULAN DAN SARAN

5.1 Kesimpulan

Lapisan SiO2 terbentuk saat dipanaskan pada suhu 1000oC dengan pemberian gas oksigen. Hasil ini dapat terlihat secara kasat mata, yaitu terjadi perubahan warna pada subtrat dari warna abu-abu menjadi kuning keemasan.

Deposisi lapisan CdS yang dibuat dengan metode chemical bath deposition (CBD) pada suhu 70oC menghasilkan lapisan berwarna kuning di atas subtrat silikon yang telah dioksidasi. Pemilihan waktu dan suhu saat deposisi sangat mempengaruhi sifat dan morfologi lapisan CdS yang dihasilkan. Daerah serapan cahaya dari lapisan CdS berada pada kisaran panjang gelombang 450-550 nm dengan nilai selah energi sebesar 2.46 eV.

Pada karakteristik I-V sensor FET, arus

drain-source dipengaruhi oleh tegangan gate

yang diberikan. Semakin besar tegangan gate

yang diberikan maka semakin besar pula arus

drain-source yang dihasilkan. Respon sensor FET terhadap cahaya memperlihatkan bahwa apabila sensor diberikan cahaya maka terjadi peningkatan arus drain-source akibat adannya penurunan resistansi dari lapisan CdS.

output saat diberikan cahaya. Terjadi penurunan tegangan output saat diberikan cahaya pada setiap peningkatan intensitas. Sensor FET memiliki waktu respon sekitar 0.9 detik dan waktu pemulihan sekitar 1.3 detik.

5.2 Saran

Penelitian ini dapat dikembang lebih lanjut dengan memvariasikan waktu dan banyaknya gas oksigen yang diberikan pada saat pembentukan lapisan SiO2. Hal ini bertujuan agar didapatkan hasil pembentukan lapisan SiO2 yang maksimal.

BAB VI DAFTAR PUSTAKA

1 Lestari, S. I. 2006. Sintesis dan optimalisasi gel kitosan-gom guar

[skripsi]. Bogor: Fakultas Matematika dan Ilmu Pengetahuan Alam, Institut Pertanian Bogor.

2 Yani, S. 2011. Sintesis dan optimalisasi gel kitosan [tesis]. Bogor : Fakultas Matematika dan Ilmu Pengetahuan Alam, Institut Pertanian Bogor.

3 Rio, S.R., Iida, M. 1999. Fisika dan Teknologi Semikonduktor. Jakarta: Pradnya Paramita

4 [Anonim]. Semikonduktor. 2012. hhtp://jonioke.blogspot.com/2010/04/-semikonduktor.html. [12 Oktober 2011].

5 [Hamonanga]. Prinsip dasar semikonduktor. 2009. http://-www.electroniclab.com/index.php?option =com_content&view=article&id=13:prin sip-dasar-semikonduktor. [12 Oktober 2011].

6 Hutauruk, P. T. P. 2000. Efek fotovoltaik

lapisan tipis CdS (Cadmium Sulfide) pada sistem sel surya fotoelektrokimik

[skripsi]. Bogor : Fakultas Matematika dan Ilmu Pengetahuan Alam, Institut Pertanian Bogor.

7 Kireen, P.S. 1975. Semiconduktor Physics. Mir Publishers.Moscow.Hal 579

8 Kurniati M.2002.Studi sifat optik, listrik

dan fotoelektrokimia lapisan tipis

semikonduktor CdS [Usulan Penelitian].

Bogor : Fakultas Matematika dan Ilmu

Pengetahuan Alam, Institut Pertanian Bogor.

9 Hiie, J., Dedova, T., Valdna, V., Muska, K. 2006. Comparative study of nano-structured CdS thin film prepared by CBD and spray pyrolysis: annealing effect. Thin Solid Film, 511,443–447. 10 Khallaf, H. et all. 2008. Characterization

of gallium-doped CdS thin film grown by chemical bath deposition. Apl Surface Sci, 255, 4129–4134.

11 Khallaf, H. et all. 2009. In-situ boron doping of chemical-bath deposited CdS thin film. Hys Status Solidi, 206, 256–

262.

12 Zhou, X., Li, Z., Xu, S.2006. Preparation and formation mechanism of CdS nano-film via chemical bath deposition. Front

Chem China, 3,18–22.

13 Çetinörgü, E., Gümüş, C., Esen, R. 2006. Effects of deposition time and suhue on the optical properties of air-annealed chemical bath deposited CdS film. Thin

Solid Film, 515,1688–1693.

14 Metin, H., Sat, F., Erat, S., Ari, M. 2008. Cadmium sulphide thin film grown by CBD: the effect of thermal annealing on the structural, electrical and optical properties. J Optoelectronics and Advanced Materials. Vol. 10. hlm 2622–

2630.

15 Murali, KR., Kumaresan, S., Prince, J.J. 2007. Characteristics of CdS thin film brush electrodeposited on low-suhue substrates. J Materials Science in Semiconductor Processing. Vol. 10.hlm 56–60.

16 Jinxin, Z., Gaoling, Z., Gaorong, H. 2007. Preparation of CdS nanoparticles by hydrothermal method in microemulsion.

Front Chem China, 2, 98–101.

13

18 Malinowska, B., Rakib, M., Durand, G. 2005. Analytical characterization of cadmium cyanamide in CdS thin film and bulk precipitates produced from CBD process in pilot plant. J Solar Energi Materials & Solar Cells. Vol 86. hlm 399–419.

19 Malvino, A.P.2003.Prinsip-Prinsip

Elektronika.Jakarta:Salemba Teknika.

20 Toole, Mike.2003. Rangkaian Elektronik Prisip dan Aplikasi. Jakarta : Erlangga. 21 Widodo, T.S. 2002. Elektronika Dasar.

Jakarta: Salemba Teknika

22 Chang, J. B.2006. Functionalized polytiophene thin-film transistor for low-cast gas sensor array isertasi]. California : Electrical Engineering and Computer Sciences, University of California at Berkley.

23 Mahdi M.A. et al. 2009. Structural and optical properties of chemical deposition CdS thin film. J Nanoelectronics and Materials. Vol. 2. hlm 163-172. 24 Pentia, E., Pintilie, L., Pintilie, I., Botila,

T. 2000. The influence of cadmium salt anion on the growth mechanism and on the physical properties of CdS thin film. J Optoelectronics and Advanced Materials.

Vol. 2. hlm 593-601.

25 Devi, R. et all. 2007. Synthesis of nanocrystalline CdS thin in PVA matrix.

15

Lampiran 1. Diagram Alir Penelitian

Mulai

Persiapan Alat dan Bahan

Pembuatan Lapisan SiO

2Deposisi Lapisan CdS

Metalisasi

Karakterisasi I-V

Pengujian FET terhadap cahaya

Pengolahan dan analisis data

Penulisan laporan

Lampiran 2.

Perhitungan nilai celah energi pada kurva absorbansi CdS

Dari gambar di atas

diperoleh nilai λ

edgesebesar 503,33 nm

Dengan nilai h (konstanta Planck) = 6,6261 x 10

-34Js, dan c (kelajuan cahaya) =

3x10

8m/s, maka didapatkan nilai Eg (celah energi) sebesar :

E

g= 6,6261.10

-34x 3.10

8= 3,94936x10

-19503,33.10

-9Jadi, nilai celah energi untuk CdS ialah sebesar 3,94936x10

-19J atau sama dengan

2,467427 eV.

0

0.2

0.4

0.6

0.8

1

1.2

1.4

400

500

600

700

800

Absor

ba

nsi (a

.u)