Laporan Praktikum I Praktik Teknik Digital IC DAN GERBANG LOGIKA

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

IC DAN GERBANG LOGIKA

I. TUJUAN PERCOBAAN

Praktikan diharapkan dapat menjelaskan sifat dan cara kerja dari gerbang logika OR, AND, NOT, NOR, NAND, EX-OR, dan EX-NOR.

II. DASAR TEORI

Gerbang Logika adalah rangkaian dengan satu atau lebih dari satu sinyal masukan tetapi hanya menghasilkan satu sinyal berupa tegangan tinggi (Logika tinggi [1]) atau tegangan rendah (Logika rendah [0]). Dikarenakan analisis gerbang logika dilakukan dengan Aljabar Boolean maka gerbang logika sering juga disebut Rangkaian logika.

Gerbang logika merupakan dasar pembentukan sistem digital. Gerbang logika beroperasi dengan bilangan biner, sehingga disebut juga gerbang logika biner. Tegangan yang digunakan dalam gerbang logika adalah tinggi atau rendah. Tegangan tinggi berarti 1(LED menyala), sedangkan tegangan rendah berarti 0 (LED padam). Rangkaian logika sering kita temukan dalam sirkuit digital (Integrated Circuit) yang diimplemetasikan secara elekrtonik dengan menggunakan dioda atau transistor.

Berikut Merupakan Jenis-jenis IC (Integrated Circuit) beserta Gerbang Logika yang terkandung di dalamnya:

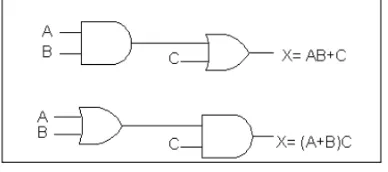

Penjelasan : Gerbang AND

kedua input berada pada logika 1 maka output akan berada pada logika 1, namun apabila semua atau salah satu inputnya berada pada logika 0 maka outputnya juga berada pada logika 0.

Gerbang OR

Gerbang OR menggunakan IC TTL tipe SN 7432. Pada gerbang OR apabila salah satu input berada pada logika 1 maka output akan berada pada logika 1.

Gerbang NOT

Gerbang NOT menggunakan IC TTL tipe SN 7404. Gerbang NOT hanya

mempunyai satu sinyal input dan satu sinyal output. Dalam gerbang NOT, untuk menghasilkan output berlogika 1 maka input harus berada pada logika 0.

Gerbang NAND

Gerbang NAND menggunakan IC TTL tipe SN 7400. Gerbang NAND merupakan kebalikan dari gerbang AND. Apabila kedua input berada pada logika 1 maka output akan mati. Namun apabila semua atau salah satu input berada pada logika 0 maka

output akan berlogika 1. Gerbang NOR

Gerbang NAND menggunakan IC TTL tipe SN 7402. Gerbang NOR merupakan kebalikan dari gerbang logika OR. Apabila kedua input berada pada logika 0 maka output berlogika 1.

Gerbang EX-OR

kedua input mempunyai logika yang sama maka output berlogika 0. Gerbang EX-NOR

Gerbang EX-NOR menggunakan IC TTL tipe SN 74266 . Gerbang EX-NOR disebut juga dengan gerbang pembanding. Gerbang EX-NOR merupakan kebalikan dari gerbang EX-OR. Pada gerbang EX-NOR untuk menghasilkan output berlogika 1 maka semua input harus pada keadaan logika yang sama.

III. ALAT DAN BAHAN PERCOBAAN 1. Digital Trainer

Melakukan percobaan satu demi satu gerbang logika: 1. Memahami terlebih dahulu IC-IC yang akan digunakan.

2. Menghubungkan power supply dengan tegangan 220 Volt. Jangan di ON sebelum yakin bahwa rangkaian sudah terangkai dengan benar.

3. Menghubungkan terminal Vcc dari semua modul yang akan digunakan pada terminal + 5 Volt dari power supply.

4. Menghubungkan terminal GND dari semua modul yang akan digunakan pada terminal GND dari power supply.

5. Menghubungkan terminal input dari masing-masing gate ke terminal input (A dan B).

6. Menghubungkan terminal output dari gate ke indikator LED.

7. Memberi kondisi logic input sesuai dengan tabel 1, mengamati dan mencatat kondisi outputnya. Jika LED menyala berarti logic tinggi (1). Jika LED padam berarti logic rendah (0).

9. Membuat kesimpulan.

LAPORAN HASIL PENGAMATAN

Gambar: Foto Laporan Sementara I.

V. ANALISIS

Dari hasil percobaan yang telah kami tulis di Laporan Sementara, kami mendapatkan beberapa data:

IC 7432 (Terindikasi sebagai Gerbang OR) :

Input Output

A B Y

0 0 0

0 1 1

1 0 1

1 1 1

Hasil: Data Sesuai dengan Teori.

IC 7408 (Terindikasi sebagai Gerbang AND) :

Input Output

A B Y

0 0 0

0 1 0

1 0 0

1 1 1

IC 7404 (Terindikasi sebagai Gerbang NOT) : Input Output

A Y

0 1

1 0

Hasil: Data Sesuai dengan Teori.

IC 7402 (Terindikasi sebagai Gerbang NOR) :

Input Output

A B Y

0 0 1

0 1 0

1 0 0

1 1 0

Hasil: Data Sesuai dengan Teori.

IC 7400 (Terindikasi sebagai Gerbang NAND) :

Input Output

A B Y

0 0 1

1 0 1

1 1 0

Hasil: Data Sesuai dengan Teori.

IC 7486 (Terindikasi sebagai Gerbang EX-OR) :

Input Output

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

Hasil: Data Sesuai dengan Teori.

VI. JAWAB PERTANYAAN

1. Sifat dari masing-masing IC itu berbeda, yaitu :

IC 7432 (OR) : Output menyala (berlogika 1) ketika (minimal) salah satu dari kedua input berlogika 1.

IC 7404 (NOT) : Memiliki sifat berlawanan dengan inputnya, jika inputnya berlogika 1 maka output akan berlogika 0, begitu pula sebaliknya.

IC 7402 (NOR) : Output menyala (berlogika 1) ketika kedua (semua) input berlogika 0.

IC 7400 (NAND) : Output menyala (berlogika 1) ketika (minimal) salah satu dari kedua input berlogika 0.

IC 7486 (EX-OR) : Output menyala (berlogika 1) ketika kedua inputnya berbeda logika.

2. Perbedaan yang terdapat antara gerbang NAND dan OR apabila salah satu inputnya diberi keadaan logika yang TETAP maka Output dari gerbang NAND dan OR akan berkebalikan:

Pada gerbang NAND jika (minimal) salah satu dari kedua Input diberi logika 0 maka Output akan berlogika 1, lalu jika kedua (semua) Input diberi logika 1, maka Output akan berlogika 0.

Sebaliknya, pada gerbang OR jika (minimal) salah satu dari kedua Input akan berlogika 0, maka Output akan berlogika 0, lalu jika kedua (semua) Input diberi logika 1, maka Output akan berlogika 1.

3. Analisa dari kedua sifat rangkain tersebut adalah: a. Pada gambar I:

Pada gambar tersebut terdapat gerbang NOT yang setiap inputnya akan menuju ke gerbang NOR. Ketika salah satu input berlogika 1, maka output akan berlogika (mati). Dan ketika kedua input berlogika 0, maka output akan berlogika 1 (menyala).

Pada gambar tersebut terdapat gerbang NOT yang setiap inputnya akan menuju ke gerbang NAND. Ketika salah satu input berlogika 1 maka output akan berlogika 1 (menyala). Ketika kedua input berlogika 1 maka output akan berlogika 0 (mati).

VII. SIMPULAN

Kesimpulan yang dapat diambil dari praktik gerbang logika tersebut adalah masing-masing IC memiliki fungsi dan cara kerja yang berbeda. Hal tersebut dikarenakan masing-masing IC memiliki jenis Gerbang yang berbeda. IC bekerja sesuai dengan fungsinya:

IC 7432 merupakan Gerbang OR. IC 7408 merupakan Gerbang AND. IC 7404 merupakan Gerbang NOT. IC 7402 merupakan Gerbang NOR. IC 7400 merupakan Gerbang NAND. IC 7486 merupakan Gerbang EX-OR.

Gerbang logika merupakan pembentuk sistem digital dimana sebuah logika digambarkan melalui perhitungan Benar (logika 1) dan salah (logika 0). Beberapa sifat Pokok dari masing-masing Gerbang dasar logika antara lain:

OR : Output akan menyala (berlogika 1) ketika (minimal) salah satu dari kedua input berlogika 1.

AND : Output akan menyala (berlogika 1) ketika kedua (semua) input berlogika 1.

NOT : Memiliki sifat berlawanan dengan inputnya, jika inputnya berlogika 1 maka output akan berlogika 0, begitu pula sebaliknya.

NOR : Adalah kebalikan dari Gerbang AND; Output akan menyala (berlogika 1) ketika kedua (semua) input berlogika 0.

Laporan Praktikum II Praktik Teknik Digital UNIVERSAL NAND GATE

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

A. TUJUAN

Praktik diharapka dapat menerapkan NAND Gate sebagai Universal Gate yang dapat membentuk dan mempunyai sifat sebagai gerbang gerbang logika dasar.

B. PENDAHULUAN

NAND Gate disebut juga sebagai Universal gate karena gate-gate dasar yang lain seperti OR, AND, NOT, NOR, EX-OR dan EX-NOR dapat dibentuk dari NAND Gate.

Dari gambar diatas dapat dibuktikan bahwa persamaan output X = (A.A)’ = (A)’

C. ALAT DAN BAHAN 1. Digital Trainer

2. IC TTL Tipe : SN 7400 (NAND Gate)

D. LANGKAH PERCOBAAN

1. Memahami terlebih dahulu IC-IC yang akan dipergunakan.

2. Menghubungkan power supply dengan tegangan 220 volt. Jangan di ON sebelum yakin bahwa rangkaian sudah terangkai dengan benar.

3. Menghubungkan terminal Vcc dari semua modul yang akan digunakan pada terminal +5 Volt dari power supply.

4. Menghubungkan terminal GND dari semua modul yang akan digunakan pada terminal GND dari power supply.

5. Merangkai NOT Gate dari NAND Gate seperti yang ditunjukan pada gambar 2.1 6. Menghubungkan terminal input dari gate ke unit input pada trainer.

7. Menghubungkan terminal output dari gate ke tindikator LED.

9. Mengulangi langkah 1 sampai dengan 8 untuk gambar 2.2, 2.3, 2.4, 2.5, 2.6, 2.7 bernilai 1, serta jika inputnya bernilai 1+0 maka outputnya akan bernilai 1.

2. NOT GATE DARI NAND GATE (IC 7400)

Gerbang AND merupakan kebalikan dari gerbang NAND, dimana ketika

inputnya bernilai 1+1 maka outputnya akan bernilai 1 (menyala), sebaliknya jika inputnya

bernilai 0+0 maka outputnya akan bernilai 0 (mati), sedangkan ketika inputnya bernilai

4. OR GATE DARI NAND GATE (IC 7400)

Gerbang OR memiliki dua buah input dan satu output. jika input bernilai 0+0 maka outputnya akan bernilai 0 (mati), sebaliknya jika input memiliki nilai 1+1 maka

outputnya akan memiliki nilai 1 (menyala), dan apabila nilai input bernilai 1+0 maka output akan bernilai 1 (menyala), begitu juga sebaliknya jika input bernilai 0+1 maka output akan bernilai 1 (menyala).

5. NOR GATE DARI NAND GATE (IC 7400)

Pada NOR Gate memiliki 2 input dan satu output dengan sifat yaitu, jika input bernilai 0+0 maka output akan bernilai nilai 1 (menyala), sebaliknya jika input menunjukkan pada keadaan nilai 1+1 maka outputnya kan bernilai 0 (mati), kemudian jika input menunjukkan nilai 0+1 maka outputnya akan menampilkan nilai 0 (mati) begitu juga sebaliknya jika inputnya menunjukan nilai 1+0 maka outputnya akan menunjukkan nilai 0 (mati).

6. EX-OR GATE DARI NAND GATE (IC 7400)

outputnya

akan bernilai 0, dan juga sebaliknya jika inputnya bernilai 1+1 maka outputnya akan bernilai 0, kemudian jika inputnya bernilai 0+1 maka outputnya akan bernilai 1, begitu pula jika inputnya memiliki nilai 1+0 maka nilai outpunya akan memiliki nilai 1.

7. EX-NOR GATE DARI NAND GATE (IC 7400)

Pada gerbang EX-NOR memiliki sifat yaitu, jika input bernilai 0+0 maka outputnya akan bernilai 1 (menyala), dan jika inputnya bernilai 1+1 maka outputnya kan bernilai 1

(menyala) juga, kemudian jika inputnya memiliki nilai 0+1 maka outputnya kan bernilai

0 (mati), serta jika inputnya menunjukkan nilai 1+0 maka outputnya akan menunjukkan nilai 0 (mati).

F. PERTANYAAN DAN TUGAS

1. Bagaimana sifat dari gerbang dasar yang dibentuk oleh Universal NAND Gate, bandingkan dengan percobaan sebelumnya?

Sifat dari gerbang dasar yang dibentuk oleh universal NAND Gate adalah memiliki sifat yang sama dengan gerbang dasar logika itu sendiri. Hanya saja yang membedakan dengan percobaan yang sebelumnya adalah pada rangkaian dan penggunaan IC, dimana pada percobaan kali ini hanya menggunakan satu IC yaitu IC NAND Gate Tipe : SN 7400, Namun pada dasarnya hal tersebut tidak

mempengaruhi fungsi kerja dari gerbang logika dan sifat asli dari masing – masing gerbang logika, karena IC tersebut memiliki banyak gerbang logika.

2. Bagaimana persamaan output dari gerbang NOT, AND, OR, NOR, EX-OR, dan EX- NOR yang tersusun dari Universal NAND Gate?

Jawab:

a) NOT Gate akan mempunyai nilai output yang berlogic 1 (menyala) ketika nilai inputnya berlogic 0 (mati).

Persamaan output NOT = (A . A) = (A)’

b) AND Gate akan mempunyai nilai output yang berlogic 1 (menyala) hanya ketika kedua nilai inputnya berlogic 1 (menyala).

Persamaan output AND = (AB) . (AB) = (AB) . (AB)

c) OR Gate akan mempunyai nilai output yang berlogic 0 (mati) hanya ketika kedua inputnya bernilai logic 0 (mati), selain itu akan menghasilkan output yang bernilai berlogic 1 (menyala).

Persamaan output OR = (AA) . (BB) = (AA) . (BB)

d) NOR Gate akan mempunyai nilai output yang berlogic 1 (menyala) hanya ketika kedua inputnya memiliki nila logic 0 (mati), selain itu outputnya akan menghasilkan nilai logic 0 (mati).

Persamaan output NOR = (AA)(BB) . (AA)(BB)’ = (AA)(BB) . (AA)(BB) e) Ex-OR Gate akan mempunyai output yang bernilai 1 (menyala) hanya ketika

kedua inputnya memiliki nilai logic yang berbeda, jika logic kedua inputnya sama maka outputnya akan menghasilkan nilai logic 0 (mati).

f) Ex-NOR Gate akan mempunyai logic yang bernilai 1 (menyala) hanya ketika kedua inputnya memiliki logic yang berbeda, jika logicnya memiliki input yang sama maka outputnya akan menghasilkan nilai logic 0 (mati).

Jadi walupun menggunakan IC dari NAND Gate tidak mempengaruhi fungsi dan sifat dari input dan output asli gerbang logika dasar.

G. KESIMPULAN

Dari rangkaian percobaan tersebut ditarik kesimpulan bahwa Gerbang NAND adalah suatu NOT-AND, atau suatu fungsi AND yang dibalikkan. Dengan kata lain bahwa gerbang NAND akan menghasilkan sinyal keluaran rendah jika semua sinyal masukan bernilai tinggi. gerbang logika dasar seperti OR, AND, NOT, NOR, OR, dan EX-NOR dapat dibentuk dari rangkaian NAND Gate sehingga disebut Universal Gate. Penggunaan IC NAND Gate dengan Tipe SN 7400 tidak mempengaruhi fungsi dan sifat dari masing-masing gerbang logika. Sehingga masing-masing gerbang logika masih meliliki fingsi dan sifat aslinya. Hanya saja terkadang keluaran yang

dihasilkan oleh Universal NAND Gate kurang maksimal. Kemungkinan salah satu atau beberapa disebabkan karena terlalu banyaknya koneksi antar segmen sehingga

kemungkinan salah satu atau beberapa koneksi tidak terkoneksi dengan benar.

H. LAMPIRAN

Rangkaian NOR GATE

Rangkaian EX-OR GATE

Rangkaian AND GATE

Laporan Praktikum III Praktik Teknik Digital ALJABAR BOOLEAN

Disusun Oleh :

Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

A.

TUJUANPraktikan diharapkan dapat memahami prinsip dari aljabar Boolean dan menarapkanya dalam rangkaian gerbang logika.

B.

KAJIAN TEORISetiap rangkaian logika, bagaimanapun kompleksnya, dapat diuraikan secara lengkap dengan menggunakan operasi-operasi Boolean. Perhatikan rangkaian pada gambar 3.1. Rangkaian ini terdiri dari 3 input, A, B, dan C

dan suatu output X. Dengan menggunakan ekspresi Boolean untuk tiap gate dengan mudah dapat ditentukan ekspresi outputnya.

Gambar 3.1. Rangkaian logika dengan ekspresi Booleannya.

Contoh lain adalah sebuah fungsi X = A’ B + A B’. Untuk membuat rangkaian digital dari fungsi diatas diperlukan gerbang NOT, AND, dan OR . Dari fungsi diatas dapat diidentifikasi bahwa fungsi tersebut mempunyai 2 buah input dan 1 buah output. Fungsi tersebut dapat diimplementasikan dalam rangkaian logika seperti gambar 3.2 dibawah ini.

C.

ALAT DAN BAHAN6 Kabel Kecil / Kabel Terminal secukupnya

D.

LANGKAH PERCOBAAN1. Memahami terlebih dahulu IC-IC yang akan dipergunakan.

2. Menghubungkan power supply dengan tegangan 220 Volt. Jangan di ON sebelum yakin bahwa rangkaian sudah terangkai dengan benar.

3. Menghubungkan terminal Vcc dari semua modul yang akan digunakan pada terminal +5 Volt dari power supply.

4. Menghubungkan terminal GND dari semua modul yang akan digunakan pada terminal GND dari power supply.

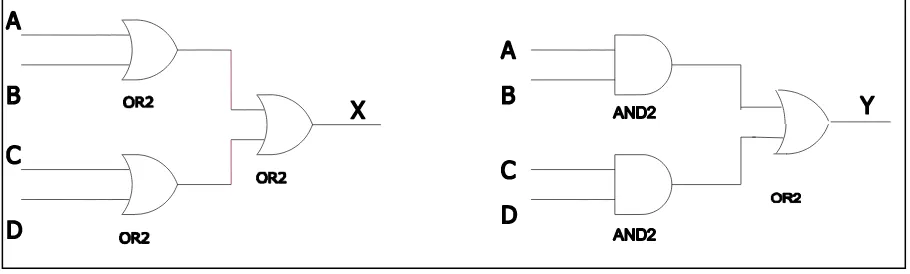

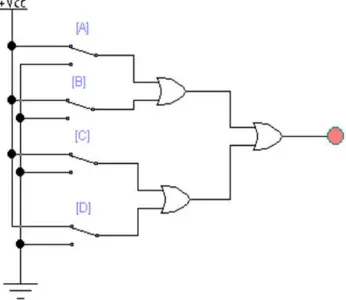

5. Membuat rangkaian logika yang mempunyai fungsi output: X = A+B+C+D

Y = (AB)+(CD)

6. Menghubungkan terminal input dari gate ke unit input pada trainer. 7. Menghubungkan terminal output dari gate ke indicator LED.

8. Memberi kondisi logic input sesuai dengan table, amati dan catat kondisi

outputnya. Jika LED menyala berarti logic tinggi (1), jika LED padam berarti logic rendah (0).

G.

ANALISA PERCOBAAN 1. Fungsi X = (A + B + C + D)Dengan menggunakan aljabar Boolean dengan fungsi X=(A+B+C+D) dapat diselesaikan menggunakan hukum-hukum teori logika. Hukum teori logika yang bisa dipakai disini yaitu hukum komutatif dan assosiatif. Hukum Komutatif untuk Gerbang Logika OR yaitu jika 2 masukan tertentu, yaitu A dan B, dapat

dipertukarkan tempatnya dan dapat merubah urutan sinyal-sinyal masukan.

Perubahan tersebut tidak akan mempengaruhi keluarannya. Jika pada gerbang OR menggunakan hukum assositif yaitu apabila 2 masukan tertentu yaitu A dan B, dapat dikelompokan tempatnya dan diubah urutan sinyal-sinyal masukannya. Perubahan tersebut tidak akan mengubah keluarannya. Dari penjelasan tersebut,

Fungsi X = A+B+C+D = (A+B) + (C+D)

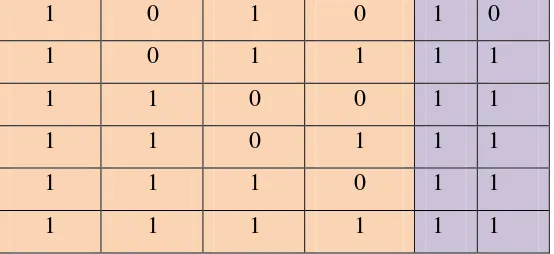

Berikut ini tabel kebenaran dari fungsi tersebut yaitu :

1 1 1 0 1

1 1 1 1 1

Sehingga dapat disimpulkan dari rangkaian tersebut, apabila 4 input menggunakan gerbang OR maka outputnya semua akan bernilai 1 kecuali apabila inputnya semuanya bernilai 0, maka outputnya juga akan bernilai 0.

2. Fungsi Y = (A.B) +(C.D)

Dengan menggunakan aljabar boole dengan fungsi Y = (A.B) +(C.D) dapat diselesaikan menggunakan hukum-hukum teori logika. Salah satunya hukum komutatif dan assosiatif. Pada hukum tersebut untuk Gerbang Logika OR yaitu jika 2 masukan tertentu, yaitu A dan B, dapat dipertukarkan tempatnya dan dapat merubah urutan sinyal-sinyal masukan. Perubahan tersebut tidak akan mempengaruhi

keluarannya. Menggunakan hukum assosiatif pada saat 2 masukan tertentu yaitu A dan B, dapat dikelompokan tempatnya dan diubah urutan sinyal-sinyal masukannya. Perubahan tersebut tidak akan mengubah keluarannya.

Dari penjelasan tersebut, Fungsi Y= (AB)+(CD)

= (BA)+(DC) = (DC)+(BA)

Berikut ini tabel kebenaran dari fungsi tersebut : yang bernilai 1, maka output tetap akan bernilai 0.

1 0 1 0 1 0

1 0 1 1 1 1

1 1 0 0 1 1

1 1 0 1 1 1

1 1 1 0 1 1

1 1 1 1 1 1

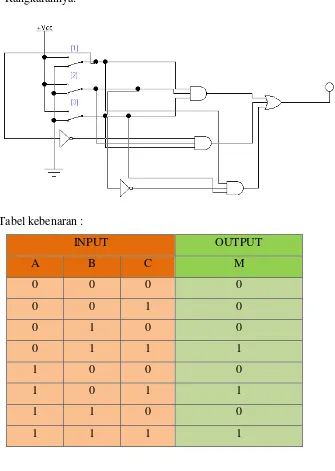

2. Rangkaian logika dari fungsi aljabar Boolean: a) M = (AB)’C + A (BC)’ + (ABC)’

Rangkaiannya:

Tabel kebenaran :

INPUT OUTPUT

A B C M

0 0 0 1

0 0 1 1

0 1 0 1

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 1

b) M = ABC + A’BC + AB’C

dan di OR kan outputnya akan bernilai 1 ketika ada salah satu atau semua output pada gerbang AND yang berlogika 1.

Laporan Praktikum IV Praktik Teknik Digital Aplikasi Teorema De Morgan

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

K.

TUJUANSetelah selesai Praktikum mahasiswa dapat: 1. Membuktikan Teorema De Morgan I. 2. Membuktikan Teorema De Morgan II.

3. Mempelajari sifat-sifat dan cara kerja dari satu rangkaian Exclusive-OR Gate yang dibentuk dari AND, OR, dan NOT Gate.

4. Mempelajari sifat-sifat dan cara kerja dari satu rangkaian Exclusive-OR Gate yang dibentuk dari NOR dan NOT Gate.

5. Mempelajari sifat-sifat dan cara kerja dari satu rangkaian Exclusive-OR Gate yang dibentuk dari NAND dan NOT Gate.

L.

KAJIAN TEORIPada Hukum De Morgan, terdapat dua persamaan yaitu :

1. Suatu rangkaian NAND gate gate adalah equivalen dengan rangkaian OR yang menggunakan NOT gate pada setiap inputnya.

(A . B)` = A` + B`

2. Suatu rangkaian NOR gate adalah ekuivalen dengan rangkaian AND gate yang menggunakan NOT gate pada setiap input-inputnya.

(A + B)` = A` . B`

M.

ALAT DAN BAHAN 7 Digital Trainer 8 Power Supply9 IC 7408 (AND Gate) 10 IC 7432 (OR Gate) 11 IC 7404 (NOT Gate) 12 IC 7402 (NOR Gate) 13 IC 7400 (NAND Gate)

14 Kabel Kecil / Kabel Terminal secukupnya

N.

LANGKAH PERCOBAANPERCOBAAN A

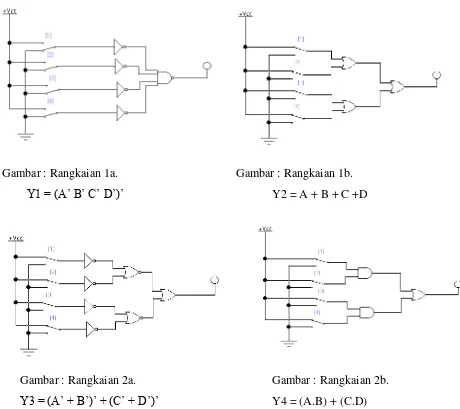

1. Buat rangkaian logika seperti pada gambar 1a dan 1b

Gambar : Rangkaian 1a. Gambar : Rangkaian 1b.

Y1 = (A’ B’ C’ D’)’ Y2 = A + B + C +D

Gambar : Rangkaian 2a. Gambar : Rangkaian 2b.

2. Kemudian berikanlah keadaan logika pada terminal-terminal input A, B, dan D dengan menggunakan sakar seperti pada Tabel 1 berikut. Catatlah keadaan outputnya.

3. Lakukan langkah 1 dan 2 untuk gambar 2a dan 2b.

Pada gambar rangkaian 1a dan 1b, merupakan gambar rangkaian untuk membuktikan teori De Morgan I yang berbunyi bahwa :

Gambar 1a Gambar 1b

Y1 = A . B . C . D Y2=A+B+C+D

Misalnya masing-masing dari rangkaian Y1 dan Y2 diberi nilai input 0. Maka dalam rangkaian gambar 1a, input akan masuk kedalam inverter, kemudian output dari gerbang NOT masing – masingnnya yakni logic 1. Semua output dari inverter tersebut kemudian masuk menuju gebang NAND, sehingga output Y1 berlogic 0. Serta dalam rangkaian gambar 1b, masing – masing input berlogic 0, kemudian masuk ke Gerbang OR sehingga berlogic 0 semua. Semua output tersebut masuk ke Gerbang OR lagi, maka akan menghasilkan output berlogic 0. Sehingga kedua rangkaian tersebut akan menghasilkan output sama dan

membuktikan teori tersebut Benar.

Sehingga diperoleh persamaan output antara gambar 1a dan 1b,

Pada gambar rangkaian 2a dan 2b merupakan gambar rangkaian untuk membuktikan Teori De Morgan II yang berbunyi bahwa :

Jika Teori De Morgan benar, maka ketika kedua rangkaian tersebut diberi input yang sama, maka outputnya juga akan bernilai sama.

Gambar 2a Gambar 2b

Y3 = (A+B)+(C+D) Y4 = (A.B) + (C.D)

Misalnya masing-masing dari rangkaian Y3 dan Y4 diberi nilai input 0. Dalam rangkaian gambar 2a, input yang diberikan oleh A, B, C dan D akan masuk kedalam Inverter. Setelah semua input masuk kedalam inverter, maka nilai yang dihasilkan adalah yakni masing – masing berlogic 1. Kemudian ke empat input tersebut masuk kedalam dua buah gerbang NOR dan menghasilkan 2 buah output bernilai “0” dan “0”. Kemudian masuk kedalam gerbang OR sehingga outputnya (0+0)=”0” (padam). Dalam rangkaian gambar 2b ini, semua input berlogic 0, kemudian masuk ke Gerbang AND dan akan menghasilkan 2 output dengan logic 0.Kedua output tersebut selanjutnya masuk ke Gerbang OR dan akan

menghasilkan ouput berlogic 0. Sehingga diperoleh persamaan output yang sama antara gambar 2a dan 2b yaitu

Y3 = ( A + B ) + ( C + D ) Y4 = (A.B) + (C.D) = ( A · B ) + ( C · D )

= AB + CD

Sehingga, dari data percobaan diatas dapat saya simpulkan Teori ini telah terbukti Benar.

Q.

PERTANYAAN DAN TUGAS3. Buatlah Tabel Kebenaran dari ke-4 percobaan tersebut, seperti terlihat pada Tabel 1. 4. Bandingkan hasil – hasil dari percobaan tersebut. Kesimpulan apa yang dapat diambil dari

perbandingan ini? Jawab :

Input Output

2. Berikut perbandingan dari percobaan yaitu

a. Nilai output yang dihasilkan rangkaian 1a dan 1b yakni Y1 dan Y2 adalah sama, hal ini membuktikan bahwa rangkaian gerbang logika NAND bernilai output sama dengan rangkaian gerbang OR yang menggunakan gerbang NOT pada setiap inputnya.

b. Nilai output yang dihasilkan rangkaian 2a dan 2b yakni Y3 dan Y4 adalah sama, hal ini membuktikan bahwa rangkaian gerbang logika NOR bernilai output sama dengan rangkaian gerbang AND yang menggunakan gerbang NOT pada setiap inputnya.

R.

KESIMPULANgerbang AND yang diberi gerbang NOT pada setiap inputnya. (AB) = A + B

(A+B) = A . B

Teori ini digunakan untuk menyederhanakan sebuah rangkaian logika agar gerbang-gerbang logika yang dibutuhkan lebih sedikit dan efisien. Namun tetap memiliki nilai keluaran yang sama. Jika gerbang logika yang dipakai lebih sedikit, maka secara otomatis rangkaian tersebut akan menjadi lebih mudah untuk dideteksi jika terjadi sebuah kesalahan.

Laporan Praktikum V Praktik Teknik Digital Adder (Half dan Full Adder)

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

A. TUJUAN

Praktikan diharapkan dapat :

1. Merangkai dan menjelaskan cara kerja rangkaian half adder. 2. Merangkai dan menjelaskan cara kerja full adder.

B. KAJIAN TEORI 1. Half Adder

Half adder adalah suatu rangkaian penjumlah system bilangan biner yang paling

sederhana. Rangkaian ini hanya dapat digunakan untuk operasi penjumlahan data bilangan biner sampai 1 bit saja. Rangkaian half adder mempunyai 2 masukan dan 2 keluaran yaitu Summary out (Sum) dan Carry out (Carry).

Masukan : A = 1 Masukan : A = 1 Dimana A dan B merupakan data-data Input.

2. Full Adder

Masukan : Carry_in = 0 Masukan : Carry_in = 1

A = 1 A = 1

B = 0 B = 1

--- + --- +

Keluaran : 0 1 Keluaran : 1 1

Carry_out Carry_out

Sum Sum

Persamaan logikanya adalah (berdasarkan tabel kebenaran) : Sum = (A+B) + C_in

C_out = (A.B) + (A.C_in) + (B.C_in)

C. ALAT DAN BAHAN PERCOBAAN 1. Digital Trainer.

D. LANGKAH PERCOBAAN

1. Membuat rangkaian half adder seperti pada gambar 1.

Gb. 1. Half adder

2. Mengatur keadaan logic dari kedua inputnya A dan B sesuai dengan tabel kebenaran dan catat keadaan outputnya.

3. Membuat rangkaian half adder dengan Exclusive-OR seperti pada gambar 2.

Gb. 2. Half adder

4. Mengatur keadaan logic dari kedua inputnya A dan B sesuai dengan tabel kebenaran dan catat keadaan outputnya.

5. Membuat rangkaian full adder seperti pada gambar 3.

Gb. 3. Full Adder

6. Mengatur keadaan logic dari kedua inputnya A, B dan Carry In sesuai dengan tabel kebenaran dan catat keadaan outputnya.

E. Hasil Praktikum

Input Output

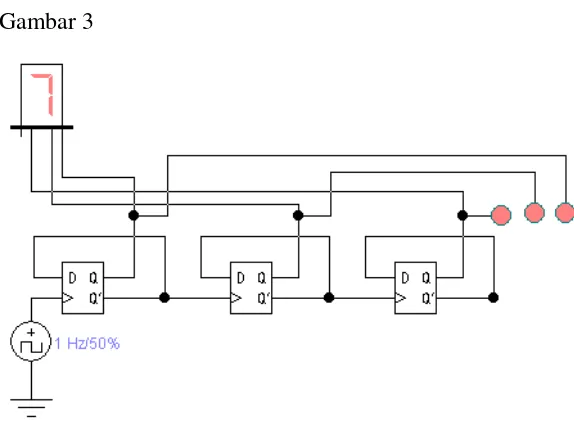

Berikut ini tabel kebenaran dari Gambar 3

Gambar 1. Half Adder Maka persamaan logikanya menjadi :

Untuk output SUM : (A' B) + (A B') Untuk output Carry : (AB)

Gambar 2. Half Adder Maka persamaan logikanya menjadi :

Untuk output SUM : (A B) Untuk output Carry : (AB)

Berikut ini tabel kebenaran rangkaian Half Adder pada Gambar 1 dan 2.

Input Output

A B Carry Out SUM

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

2. Gambar 3

Pada rangkaian ketiga ini (Full Adder) merupakan rangkaian penjumlahan untuk menjumlahkan beberapa bit biner. Rangkaian ini disusun dari Half Adder yang digabungkan menggunakan gerbang OR. Sehingga penjumlahan tersebut pada

Gambar 3 Full Adder Maka persamaan logikanya menjadi :

Untuk output SUM : A B Carry In Untuk output Carry : AB+ (A B) Carry In

Berikut ini tabel kebenaran dari Gambar 3

Input Output

1. Rancanglah sebuah rangkaian Full Adder dengan menggunakan gerbang OR, AND dan NOT.

2. Buatlah kesimpulan dari percobaan yang telah dilakukan. Jawab :

1. Rangkaian Full Adder

2. Kesimpulan dari rangkaian diatas

Berdasarkan rangkaian tersebut didapatkan tabel kebenaran sebagai berikut.

INPUT OUPUT

Dari percobaan di atas kita dapat menyimpulkan bahwa :

1. Full Adder dapat digunakan untuk menjumlahkan rangkaian bilangan-bilangan biner yang lebih dari 1 bit. Penjumlahan bilangan-bilangan biner sama halnya dengan penjumlahan bilangan decimal dimana hasil penjumlahan tersebut terbagi menjadi 2 Output, yaitu Summary (Jumlah Hasil) dan Carry (Simpan).

2. Rangkaian half adder dapat dibentuk dengan menggunkan gerbang NOT, AND, dan OR ataupun bisa dirangkai menggunakan gerbang logika EX-OR dan AND.

3. Dalam rangkaian Half Adder, apabila salah satu switch berlogic 1, maka hasil outputnya; Sum bernilai 1 dan Carry bernilai 0.

4. Rangkaian Full adder dapat digunakan untuk menjumlahkan bilangan biner yang lebih dari 1 bit. Pada rangkaian ini terdapat 3 input yaitu Carry In, A dan B. Rangkain ini dapat dibuat menggunakan gerbang logika OR, NOT, dan OR ataupun dapat dibentuk menggunakan gerbang logika EX-OR, AND, dan OR.

5. Dalam rangkaian Full Adder 1 bit, apabila semua switch berlogic 1, maka hasil outputnya semua bernilai 1.

Laporan Praktikum VI Praktik Teknik Digital

Subtractor 1 Bit

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

VIII. TUJUAN PERCOBAAN

Setelah selesai Praktikum Mahasiswa diharapkan dapat:

1. Merangkai dan menjelaskan cara kerja rangkaian Half Subtractor. 2. Merangkai dan menjelaskan cara kerja rangkaian Full Subtractor.

IX. DASAR TEORI A.Half Substractor

Half subtractor adalah suatu rangkaian yang dapat digunakan untuk melakukan operasi pengurangan data-data bilangan biner hingga 1 bit saja. Half substractor mempunyai karakteristik : 2 masukan yaitu input A dan B serta 2 keluaran yaitu Summary (Sum) dan Borrow. Pada contoh berikut, input B sebagai bilangan pengurangnya dan input A sebagai bilangan yang dikurang.

Masukan : A = 1 Masukan : A = 0 Dimana A dan B merupakan data-data Input.

B. Full Subtractor

Rangkaian full subtractor digunakan untuk melakukan operasi pengurangan bilangan biner yang lebih dari 1 bit. Dengan 3 terminal input yang dimilikinya yaitu A, B, serta terminal Borrow input dan 2 terminal output yaitu Sum dan Borrow out.

X. ALAT DAN BAHAN PERCOBAAN 8. Power Supply

9. Digital Trainer (EWB512)

10. IC TTL tipe : SN 7408 (AND Gate) 11. IC TTL tipe : SN 7432 (OR Gate) 12. IC TTL tipe : SN 7404 (NOT Gate) 13. IC TTL tipe : SN 7486 (EX-OR Gate)

XI. LANGKAH PERCOBAAN

1. Membuat rangkaian Half Subtractor seperti pada gambar 1.

Gambar 1: Rangkaian Half Subtractor 1

2. Mengatur keadaan logika dari kedua inputnya A dan B sesuai dengan tabel kebenaran dan mencatat keadaan outputnya.

3. Membuat rangkaian Half Subtractor dengan Ex-Or seperti pada gambar 2.

Gambar 2: Rangkaian Half Subtractor 2

4. Mengatur keadaan logika dari kedua inputnya A dan B sesuai dengan tabel kebenaran dan mencatat keadaan outputnya.

Gambar 3: Rangkaian Full Subtractor

6. Mengatur keadaan logika dari kedua inputnya A, B dan Borrow In sesuai dengan tabel kebenaran dan mencatat keadaan outputnya.

XII. LAPORAN HASIL PENGAMATAN

A.Tabel 1 : Percobaan rangkaian Half Subtractor 1

INPUT OUPUT

A B Borrow Out Sum

0 0 0 0

0 1 1 1

1 0 0 1

1 1 0 0

B. Tabel 2 : Percobaan rangkaian Half Subtractor 2

INPUT OUPUT

A B Borrow Out Sum

0 0 0 0

0 1 1 1

1 0 0 1

C.Tabel 3 : Percobaan rangkaian Full Subtractor 1

Dari hasil percobaan yang telah kami lakukan, kami mendapatkan beberapa data sebagai berikut.

A.Tabel 1&2 : Percobaan rangkaian Half Subtractor 1&2

INPUT OUPUT

Half subtractor merupakan suatu rangkaian yang dapat digunakan untuk melakukan operasi pengurangan data-data bilangan biner hingga 1 bit saja. Rangkaian half subtractor mempunyai 2 input dan 2 output yaitu Summary (Sum) dan Borrow.

B.Tabel 3 : Percobaan rangkaian Full Subtractor

INPUT OUPUT

Out

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 1 0

1 0 0 0 1

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

Full Subtractor merupakan rangkaian yang dapat di gunakan untuk melakukan operasi pengurangan bilangan biner yang lebih dari 1 bit. Full Subtractor memiliki standar minimal 3 terminal input yang dimilikinya yaitu A , B serta terminal Borrow Input dan 2 terminal output yaitu Summary (Sum) dan Borrow-Out.

XIV. PERTANYAAN DAN TUGAS

1. Rancanglah sebuah rangkaian Full Subtractor dengan menggunakan gerbang OR, AND dan NOT.

2. Buatlah kesimpulan dari percobaan yang telah dilakukan. Jawab :

1. Rangkaian Full Subtractor

Dari rangkaian Full Subtractor 1 bit dengan menggunakan gerbang OR, AND, NOT, didapatkan hasil sebagai berikut.

INPUT OUPUT subtractor merupakan rangkaian pengurang untuk mengurangkan lebih dari 1 bit. Rangkaian ini merupakan kombinasi dari rangkaian half dan memiliki 3 inputan. Input ketiga borrow in.

Laporan Praktikum VII Praktik Teknik Digital

Flip Flop

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

UNIVERSITAS NEGERI YOGYAKARTA 2016

XVII. TUJUAN PERCOBAAN

Setelah selesai Praktikum Mahasiswa diharapkan dapat:

3. Memahami kerja rangkaian Latch yang tersusun dari gerbang NAND. 4. Memahami kerja rangkaian Latch yang tersusun dari gerbang NOR.

5. Memahami cara kerja rangkaian Clocked R-S Flip-Flop dari NAND Gate dan NOR Gate.

6. Menjelaskan sifat dan cara kerja rangkaian D Flip-Flop dari NAND Gate.

7. Menjelaskan sifat dan cara kerja rangkaian D Flip-Flop yang menggunakan IC tipe 7474.

8. Menjelaskan sifat dan cara kerja rangkaian J-K Flip-Flop dengan menggunakan IC tipe 7473.

9. Merangkai dan menganalisa rangkaian T Flip-Flop.

10. Menjelaskan sifat dan cara kerja rangkaian T Flip-Flop.

XVIII. DASAR TEORI

A. NAND GATE LATCH

Rangkaian dasar Flip-Flop dapat disusun dari dua buah NAND gate atau NOR gate. Apabila disusun dari NAND gate, disebut dengan NAND Latch atau secara sederhana disebut latch, seperti ditunjukkan pada gambar 7.1 (a). Dua buah NAND gate disilangkan antara output NAND gate-1 dihubungkan dengan salah satu input NAND gate-2, dan sebaliknya. Output gate (output latch) diberi nama Q dan Q’. Pada kondisi normal kedua output tersebut saling berlawanan. Input latch diberi nama SET dan RESET.

Gambar 7.1 (b) menunjukkan symbol dari NAND gate latch.

B. NOR GATE LATCH

Dua buah NOR gate yang paling disilangkan dikenal sebagai NOR gate latch,

dengan dua buah output Q dan Q’ yang saling berlawanan serta dua buah input SET dan

RESET, seperti ditunjukkan pada gambar 7.2. Jika logika 1 diberikan pada input S, maka kondisi ini menyebabkan FF di set ke 1 (Q=1). Jika logika 1 diberikan ke input R, maka

kondisi ini menyebabkan FF di reset ke 0 (Q=0).

Gambar 7.2 NOR gate Latch

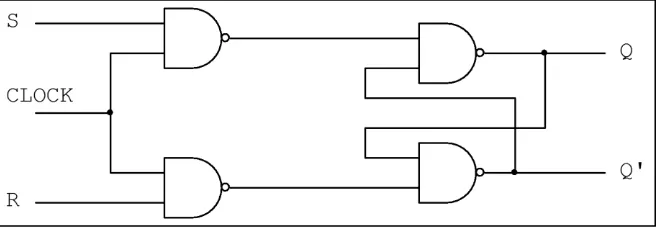

C. CLOCKED R-S FLIP – FLOP

Clocked RS Flip-Flop merupakan suatu latch yang dilengkapi dengan sebuah terminal untuk pulsa clock. Pulsa clock tersebut akan mengatur keadaan SET ataupun RESET dari Flip-Flop ini, yang juga tergantung dari keadaan logic pada terminal-terminal input R dan S nya.

Apabila pulsa clock berada pada keadaan logic 0, maka perubahan keadaan logic pada terminal input R dan S tidak akan mengakibatkan perubahan pada input Q dan Q’.

Tetapi bila pulsa clock berada pada keadaan logic 1, maka perubahan-perubahan pada input R dan S akan mengakibatkan perubahan pada output Q dan Q’. Perubahan tersebut sesuai dengan sifat latch pembentuknya.

Clocked RS Flip-Flop akan berada pada keadaan SET (Q=1) bila pulsa clock berada pada keadaan 1 dan input S juga berada pada keadaan SET (Q=1) bila pulsa clock berada pada keadaan q dan input S juga berada pada keadaan logic 1. Sedangkan keadaan RESET (Q=0) akan terjadi jika pulsa clock berada pada keadaan logic 1 dan input R berada pada keadaan logic 1.

D. CLOCKED RS FLIP-FLOP DENGAN NAND GATE

(Q=1) bila pulsa clock berada pada keadaan 1, dan input S juga berada pada keadaan logic 1. Sedangkan keadaan RESET (Q=0) akan terjadi jika pulsa clock berada pada keadaan logic 1 dan input R juga berada pada keadaan logic 1.

E. D FLIP-FLOP DENGAN NAND GATE

D Flip-Flop merupakan suatu RS Flip-Flop yang ditambah dengan suatu inverter pada RESET inputnya. Sifat dari suatu D FF adalah : Output Q akan berada pada keadaan logic (Q=1) bila input D dan pulsa clock dalam keadaan logic 1. Dan bilamana input D dalam keadaan logic 0, maka D FF ini akan berada dalam keadaan RESET (Q=0).

Jika Clock berada pada kondisi logic 0, maka perubahan logic pada input D tidak akan mempengaruhi outputnya.

F. D FLIP-FLOP DENGAN IC 7474

Di dalam sebuah IC tipe 7474, terdapat 2 buah D FF yang memiliki terminal CLEAR dan PRESET. Apabila diberikan logic 0 ke terminal CLEAR maka output Q akan bearada pada keadaan logic 1 (SET).

Fungsi dari terminal-teminal input lainnya, yaitu Cloock dan Data (D), samadengan D FF biasa. Keadaan-keadaan logic yang terdapat pada input D akan diteruskan ke output Q pada saat pulsa clock berubah dari keadaan logic 0 ke keadaan logic

D FF ini dapat digunakan untuk membuat rangkaian-rangkaian antara lain Shift Resgister, counter.

G. CLOCKED J-K FF

Gambar 10.1 (a) menunjukkan seubah Clocked JK FF yang ditrigger oleh sisi menuju positip dari pulsa cock. Input – input J dan K mengontrol keadaan FF dengan cara yang sama seprti input-input S dan R kecuali satu perbedaaan menetu. Untuk keadaan ini FF akan selalu berada dalam keadaan yang berlawanan.

Gambar 10.1 Clocked JK Flip-Flop

a) Mula-mula semua input adalah 0 dan output Q samadengan 1.

b) Apabila terjadi sisi menuju positif dari pulsa clock pertama berlangsung pada kondisi J=0 dan K=1, maka output Q=0.

c) Pulsa clock kedua mendapatkan J=0 dan K=0 pada saat melakukan transisi positipnya, ini menyebabkan output Q tetap berada pada kondisi sebelumnya yaitu Q=0.

d) Pulsa clock ketiga mendapatkan J=1 dan K=0 pada saat melakukan transisi positipnya, ini menyebabkan output Q=1.

e) Pulsa Clock keempat mendapatkan J=1 dan K=1 pada saat melakukan transisi positipnya, ini menyebabkan FF toggle sehingga output Q berlawanan dari kondisi sebelumnya yaitu menjadi Q=0.

Gambar 10.2 Bentuk Gelombang

Dari bentuk gelombang ini hendaknya diperhatikan bahwa FF tidak terpengaruh oleh sisi menuju positip dari pulsa clock. JK FF adalah jauh klebih baik dari pada SR FF karena tidak mempunyai keadaan kerja yang tidak menentu. Keadaan J=K=1, yang menghasilkan operasi toggle, sangat banyak ditemukan pemakiannya di dalam semua jenis alat hitung biner. Oleh karena itu, JK FF digunakan secara luas oleh hamper semua sisitem-sistem digital.

H. T FLIP-FLOP

T (Toggle) Flip-Flop dapat diterminal T inpuy maka terbentuk dari modifikasi

clocked RS FF, D FF maupun J-K FF. T FF memiliki sebuah terminal masukan input, yaitu T input dan 2 buah terminal keluaran yautu Q dan Q’.

Apabila diberian pulsa-pulsa kontinyu pada terminal T input maka pada output-outputnya akan diperoleh pulsa – pulsa kontinyu dengan frekuensi sebesar setengah dari inputnya. Jadi setiap 2 buah pulsa input akan menghasilkan sebuah pulsa output. Pada percobaan ini dibuat suatu rangkaian T FF dengan menggunakan JK FF.

XIX. ALAT DAN BAHAN PERCOBAAN 14. Power Supply

3. Amati dan catat logika Q dan Q’ untuk setiap perubahan input. 4. Catat hasilnya pada table percobaan

5 .Ulangi langkah 1-4 untuk gambar 7.2 (a)

Gambar 7.2 a 2. RS Flip Flop

1. Buatlah rangkaian seperti pada gambar 9.1.

Gambar 9.1 Clocked RS Flip-Flop dengan NAND Gate

2. Hubungkan terminal input S , R dan Clock ke unit input yang ada pada trainer digital. 3. Periksa kembali semua rangkaian, jika sudah benar nyalakan power supply

4. Berikanlah masukan logik seperti pada tabel keterminal input S, R, dan Clock. Catat kondisi outputnya.

5. Matikan power supply.

Gambar 9.2 Clocked RS Flip-Flop dengan NOR Gate

7. Hubungkan terminal input S , R dan Clock ke unit input yang ada pada trainer digital. 8. Periksa kembali semua rangkaian, jika sudah benar nyalakan power supply

9. Berikanlah masukan logik seperti pada tabel keterminal inpur S, R, dan Clock. Catat kondisi outputnya.

10.Matikan power supply.

3. D Flip Flop

1. Buatlah rangkaian seperti pada gambar .1

Gambar 9.1 D FF dari NAND gate

2. Hubungkan terminal input D dan Clock ke terminal input logik pada trainer digital 3. Periksa kembali semua rangkaian, jika sudah benar nyalakan power supply

4. Berikanlah masukan logik seperti pada tabel keterminal input D dan Clock. Catat kondisi outputnya.

5. Matikan power supply.

7. Hubungkan terminal input D, Clock, PRESET dan CLEAR ke terminal input logik pada trainer digital

8. Periksa kembali semua rangkaian, jika sudah benar nyalakan power supply

9. Berikanlah masukan logik seperti pada tabel keterminal input D , Clock., PRESET dan CLEAR . Catat kondisi outputnya.

10.Matikan power supply.

Gambar 9.2. D Flip-Flop dengan IC 7474

4. JK Flip Flop

1. Buatlah rangkaian seperti pada gambar 10.3.

Gambar. 10.3. J – K Flip Flop

2. Hubungkan terminal input J , K , Clock dan Clear ke unit input yang ada pada trainer digital.

3. Periksa kembali semua rangkaian, jika sudah benar nyalakan power supply

4. Selanjutnya berikanlah keadaan-keadaan logik input seperti pada tabel, kondisi Clear pada logik 0 , amati kondisi outputnya.

6. Berikanlah masukan logik seperti pada tabel keterminal input S, R, dan Clock. Catat kondisi outputnya.

5. T Flip Flop

1. Buatlah rangkaian seperti pada gambar 11.

Gambar 11. T Flip-Flop dari J K Flip-Flop

2. Hubungkan terminal input J, K dan Clock ke terminal input logik pada trainer digital

3. Periksa kembali semua rangkaian, jika sudah benar nyalakan power

4. Berikanlah masukan logik seperti pada tabel keterminal, dan Catat kondisi outputnya.

XXI. LAPORAN HASIL PENGAMATAN

D.Tabel 1 : Percobaan NAND Gate Latch dan NOR Gate Latch

A B Clock Q Q’ Q Q’ 0 0 0 Tak Tentu Tak Tentu Tak Tentu Tak

Tentu

0 0 1 Tak Tentu Tak Tentu Q Q

0 1 0 Tak Tentu Tak Tentu Tak Tentu Tak Tentu

0 1 1 0 1 0 1

1 0 0 Tak Tentu Tak Tentu Tak tentu Tak tentu

1 0 1 1 0 1 0

1 1 0 Tak Tentu Tak Tentu Tak Tentu Tak Tentu

1 1 1 Q Q Tak Tentu Tak

Tentu 0 0 0 Tak Tentu Tak Tentu Tak Tentu Tak

Tentu

0 0 1 Tak Tentu Tak Tentu Q Q

0 1 0 Tak Tentu Tak Tentu Tak Tentu Tak Tentu

C. Tabel 3

INPUT OUPUT

D Clock Q Q’

0 0 Tak Tentu

0 1 0 1

1 0 Tak Tentu

1 1 1 0

0 0 Tak Tentu

0 1 0 1

1 0 Tak Tentu

1 1 1 0

D. Tabel 4 : Percobaan rangkaian D FF dengan IC 7474

INPUT INPUT OUTPUT

PRESET CLEAR CLOCK D Q Q’

0 0 0 0 1 1

0 0 0 1 1 1

0 1 1 1 1 0

1 0 0 0 0 1

1 0 0 1 0 1

1 1 1 0 Tak Tentu

1 1 0 1 Tak Tentu

Dari hasil percobaan yang telah kami lakukan, kami mendapatkan beberapa data sebagai berikut.

A. NAND dan NOR Gate Latch

Pada rangkaian NAND gate latch apabila Set diberi logik 1 dan Reset diberi logik 1 maka outputnya Q dan Q’ adalah Tak berubah. Bila Set diberi logik 0 dan Reset diberi logik 1 maka outputnya Q adalah 1 dan Q’adalah 0. Bila Set yang di input berlogik 1 dan Reset di input logik 0 maka outputnya Q adalah 0 dan Q’ adalah 1. Sedangkan jika Set dan Reset yang di input berlogik 0 maka outputnya Q dan Q’ adalah Tak Tentu.

Pada rangkaian NOR gate latch apabila Set dan Reset yang dinput berlogic 1 maka

outputnya Q dan Q’ adalah Tak Tentu. Apabila Set 0 dan Reset 1 maka Keluaran Nor

gate Q adalah 0 dan Q’ adalah 1. Apabila Set 1 dan Reset 0 maka Keluaran Nor gate Q

adalah 1 dan Q’ adalah 0. Sedangkan bila Set dan Resetnya berlogic 0 maka outputnya

Q dan Q’ adalah Tak Berubah.

B. RS FLIP FLOP

Pada rangkaian Clocked RS Flip-Flop dengan NAND gate, semua output akan berlogic Tak Tentu kecuali jika inputnya : a) S=0, R=1 dan Clock = 1, b) S=1, R=0 dan Clock berlogic 1, c) semua input S,R,Clock berlogic 1. Apabila nilai S=0, R dan Clock = 1, maka outputnya Q=0 dan Q’=1. Jika nilai S=1, R=0 dan Clock berlogic 1, maka outputnya Q=1 dan Q’=0. Jika semua input baik S,R, dan Clock=1, maka outputnya

outputnya berlogic Q=1 dan Q’=0. C. FLIP FLOP

Pada rangkaian D FF dari NAND gate apabila Input D dan Clock=0 maka outputnya Q dan dan Q’ berlogic Tak Tentu. Jika inputnya D=0, dan Clock=1 maka

outputnya adalah Q= 0 dan Q’=1. Jika inputnya D=1, Clock=0 maka keluaran Q dan

Q’= Tak Tentu. Sedangkan untuk input D dan Clock=1 maka keluaran Q= 1 dan Q’=0.

akan berlogic 0 jika semua input berlogic 0 ataupun Clock=0, dan D=1. Untuk Q berlogic 1 jika a) semua inputnya berlogic 0 atau 1, b) Clock=0, D=1, c) Clock=1, D=0. Sedangkan untuk Q’ berlogic 1 jika semua inputnya berlogic 0 ataupun Clock=1, D=0 dan Clock dan D=1.

D. JK FLIP FLOP

Pada rangkaian JK Flip-Flop jika Clear=0, Semua output Q akan menghasilkan

logic 0 dan Q’ berlogic 1. Dan pada rangkaian JK Flip-Flop jika Clear=1, semua

output Q akan berlogic 0 dan Q berlogic 1, kecuali jika logic J dan K=1 sedang Clock berlogic 0.

E. T FLIP FLOP

Pada rangkaian T F-F, semua input yang diinputkan nanti semuanya akan menghasilkan outputan yang sama yaitu Q berlogic 0 dan Q’ berlogic 1.

VIII. PERTANYAAN DAN TUGAS a) LATCH

1. Buatlah kesimpulan dari percobaan yang telah dilakukan. 2. Jelaskan kerja dari rangkaian Latch.

3. Jelaskan perbedaan antara NAND latch dengan NOR latch.

b) RS FLIP FLOP

1. Terangkan cara kerja rangkaian flip-flop diatas

2. Jelaskan perbedaan yang terdapat diantara rangkaian clocked RS Flip-Flop dengan RS Flip-Flop biasa.

3. Kesimpulan apa yang dapat diambil dari percobaan diatas.

c) D FLIP FLOP

1. Jelaskan fungsi Clock, Clear dan Preset dari D Flip-Flop. 2. Simpulkan percobaan yang telah dilakukan.

d) JK FLIP FLOP

e) T FLIP FLOP

1. Buatlah rangkaian pembagi frekuensi yang mempunyai nilai pembagian 4.

G. JAWABAN :

A LATCH

1. Pada rangkaian tersebut dapat disimpulkan bahwa terdapat 2 input yaitu S (Set) dan R

(Reset) yang mana juga mempunyai 2 output yaitu Q dan Q’. Rangkain Flip-flop

tersebut dapat dibentuk dari kombinasi dua gerbang NAND atau gerbang NOR. IC yang dipakai untuk rangkaian SR flip-flop tersebut dapat menggunakan IC 7400 yang mana sebagai IC NAND dan IC 7402 sebagai IC NOR.

2. Cara kerja dari rangkaian Latch tersebut dapat digambarkan dalam bentuk table antara output NAND gate-1 yang dihubungkan dengan salah satu input NAND gate-2, dan sebaliknya. Output gate (output latch) diberi nama Q dan Q’. Nor Lacth: Dua buah NOR gate yang saling disilangkan dikenal sebagai NOR gate latch, dengan dua buah output Q dan Q’ yang saling berlawanan serta dua buah input SET dan RESET. Selain itu, pada NAND Latch, jika semua input berlogika 0 maka output memory dan jika semua input 1, maka outputnya tak tentu. Jika pada NOR Latch, jika semua input berlogic 0 maka output akan berlogic tak tentu dan jika semua 1 maka akan berlogic memory.

B RS FLIP FLOP

ada. Dengan penambahan inputan ini, pada rangkaiannya juga dilakukan penambahn yaitu berupa penambahan dua gerbang NAND pada RS flip-flop dari gerbang NAND. Clocked RS Flip-Flop akan berada pada keadaan SET (Q=1) bila pulsa clock berada pada keadaan 1 dan input S juga berada pada keadaan logik 1. Sedangkan keadaan RESET (Q=0) akan terjadi jika pulsa clock berada pada keadaan logik 1 dan input R juga berada pada keadaan logik 1.

2. Perbedaannya yaitu pada Clocked RS Flip-Flop terdapat penambahan inputan

sehingga jumlah inputannya menjadi 3, sedang pada RS Flip-Flop biasa tidak terdapat penambahan sehingga jumlahnya hanya 2 inpuntan.

3. Flip-flop ini dapat dianggap sebagai flip-flop universal, karena flip-flop jenis lain dapat dibuat dari flip-flop JK. Simbol logika terbagi tiga input sinkron (J, K dan CK). Input J dan K merupakan input data, dan input clock memindahkan data dari input ke output. Diperlukan keseluruhan pulsa (bukan sekedar tansisi low ke high atau high ke low saja) untuk memindahkan data dari input ke output. IC yang digunakan dalam JK flip-flop adalah IC 7400.

C D FLIP FLOP

1. Fungsi dari Clock, Clear dan Preset sebagai berikut. Preset berfungsi memberikan nilai set awal. Clear memberikan nilai reset awal, Clock adalah pengaruh aksi Preset dan Clear pada rangkaian tersebut.

2. Merupakan modifikasi dari SR flip-flop dengan tambahan gerbang pembalik pada masukan R sehinga R merupakan komplemen dari masukan S. Pada dasarnya sebuah flip-flopmemiliki dua input, pada FF D input yang dibutuhkan hanyalah 1. Dengan modifikasi tambahan pada FF SR dengan NOT Gate, input D akan mengontrol kondisi set dan reset gate.

D JK FLIP FLOP

1. Sifat dari J-K Flip Flop yaitu Jika kedua data input pada keadaan nol, tidak akan terjadi perubahan pada output meskipun diberikan sinyal clock (output tetap). Jika kedua data input pada keadaan satu, pada tiap pulsa clock data output akan berubah dari sebelumnya (komplemen dari data sebelumnya).

flipflop akan direset hingga diperoleh keluaran Q=0 (kecuali jika flip-flop memang sudah dalam keadaan reset atau Q memang sudah pada keadaan rendah). Pada saat J=1 dan K= 0 atau ketika J berlogika high dan K berlogika low, maka masukan ini akan mengeset flip-flop hingga diperoleh keluaran Q=1 (kecuali jika flip-flop memang sudah dalam keadaan set atau Q sudah dalam keadaan tinggi). Pada saat J dak K kedua-duanya tinggi, maka flip-flop berada dalam keadaan toggle, artinya keluaran Q akan berpindah pada keadaan lawan jika pinggiran pulsa clocknya tiba. Berikut ini merupakan bentuk diagram konstruksi dari JK Flip-Flop dan bagaimana mode toggle bekerja

2. Flip-flop ini dapat dianggap sebagai flip-flop universal, karena flip-flop jenis lain dapat dibuat dari flip-flop JK. Simbol logika terbagi tiga input sinkron (J, K dan CK). Input J dan K merupakan input data, dan input clock memindahkan data dari input ke output. Diperlukan keseluruhan pulsa (bukan sekedar tansisi low ke high atau high ke low saja) untuk memindahkan data dari input ke output. IC yang digunakan dalam JK flip-flop adalah IC 7400

E. T FLIP FLOP

Rangkaian pembagi frekuensi

XXIII. KESIMPULAN

Laporan Praktikum VIII Praktik Teknik Digital Counter Asynchronous

Disusun Oleh : Nama : Imania Diah Rachma Kelas : T. Elektronika B1 NIM : 15507134009

Dosen : Bekti Wulandari, M.Pd

TEKNIK ELEKTRONIKA FAKULTAS TEKNIK

XXIV. TUJUAN PERCOBAAN

Mahasiswa diharapkan dapat mengkaji prinsip kerja dari : 1. Counter Asynchronous modulo-4.

2. Counter Asynchronous modulo-8. 3. Counter Asynchronous modulo-16.

Yang tersusun dari D Flip-flop dan JK Flip-Flop

XXV. DASAR TEORI

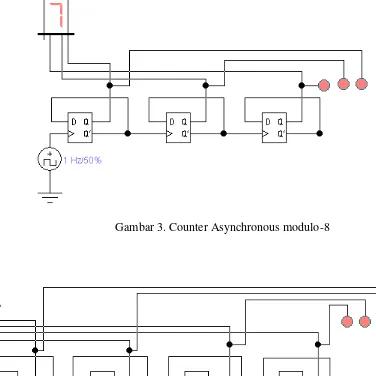

Counter (Pencacah/Penghitung) merupakan rangkaian logika sekuensial yang dibentuk dari flip-flop. Mencacah dapat diartikan menghitung, hampir semua sistem logika menerapkan pencacah. Komputer digit menerapkan pencacah guna mengemudikan urutan dan pelaksanaan langkah-langkah dalam program. Fungsi dasar pencacah adalah untuk “mengingat” berapa banyak pulsa detak yang telah dimasukkan kepada masukkan; sehingga pengertian paling dasar pencacah adalah system memori. Terdapat 2 jenis pencacah (counter), yaitu :

1. Pencacah sinkron (synchronous counters), (yang beroperasi serentak dengan pulsa clock) yang kadang disebut juga pencacah deret (series counters), atau pencacah jajar. 2. Pencacah tak sinkron (asynchronous counters) (yang beroperasi tidak serentak dengan

pulsa clock) atau pencacah kerut (ripple counters).

Pencacah juga memliki karakteristik yang penting, yaitu :

i. Sampai berapa banyak ia dapat mencacah (modulo pencacah); ii. Mencacah maju, ataukan mencacah mundur;

iii. Kerjanya sinkron atau tak sinkron; Beberapa kegunaan pencacah :

a. Menghitung banyaknya detak pulsa dalam satu periode waktu b. Membagi frekuensi

c. Pengurutan alamat

d. Beberapa rangkaian aritmatika

Pencacah Tak sinkron (Asynchronous counters) dinamakan juga serial counter karena output yang dihasilkan masing-masing flip-flop yang digunakan akan berubah kondisi dari 0 ke 1, atau sebaliknya dengan secara berurutan. Hal ini disebabkan karena hanya flip -flop yang paling ujung saja yang dikendalikan oleh sinyal clock, sedangkan clock untuk flip-flop yang lainnya diambil dari masing-masing flip-flop sebelumnya.

membuat table Present state dan Next state, membuat state diagram, serta menurunkan timing diagram.

Perhatikan gambar 1 yang merupakan rangkaian counter Asynchronous modulo-4. Dari hal pertama yang dikemukakan diatas didapatkan persamaan eksitasi :

Q0 (next) = D0 = Q0’ ……….. (1) Q1 (next) = D1 = Q1’ ……….. (2)

Sedangkan table present state dan next state adalah

Present State Next State Q1 Q0 Clock=0 Clock=1

0 0 0 0 0 1

0 1 0 1 1 0

1 0 1 0 1 1

1 1 1 1 0 0

Gambar 2. State diagram table 1

Dengan bantuan logic analyzer didapatkan timing diagram dari counter gambar 1.

Dari gambar 1 di atas dapat dikembangkan untuk counter Asynchronous modulo-8, modulo-16 dan seterusnya. Dengan cara yang relative sama dapat diketahui persamaan eksitasi, table present state dan next state, state diagram, serta timing diagram. Pada gambar 3 ditunjukkan counter Asynchronous modulo-8 dan gambar 4 ditunjukkan counter Asynchronous modulo-16 masing-masing dengan D FF sebagai komponen dasarnya.

Gambar 3. Counter Asynchronous modulo-8

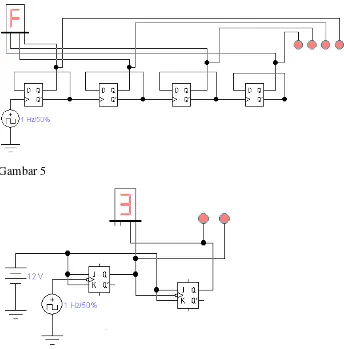

Gambar 5. Counter Asynchronous modulo-4 dari JK FF

XXVI. ALAT DAN BAHAN PERCOBAAN

Software EWB 5.12 dengan spesifikasi kebutuhan: a. D Flip-Flop

b. JK Flip-Flop c. Red Probe d. Clock

e. Seven Segment

XXVII. KESELAMATAN KERJA

1. Perhatikan langkah-langkah pengoperasikan computer. 2. Data segera di save untuk menghindari kecelakaan data. 3. Bila selesai menggunakan, komputer di shut down.

XXVIII. LANGKAH PERCOBAAN

2. Amati dan catat setiap variasi masukan terhadap pola keluaran. Keluaran pada Red Probe dapat saudara tambahh dengan logic analizer untuk mengetahui timing diagram. 3. Ulangi langkah 1 dan 2 untuk uji gambar 3, 4, dan 5. Buat tabel present state dan next state, serta state diagram.

Gambar 3

Gambar 5

XXIX. HASIL PENGAMATAN

Pada Asynchronous counter, output dari Flip-Flop pada bit dengan level yang lebih rendah menjadi input dari Flip-Flop pada bit berlevel lebih tinggi. Dengan kata lain, input clock dari masing-masing Flip-Flop berasal dari output Flip-Flop yang lain.

Percobaan 1. Modulo-4 dengan D FF

Rangkaian dengan logic analyzer

Present State Next State

Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 1

0 1 0 1 1 0

1 0 1 0 1 1

1 1 1 1 0 0

State diagramnya

Catatan :

Dari percobaan ini menggunakan D FF, clock bermula dari nol lalu ketika sampai biner 3, clock akan berulang lagi dari nol lagi dan begitu seterusnya.

Rangkaian dengan logic analyzer

Present State Next State

Q2 Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 0 0 0 1

0 0 1 0 0 1 0 1 0

0 1 0 0 1 0 0 1 1

0 1 1 0 1 1 1 0 0

1 0 0 1 0 0 1 0 1

1 0 1 1 0 1 1 1 0

1 1 0 1 1 0 1 1 1

1 1 1 1 1 1 0 0 0

State Diagram

Catatan :

Dalam percobaan counter asyncronous modulo-8 menggunakan D FF, clock bermula dari nol, lalu ketika telah mencapai biner 7. Maka clock akan berulang kembali menjadi nol dan begitu

Percobaan 3. Modulo-16 dengan D FF

Rangkaian dengan logic analyzer

Present State Next State

Q3 Q2 Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 0 0 0 0 0 0 1

0 0 0 1 0 0 0 1 0 0 1 0

0 0 1 0 0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 1 0 1 0 0

0 1 0 0 0 1 0 0 0 1 0 1

0 1 0 1 0 1 0 1 0 1 1 0

0 1 1 0 0 1 1 0 0 1 1 1

0 1 1 1 0 1 1 1 1 0 0 0

1 0 0 0 1 0 0 0 1 0 0 1

1 0 0 1 1 0 0 1 1 0 1 0

1 0 1 0 1 0 1 0 1 0 1 1

1 0 1 1 1 0 1 1 1 1 0 0

1 1 0 0 1 1 0 0 1 1 0 1

1 1 0 1 1 1 0 1 1 1 1 0

1 1 1 0 1 1 1 0 1 1 1 1

State Diagram

Catatan :

Counter Asynchronous modulo-16 dibuat menggunakan D FF. Clock dalam modulo-16 ini berawal dari nol, lalu akan berjalan hingga biner F dan clock akan kembali ke nol lagi dan begitu seterusnya.

Percobaan 4. Modulo-4 dengan JK FF

Present State Next State

Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 1

0 1 0 1 1 0

1 0 1 0 1 1

1 1 1 1 0 0

State diagramnya

Catatan :

Dari percobaan ini menggunakan JK FF, clock bermula dari nol lalu ketika sampai biner 3, clock akan berulang lagi dari nol lagi dan begitu seterusnya

Percobaan 5. Modulo-8 JK FF

Present State Next State

Percobaan 6. Modulo-16 JK FF

Rangkaian dengan logic analyzer

Present State Next State

Q3 Q2 Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 0 0 0 0 0 0 1

0 0 0 1 0 0 0 1 0 0 1 0

0 0 1 0 0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 1 0 1 0 0

0 1 0 0 0 1 0 0 0 1 0 1

0 1 0 1 0 1 0 1 0 1 1 0

0 1 1 0 0 1 1 0 0 1 1 1

0 1 1 1 0 1 1 1 1 0 0 0

1 0 0 0 1 0 0 0 1 0 0 1

1 0 0 1 1 0 0 1 1 0 1 0

1 0 1 0 1 0 1 0 1 0 1 1

1 1 0 0 1 1 0 0 1 1 0 1

Counter Asynchronous modulo-16 dibuat menggunakan JK FF. Clock dalam modulo-16 ini berawal dari nol, lalu akan berjalan hingga biner F dan clock akan kembali ke nol lagi dan begitu seterusnya.

Percobaan 7. Modulo-4 dengan IC 7474

Present State Next State

Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 1

0 1 0 1 1 0

1 0 1 0 1 1

1 1 1 1 0 0

State diagram

Catatan :

Dari percobaan ini menggunakan D FF, clock bermula dari nol lalu ketika sampai biner 3, clock akan berulang lagi dari nol lagi dan begitu seterusnya

Perco baan 8. Modul o-8 denga n IC 7474

Present State Next State

Q2 Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 0 0 0 1

0 0 1 0 0 1 0 1 0

0 1 0 0 1 0 0 1 1

0 1 1 0 1 1 1 0 0

1 0 0 1 0 0 1 0 1

1 0 1 1 0 1 1 1 0

1 1 0 1 1 0 1 1 1

1 1 1 1 1 1 0 0 0

State diagram

Catatan :

Dalam percobaan counter asyncronous modulo-8 menggunakan D FF, clock bermula dari nol, lalu ketika telah mencapai biner 7. Maka clock akan berulang kembali menjadi nol dan begitu seterusnya

Percobaan 9. Modulo-16 dengan IC 7474

Catatan :

Counter Asynchronous modulo-16 dibuat menggunakan D FF. Clock dalam modulo-16 ini berawal dari nol, lalu akan berjalan hingga biner F dan clock akan kembali ke nol lagi dan begitu seterusnya.

Percobaan 10. Modulo-4 dengan IC 7476

Present State Next State

Q1 Q0 Clock = 0 Clock = 1

0 0 0 0 0 1

0 1 0 1 1 0

1 0 1 0 1 1

1 1 1 1 0 0

State diagram

Catatan :

Dari percobaan ini menggunakan JK FF, clock bermula dari nol lalu ketika sampai biner 3, clock akan berulang lagi dari nol lagi dan begitu seterusnya.