44 Seminar dan Call For Paper Munas Aptikom Politeknik Telkom

Bandung, 9 Oktober 2010

PERANCANGAN DAN REALISASI GENERATOR SINYAL NAVIGASI LORAN C

BERBASIS FPGA DENGAN INTERFACE DAC

Rini Handayani

1, Heroe Wijanto

2, M. Ary Murti

31 Program Studi Teknik Komputer – Politeknik Telkom 2,3Jurusan Teknik Elektro – Institute Teknologi Telkom

1vespa_rini@yahoo.co.id, 2hrw@ittelkom.ac.id, 2mam@ittelkom.ac.id

ABSTRAK

Loran (Long Range Navigation) merupakan sistem radio terestrial yang memanfaatkan sifat perambatan gelombang radio di atas permukaan bumi (ground wave). Sistem navigasi Loran-C bekerja pada rentang frekuensi 80 KHz sampai dengan 100 KHz. Satu sistem Loran, terdiri dari beberapa subsistem berupa sel atau biasa disebut chain. Satu sel Loran, dengan daerah cakupan yang luas, terdiri dari satu stasiun master dan sedikitnya dua stasiun sekunder. Karena memiliki cakupan yang cukup luas, diharapkan teknologi ini cocok untuk kondisi geografis Indonesia yang berkepulauan dan diharapkan dapat mengurangi ketergantungan kepada negara lain, seperti pada GPS (Global Positioning System), sehingga ketahanan nasional dapat ditingkatkan.

Dalam Tugas Akhir ini penulis melakukan perancangan perangkat pemancar Loran-C menggunakan FPGA pada dengan interface DAC. FPGA disini digunakan sebagai pembangkit sinyal sekaligus modulator. Sinyal yang dikeluarkan FPGA masih berupa sinyal digital yang harus dikonversikan ke dalam bentuk sinyal analog hingga sinyal tersebut dapat dipancarkan oleh antenna pemancar.

Kata kunci: Loran-C, chain, GPS, FPGA, modulator, DAC

__________________________________________________________________________________________ PENDAHULUAN

1.1 Latar Belakang

Teknik penentuan posisi yang digunakan pada navigasi di Indonesia saat ini menggunakan satelit GPS (Global Positioning System). GPS dimiliki dan dikelola oleh Departemen Pertahanan Amerika Serikat (U.S Department of Defense), sehingga penggunaannya harus mengikuti standar yang telah ditentukan. Indonesia, yang merupakan negara kepulauan, sangat memerlukan sistem navigasi laut, darat dan udara. Sistem navigasi ini harus handal dan tidak bergantung ke negara lain, sehingga Loran perlu dibuat di Indonesia sebagai sistem pertahanan nasional.

Loran-C (Long Range Navigation-C)

menyediakan cara yang sempurna untuk melengkapi GPS dan sistem satelite lain. Loran merupakan suatu sistem navigasi dengan menggunakan gelombang radio berjangkauan jauh mempunyai daya yang tinggi, operasi system navigasi hiperbolik pada band frekuensi 100 khz dan dapat mengatasi kelemahan dari GPS.

Loran-C paling sedikitnya mempunyai tiga transmitter, satu sebagai stasiun master dan dua

lainnya sebagai secondary. Pada generasi Tugas Akhir mengenai Loran-C sebelum ini, sinyal yang dibangkitkan belum bisa ditransmisikan lewat RF design, karena terbentur oleh konversi format sinyal analog pada sisi transmitter. Dalam transmitter tersebut dibutuhkan pembangkit sinyal dan modulator untuk mengolah sinyal yang akan dipancarkan. Karena modulator yang digunakan, dalam hal ini FPGA, keluarannya masih berupa sinyal digital maka diperlukan modul Digital to

Analog Converter yang dapat mentransmisikan

sinyal Loran-C.

1.2 Tujuan

Tujuan penelitian ini adalah mendesain arsitekture hardware algoritma IFFT dengan bahasa pemrograman VHDL; mensintesis hesil desai VHDL dengan Xilinx Synthesis Tool seri ISE 8.1; mendapatkan hasil sintesis berupa jumlah slice, flip-flop, LUT, FIFO/RAM, GCLK, dan DSP; memprediksi kebutuhan hasil sintesis untuk titik lebih banyak;menghitung delay saat simulasi.

1.3 Perumusan Masalah

Masalah yang akan diteliti dalam penelitian ini adalah :

Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010

45

1. Menentukan spesifikasi dari format sinyal

Loran-C.

2. Generate sinyal input pada sisi transmitter dengan spesifikasi yang ada.

3. Menentukan sample rate terbaik untuk mengubah sinyal digital menjadi sinyal analog. 4. Memodelkan sistem pengolahan sinyal

keluaran modulator menjadi sinyal yang siap pancar.

1.4 Pembatasan Masalah

Batasan-batasan masalah yang digunakan dalam penelitian ini adalah :

1. Asumsi awal masukan berasal dari FPGA berupa clock generator.

2. Tidak membahas masalah Up Converter pada sisi transmitter dan Down Converter pada sisi receiver.

3. Pemodelan kanal untuk propagasi groundwave menggunakan AWGN.

4. Menggunakan multiplexer yang sekaligus berperan sebagai filter.

5. Digunakan level kuantisasi 8 bit.

6. Dalam satu chain hanya digunakan 1 Stasiun Master dan 2 Stasiun Sekunder.

2. DASAR TEORI

2.1 LORAN (Long Range Navigation)

Loran merupakan teknologi navigasi yang menggunakan bantuan gelombang radio untuk menentukan posisi suatu objek di atas permukaan bumi. Loran menggunakan stasiun-stasiun terestrial untuk memancarkan gelombang radio yang nantinya akan membantu penentuan posisi. Loran bekerja pada frekuensi disekitar 100 KHz, dengan frekuensi yang kecil tersebut maka kestabilan propagasi dapat terjaga dikarenakan loss propagasi yang tidak terlalu besar. Loran–C menggunakan prinsip propagasi groundwave untuk perambatan gelombang navigasinya.

Secara umum sistem Loran-C terdiri dari beberapa stasiun transmit. 1 buah stasiun master dan minimal 2 buah stasiun sekunder. Masing – masing stasiun terpisah ratusan mil, dan konstelasi beberapa stasiun tadi di sebut chain. Stasiun Loran pada umumnya hanya memancarkan grup pulsa secara singkat dan tidak kontinu, melainkan dengan selang waktu tertentu yang disebut GRI, hal ini digunakan untuk melakukan penghematan daya mengingat daya pancar stasiun yang tinggi.

2.2 Ground Wave

Ground wave atau surface wave merupakan gelombang yang berpropagasi mengikuti bentuk

permukaan bumi, yang dibatasi oleh dua lapisan yaitu permukaan bumi (startosfer) dan ionosfer.

Gambar 2.1 Propagasi Ground Wave

Ground wave berpolarisasi secara vertikal, karena setiap komponen medan listrik horisontal yang bersinggungan dengan permukaan bumi akan dihubung singkat. Ground wave akan menginduksi muatan pada permukaan bumi sehingga terjadi arus bolak balik yang kemudian akan menginduksi medan elektromagnetik, demikian seterusnya, sehingga merambat bersama dengan arus. Arus listrik yang terjadi akan mengalami redaman karena bumi bersifat kapasitif dengan rugi tertentu yang ditentukan oleh konduktivitas, permitivitas dan frekuensi kerja gelombang yang digunakan.

2.3 Stasiun Pemancar

Stasiun master merupakan stasiun utama dari sel Loran. Stasiun master berfungsi sebagai stasiun pertama yang memancarkan pulsa, lalu diikuti oleh stasiun sekunder yang lain setelah delay waktu tertentu. Untuk servis navigasi, stasiun master memancarkan grup pulsa yang terdiri dari sembilan pulsa. Tiap grup pulsa ini dipancarkan dengan selang waktu waktu tertentu yang disebut GRI (Group Repetition Interval).

Harga GRI harus cukup besar agar tidak terjadi

overlaping pulsa antara stasiun yang satu dengan

stasiun yang lain dalam satu sel Loran. Pada jaringan Loran yang sudah ada, nilai GRI berkisar antara 40.000 – 100.000 us. Stasiun master juga memancarkan grup pulsa timing dan paging. Stasiun master memiliki daya pancar yang paling besar dibanding stasiun yang lain, karena sinyal stasiun master harus mencakup baik stasiun sekunder dan pesawat penerima pada daerah cakupan satu sel Loran.

Gambar 2.2 Group Repetition Interval

Stasiun master pada LORAN terdiri dari 3 blok servis, yaitu navigasi, timing, dan paging. Blok navigasi bertugas untuk menghasilkan grup pulsa

46 Seminar dan Call For Paper Munas Aptikom Politeknik Telkom

Bandung, 9 Oktober 2010

yang kontinu, dengan format tertentu dan dengan selang waktu tertentu yang disebut GRI. Blok navigasi tidak memiliki input, ketika stasiun master aktif, blok ini secara kontinu mengeluarkan output berupa grup pulsa yang terdiri dari 9 pulsa, menuju tingkat RF .

2.2.1Karateristik Pulsa Stasiun Master dan Sekunder

Blok Navigation Pulse Generator dirancang sedemikian rupa, sehingga mengeluarkan 9 pulsa dengan format tertentu dengan selang waktu GRI. Tiap pulsa Loran memiliki perioda 200 us. Selang waktu antar pulsa dalam satu grup adalah 1000 us, kecuali untuk pulsa ke-9 pada grup master memiliki jarak 2000 us.

Gambar 2.2 grup pulsa stasiun master Loran

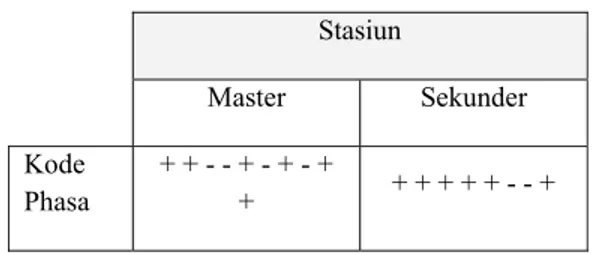

Grup pulsa Loran juga memiliki Phase Coding, yaitu pola perubahan fasa pada pulsa – pulsa Loran. Kode phasa ini berguna untuk meredam efek interferensi sky wave dan membantu membedakan grup pulsa stasiun master dengan stasiun sekunder. Pola perubahan fasa pulsa – pulsa Loran tertera pada gambar di bawah, dimana tanda positif berarti pulsa tidak mengalami perubahan fasa dan tanda negatif berarti pulsa mengalami perubahan fasa 1800.

Tabel 2.1 Phase Coding

Stasiun Master Sekunder Kode Phasa + + - - + - + - + + + + + + + - - + 2.2.2 Karateristik Sinyal

Untuk membentuk yang sesuai dengan format sinyal LORAN, ketepatan envelope sinyal mutlak diperlukan. Persamaan yang digunakan untuk membentuk envelope standar sinyal LORAN adalah:

p p t t t t A t E exp21 2 Dimana : t = waktu ( s tp = 65 sKemudian envelope E(t) dimodulasi dengan frekuensi carrier 100 Khz :

)

2

sin(

)

(

)

(

0 0t

E

t

f

t

Dimana,:0 (t) = Sinyal Modulasi; E(t) = Sinyal

Envelope

f0 = Frekuensi Modulasi

Dari persamaan diatas dihasilkan sinyal LORAN seperti dibawah ini :

Gambar 2.3 Sinyal Hasil Modulasi

2.3 Modulasi ASK

Modulasi ASK (Amplitudo Shift Keying) dapat dipandang sebagai modulasi amplituda dengan pemodulasi sinyal data biner (bit “0” atau bit “1”) seperti halnya pada modulasi AM. Jadi sinyal ASK merepresentasikan sinyal data biner “0” dan “1” dengan level amplituda yang berbeda.

Salah satu pembentukan sinyal ASK, yaitu dengan modulator AM-DSB-SC. Dengan modulator AM Doble Side Band Supressed

Carrier dihasilkan sinyal ASK dengan harga m

= 1 (dikenal sebagai modulasi On-Off Keying / OOK)

Gambar 2.4 Modulator ASK

Persamaan sinyal ASK secara umum adalah :

mb

t

f

t

A

t

s

(

)

ASK

1

(

)

sin

2

cdimana, A = amplit A V 2

1 ) (t b Diguna dilakukan sinyal anta yang sink transmiter, sinkron. B dengan det Dalam ASK deng sinyal deng St t Sm s 2 ) ( ) ( ' dilewatkan sin 2 ) ( ) ( 't St S berisi S(t) s didapatkan diteruskan penentuan biner bit “ kepada mengemba 2.4 VHDL VHDL High Sp Description Amerika pengemban dengan terintegrasi telah menj perancanga 2.4.1 Mtudo sinyal carr

1 ; 0 ; 1bitbit akan teknik d dengan mengg ara sinyal ASK kron terhadap atau disebu Blok diagram ektor sinkron s ~ S(t) S’c(t) Pemb Sm’ Gambar 2.5 D m detektor sinkr gan lokal osi gan persamaan S t sin2 2 ) ( sin n filter LPF ag n merupakan sinyal informa n selubung sin ke Voltag level sinyal, a 1” atau bit “0 level refer alikan pola data

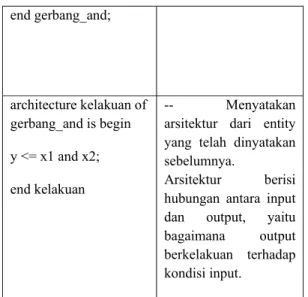

L L adalah singk eed Integrat n Language. Serikat da ngan bahasa tujuan men i berkecepatan jadi salah sat an sistem digita Memodelkan Si Seminar rier; m = index demodulasi co gunakan prins K dengan pem p sinyal pem ut juga deng penerimaan sebagai berikut = sin (2 πfct+φ) awa Lokal LPF (t) S’(t) Voltage Comparator Detektor Sinkro ron perkalian ilator akan m : t fc) 2 ( gar referensi 2 n baseband re si dengan Φ = nyal informas ge comparat apakah sebaga 0” dengan mem rensi terten a kebentuk siny katan dari VH ted Circuit) Departemen an IEEE pemodelan h ngembangkan tinggi. Kini ba tu standar ind al. istem Digital dan Call For x modulasi = herent yaitu sip perkalian mbawa lokal mbawa dari gan detektor sinyal ASK t : on antara sinyal menghasilkan kemudian 2fc diredam. covery yang 180. Setelah si kemudian tor dengan ai sinyal data mbandingkan ntu, untuk yal digital. HSIC (Very Hardware Pertahanan mensponsori hardware ini rangkaian ahasa VHDL dustri dalam Paper Munas Politekn Se beberap yang te Gam Tingka tingkat dimode sistem mengg hubung 2.4.2St Ba gerbang Gerban port-po pada G Gamb Perhati gerban library use ieee.s use ieee.s entity port ( x1 : in x2 : in y : ou ); s Aptikom ik Telkom ebuah sistem d pa tingkat pem erlihat pada Gb mbar 2.6 Tingka Structu at pemodelan t behavioral. P elkan dengan itu bertinda ambarkan gan antar komp

truktur Dasar

ayangkan kita g AND dengan ng AND yang ort input dan o Gb.2.7 bar 2.7 Gerban ikan file VHDL ng_and.vhd: y ieee; td_logic_1164 td_logic_arith. y gerbang_and n std_logic; n std_logic; ut std_logic digital dapat di modelan (abst b.2.6 atan pemodela ral, dan Physic

yang paling ada tingkatan cara menulis ak (behaves), komponen-ko ponen. r VHDL a ingin mem n menggunakan akan kita mo output seperti y ng AND beserta outputnya L di bawah ini, 4.all; .all; -- referen digunak is -- Men yang gerban daftar outputn modelkan dala traction), sepe n: Behavioral, cal g tinggi adal ini, suatu siste skan bagaima bukan deng omponen d modelkan sebu n bahasa VHD odelkan memil yang ditunjukk a port input da

, file ini bernam Menyataka nsi yan kan nyatakan enti bernam g_and da port input da nya. 47 am erti lah em ana gan dan uah DL. iki kan an ma an ng ity ma an an

48 Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010 end gerbang_and; architecture kelakuan of gerbang_and is begin y <= x1 and x2; end kelakuan -- Menyatakan arsitektur dari entity yang telah dinyatakan sebelumnya.

Arsitektur berisi hubungan antara input dan output, yaitu bagaimana output berkelakuan terhadap kondisi input.

Gerbang AND kita tadi memiliki tabel kebenaran berikut ini:

Tabel 2.2 Tabel kebenaran gerbang AND

X1 X2 Y

0 0 0

1 0 0

0 1 0

1 1 1

Lalu perhatikanlah hasil simulasi gerbang AND kita itu berikut ini:

Gambar 2.8 Hasil simulasi gerbang_and.vhd yang sesuai dengan Tabel

2.5 FPGA

FPGA merupakan salah satu piranti yang termasuk dalam kelompok programable logic

device. FPGAs berbeda dari general-purpose

mikroprosesor (misalnya Intel) dalam hal fleksibilitas logic-nya. Mikroprosesor mempunyai hardware yang tetap. Assembly programmer memprogram suatu komputasi dengan keterbatasan pada tetapnya banyaknya register, siklus

fetch-decode-execute, serta fungsi-fungsi ALU

(arithmetic and logic unit) dan pada banyaknya bit

suatu register. FPGAs berbeda dari mikrokontroler, karena mikrokontroler pada prinsipnya adalah mikroprosesor yang diprogram dengan bahasa assembly dan dirancang sebagai pengendali bukan untuk komputasi. Mikroprosesor dan mikrokontroler mengimplementasikan suatu komputasi pada hardware yang tetap. Hardware pada FPGA diserahkan sepenuhnya pada desain

engineer untuk memprogramnya. Sebelum

diprogram, FPGA hanyalah tersusun atas blok-blok yang belum dikonfigurasikan dan interkoneksi yang belum disusun dan difungsikan. Chip FPGAs yang sama dikonfigurasikan dengan data yang berbeda akan mengimplementasikan hardware yang berbeda.

Spesifikasi FPGA yang digunakan pada Tugas Akhir ini, secara umum sebagai berikut :

· Xilinx XC4VLX25-10SF363 FPGA · 64MB of DDR SDRAM

· 10/100 Ethernet PHY

· On-board 100MHz LVTTL Oscillator · On-board LVTTL Oscillator Socket (4/8-Pin

Oscillators) · P160 Connectors · LCD Panel

· 16Mb Serial Flash for FPGA configuration · PC4 JTAG Programming/Configuration Port · SystemACE™ Module Connector

· RS232 Port · User LEDs

· Four User Push Button Switches, an 8-position DIP Switch

G 2.6 TDM Time D proses pen yang hany masing-ma tertentu. Sejum multiplexer yang berag multiplexer switch rota yang sebe berubah-ub ini merupa Modulation sinyal infor Setelah ditransmisi informasi Kanal tran disinkronis untuk mem membagi s Ketika demultiplex tingi (sinya sinyal info Kemudian mengarahk masing dar Gambar 2.9 FP (Time Divisio Division Multi ntransmisian b ya melalui satu asing sinyal di

lah sinyal info r memiliki bi gam. Ketika r, maka siny ary yang meny elumnya telah

bah tiap waktu akan gelomban n) yang menga rmasi yang per h melalui mu ikan dengan

bedasarkan ho nsmisi ini mer sasikan. Kanal mbangun tiap k ample-sample a sinyal xer, gabungan al transmisi) di ormasi awal akan ada rotar kan sinyal-sin ri sinyal itu. Seminar FPGA XC4VLX n Multiplexin iplexing merup beberapa sinya u kanal transm transmisikan p ormasi yang ak it rate dan su sinyal tersebu yal akan mel yebabkan siny disampling u. Hasil output ng PAM (Puls andung sample riodik terhadap ultiplex, sinya membagi-ba old time / ju rupakan kanal l sinkron ini kelompok dari tepat ke dalam transmisi n sinyal yang ibagi-bagi kem yang berbit r ry switch pula nyal ke tuju dan Call For X25 ng) pakan sebuah al informasi misi dengan pada periode kan masuk ke umber sinyal ut memasuki lalui sebuah yal informasi akan dibuat t dari switch e Amplitude e-sample dari p waktu. al kemudian agi sample umlah kanal. l yang telah dibutuhkan i sample dan m framenya. memasuki ber bit rate mbali menjadi rate rendah. disana yang uan masing-Paper Munas Politekn 2.7 Di Ka berupa melalui menjad adalah mengko 2.7.1 Re Numbe bit dar merepr 2.7.2 Fre ukuran berfung Berdas sinyal h kali fre 2.7.3 Se keluara dengan convert (Differe 1 LSB. 2.7.4 Un interva keluara yang b dipeng DAC d 2.7.5 TH merupa sinyal s Aptikom ik Telkom Gambar 2 igital to Analo arena keluaran sinyal digita i RF maka di sinyal analog suatu mod onversinya. Resolusi esolusi yang er of Bits (ENO ri sebuah DAC roduksi sinyal a Frekuensi S ekuensi sampl n kecepatan m gsi dan meng

arkan teori harus disampel ekuensi dari sin

Monotonici ebuah DAC an analognya n peningkatan ter dijamin ential of Non-L . Settling Tim ntuk sebuah D al antara sebua annya untuk biasanya diuku aruhi oleh sle dalam menguba THD+N HD+N (Total H akan ukuran di yang dihasilk 2.10 Sistem Tra og Converter n dari modu al, untuk men sinyal tersebu g. Digital to A dul yang di dimaksud a OB), dalam ha C yang memu analog. Sampling Mak ling maksimum maksimum dim ghasilkan nila sampling S

l lebih dari ata nyal yang diing

ty dikatakan m selalu menin code-input DA monotonic ji Linearity) tidak me DAC, settling ah perintah m menghasilkan ur dalam perse ew rate, kecep ah keluarannya Harmonic Dis

istorsi dan nois kan DAC, yan

ansmitter TDM ulasi ASK/OO ntransmisikann ut perlu diub Analog Convert igunakan unt adalah Effecti al ini adalah ni ungkinkan unt ksimum m adalah sebu mana DAC ak ai yang akur Shannon-Nyqui au sama dengan ginkan. monotonic ji ngkat sebandi AC. Dan sebu ika error DN k lebih besar d

time merupak meng-update ni nilai akhirny en. Settling tim patan maksimu a, dari amplifie tortion + Nois se yang ada pa ng diekspresik 49 M OK nya bah ter tuk ive lai tuk uah kan rat. ist, n 2 ika ng uah NL ari kan lai ya, me um er. se) ada kan

50 Seminar dan Call For Paper Munas Aptikom Politeknik Telkom

Bandung, 9 Oktober 2010

dalam persentasi dari total daya dari sinyal distorsi harmonic yang tidak diinginkan dan noise yang ada pada sinyal keluaran .

2.7.6 Dynamic Range

Dynamic range adalah selisih antara sinyal terbesar dan sinyal terkecil dari yang bisa dihasilkan DAC dan diekspresikan dalam decibel (dB). Dynamic range juga berhubungan denga resolusi dan noise floor.

3. PERANCANGAN DAN IMPLEMENTASI SISTEM

3.1 Gambaran Umum Sistem Operasi Loran C

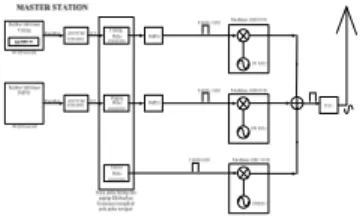

Gambar 3.1 Sistem Operasi Minimum Loran C

Secara umum, perancangan sistem navigasi Loran C digambarkan seperti konfigurasi diatas. Stasiun master memancarkan sinyal informasi ke semua stasiun sekunder dan user. Dan oleh stasiun sekunder sinyal informasi tersebut dipancarkan ke arah user. User akan menerima sinyal informasi tersebut dari stasiun master dan stasiun sekunder dengan waktu yang berbeda-beda. Dengan begitu didapatkan nilai-nilai yang dapat menentukan Time Different Loran C.

Sistem yang akan dirancang pada Tugas Akhir ini akan direalisasikan dengan menggunakan digital signal processing chip berupa FPGA (Field Programmable Gate Array), yang sudah terintegrasi pada Development Board FPGA Xilinx Virtex4 XC4VLX25 dan Conversion Block Digital to Analog using DAC 0832 National Semiconductor.

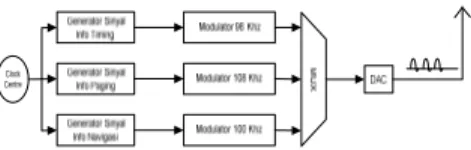

3.2 Gambaran Umum Blok Stasiun Master Loran C

Gambar 3.2 Perancangan Stasiun Master

Sinyal informasi pada stasiun master terdiri dari informasi timing, paging dan navigasi itu sendiri. Garis besar alur kerja pada stasiun master dijabarkan sebagai berikut:

Pembangkitan data informasi pada stasiun master meliputi pulsa navigasi, timing dan

paging.

Pulsa timing dan paging dikirim dalam format bit-bit ASCII dalam bentuk sinyal Loran C dengan frekuensi 98 KHz untuk pulsa timing dan 108 KHz untuk pulsa paging. Sedangkan untuk navigasinya dikirim berdasarkan format yang telah ditentukan dengan frekuensi 100 KHz. Ketiga sinyal informasi ini dikirim dengan rentang waktu yang telah ditentukan sehingga tidak terjadi collision satu sama lain. Jika tidak bisa dihindari maka sistem akan menentukan prioritas pulsa yang dipancarkan. Pulsa-pulsa yang sudah di-generate akan

dimodulasi oleh sinyal carrier dengan frekuensi carrier yang berbeda-beda, sesuai dengan yang telah ditentukan sebelumnya. Pulsa-pulsa digital yang telah dimodulasikan

tadi akan di-multiplexing, sehingga informasi dapat dikirim melalui satu kanal transmisi. Sinyal digital yang keluar dari multiplexer

dikonversi ke dalam bentuk sinyal analog pada blok DAC, sehingga sinyal informasi yang dikirimkan tadi dapat dipancarkan oleh blok RF ke stasiun-stasiun sekunder dan user.

3.3 Blok Kerja Stasiun Master

Blok kerja pada stasiun master yang akan dibuat dalam Tugas Akhir Perancangan dan Realisasi Generator Sinyal Navigasi Loran C berbasis FPGA dengan Interface DAC ini digambarkan dalam garis putus-putus dibawah ini,

Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010

51 Gambar 3.3 Blok Kerja di Stasiun Master

3.3.1 Clock Centre

Clock centre adalah bagian yang terpenting dari sistem ini. Clock centre merupakan sumber clock yang dihasilkan Development Board FPGA XC4VLX25 sebesar 100 MHz.

Gambar 3.3 Perancangan Blok Penghasil Clock 10 MHz

Untuk membangkitkan clock sebesar 10 MHz diperlukan adanya counter. Gunanya counter disini adalah mencacah setiap kali clock dalam kondisi transisi naik. Sehingga diketahui besarnya counter yang dibutuhkan untuk membangkitkan clock 10 MHz adalah sebesar 100 counter.

Dengan begitu, pengimplementasian rangkaian menjadi lebih mudah dan cukup presisi untuk membangkitkan frekuensi sinyal carrier mengingat frekuensi kerja Loran C berada di sekitar 90 KHz sampai dengan 110 KHz.

3.3.2 Pulse Generator

Untuk menghasilkan deret-deret pulsa navigasi yang akan dikirim pada 1 (satu) GRI dibentuklah pulse generaotor. Pada blok ini, deret pulsa dibangkitkan sesuai ketentuan kode fasa yang telah ditetapkan sebelumnya pada Bab II.

Gambar 3.4 Blok Penghasil Deret Pulsa

Clock pada blok ini merupakan clock yang berasal dari keluaran blok clock centre yaitu sebesar 10 MHz. Alur kerja pada blok ini dirinci sebagai berikut,

Untuk mengaktifkan blok ini maka masukan pada pin rst diberi logika ‘0’.

Counter yang terdapat pada blok ini berfungsi sebagai pencacah waktu, sehingga deret-deret

pulsa yang keluar sesuai dengan aturan yang ada yaitu, lebar tiap pulsa Loran C sebesar 300 us, lebar jarak antar pulsa berikutnya 700 us. Deret yang merupakan keluaran dari blok ini

mengeluarkan logika deret-deret pulsa selama satu GRI. Dan dibangkitkan setiap periodenya. GRI yang dibangkitkan pada blok ini disesuaikan dengan jarak coverage antenna pada sisi transmit. Sehingga perancangan pada sistem ini dapat diimplementasikan.

3.3.3 Envelope Generator

Pada envelope generator sinyal yang dibangkitkan adalah gelombang Loran C sesuai dengan persamaan 2.1.

Gambar 3.4 Perancangan Blok Envelope Generator

Alur kerja blok envelope generator adalah sebagai berikut:

Sinyal clock yang digunakan pada blok ini berasal dari keluaran blok clock centre yang mempunyai periode 100 ns. Dan keluaran pada blok envelope generator akan dimodulasikan dengan sinyal carrier periode sebesar 10 us. Sehingga banyaknya counter yang dibutuhkan untuk membangkitkan setiap sample adalah 100.

Satu pulsa yang akan ditransmisikan pada stasiun master merupakan dalam bentuk satu sinyal Loran C. Untuk pulsa positif (+) direpresentasikan dengan logika ‘01’, pulsa negatif (-) direpresentasikan dengan logika ‘11’ dan untuk delay direpreaentasikan dengan logika ‘00’.

Satu gelombang dari Loran C ini memiliki periode 300 us. Sehingga dibutuhkan 30 sinyal carrier untuk memodulasikan satu gelombang Loran C. Dengan begitu untuk membangkitkan satu gelombang Loran C untuk setiap periodenya diperlukan 30 sample dan 3000 counter clock.

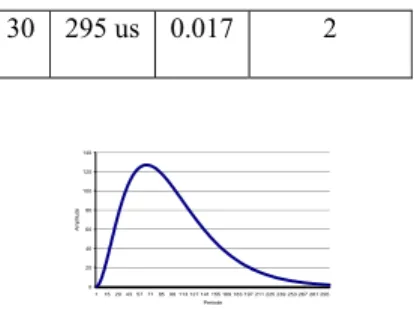

Dengan mengacu pada persamaan 2.1, maka didapat nilai tiap-tiap samplenya sebagai berikut,

Tabel 3.1 Sample Gelombang Loran C untuk Pulsa Positif

n t E(t) E(t) x 127

52 Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010 2 15 us 0.248 32 3 25 us 0.506 64 4 35 us 0.729 93 5 45 us 0.887 113 6 55 us 0.974 124 7 65 us 1 127 8 75 us 0.979 124 9 85 us 0.924 117 10 95 us 0.849 108 11 105 us 0.762 97 12 115 us 0.672 95 13 125 us 0.584 74 14 135 us 0.5 64 15 145 us 0.424 54 16 155 us 0.356 45 17 165 us 0.297 38 18 175 us 0.246 31 19 185 us 0.202 26 20 195 us 0.165 21 21 205 us 0.134 17 22 215 us 0.108 14 23 225 us 0.087 11 24 235 us 0.07 9 25 245 us 0.056 7 26 255 us 0.044 6 27 265 us 0.035 5 28 275 us 0.028 4 29 285 us 0.022 3 30 295 us 0.017 2

Gambar 3.5 Gelombang Loran C yang diharapkan

Pada satu grup pulsa terdiri dari pulsa-pulsa positif dan negatif, sehingga gelombang ini memiliki nilai amplitude peak-to-peak. Bentuk Resolusi yang digunakan untuk realisasi ke sinyal analog adalah 8 bit. Oleh karena itu hasil dari perhitungan pada persamaan 2.1 dikalikan 127, sehingga besar amplitude peak-to-peak adalah senilai 256.

3.3.4 Sine Generator

Fungsi dari sine generator ini adalah sebagai pembangkit sinyal carrier yang nantinya akan digunakan sebagai multiplier pada modulator. Sinyal carrier yang dihasilkan harus sesuai dengan frekuensi kerja sinyal navigasi Loran C yaitu 100 KHz.

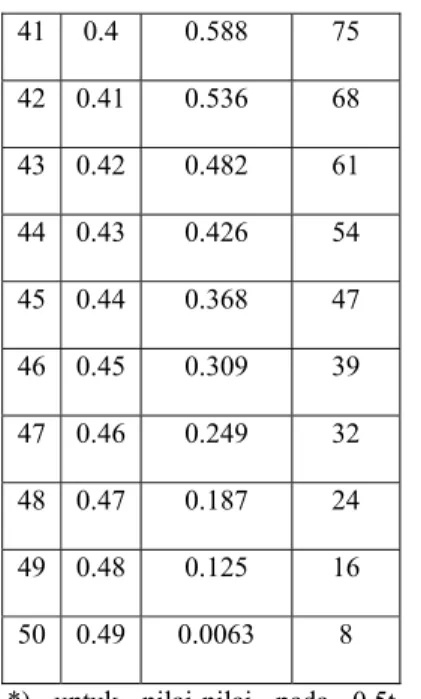

Tabel 3.2 Sample Gelombang Sinusoidal

n t sin (2π.t) x 127 1 0 0 0 2 0.01 0.0063 8 3 0.02 0.125 16 4 0.03 0.187 24 5 0.04 0.249 32 6 0.05 0.309 39 7 0.06 0.368 47 8 0.07 0.426 54 9 0.08 0.482 61 10 0.09 0.536 68 11 0.1 0.588 75 0 20 40 60 80 100 120 140 115294357718599 113 127 141 155 169 183 197 211 225 239 253 267 281 295 Periode Am plitu d e

Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010 53 12 0.11 0.637 81 13 0.12 0.685 87 14 0.13 0.729 93 15 0.14 0.77 98 16 0.15 0.809 103 17 0.16 0.844 107 18 0.17 0.876 111 19 0.18 0.905 115 20 0.19 0.929 118 21 0.2 0.951 121 22 0.21 0.968 123 23 0.22 0.982 125 24 0.23 0.992 126 25 0.24 0.998 127 26 0.25 1 127 27 0.26 0.998 127 28 0.27 0.992 126 29 0.28 0.982 125 30 0.29 0.968 123 31 0.3 0.951 121 32 0.31 0.929 118 33 0.32 0.905 115 34 0.33 0.876 111 35 0.34 0.844 107 36 0.35 0.809 103 37 0.36 0.77 98 38 0.37 0.729 93 39 0.38 0.685 87 40 0.39 0.637 81 41 0.4 0.588 75 42 0.41 0.536 68 43 0.42 0.482 61 44 0.43 0.426 54 45 0.44 0.368 47 46 0.45 0.309 39 47 0.46 0.249 32 48 0.47 0.187 24 49 0.48 0.125 16 50 0.49 0.0063 8

*) untuk nilai-nilai pada 0.5t s.d 1t merupakan pengulangan negatif dari nilai-nilai tersebut diatas. Nilai-nilai-nilai yang sudah dikalikan merupakan hasil pembulatan terdekat. Sama halnya dengan blok envelope generator, hasil perhitungan dari persamaan sinusoidal dikalikan 127.

Pada blok sine generator ini, sumber clock berasal dari blok clock centre yang besarnya 10 MHz. Untuk menghasilkan gelombang sinusoidal 100 KHz, maka gelombang tersebut mengalami penyamplingan sebanyak 100 kali untuk setiap periodenya. Adapun sampling yang diambil pada pembentukan gelombang sinusodal ini tertera pada tabel berikut.

Gambar 3.6 (kiri)Perancangan Blok Pembangkit Sinyal Sinus 100 KHz

(kanan) Gelombang Sinus yang Dihasilkan pada Fasa Positif

Karena pulsa-pulsa (grup pulsa) yang dibangkitkan pada sistem Loran C dibedakan bedasarkan fasanya, dengan pola perubahan dimana tanda positif berarti pulsa tidak mengalami

54 perubahan mengalami ini dibutuh fasa positi negatif inp antar pulsa Gamb Denga yang digam generator b Clock sebesa disamp Sinyal terdete atau ‘1 Jika in yang d 3.3.5 M Untuk adalah sal transmisi. akan diben Akhir ini. Gamba Masuk dibangkitka ,yang diba selubung, generator.

fasa dan tan i perubahan fa hkan dua bit i f input deret put deret beru

diberi logika ‘ bar 3.7 (atas) G 1 G (bawah) Besa an mengikuti k mbarkan pada bekerja dengan yang digunak ar 10 MHz. Art pling sebanyak sinus ini eksi ada input 11’ selama 300 nput bernilai ‘0 dihasilkan akan

Modulator Bloc

memancarkan lah satu bagi

Oleh karena ntuk dalam tah

ar 3.8 Keluara dihar

kan dari blok an dari blok angkitkan p yang diban Setelah sinyal Sem Polit nda negatif b asa 1800, maka input berupa d berupa logik upa logika ‘11 ‘00’.

Grup Pulsa Lor GRI

ar Jarak Antar

ketentuan-keten a gambar 3.5 n cara berikut,

kan pada blok tinya sinyal sin k 100 kali. akan dibang pulsa dengan 0 us 00’, maka nilai n bernilai ‘0’ (n ck n suatu sinya ian yang pen itu, blok mo hap transmisi an Blok Modula rapkan k ini adalah Pulse Gener pada sine gen ngkitkan pad Loran C dan s inar dan Call teknik Telkom berarti pulsa a dalam blok deret. Untuk ka ‘01’, fasa 1’ dan delay ran C dalam Pulsa ntuan seperti maka sine k ini adalah nus 100 KHz gkitkan jika n logika ‘01’ i sinyal sinus nol). al, modulasi nting dalam dulator juga pada Tugas asi yang pulsa, yang rator, carrier nerator, dan a envelope sinyal carrier For Paper M m dibangk dimodu G Al Pu ak den ‘01 de Ni ge Ya DS per den Se ma dik dib Ha me Ka dig per ha dih yan 3.3.6 Sin master sinyal tersedia hanya multipl G Bl division dipanca digital. unas Aptikom kitkan, maka ulasikan denga Gambar 3.9 Per

lur kerja pada b ulsa yang diba an memberi n ngan ketentuan 1’, pulsa nega

lay dengan log ilai pulsa ters lombang Loran ang digunakan SB SC. Seh rkalian magn ngan sinyal Lo etelah terbentu aka setiap sa kalikan denga bangkitkan pad asil dari enghasilkan p arena pada im gunakan adal rkalian tersebu silnya sekaran hasilkan adala ng akan ditran Multiplexer nyal yang di tidak hanya timing dan p a untuk ditran ada satu. Oleh leksing pada bl Gambar 3.10 P ok multipleks n karena arkan tersebu m a sinyal Lor an sinyal carrier rancangan Blo

blok ini adalah angkitkan dari nilai pada ma n pulsa positif atif (-) diberi gika ‘00’. sebut menent n C yang akan n adalah jenis hingga yang nitude antara oran C. uknya gelomb ampling gelo an sinyal car da blok sine ge perkalian panjang bit s mplementasiny ah 8 bit m ut dibagi deng ng panjang bit ah 8 bit. Hasi smitkan ke blo r Block ikirimkan pad sinyal navig aging. Sedang nsmisikan me h karena itu di lok stasiun ma Perancangan B

ser ini beker sinyal-sinyal ut merupaka ran C terseb rnya. ok Modulasi h sebagai beriku pulse generat asukan blok i (+) diberi logi logika ‘11’ d tukan nilai d dibangkitkan. s modulasi A terjadi adal sinyal carri bang Loran mbang terseb rrier yang tel enerator. tersebut ak sebesar 16 b a resolusi ya maka hasil d an 256 sehing maksimum ya il terakhir inil ok multiplexer. da blok stasi gasi, tetapi ju gkan kanal ya lalui RF desi ibutuhkan pros ster. lok Multiplexe

rja secara tim yang ak an sinyal-siny but ut, tor ini ika dan ari AM lah ier C, but lah kan bit. ang ari gga ang lah un uga ang gn ses er me kan yal

Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010

55

3.3.7 Converter Block

Proses pengubahan sinyal dari sinyal digital ke sinyal analog dibutuhkan blok konversi. Pada blok konversi ini komponen DAC yang digunakan adalah DAC 0832 dari National. Mengenai karakteristik DAC 0832 terlampir pada lampiran buku ini.

Gambar 3.11 Perancangan Blok Konversi

Bit-bit pulsa yang keluar dari FPGA memiliki beda potensial 1 Volt sampai dengan 1.2 Volt. Supaya bit-bit tersebut dapat diproses pada blok konversi, yang memiliki karateristik masukan 5 Volt sampai dengan 15 Volt, maka data tersebut harus melewati interface optocoupler. Hal ini dilakukan untuk menghindari lonjakan arus yang terlalu besar dari blok konversi.

Interface yang digunakan pada Tugas Akhir ini ada delapan optocoupler. Masing-masing pin masukan terhubung dengan pin-pin keluaran data pada FPGA. Keluaran dari blok optocoupler inilah yang akan diolah blok DAC hingga menghasilkan sinyal-sinyal analog yang kemudian akan siap diolah pada RF design.

3.4 Pengujian Subsistem Loran C

Pengujian subsistem penerima Loran pada tahap implementasi dilakukan dengan cara menanamkan program dari blok subsistem pemancar Loran yang akan diuji pada FPGA. Hasil keluaran dari blok subsistem yang diuji dapat dilihat pada PC dengan menggunakan interface antara FPGA dan PC berupa Logic Analyzer 2124 A.

Gambar 3.13 Konfigurasi Pengujian Subsistem pemancar Loran C

3.5 Pengujian Sistem Pemancar Loran C

Pengujian sistem penerima Loran pada tahap implementasi dilakukan dengan cara menanamkan program dari blok sistem pemancar Loran dalam satu FPGA. Hasil keluaran dari blok sistem yang diuji dapat dilihat pada PC dengan menggunakan

interface antara FPGA dan PC berupa Logic

Analyzer 2124 A.

Gambar 3.13 Konfigurasi Pengujian Sistem Pemancar Loran-C

3.6 Pengujian Sistem Loran C

Pengujian sistem Loran-C dilakukan dengan cara me-load program ke blok sistem penerima dan pemancar Loran dengan FPGA yang sama.

Hasil keluaran dari sistem Loran-C dapat dilihat pada sisi penerima pada LCD yang terdapat pada Development Board FPGA Xilinx Virtex4

XC4VLX25 FPGA Sistem Pemancar Loran Subistem Penerima Loran Masukan dari Pin FPGA Keluaran pada LCD

Gambar 3.14 Konfigurasi Pengujian Sistem Loran-C

3.7 Interkoneksi dengan Blok RF Design

Agar bisa diuji dengan kondisi sebenarnya, atau test lapangan. Maka dibutuhkan blok tambahan yaitu blok RF, yang terdiri dari DAC, power amplifier dan antena. Spesifikasi teknik yang bisa di gunakan untuk blok RF adalah :

Tabel 3.3 Spesifikasi Blok RF

1 DAC Spesifikasi

Resulosi(bit) 8

56 DA Ti Ou 2 Pe -3d -in ou 3 An (P 4. IMPL SISTE Implem menggunak yang kemu sehingga d digunakan gerbang-ge jumlah ters Xilinx Virte 4.1 Pengu Penguk blok dari su dari, AC Settling ime utput FSR enguat 2,5 wat -. Power Outpu -. Bandwidth – dB -. Efisensi -. Impedansi nput - Impedansi utput ntenna -. Frekuensi -. Bandwidth -. Impedansi -. Max Daya -. Gain Penguatan) EMENTASI EM mentasi dan pe kan software udian disintesis diketahui jum untuk memban erbang logika sedianya pada D ex4 XC4VLX25 ukuran Subsist kuran subsiste usunan sistem Sem Polit 1 s (Bip Vref Vref) tt. ut 2,5 watt 50 KHz 50 Ohm(unb 50 Ohm(unb Monopole (80 - 120) 80 KHz 50 Ohm(unb 50 Watt 5 dBd DAN PE engujian dilaku simulasi Mo s software Xil mlah gerbang ngun sistem in tersebut terh Development B 5. tem Loran C em Loran C d yang telah dib

inar dan Call teknik Telkom f),(Uni 30% balance) balance) e )KHz balance) ENGUJIAN ukan dengan odelSim 6.0 linx ISE 8.1i

logika yang i, bagaimana hubung dan Board FPGA ilakukan per angun terdiri For Paper M m Cl Pu En gen Sin 4.1.1 Pada h berasal MHz. G 4.1.2 Ma reset. adalah berdasr pulsa p negatif antar pu Ga Gamb unas Aptikom ock centre, ulse generator, nvelope nerator, ne generator, Clock C asil simulasi d l dari Board F Gambar 4.1 Ha Pulse Gener asukan dari pu Keluaran yan deret-deret lo raan waktu ya positif “01” yan f “11” yang leb ulsa “00” deng

ambar 4.2a Has

ar 4.2b Hasil P m Mod Mul Con Centre dapat terlihat ba FPGA dapat di asil Pengukura rator ulse generator b ng diharapkan ogika pulsa ya ang telah dite ng lebar pulsan bar pulsanya 3 gan lebar pulsa

sil Pengukuran Pengukuran ja dulator block, ltiplexer block, nverter block. ahwa clock ya ibagi menjadi an Clock Centr berupa clock d n pada blok i ang dibangkitk etapkan. Deng nya 300 us, pul 300 us dan jar a 700 us.

n lebar pulsa

rak antar puls

, ang 10 re dan ini kan gan lsa rak sa

Seminar dan Call For Paper Munas Aptikom Politeknik Telkom Bandung, 9 Oktober 2010

57

Dengan kondisi khusus jarak pulsa kesembilan dengan pulsa kedelapan adalah 1700 us. Pulsa kesembilan ini berfungsi sebagai flag bahwa pulsa yang dikirimkan ini merupakan pulsa navigasi.

4.1.3 Envelope Generator

Pulse generator dibangitkan berdasarkan cuplikan per periode waktu.

Gambar 4.3a Hasil Pengukuran Pulsa Positif Loran C

Gambar 4.3b Hasil Pengukuran Pulsa Negatif Loran C

Gambar 4.3c Hasil Pegukuran Delay / Jarak antar pulsa Loran C

Pulsa positif maupun pulsa negatif memiliki periode pulsa sebesar 300 us, sedangkan delay akan menghasilkan nilai “0” pada gelombangnya.

4.1.4 Sine Generator

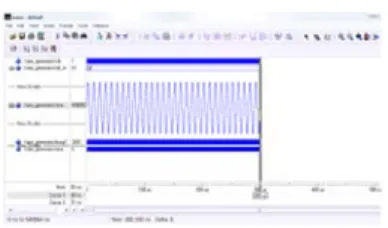

Blok Sine Generator berfungsi sebagai penghasil sinyal carrier 100 KHz dengan besar periodenya adalah 10 us yang dibangkitkan jika hanya ada pulsa yang terdeteksi. Artinya sinyal carrier ini hanya dibangkitkan selama 300 us.

Gambar 4.4 Hasil Pengukuran Sinyal Carrier selama ada pulsa terdeteksi

Sinyal carrier yang dibangkitkan selama 300 us disini bermaksud agar tidak ada kesalahan dalam membaca fasa. Untuk menghindari kesalahan pengiriman pulsa-pulsa Loran pada sisi stasiun master, karena yang membedakan pulsa positif dan negatif adalah melalui fasa dari sinyal carrier ini.

5. KESIMPULAN DAN SARAN

5.1 Kesimpulan

Dari simulasi yang dilakukan menggunakan Model Sim PLUS 6.0 dan Implementasi menggunakan FPGA, maka dapat disimpulkan beberapa hal, yaitu :

1. FPGA berhasil membangun sistem pemancar LORAN untuk servis navigasi. Yaitu dengan membangkitkan sinyal LORAN untuk stasiun master.

2. Ketelitian lebar pulsa 300 μs dan delay antara pulsa sebesar 700 μs dapat di hasilkan oleh FPGA. Sehingga sesuai dengan standar LORAN.

3. Sub system envelope generator dibangkitkan oleh sub system pulse generator, kemudian envelope mempunyai fasa dan lebar yang sama dengan pulsa yang dihasilkan blok pulse generator.

4. Sinyal carrier dengan frekuensi 100 Khz, di hasilkan selama 300 us dan akan memodulasi pulsa envelope sehingga terbentuk sinyal LORAN.

5. Sinyal Loran yang terbentuk mempunyai lebar 300 μs, delay antara sinyal 700 μs.

5.2 Saran

Beberapa hal yang belum dilakukan dapat menjadi saran pengembangan penelitian berikutnya 1. Untuk pengkajian selanjutnya dapat

perencanaan untuk sistem LORAN-C di Indonesia.

2. Penelitian dan pengembangan untuk tahap selanjutnya dapat dilihat di Road Map pengembangan sistem Loran-C di Indonesia yang terdapat di lampiran.

58 Seminar dan Call For Paper Munas Aptikom Politeknik Telkom

Bandung, 9 Oktober 2010

6. DAFTAR PUSTAKA

[1] ECKER , W.J, “Loran-C User

Handbook”, Office of Navigation Safety

and Waterway Services, Washington, DC, 1980.

[2] U.S Departement of Transportation, “Specification of the Transmitted Loran-C

Signal”, United Stated Coast Guard, 1994.

[3] L. Mills, David, “A Computer-Controlled

LORAN-C Receiver for Precision Timekeeping”, Electrical Engineering

Department University of Delaware, 1992. [4] H. Dana, Peter, “Loran C Signal

Reflections”, International Loran

Association, Long Beach, California, 1990.

[5] C. Lo, Sherman, “Data Transmission

Using LORAN C”, Department of

Aeronautics and Astronautics, Stanford University, 2001.

[6] Keputusan Menteri Perhubungan Nomor : Km.5 Tahun 2001, “Penyempurnaan

Tabel Alokasi Spektrum Frekuensi Radio Indonesia”, Departemen Perhubungan RI,

2001.

[7] Adiono, Trio, “Perancangan &

Prototyping Rangkaian Digital dengan VHDL”,

[8] ITB Microelectronic Center, “Tutorial

VHDL”