Nama

: Ahmad Sadili

Jurusan

: Teknik Komputer (Reg)

Tugas Mata Kuliah Mikroprosesor

Mikroprosesor Zilog Z80

Mikroprosesor Zilog Z80 dikembangkan oleh Zilog Inc. dan mulai dipasarkan pada tahun 1976. Z80 merupakan sebuah mikroprosesor satu chip dan dimaksudkan untuk menggantikan Intel 8080 yang memerlukan dua chip tambahan (sebuah penghasil detak sistem dan sebuah pengontrol sistem) untuk membentuk sebuah CPU yang fungsional.

Pada dasarnya Z80 memiliki semua keistimewaan (features) yang dimiliki Intel 8080, dan segi perangkat keras maupun perangkat lunak. Tetapi Z80 masih memiliki sejumlah keistimewaan penting lainnya yang tidak dimiliki Intel 8080. Salah satu keistimewaan Z80 ini adalah kemampuannya untuk melakukan penyegaran memori secara dinamis (dynamic memory refresh) secara otomatis. Adalah menarik untuk diketahui bahwa beberapa pendiri Zilog Inc. adalah mantan para ahli Intel Corporation yang ikut merancang Intel 8080, tetapi kemudian pindah ke Zilog Inc.

Mikroprosesor Z80 dibuat dengan menggunakan teknologi NMOS dan dikemas dalam sebuah DIP (dual inline package) dengan 40 pin. Jumlah saluran alamatnya sama dengan 16, dan jumlah saluran datanya delapan. Saluran-saluran ini tidak

di-multiplexed. Mikroprosesor Z80 sudah memiliki penghasil detak (clock) sendiri dan

hanya memerlukan satu tegangan catu +5 volt.

Secara garis besar dapat dikatakan bahwa jumlah register dan jumlah instruksi Z80 kira-kira dua kali Intel 8080/8085. Kumpulan instruksi Intel 8080 merupakan suatu sub kumpulan dari kumpulan instruksi Z80, artinya Z80 memiliki semua instruksi yang dimiliki Intel 8080, tetapi selain itu Z80 masih memiliki banyak instruksi lain yang tidak dimiliki Intel 8080. mikroprosesor Z80 memiliki 158 instruksi dasar, sedangkan Intel 8080 hanya 78. Karena itu bisa dikatakan bahwa Z80 upward

compatible dengan Intel 8080.

Z80 adalah mikroprosesor yang digunakan dalam komputer pribadi Radio Shack TRS-80. Z80 bekerja dengan sinyal detak (clock) 2,5 MHz. Versi Z80A sama dengan Z80, hanya Z80A dapat bekerja dengan sinyal detak 4 MHz.

Gambar 1 Chip mikroprosesor Zilog Z80 (Z0840008PSC)

Fitur Zilog Z80

Perluasan set instruksi terdiri dari 158 instruksi, termasuk 78 instruksi 8080A sebagai subsetnya (semuanya kompatibel). Instruksi baru termasuk operasi 4-, 8- dan 16-bit dengan mode pengalamatan lebih berguna seperti pengalamatan terindeks, bit, dan pengalamatan relatif.

Chip tunggal. Dengan versi NMOS untuk solusi harga rendah kinerja tinggi,

sementara versi CMOS untuk rancangan kinerja tinggi berdaya rendah

NMOS Z0840004 – 4 MHz; NMOS Z0840006 – 6,17 MHz; NMOS Z0840008 – 8 MHz. CMOS Z84C0006 – DC sampai 6,17 MHz; CMOS Z84C0008 – DC sampai 8 MHz; CMOS Z84C0010 – DC sampai 10 MHz; CMOS Z84C0020 – DC sampai 20 MHz

Versi 6 MHz bisa beroperasi pada clock 6,144 MHz.

Mikroprosesor Z80 dan keluarga periferal Z80 bisa dihubungkan dengan sebuah sistem interupsi tervektor. Sistem ini bisa dihubungkan secara daisy-chain yang mengijinkan implementasi skema interupsi terprioritas.

Penggandaan kumpulan (set) register serba-guna dan flag 17 register internal termasuk dua register indeks 16-bit Tiga mode interupsi maskable

Mode 0 – sama dengan 8080A

Mode 1 – Lingkungan non-Z80, beralamat di 38H Mode 2 – periferal keluarga Z80, interupsi tervektor Pencacah refresh memori dinamis dalam chip

Antarmuka langsung dengan memori dinamis atau statis kecepatan standar tanpa membutuhkan logika eksternal

Kinerja jauh di atas mikroprosesor chip tunggal lain dalam aplikasi 4-, 8-, atau 16-bit

Semua pin kompatibel dengan level tegangan TTL (TTL Compatible).

Arsitektur Mikroprosesor Zilog Z80

CPU Z80 adalah mikroprosesor generasi keempat yang ditingkatkan tak terkecuali untuk kebutuhan daya komputasi. Mikroprosesor ini menawarkan throughput sistem yang lebih tinggi dan penggunaan memori yang efisien dibandingkan dengan mikroprosesor yang sama pada generasi kedua dan ketiga. Register internalnya terdiri dari 208-bit memori baca/tulis yang bisa diakses oleh programmer. Register-register tersebut termasuk dua set enam register serba-guna yang bisa digunakan secara sendiri-sendiri (individual) sebagai register 8-bit atau sebagai pasangan register 16-bit. Sebagai tambahan, ada dua set register lagi, yaitu akumulator dan register bendera (flag). Grup perintah "Exchange" membuat set register utama atau register alternatif bisa diakses oleh programmer. Set alternatif mengijinkan operasi dalam mode nampak-tersembunyi (foreground-background) atau bisa digunakan sebagai cadangan bagi tanggapan interupsi sangat cepat.

CPU Z80 juga tersusun atas sebuah Stack Pointer, Program Counter, dua buah register indeks, sebuah register Refresh (counter), dan sebuah register interupsi.CPU Z80 juga sangat mudah disertakan pada sistem karena hanya memerlukan sumber tegangan tunggal +5V. Semua sinyal output sepenuhnya di-decode dan di-time untuk mengontrol sirkuit memori atau periferal standar. CPU Z80 didukung oleh perluasan keluarga pengontrol periferal.

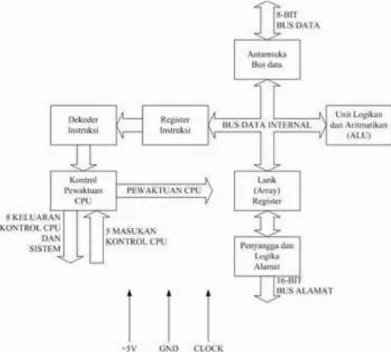

Diagram blok internal (Gambar 2) memperlihatkan fungsi utama dari prosesor Z80. Bagian-bagian utama mikroprosesor Z80 adalah:

ALU (Aritmatic and Logic Unit), bagian ini merupakan pusat pengolahan data. Di bagian ini dilakukan operasi logika, seperti: AND dan OR, serta operasi-perasi aritmatika, seperti: penjumlahan dan pengurangan.

Larik Register (Registers Array), merupakan kumpulan register-register yang terdiri dari register serba-guna dan register fungsi khusus.

Register Instruksi (Instruction Register), merupakan tempat untuk menyimpan sementara instruksi yang akan diterjemahkan oleh penerjemah (decoder) instruksi. Decoder (Penerjemah) Instruksi (Instruction Decoder), merupakan bagian yang berfungsi dalam menerjemahkan instruksi yang diambil dari memori setelah sebelumnya melewati register instruksi.

Kontrol Pewaktuan CPU (CPU Timing Control), bagian ini berfungsi dalam mengendalikan kerja CPU secara keseluruhan dan juga pewaktuan bagi periferal atau memori yang memiliki hubungan dengan CPU.

Antarmuka Bus Data (Data Bus Interface), bagian ini merupakan pintu gerbang untuk keluar-masuk data dari dan ke CPU.

dalam menyediakan alamat memori atau I/O yang diakses oleh CPU.

Bus Data Internal (Internal Data Bus), di bagian ini lalu lintas data dalam CPU berlangsung.

Gambar 2 Arsitektur mikroprosesor Zilog Z80

Tabel 1 Register-register internal mikroprosesor Zilog Z80

Register Ukuran Keterangan

A, A' Akumulator 8-bit Menyimpan sebuah operand atau hasil sebuah operasi F, F' Flag 8-bit menyimpan flag atau tanda dari operasi yang dilakukan ALU B, B' Serbaguna 8-bit Bisa digunakan tersendiri atau sebagai register 16-bit dengan C C, C' Serbaguna 8-bit Bisa digunakan tersendiri atau sebagai register 16-bit dengan B D, D' Serbaguna 8-bit Bisa digunakan tersendiri atau sebagai register 16-bit dengan E E, E' Serbaguna 8-bit Bisa digunakan tersendiri atau sebagai register 16-bit dengan D H, H' Serbaguna 8-bit Bisa digunakan tersendiri atau sebagai register 16-bit dengan L L, L' Serbaguna 8-bit Bisa digunakan tersendiri atau sebagai register

16-bit dengan H

I interupsi Register 8-bit Menyimpan delapan bit tinggi alamat memori untuk pemrosesan interupsi tervektor

R Register refresh 8-bit

Menyediakan refresh memori dinasmis yang tak terlihat oleh pengguna. Secara otomatis

di-increment dan ditempatkan pada saluran

alamat selama tiap siklus pengambilan instruksi IX Register indeks 8-bit Digunakan dalam pengalamatan terindeks

IY Register indeks 8-bit Digunakan dalam pengalamatan terindeks

SP Penunjuk Stack 8-bit Memegang alamat atas stack. Lihat instruksi Push atau Pop PC Pencacah Program 8-bit Memegang alamat instruksi selanjutnya

IFF1 -

IFF2 Interupsi Enable 8-bit Set atau reset untuk menunjukkan status interupsi IMFa -

IMFb Mode Interupsi 8-bit Menggambarkan mode interupsi

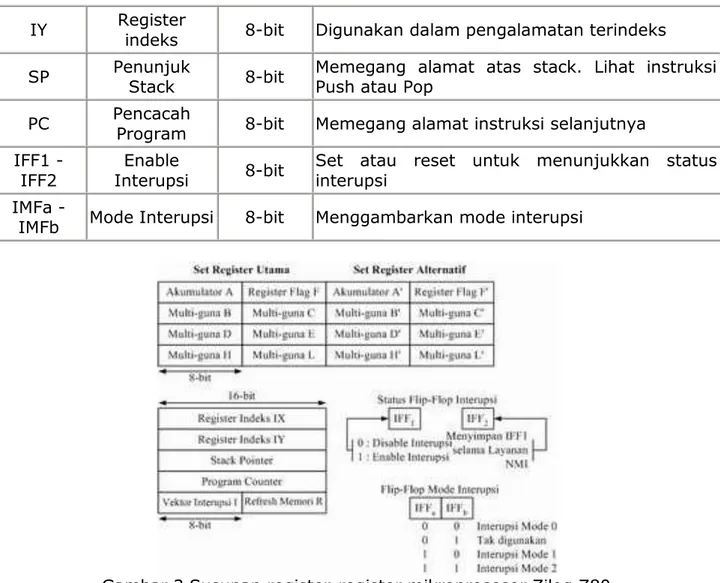

Gambar 3 Susunan register-register mikroprosesor Zilog Z80

Gambar 3 memperlihatkan tiga grup register di dalam CPU. Grup pertama terdiri atas set salinan/penggandaan register 8-bit: satu set prinsipal dan satu set alternatif (yang ditunjukkan oleh ' (petik tunggal) seperti A'). Kedua set terdiri dari register Akumalator, register Flag, dan enam register serba-guna. Transfer data antara set register salinan tersebut dipenuhi dengan instruksi "Exchange". Hasilnya tanggapan yang lebih cepat untuk interupsi dan implementasi efisien, mudah dari teknik pemrograman serba guna sebagai pemrosesan data nampak-tersembunyi (background-foreground). Set register kedua terdiri atas enam register dengan fungsi-fungsi khusus. Register-register tersebut adalah I (register interupsi), R (register refresh), IX dan IY (register indeks), SP (Stack Pointer) dan PC (Program Counter). Grup ketiga terdiri atas dua flip-flop status interupsi ditambah satu pasang flip-flop yang membantu dalam indentifikasi mode interupsi di waktu tertentu. Tabel 1 memperlihatkan informasi register-register tersebut.

Pada dasarnya register-register CPU Z80 terbagi ke dalam dua jenis, yaitu Register serba-guna (GPR: General-purpose Registers)

Register Akumulator. Register ini sangat penting peranannya dalam pengolahan data oleh ALU. Berbagai operasi logika dan aritmatika menggunakan register ini untuk menyimpan salah satu operan dan menyimpan hasil operasi yang telah dilakukan oleh ALU.

Register Bendera (flag). Register ini merupakan status dari berbagai hasil operasi yang dilakukan ALU. Operasi logika dan aritmatika yang dilakukan oleh ALU akan mempengaruhi sebagian atau seluruh flag-flag yang ada dalam register flag ini. Register flag ini terdiri atas:

7 6 5 4 3 2 1 0

S Z - H - P/V N C

S : bendera tanda (sign flag) yang menyatakan hasil operasi aritmatika. Bidang ini akan bernilai 1 jika MSB (most significant byte) bernilai 1.

Z :bendera nol (zero flag). Bidang ini menyatakan hasil dari operasi yang dilakukan ALU apakah menghasilkan nol atau tidak. Bidang ini bernilai 1 jika hasil operasi ALU sama dengan nol.

H : Bendera Pengambilan setengah (half-carry). Bendera ini bernilai 1 jika operasi penambahan atau pengurangan menghasilkan sebuah pengambilan ke dalam, atau meminjam dari bit 4 akumulator.

P/V : Bendera paritas atau oberflow. Paritas (P) dan overflow berbagi bendera yang sama. Operasi logika mengakibatkan bendera ini dengan paritas hasil sementara operasi aritmatika mempengaruhi bendera ini dengan overflow dari hasil. Jika P/V memegang paritas: P/V = 1 jika hasil operasi adalah genap; P/V = 0 jika hasilnya ganjil. Jika P/V memegang overflow, P/V = 1 jika hasil operasi mengeluarkan sebuah overflow; jika P/V tidak memegang overflow, P/V sama dengan 0.

N : Bendera Tambah/Kurang (Add/Subtract). Nilai bendera ini sama dengan 1 jika operasi sebelumnya adalah pengurangan (subtract).

C :Bendera Pengambilan/Sambungan (carry/link). Bendera ini bernilai 1 jika operasi menghasilkan pengambilan (carry) dari MSB operand atau hasil.

Register Serba-guna lainnya (B, C, D, E, H, L).

Register fungsi khusus (SFR: Special Function Registers)

Program Counter (PC), register ini perfungsi sebagai pencacah alamat instruksi selanjutnya yang akan diambil dari memori.

Stack Pointer (SP), register ini menyimpan alamat atas (top) dari stack. Stack berfungsi sebagai penyimpanan dalam memori yang sifatnya sementara bagi nilai-nilai (value) dari register-register CPU ketika register tersebut akan dipakai. Stack digunakan dengan perintah Push dan Pop.

Register Indeks (IX dan IY), register ini digunakan untuk pengalamatan terindeks. Register Interupsi (I), register ini menyimpan alamat memori untuk vektor interupsi. Register Refresh (R)

Flip-flop Status Interupsi (IFF) dan Mode Interupsi (IMF).

Interupsi

CPU Z80 menerima dua sinyal input interupsi: NMI# dan INT#. NMI# adalah interupsi

non-maskable dan memiliki prioritas tertinggi. INT# adalah interupsi berprioritas lebih

rendah dan diperlukan bahwa interupsi ini diaktifkan melalui software agar beroperasi. INT# bisa dihubungkan ke divais periferal bervariasi dalam konfigurasi terhubung OR1.

Z80 memiliki sebuah mode tanggapan tunggal bagi layanan interupsi pada interupsi

non-maskable. Interupsi maskable, INT#, memiliki tiga mode tanggapan yang bisa

diprogram yang tersedia. Mereka itu adalah:

Mode 0 – sama dengan mikroprosesor 8080

Mode 1 – layanan interupsi periferal untuk penggunaan dengan sistem bukan 8080/Z80

Mode 2 – skema interupsi tervektor, biasanya di-daisy-chain, bagi pernggunaan dengan keluarga Z80 dan divais periferal yang sesuai (kompatibel). CPU melayani interupsi dengan men-sampling sinyal NMI# dan INT# pada sisi menaik (raising edge) clock terakhir sebuah instruksi. Selanjutnya pemrosesan layanan interupsi tergantung pada jenis interupsi yang dideteksi.

Interupsi Non-Maskable (NMI: Non-Maskable Interrupt). Interupsi Non-Maskable

tidak bisa dinon-aktifkan dengan kontrol program dan oleh karena itu akan diterima di setiap waktu oleh CPU. NMI# biasanya dijadikan cadangan hanya bagi layanan jenis interupsi berprioritas tertinggi, seperti untuk shutdown setelah adanya gangguan daya yang terdeteksi. Setelah pengenalan sinyal NMI# (penyediaan BUSREQ# tidak aktif), CPU melompat ke lokasi restart 0066H. Normalnya, software mengawali pada alamat tersebut yang berisi rutin layanan interupsi.

Interupsi Maskable (INT#). Dengan tanpa memperhatikan mode interupsi yang

diset oleh pengguna, CPU menanggapi masukan (input) interupsi maskable menurut satu siklus pewaktuan umum. Setelah interupsi dideteksi oleh CPU (dinyatakan bahwa interupsi diaktifkan dan BUSREQ# tidak aktif) satu siklus pemrosesan interupsi khusus dimulai. Dimulai dengan siklus pengambilan khusus (M1#) dimana IORQ# menjadi aktif sementara MREQ# tidak, sebagaimana dalam siklus M1# normal. Sebagai tambahan, siklus M1# khusus ini secara otomatis diperpanjang sebanyak dua keadaan WAIT#, untuk mengijinkan bagi waktu yang diperlukan dalam pemberitahuan permintaan interupsi.

Operasi Interupsi Mode 0. Mode ini sama dengan prosedur layanan interupsi

mikroprosesor 8080. Divais yang menginterupsi menempatkan sebuah instruksi pada bus data. Normalnya sebuah instruksi Restart, yang memulai satu pemanggilan pada satu lokasi dari delapan lokasi restart yang terpilih di halaman (page) memori nol. Tidak seperti 8080, CPU Z80 merespon pada instruksi Call dengan hanya satu siklus pemberitahuan interupsi diikuti dengan dua siklus baca memori.

Operasi Interupsi Mode 1. Operasi Mode 1 sangat sama dengan interupsi NMI#.

Secara prinsip perbedaannya hanya satu yaitu interupsi Mode 1 restart (memulai kembali) pada alamat 0038H.

Operasi Interupsi Mode 2. Mode interupsi ini telah dirancang untuk penggunaan

kemampuan yang sangat efektif dari mikroprosesor Z80 dan hubungannya dengan keluarga periferalnya. Divais periferal yang menginterupsi memilih alamat awal rutin layanan interupsi. Divais itu melakukannya dengan menempatkan sebuah vektor 8-bit pada bus data selama siklus pemberitahuan interupsi. CPU membentuk satu penunjuk (pointer) menggunakan byte ini sebagai 8-bit rendah dan isi register I sebagai 8-bit tinggi. Penunjuk ini menunjukkan sebuah masukan (entry) dalam tabel alamat bagi rutin layanan interupsi. CPU kemudian melompat ke rutin pada alamat tersebut. Kefleksibelan dalam pemilihan alamat rutin layanan interupsi ini mengijinkan divais perifera; menggunakan beberapa jenis rutin layanan yang berbeda. Rutin-rutin tersebut mungkin ditempatkan pada suatu alamat di memori yang tersedia. Karena divais yang menginterupsi mensuplay byte orde rendah dari vektor 2-byte, bit 0 (A0) harus menjadi nol.

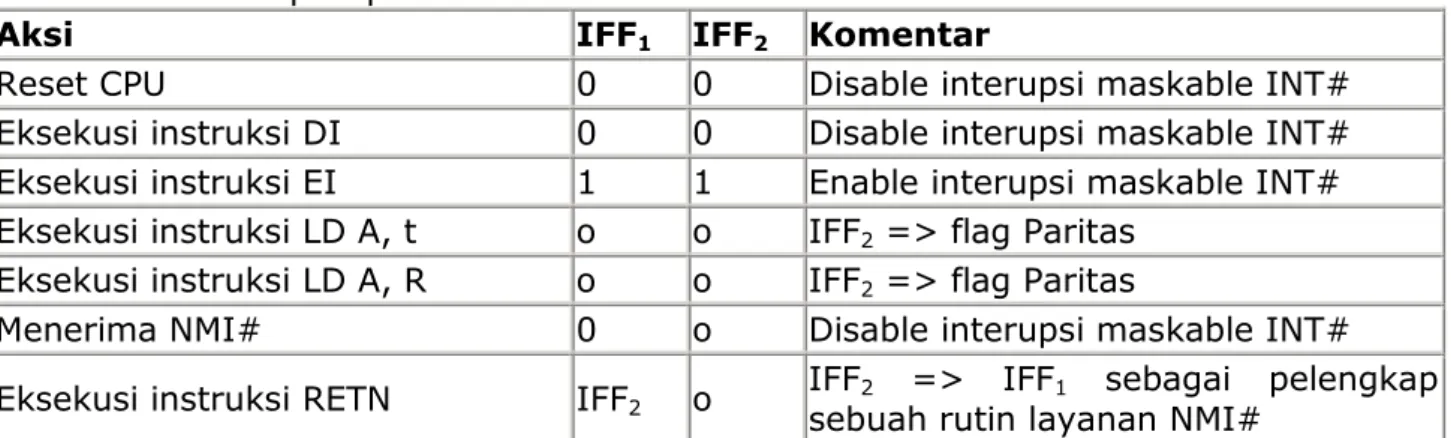

Operasi Pengaktif/Penon-aktif (Enable/Disable) Interupsi. Dua flip-flop IFF1 dan IFF2, ditunjukkan pada gambaran (dekripsi) register, digunakan untuk memberikan tanda status interupsi CPU. Operasi kedua flip-flop digambarkan pada Tabel 2.

Tabel 2 Kondisi flip-flop

Aksi IFF1 IFF2 Komentar

Reset CPU 0 0 Disable interupsi maskable INT# Eksekusi instruksi DI 0 0 Disable interupsi maskable INT# Eksekusi instruksi EI 1 1 Enable interupsi maskable INT# Eksekusi instruksi LD A, t o o IFF2 => flag Paritas

Eksekusi instruksi LD A, R o o IFF2 => flag Paritas

Menerima NMI# 0 o Disable interupsi maskable INT# Eksekusi instruksi RETN IFF2 o IFFsebuah rutin layanan NMI# 2 => IFF1 sebagai pelengkap

Konfigurasi dari kaki-kaki pin Mikroprosesor Z80:

A0 – A15. Bus Alamat (keluaran, aktif High, 3-state). A0 – A15 membentuk bus alamat

16-bit. Bus Alamat menyediakan alamat bagi pertukaran bus data memori (sampai 64Kbyte) dan bagi pertukaran divais I/O.

D0 – D7. Bus Data (masukan/keluaran, aktif High, 3-state). D0 – D7 membuat sebuah

bus data dua arah (bidirectional) 8-bit, yang digunakan untuk pertukaran data dengan memori dan I/O.

BUSACK# (Bus Request Acknowloegmnet). Pemberitahuan Bus (keluaran, aktif Low).

Pemberitahuan Bus menunjukkan pada divais yang meminta bahwa bus alamat CPU, dan sinyal kontrol MREQ#, IORQ#, RD#, dan WR# telah memasuki keadaan impedansi tinggi (high-impedance). Sirkuit eksternal sekarang bisa mengontrol jalur-jalur tersebut.

BUSREQ# (Bus Request). Permintaan Bus (masukan, aktif Low). Permintaan Bus

memiliki prioritas lebih tinggi dibandingkan dengan NMI# dan selalu dikenali di akhir siklus mesin yang sedang berjalan. BUSREQ# memaksa bus alamat CPU, bus data

dan sinyal kontrol MREQ#, IORQ#, RD# dan WR# menuju keadaan impedansi tinggi sehingga divais lain bisa mengontrol jalur-jalur tersebut. BUSREQ# normalnya terhubung OR (wired-OR) dan memerlukan satu resistor pullup eksternal bagi aplikasi tersebut. Perluasan periode BUSREQ# karena operasi DMA yang luas bisa menjaga CPU dari penyegaran (refreshing) RAM dinamis yang benar.

HALT#. Keadaan Berhenti (Halt) (output, aktif Low). HALT# menunjukkan bahwa

CPU telah mengeksekusi perintah Halt dan sedang menunggu sebuah interupsi

non-maskable atau non-maskable (dengan mask aktif) sebelum operasi bisa dilanjutkan

kembali. Ketika terhenti, CPU mengeksekusi NOP untuk menjaga refresh memori.

INT# (Interupt Request). Permintaan Interupsi (masukan, aktif Low). Permintaan

Interupsi dihasilkan oleh divais I/O. CPU menerima sebuah interupsi di akhir instruksi yang sedang berjalan jika flip-flop pengaktif interupsi terkontrol software internal (IFF) diaktifkan. INT# normalnya dihubung OR dan memerlukan resistor pullup eksternal bagi aplikasi-aplikasi tersebut.

IORQ# (I/O Request). Permintaan Masukan/Keluaran (keluaran, aktif Low, 3-state).

IORQ# menunjukkan bahwa setengah bus alamat rendah memegang sebuah alamat I/O yang sah bagi sebuah operasi penulisan atau pembacaan I/O. IORQ# juga dihasilkan secara bersamaan dengan M1# selama sebuah siklus pemberitahuan interupsi untuk menunjukkan bahwa sebuah vektor tanggapan interupsi bisa ditempatkan pada bus data.

MI# (Maskable interupt). Siklus Mesin (keluaran, aktif Low). M1#, bersama-sama

dengan MREQ#, menunjukkan bahwa siklus mesin yang sedang berjalan adalah siklus pengambilan opcode dari sebuah eksekusi instruksi. M1#, bersama-sama dengan IORQ# menunjukkan bahwa siklus pemberitahuan interupsi.

MREQ# (Memory Request). Permintaan Memori (keluaran, aktif Low, 3-state).

MREQ# menunjukkan bahwa bus alamat memegang alamat yang sah bagi operasi pembacaan memori atau penulisan memori.

NMI# (Non-maskable Interupt Request). Interupsi Non-Maskable (masukan, terpicu

ujung negatif). NMI# memiliki prioritas lebih tinggi dibandingkan dengan INT#. NMI# selalu dikenali di akhir instruksi yang sedang berjalan, tak tergantung dari status flipf-flop pengaktif interupsi (interrupt enable flip-flipf-flop), dan secara otomatis memaksa CPU untuk memulai kembali pada alamat 0066H.

RD# (Read). Baca (keluaran, aktif Low, 3-state). RD# menunjukkan bahwa CPU ingin

membaca data dari memori atau divais I/O. Divais I/O atau memori yang dialamati akan menggunakan sinyal ini untuk menempatkan data ke dalam bus data CPU.

RESET#. Reset (masukan, aktif Low). RESET# mengawali CPU sebagai berikut:

me-reset flip-flop pengaktif interupsi, menghapus PC dan register I dan R, men-set status interupsi ke Mode 0. Selama waktu reset, bus alamat dan data berkondisi impendansi tinggi, dan semua sinyal keluaran kontrol menjadi tidak aktif. Catat bahwa RESET# harus aktif minimal selama tiga siklus clock penuh sebelum operasi reset lengkap.

RFSH# (Refresh timing). Refresh (keluaran, aktif Low). RFSH#, bersama-sama

dengan MREQ# menunjukkan tujuh bit bus alamat sistem terendah bisa digunakan sebagai alamat penyegaran ke memori dinamis sistem.

WAIT#. Tunggu (masukan, aktif Low). WAIT# menunjukkan pada CPU bahwa

memori atau divais I/O yang dialamati tidak siap untuk sebuah pengiriman data. CPU selanjutnya memasuki sebuah keadaan tunggu selama sinyal tersebut aktif. Perluasan periode WAIT# bisa menjaga CPU dari penyegaran memori dinamis yang benar.

WR# (Write). Tulis (keluaran, aktif Low, 3-state). WR# menunjukkan bahwa bus data

CPU memegang data yang sah untuk disimpan pada lokasi memori atau I/O yang dialamati.