TUGAS AKHIR

TAPIS PELEWAT TINGGI MENGGUNAKAN

KAPASITOR TERSAKLAR

Diajukan untuk memenuhi salah satu syarat memperoleh gelar Sarjana Teknik pada

Program Studi Teknik Elektro Fakultas Teknik Universitas Sanata Dharma

Disusun Oleh :

ROY HARIANTO NIM : 005114081

PROGRAM STUDI TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

HIGH PASS FILTER WITH SWITCHED CAPACITOR

Final Project

Presented as Partial Fulfilment of the Requirements To Obtain the Sarjana Teknik Degree

In Electrical Engineering

ROY HARIANTO NIM : 005114081

ELECTRICAL ENGINEERING STUDY PROGRAM

ELECTRICAL ENGINEERING DEPARTMENT

ENGINEERING FACULTY

SANATA DHARMA UNIVERSITY

TAPIS PELEWAT TINGGI MEGGUNAKAN

KAPASITOR TERSAKLAR

Nama : Roy Harianto

NIM : 005114081

INTISARI

Berawal dari semakin berkembangnya teknologi khususnya teknologi telekomunikasi, antara lain telepon, radio, dan berbagai alat elektronik yang semuanya menggunakan tapis untuk membatasi arus listrik dengan frekuensi-frekuensi tertentu, sesuai dengan yang dibutuhkan, maka dibuatlah suatu tapis pelewat tinggi menggunakan kapasitor tersaklar.

Tapis pelewat tinggi ini adalah alat yang mempelajari tapis pelewat tinggi dan kapasitor tersaklar. Yang di dalamnya terdapat rangkaian-rangkaian : Tapis pelewat tinggi orde-3, pembangkit detak dua fase non-overlap, dan pewaktu. Frekuensi penggal tapis pelewat tinggi dirancang 3 kHz, frekuensi penyaklarannya 100 kHz sehingga frekuensi pewaktunya 200 kHz.

Hasil yang telah dibuat adalah frekuensi penggal 3121 Hz untuk kapasitor

utama dan 1687 Hz untuk kapasitor utama . Tanggapan frekuensinya

menghasilkan kemiringan -13.9794 dB/oktaf untuk kapasitor utama dan

-17.5323 untuk kapasitor utama .

nF

56 5,6nF

nF

56

nF

6 , 5

HIGH PASS FILTER WITH SWITCHED CAPACITOR

Nama : Roy Harianto

NIM : 005114081

ABSTRACT

Starting from the development of technology especially the technology of communication, for instances : telephone, radio, and other kinds of technology appliances using filter to limit the flow of electrics current with the certain frequencies, according to what they need , then a high pass filter with switched capacitor is created.

This high pass filter is a tool which learn the high pass filter and switched capacitor. On which the inside part includes combinations of third order high pass filter, generator of two non-overlapping clock, and clock. Cutoff frequency of high pass filter is made into 3 kHz, electric switch frequency 100 kHz so that the clock frequency is 200 kHz.

The result is a cutoff frequency of 3121 Hz for the first central capacitor

and 1687 Hz for the second central capacitor .The frequency response

produced a rolloff of -13.9794 dB/octave for the first central capacitor and

-17.5323 dB/octave for the second central capacitor .

nF

56

nF

6 , 5

nF

56

nF

6 , 5

KATA PENGANTAR

Puji dan syukur kupanjatkan kepada Allah Bapa dan Yesus Kristus atas segala

kasih dan karunia-Nya sehingga penulis dapat menyelesaikan skripsi ini dengan baik.

Penulis mengucapkan terima kasih kepada semua pihak yang telah membantu

penulis baik berupa waktu, tenaga, bimbingan, dorongan, dan sumbang saran yang

penulis butuhkan dalam penyelesaian skripsi ini. Pada kesempatan ini penulis ingin

mengucapkan terima kasih kepada :

1. Allah Bapa di Surga, atas kehendak-Mu penulis dapat menyelesaikan tugas

akhir ini.

2. Bapak Martanto,ST.,M.T., sebagai dosen pembimbing I yang telah memberikan

pengarahan, petunjuk, serta saran selama pengerjaan alat dan skripsi.

3. Bapak Ir. Tjendro, sebagai dosen pembimbing II yang telah memberikan saran,

bimbingan, dan waktu yang penulis butuhkan selama penyelesaian skripsi.

4. Kedua orang tuaku yang tanpa henti memberikan dukungan, dorongan, doa,

dan kasihnya sehingga penulis dapat menyelesaikan skripsi ini.

5. Luxy tercinta yang selalu memberikan semangat dan doanya pada waktu

penulis mengerjakan skripsi ini.

6. Teman-teman seperjuangan angkatan 2000 yang saling membantu, saling

bertukar pikiran, dan atas kebersamaannya.

Penulis menyadari bahwa dalam penulisan ini masih banyak kekurangan, oleh

karena itu penulis sangat mengharapkan saran dan kritik yang sangat membangun dari

Akhirnya penulis berharap semoga skripsi ini dapat bermanfaat bagi pembaca.

Yogyakata, Juli 2007

DAFTAR ISI

HALAMAN JUDUL ...i

HALAMAN PENGESAHAN PEMBIMBING...iii

HALAMAN PENGESAHAN PENGUJI ...iv

PERNYATAAN KEASLIAN KARYA ...v

INTISARI ...vi

ABSTRACT ...vii

KATA PENGANTAR ...viii

DAFTAR ISI ...x

DAFTAR GAMBAR ...xiii

DAFTAR TABEL ...xv

BAB I PENDAHULUAN ... 1

1.1. Latar Belakang ... 1

1.2. Tujuan Penelitian ... 2

1.3. Manfaat Penelitian ... 2

1.4. Perumusan Masalah ... 3

1.5. Batasan Masalah ... 3

1.6. Meteologi Penelitian ... 4

BAB II DASAR TEORI ... 7

2.1. Tapis Secara Umum ... 7

2.1.1. Pengertian Tapis ... 7

2.1.2. Klasifikasi Tapis... 8

2.1.3. Watak Tapis Nyata ... 9

2.1.4. Realisasi Tapis Nyata ... 11

2.2. Tapis Butterworth Pelewat Tinggi ... 11

2.2.1. Untai Tapis Pelewat Tinggi ... 14

2.2.2 Tapis Pelewat Tinggi Orde-1. ... 14

2.2.3. Tapis Pelewat Tinggi Orde-2 ... 15

2.2.4. Tapis Pelewat Tinggi Orde lebih dari 2... 16

2.3. Kapasitor Tersaklar ... 18

2.3.1. Dasar Kapasitor Tersaklar ... 18

2.3.2. Saklar MOS ... 20

2.3.3. Konfigurasi Saklar MOS ... 21

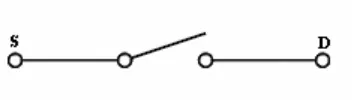

2.3.3.1. Saklar SPST ( Single Pole, Single Throw ) ... 21

2.3.3.2. Saklar SPDT (Single Pole, Double Throw). ... 22

2.3.3.3. Saklar DPDT (Double Pole, Double Throw)... 23

2.4. Tapis pelewat tinggi menggunakan kapasitor tersaklar ... 23

2.4.1. Tapis Pelewat Tinggi Orde-1 Kapasitor Tersaklar... 23

2.4.2. Tapis Pelewat Tinggi Orde-2 Kapasitor Tersaklar... 24

BAB III PERANCANGAN PERANGKAT KERAS... 27

3.1. Tapis pelewat tinggi orde-3 kapasitor tersaklar ... 28

3.2. Pembangkit detak dua fase non-overlap ... 31

BAB IV PENGUJIAN DAN PEMBAHASAN ...35

4.1. Pengamatan tanggapan frekuensi...36

4.1.1. Tapis pelewat tinggi menggunakan kapasitor utama 56 nF ...37

4.1.2. Tapis pelewat tinggi menggunakan kapasitor utama 5,6 nF ...39

4.2. Pembahasan...41

BAB V PENUTUP ... 46

5.1. Kesimpulan ... 46

5.2. Saran ... 46

DAFTAR PUSTAKA ... 48

DAFTAR GAMBAR

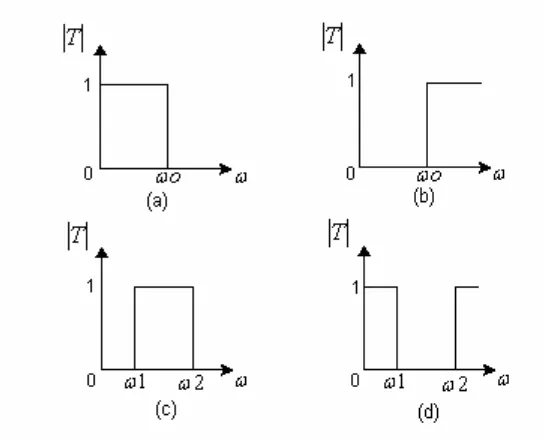

Gambar 2-1. Tanggapan tapis ideal ... 9

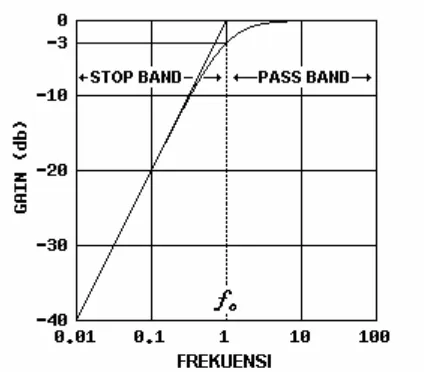

Gambar 2-2. Prinsip Pelewat Tinggi ... 11

Gambar 2-3. Kurva respons penapis pelewat tinggi... 12

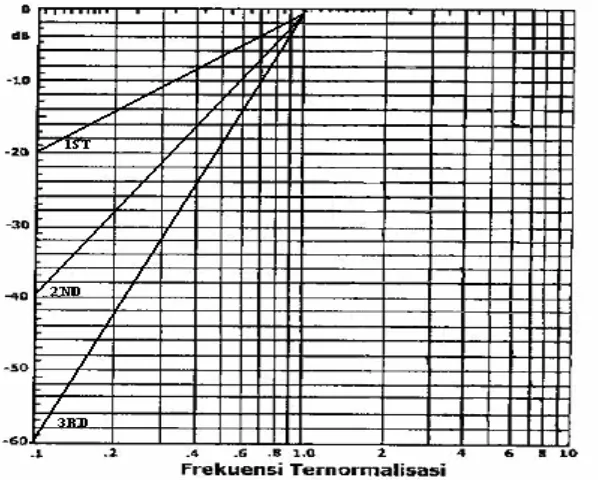

Gambar 2-4. Rolloff tapis pelewat tinggi dengan orde berbeda-beda... 13

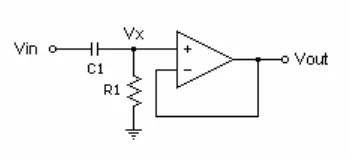

Gambar 2-5. Tapis Pelewat Tinggi Orde-1 ... 14

Gambar 2-6. Tapis Pelewat Tinggi Orde-2 ... 16

Gambar 2-7. (a) Tapis Pelewat Tinggi Orde-3 ... 17

(b) Tapis Pelewat Tinggi Orde-4 ... 17

Gambar 2-8. Untai dasar kapasitor tersaklar ... 18

Gambar 2-9. Transistor MOS ... 20

Gambar 2-10. Saklar SPST ( Single Pole, Single Throw )... 21

Gambar 2-11. Bentuk gelombang untuk mengaktifkan SPST ... 22

Gambar 2-12. Saklar SPDT (Single Pole, Double Throw)... 22

Gambar 2-13. Saklar DPDT ... 23

Gambar 2-14. HPF Orde-1 menggunakan kapasitor tersaklar ... 23

Gambar 2-15. HPF Orde-2 menggunakan kapasitor tersaklar ...24

Gambar 2-16. HPF Orde-3 menggunakan kapasitor tersaklar. ... 26

Gambar 3-1. Diagram blok tapis pelewat tinggi kapasitor tersaklar ... 27

Gambar 3-2. HPF Orde-3 menggunakan kapasitor tersaklar dengan nilainya ... 30

Gambar 3-3. IC saklar CMOS 4016 ... 31

Gambar 3-4. Untai pembangkit detak dua fase non-overlap ... 32

Gambar 4-1. Kurva tanggapan frekuensi untuk kapsitor utama C =56nF ... 38

DAFTAR TABEL

Tabel 4-1. Data hasil pengujian dengan kapsitor utama C=56nF ... 37

Tabel 4-2. Data hasil pengujian dengan kapsitor utama C=5,6nF ... 39

1

BAB I

PENDAHULUAN

1.1. Latar Belakang

Salah satu bentuk kemajuan teknologi elektronika yang telah dapat

dirasakan manfaatnya adalah penapis aktif. Peran suatu penapis aktif yang begitu

besar bagi peralatan-peralatan elektronik terkadang tidak disadari atau bahkan

tidak diketahui. Penapis aktif disini menggunakan kapasitor tersaklar. Dimana

kapasitor tersaklar ini digunakan untuk menggantikan resistor ekivalennya.

Karena tapis aktif RC tidak bisa memuaskan dalam hal keakuratan dan kestabilan

yang dikehendaki. Pengetahuan mahasiswa elektro mengenai penapis aktif yang

menggunakan kapasitor tersaklar pun terkadang tidaklah begitu baik. Dalam hal

ini, pemahaman tentang penapis aktif menggunakan kapasitor tersaklar dapat

menjadi maksimal apabila mahasiswa juga melakukan praktek langsung maupun

melalui perancangan suatu alat yang menggunakan penapis aktif kapasitor

tersaklar sebagai salah satu komponennya.

Di dalam penapis aktif kapasitor tersaklar ini menggunakan tapis

pelewat tinggi (high-pass filter). Penapis pelewat tinggi menggunakan kapasitor

tersaklar ini menggunakan kapasitor tersaklar sebagai pengganti resistor

ekivalennya. Penemuan ini didasarkan atas kenyataan bahwa sebuah resistor dapat

disimulasikan dengan menggunakan saklar MOS yang dioperasikan secara

periodis dan sebuah kapasitor. Konstanta waktu dari rangkaian bukan lagi

setara resistor berbanding lurus dengan perioda penyaklaran, atau berbanding

terbalik dengan frekuensi penyaklaran.

1.2. Tujuan Penelitian

Tujuan dari penelitian Tapis pelewat tinggi menggunakan kapasitor

tersaklar ini adalah:

1.2.1. Membuat suatu tapis pelewat tinggi menggunakan kapasitor tersaklar

dengan menerapkan pengetahuan tentang kapasitor tersaklar.

1.2.2. Dengan pembuatan tapis pelewat tinggi menggunakan kapasitor

tersaklar ini dapat mengurangi tingkat kesalahan resistor,

menggantikannya dengan kapasitor tersaklar pada tapis pelewat tinggi.

1.3. Manfaat Penelitian

Manfaat dari penelitian Tapis pelewat tinggi menggunakan kapasitor

tersaklar ini adalah:

1.3.1. Terciptanya pemahaman yang lebih baik tentang berbagai hal tentang

tapis pelewat tinggi dan kapasitor tersaklar.

1.3.2. Adanya acuan memakai tapis pelewat tinggi menggunakan kapasitor

1.4. Perumusan Masalah

Permasalahan yang diajukan dalam penelitian ini:

1.4.1. Bagaimana merancang tapis pelewat tinggi menggunakan kapasitor

tersaklar?

1.4.2. Bagaimana menentukan nilai kapasitor tersaklar (CR)?

1.5. Batasan Masalah

Penelitian pada Tapis pelewat tinggi menggunakan kapasitor tersaklar ini

dibatasi pada masalah-masalah sebagai berikut:

1.5.1. Tapis pelewat tinggi tersebut menggunakan tanggapan penaksiran

Butterworth.

1.5.2. Orde tapis pelewat tinggi yang digunakan adalah orde ketiga dengan

frekuensi penggal 3 kHz.

1.5.3. Tapis pelewat tinggi dibuat dua untaian dengan nilai kapasitor

utamanya berbeda yaitu C dan .

1.5.4. Tapis diimplementasikan dengan menggunakan komponen yang

sifatnya diskret yaitu dengan menggunakan kapasitor, penguat operasi,

dan saklar CMOS.

nF

56

1.5.5. Frekuensi masukannya menggunakan AFG (Audio Function

Generator) yang batasan nilainya antara 20 Hz sampai dengan 20

KHz.

1.5.6. Frekuensi penyaklarannya 100 KHz.

1.6. Metodologi Penelitian

Dalam perancangan piranti Tapis pelewat tinggi menggunakan kapasitor

tersaklar melalui beberapa tahap penelitian dasar yang akan mendukung

suksesnya perancangan ini. Tahap-tahap penelitian tersebut adalah:

1.6.1. Mengumpulkan bahan literature pendukung: paper, buku-buku, dan

data sheet.

1.6.2. Pembuatan alat.

1.6.3. Pengujian dan perbaikan alat: pengukuran tegangan masukan dan

tegangan keluaran pada penapis pelewat atas dengan menggunakan

osiloskop, pembuatan grafik tanggapan frekuensi.

1.7. Sistematika Penulisan

Sistematika penulisan dalam penyusunan laporan penelitian ini tersusun

sebagai berikut:

BAB I PENDAHULUAN

Pada bab ini berisi tentang: latar belakang yang mendasari

dipilihnya topik dalam tugas akhir ini, tujuan penelitian, manfaat

penelitian, perumusan masalah, batasan masalah, metodologi

penelitian, dan sistematika penulisan.

BAB II DASAR TEORI

Pada bab ini berisi tentang teori yang berkaitan tentang tapis

Butterworth untuk tapis pelewat tinggi dan dasar-dasar kapasitor

tersaklar dengan operasi analog yang dapat dipakai dengan

kapasitor tersaklar.

BAB III PERANCANGAN PERANGKAT KERAS

Pada bab ini berisi tentang perancangan tapis pelewat tinggi orde

ketiga dengan menggunakan kapasitor tersaklar beserta

BAB IV PENGUJIAN DAN PEMBAHASAN

Pada bab ini berisi tentang data pengamatan terhadap tapis yang

telah diimplementasikan dan pembahasan dan analisa terhadap data

pengamatan tersebut.

BAB V PENUTUPAN

Pada bab ini berisi tentang kesimpulan terhadap seluruh

pembahasan tentang Tapis pelewat atas menggunakan kapasitor

BAB II

DASAR TEORI

2.1. Tapis Secara Umum

2.1.1. Pengertian Tapis

Penapis merupakan sebuah alat atau rangkaian atau substansi yang

meneruskan atau meloloskan arus listrik pada frekuensi-frekuensi atau jangkauan

frekuensi tertentu serta menahan (menghalangi) frekuensi-frekuensi lainnya.

Penapis dapat berupa penapis pasif atau penapis aktif.

Secara khusus, sebuah penapis aktif adalah suatu rangkaian penapis yang

tersusun atas resistor-resistor dan kapasitor-kapasitor disertai dengan suatu

rangkain penguat, biasanya berupa penguat operasional. Sedangkan penapis pasif

hanya terdiri dari resistor, induktor dan kapasitor.

Sebuah penapis aktif memiliki beberapa kelebihan sebagai berikut:

1. Tidak ada sinyal hilang – Hal ini disebabkan karena penguat operasional

mampu menyediakan penguat atau gain, sehingga sinyal masukan tidak akan

segera mengalami pelemahan (atenuasi) selama rangkaian meneruskan

sinyal-sinyal dengan frekuensi yang dikehendaki.

2. Biaya dan kemudahan – Sebenarnya rangkaian penapis aktif ongkos

disebabkan karena pada rangkain pasif menggunakan komponen induktor

yang harganya jauh lebih mahal dan tidak selalu tersedia di pasaran.

3. Penyetelan – Penapis aktif mudah disetel ( tune ) untuk jangkauan frekuensi

yang lebar tanpa mempengaruhi tanggap rangkaian yang telah ditentukan

( sesuai dengan yang diinginkan ).

4. Isolasi – Sebagai akibat dari penggunaan penguat operasional, penapis aktif

akan memiliki impedansi masukan yang tinggi dan keluaran yang rendah, hal

ini sebenarnya hampir menjamin tidak adanya interaksi antara penapis dengan

sumber atau beban sinyal.

2.1.2. Klasifikasi Tapis

Tapis diklasifikasikan menurut fungsi yang dibentuk dalam hal jangkauan

frekuensi, yaitu jalur lewat (pass band) dan jalur henti (stop band). Pola dari jalur

lewat dan jalur henti, mempunyai empat macam tapis yang sangat umum.

Keempat tapis tersebut dapat dijelaskan sebagai berikut:

1. Tapis pelewat rendah (low pass filter)

Tapis ini memiliki jalur pelewat dari ω=0 sampai ω=ωo, denganωo

disebut sebagai frekuensi pancung, seperti gambar 2-1.(a)

2. Tapis pelewat tinggi (high pass filter)

Tapis ini merupakan komplemen dari tapis pelewat rendah, dengan frekuensi

dari 0 sampaiωo merupakan jalur henti (stop band), sedangkan jalur pelewat

(pass band) adalah dari frekuensiωo sampai tak hingga, sepert gambar

3. Tapis pelewat jalur (band pass filter)

Tapis ini merupakan frekuensi antara 1ω sampai 2ω , selain frekuensi ini tidak dilewatkan, seperti gambar 2-1.(c).

4. Tapis jalur henti (band elimination filter)

Tapis ini merupakan komplemen dari tapis pelewat jalur dengan frekuensi dari

1

ω sampai 2ω dihentikandan lainnya dilewatkan. Tapis ini biasa disebut

“notch filter”, seperti gambar 2-1.(d)

Gambar 2-1. Tanggapan tapis ideal

2.1.3. Watak Tapis Nyata

Dalam praktisnya, penapisan dikehendaki untuk menolak komponen sinyal

dengan merancang tapis yang menghasilkan pelemahan ( atenuasi ) pada daerah

frekuensi tertentu, dan diinginkan komponen-komponen dari sinyal yang lewat

Dalam hal ini perlu, adanya pengukuran atenuasi dan perolehan ( gain ).

Pelemahan atau atenuasi didefinisikan sebagai :

[ ]

T dBlog 20

− =

α . . . (2-1)

Dengan adalah perbandingan antara besaran output dengan besaran

input. Satuan pelemahan adalah decibel (dB), dan tanda minus menjelaskan

bahwa

T

α adalah positif bila rangkaian menghasilkan rugi-rugi, seperti dijelaskan

dengan T ≤1. Bila dipakai simbol yang berlainan, yang menyatakan suatu

perolehan (gain), dengan :

1

≥ T

[ ]

T dBA=−20log . . . (2-2)

Penyelesaian untuk

[ ]

T apabila α sudah diketahui, adalah denganpersamaan :

[ ]

T =10 −α20 . . . .(2-3)Sedangkan bila diketahui A,

[ ]

T dapat dicari dengan persamaan :[ ]

(

)

AT = 100.05 . . . (2-4)

Oleh karena tidak mungkin merealisasikan tapis ideal dengan perubahan

yang tajam dari jalur pelewat dan jalur henti, maka tapis ideal harus didekati

dengan tapis yang nyata. Watak yang dikehendaki ditentukan dengan

mendefinisikan perbedaan antara jalur pelewat dengan jalur henti, sebagai berikut:

1. Jalur pelewat adalah suatu tanggapan yang memiliki pelemahan kurang dari

suatu nilai perancangan, yakni αmaks.

2. Jalur henti adalah tanggapan yang selalu memiliki pelemahan lebih besar dari

3. Jalur frekuensi antara jalur henti dan jalur pelewat didefinisikan sebagai jalur

peralihan.

Pada tapis pelewat rendah jalur, pelewat berada pada ω=0sampai

p

ω

ω = , jalur peralihan adalah dari ωpsampai ωs, dan jalur henti adalah semua

frekuensi diatas ωs sampai tak terhingga. Huruf s dan p pada ω menandakan tepi dari jalur pelewat dan jalur henti. Konsep yang sama diterapkan pada pelewat

tinggi, pelewat jalur dan penolak jalur.

2.1.4. Realisasi Tapis Nyata

Untuk merealisasikan tapis dengan watak yang ideal tidak mungkin

dicapai, dengan adanya keterbatasan komponen yang digunakan.

Ada beberapa realisasi tapis sebagai pendekatan tapis ideal antara lain

tapis Butterworrh. Watak tapis Butterworth yalah pada jalur pelewat memiliki

tanggapan yang datar maksium ( maximally flat ).

2.2. Tapis Butterworth Pelewat Tinggi

Tapis pelewat tinggi adalah suatu tapis yang melewatkan sinyal dengan

frekuensi-frekuensi yang tinggi dan menolak frekuensi-frekuensi yang rendah.

Sebagai contoh seperti pada gambar 2-2, yaitu suatu sinyal berfrekuensi tinggi

yang tergantung oleh getaran frekuensi rendah.

Gambar 2-3. Kurva respons penapis pelewat tinggi

Semua penapis Butterworth mempunyai penguatan pada

det 1

2 0

0 = π f = rad

ω , dimana diperoleh persamaan sebagai berikut:

( )

dBf f f

At

⎥ ⎥ ⎥ ⎥

⎦ ⎤

⎢ ⎢ ⎢ ⎢

⎣ ⎡

+ =

n 2 0 n

) ( 1

1 log

20 ...(2-5)

Keterangan:

( )

fAtn = tanggapan frekuensi secara teoritis

( )

dB0

f = frekuensi penggal

( )

Hzf = frekuensi pengamatan

( )

Hzn = orde tapis

Pada gambar 2-3. kemiringan atau gradien garis pada stopband dinamakan

sebagai rolloff atau falloff dan didefinisikan berdasarkan order (tingkatan) tapis

- Tapis pelewat tinggi orde pertama (1st order) rolloff-nya adalah -6

dB/oktaf atau -20 dB/dekade

- Tapis pelewat tinggi orde kedua (2nd order) rolloff-nya adalah -12

dB/oktaf atau -40 dB/dekade

- Tapis pelewat tinggi orde ketiga (3rd order) rolloff-nya adalah -18

dB/oktaf atau -60 dB/dekade

Sebuah oktaf (an octave) memiliki pengertian menggandakan maupun pembagi

dua suatu frekuensi, misalnya untuk 1 kHz, maka oktaf diatas 1 kHz adalah 2, 4, 8

kHz dan seterusnya. sedangkan yang dibawah 1 kHz adalah 500, 250, 125 Hz dan

seterusnya. Sedangkan dekade (decade) adalah sepuluh kali atau sepersepuluh kali

suatu frekuensi, misalnya untuk 1 kHz, dekade diatasnya adalah 10, 100 kHz dan

seterusnya, sedangkan di bawahnya adalah 100, 10, 1 Hz, dan seterusnya.

2.2.1. Untai Tapis Pelewat Tinggi

Untai tapis analog pelewat tinggi dapat menggunakan untai Sallen & Key,

terutama untuk orde genap. Untuk penjelasan yang lebih rinci, berikut dibahas

orde satu sampai orde lebih dari dua.

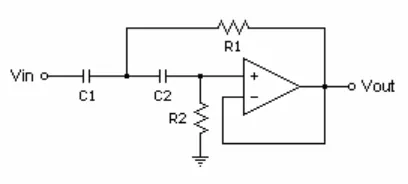

2.2.1.1. Tapis Pelewat Tinggi Orde-1

Untai pelewat tinggi orde-1 ini dibangun dengan sebuah kapasitor dan

sebuah resistor dan bisa ditambahkan penguat operasi pada keluarannya. Untai ini

menggunakan penguatan satu tidak membalik, sehingga tegangan keluarannya

sama dengan tegangan masukannya. Hubungan antara tegangan keluaran dengan

tegangan masukan dapat dicari dengan metode pembagi tegangan (superposisi).

Tegangan pada masukan penguat operasi Vx, yang sama dengan Vo, merupakan

superposisi dari sinyal masukan dengan ground, seperti gambar 2-5. perbandingan

tegangan keluaran dengan tegangan masukan yang dinyatakan dalam T( ),

dengan =

s

s jω, adalah sebagai berikut:

( )

( )

( )

(

RC s

s s

V s V s T

i o

1

+ =

= . . . (2-6)

Untaian ini memiliki frekuensi setengah daya sebesar:

( )

1RC0 =

ω . . . (2-7)

Gambar 2-5. Tapis Pelewat Tinggi Orde-1

Dengan melihat watak alih tapis pelewat tinggi ini dapat diketahui cara

kerja dari tapis ini. Bila frekuensi (ω) sama dengan nol maka besar tanggapan

T( j0) juga sama dengan nol. Saat frekuensi (ω) =ω0, tanggapan T( jω 0) =

2

1 , dan bila frekuensi (ω) menuju tak berhingga maka besar tanggapannya

akan sama satu.

2.2.1.2. Tapis Pelewat Tinggi Orde-2

Untai pelewat tinggi orde-2 menggunakan untai CR Sallen & key seperti

pada gambar 2-6.

Untai ini memiliki watak alih seperti berikut ini:

( )

(

)

2 1 2 1 2 1 2 2 1 2 2 1 c c R R s c c R c c s s s T + ⎥⎦ ⎤ ⎢⎣ ⎡ + + =Untuk mencari frekuensi pusat dan faktor kualitas tapis Q, bisa dibandingkan

dengan watak alih tapis orde-2 standar.

Watak alih tapis pelewat tinggi standar adalah:

( )

⎟ ⎠ ⎞ ⎜ ⎝ ⎛ + ⎥⎦ ⎤ ⎢⎣ ⎡ + = 2 0 0 2 2 Q ω ω s s s sT . . . (2-8)

Dari sini dapat ditentukan ωo dan Q dari untai pelewat tinggi orde-2, sebagai berikut: 2 1 2 1 0 1 C C R R =

ω . . . (2-9)

(

1 2)

1 2 2 1 Q C C R R C C + ⎥ ⎦ ⎤ ⎢ ⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛

Gambar 2-6. Tapis Pelewat Tinggi Orde-2

Apabila diambil harga ωo=1, serta = =1, maka akan didapatkan nilai dan

sebagai berikut:

1

c c2 R1

2 R

Q 2 1 1 =

R . . . (2-11)

Q 2 2 =

R . . . (2-12)

Oleh karena tanggapan tapis yang dikehendaki berupa tanggapan

Butterworth maka nilai Q dari pelewat tinggi orde-2 sama dengan 0,7071.

sehingga untuk nilai-nilai ternormalisasi didapatkan sebagai berikut:

1 0 =

ω

1 2

1 =c =

c

5 , 0

1 =

R

2

2 =

R

2.2.1.3. Tapis Pelewat Tinggi Orde lebih dari 2

Untuk mendapatkan untai tapis pelewat tinggi yang memiliki orde lebih

dari dua dilakukan dengan cara mengkaskade tapis pelewat tinggi yang berorde

satu dengan orde-2 atau berorde dua semua. Untuk tapis dengan orde ganjil, salah

satu untainya berupa untai tapis orde satu seperti pada gambar 2-7. dan untuk orde

(a)

(b)

Gambar 2-7. (a) Tapis Pelewat Tinggi Orde-3;(b)Tapis Pelewat Tinggi Orde-4

Didalam pembentukan tapis pelewat tinggi berorde lebih dari dua perlu

diperhatikan factor Q dari masing-masing bagian dari kaskade memiliki harga

yang tidak sama. Hal ini disebabkan karena untuk tanggapan Butterworth nilai Q

sudah tertentu sesuai dengan orde dari tapis.

Watak alih tapis pelewat tinggi orde lebih dari dua besarnya merupakan

perkalian dari watak alih tiap-tiap pembangun kaskade. Frekuensi setengah daya

(3 dB) dari masing-masing tapis pembangun kaskade memiliki nilai yang sama,

2.3. Kapasitor Tersaklar

Dalam teknologi pembuatan MOS ada kecenderungan lebih mudah

membuat kapasitor dan saklar, dibanding membuat resistor dengan ketelitian yang

tinggi. Pengetahuan tentang hambatan yang dapat didekati dengan dua buah saklar

MOS dan sebuah kapasitor merupakan kunci akan pemecahan masalah pembuatan

hambatan ini, dan telah memunculkan bidang baru dalam perancangan suatu tapis,

terutamanya disesuaikan dengan pembuatan untai terpadu.

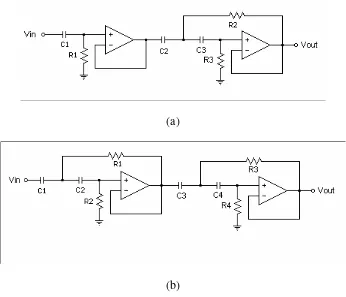

2.3.1. Dasar Kapasitor Tersaklar

Banyak fungsi penapis analog dibentuk oleh tapis aktif dengan Op Amp

dapat ditiru dengan penggunaan untai kapasitor tersaklar. Untai kapasitor tersaklar

dibangun oleh Op Amp, saklar MOS dan kapasitor-kapasitor yang nilai

kapasitansinya kecil. Bila Op Amp terbuat dari MOSFET, seluruh jaringan

kapasitor tersaklar tak mengandung resistor yang dapat dibangun pada untai

terintegrasi tunggal. Frekuensi kutub dan frekuensi nol dari untai kapasitor

tersaklar dapat dikendalikan dari luar melalui frekuensi clock. Kenampakan ini

mengundangkan suatu keuntungan yang prinsip disbanding tapis analog yang

memakai resistor.

Dasar dari untaian kapasitor tersaklar sebagai pengganti resistor terdapat

pada untai sederhana pada gambar 2-7. Saklar sinkronisasi S1 dan S2 membuka

dan menutup setiap setengah siklus dari interval clock Τc dan secara periodik

memuati dan melucuti muatan pada kapasitor. Untuk susunan ini akan berfungsi

sebagai resistor, maka anggapan berikut ini harus dipenuhi.

1. Pada saat tertentu hanya ada satu saklar yang tertutup; kedua saklar tak pernah

tertutup secara serentak.

2. Selang waktu selama kedua saklar tidak tertutup sangat singkat dibandingkan

dengan periode detak Τc.

3. Apabila S1 tertutup, kapasitor memuati secara cepat tegangan sinyal masukan

. s

V

4. Jika S2 tertutup, kapasitor segera melucuti muatan ke ground.

Selama interval S1 tertutup, muatan kapasitor mencapai nilai

s

V C =

ϕ . . . . . . (2-13)

Muatan ini secara lengkap dilucuti ke ground ketika S2 tertutup. Dalam satu

interval clock Τc, muatan keseluruhan akibat tegangan Vs adalah sama dengan:

c s

T V C

t =

Δ

Δϕ

. . . (2-14)

Muatan ini harus secara terus menerus disuplai ke kapasitor dengan sumber ,

karena muatan dilucuti ke ground setelah setiap siklus clock. Setelah beberapa

siklus clock, aliran muatan yang kontinyu dari arus tunak (steady) yang

memiliki rerata sama dengan :

s

V

s

( )

c s T

c T

V C dt

t T

i c =

Δ Δ

=

∫

0 1

1 ϕ

. . . (2-15)

Perbandingan antara dengan C mempunyai satuan resistansi

(sec/Coulomb/Volt = Ohm), oleh karena itu persamaan tersebut mempunyai

bentuk hukum Ohm : c

Τ

( )

R V

i = s

1 . . . (2-16)

Mekanisme rugi-rugi dari untai kapasitor tersaklar pada gambar 2-12. dapat

dimodelkan sebagai sebuah resistansi dengan nilai = C Tc

.

clk

eq 1C F

R = × . . . (2-17)

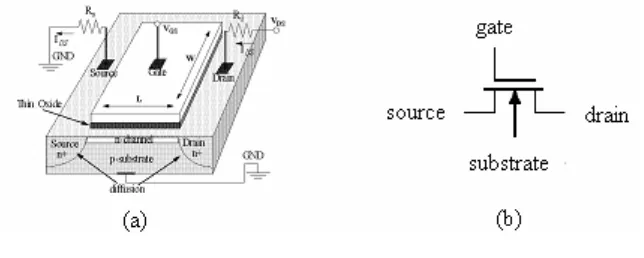

2.3.2. Saklar MOS

Pada gambar 2-9. menunjukkan penampang melintang dari suatu untai

terpadu dari transistor MOS. Salah satu penggunaannya adalah sebagai suatu

saklar, yakni saklar MOS. Transistor MOS beroperasi sebagai saklar bila tegangan

kerja antara sumber (source) dan gerbang (gate) adalah nol dan tegangan yang

berharga lebih besar dari tegangan ambang VTH.

2.3.3. Konfigurasi Saklar MOS

2.3.3.1. Saklar SPST ( Single Pole, Single Throw )

Pada gambar 2-9.(b) menunjukan suatu lambang transistor MOS.

Tegangan penyaklaran dituliskan sebagai gate dan ujung-ujung sebagai source

dan drain yang mempunyai resistansi sebesar Rgate. Ketika transistor keadaan

‘OFF’, maka Rgate mempunyai nilai yang sangat besar sekitar 100 Mohm -1000

Mohm. Sedangkan bila transistor keadan ‘ON’, maka Rgate sangat kecil nilainya

yakni sekitar 10 Kohm – 100 Ohm, tergantung pada ukuran transiator dalam suatu

keping. Pada gambar 2-10. berikut ini menunjukkan saat saklar membuka atau

menutup tergantung pada harga dari Rgate. Saklar ini dikenal sebagai saklar SPST

( Single Pole, Single Throw).

Gambar 2-10. Saklar SPST ( Single Pole, Single Throw)

Bentuk gelombang tegangan yang dipakai untuk menaktifkan saklar MOS

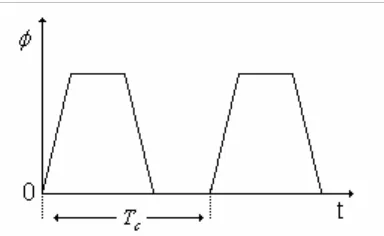

diperlihatkan pada gambar 2-11. di sini ada suatu peubah yang berubah yang

dituliskan sebagai VDS dan disimbolkan dengan φ untuk pemakaian yang lebih

umum. Gelombang ini dihasilkan oleh sumber detak (clock) yang memiliki

Gambar 2-11. Bentuk gelombang untuk mengaktifkan SPST

Besaran ⎟

⎠ ⎞ ⎜ ⎝ ⎛ =

c

c T

f 1 disebut sebagai frekuensi clock dari deretan pulsa. Dalam

hal ini clock digunakan untuk mengaktifkan dan mematikan saklar MOS.

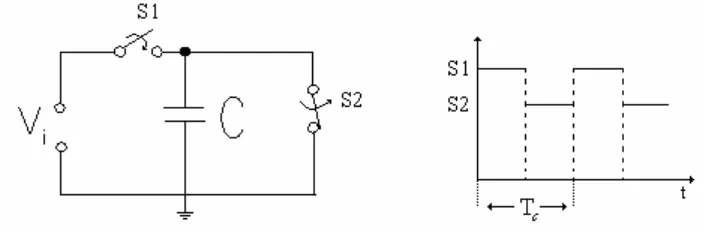

3.3.3.2. Saklar SPDT (Single Pole, Double Throw)

Apabila dua buah saklar MOS dihubungkan, dan dikendalikan oleh dua

bentuk gelombang φ1 dan φ2. Maka bentuk gelombang φ1 dan φ2 merupakan dua gelombang yang memiliki fase yang berbeda, tetapi memiliki frekuensi yang

sama, dan juga keduanya tidak saling tumpang tindih (non-overlap). Sehingga bila

1

φ ON dan φ2 OFF atau sebaliknya. Oleh karena itu tidak terjadi hubungan

langsung dari titik 1 dan titik dua yaitu pada saat saklar pertama terhubung saklar

kedua terbuka atau sebaliknya. Penyalaran seperti ini ekivalen dengan yang

ditunjukkan pada gambar 2-12. Saklar semacam ini disebut sebagai saklar kutup

tunggal dua posisi (SPDT = Single Pole, Double Throw).

2.3.3.3. Saklar DPDT (Double Pole, Double Throw)

Salah satu skema untuk penyaklaran dikembangkan dengan menggunakan

saklar MOS SPST seperti pada gambar 2-13. Dengan dua tegangan clock φ1 dan

2

φ yang dihubungkan seperti pada gambar 2-13. Saklar ini disebut saklar dua

katup dua posisi (DPDT = Double Pole, Double Throw).

Gambar 2-13. Saklar DPDT

2.4. Tapis Pelewat Tinggi Menggunakan Kapasitor Tersaklar

2.4.1. Tapis Pelewat Tinggi Orde-1 Kapasitor Tersaklar

Dengan menggantikan resistor pada untai RC analog Orde-1 dengan

sebuah kapasitor tersaklar didapatkan untai tapis pelewat tinggi orde-1, yang

hasilnya dapat dilihat pada gambar 2-14. berikut ini;

Watak alih untai tapis pelewat tinggi orde-1 kapasitor tersaklar seperti

pada gambar 2-14. ini dapat dicari dengan dengan menggantikan resistor R

dengan

(

⎥⎦ ⎤ ⎢⎣ ⎡ clk R F C

1 pada watak alih tapis analog. Sehingga akan dihasilkan :

( )

⎥⎦ ⎤ ⎢⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ + = C C F s s s T R clk. . . (2-18)

Harga frekuensi pusat sebesar

(

)

C F

CR clk

= 0

ω . . . (2-19)

Dengan memperhatikan persamaan di atas, dapat diketahui bahwa frekuensi 3 dB

pelewat atas berbanding lurus dengan frekuensi detak , dengan suatu

konstanta tetap yang ditentukan oleh perbandingan kapasitansi clk F ⎥⎦ ⎤ ⎢⎣ ⎡ C

CR .

2.4.2. Tapis Pelewat Tinggi Orde-2 Kapasitor Tersaklar

Untai tapis pelewat tinggi orde-2 kapasitor tersaklar ini didasarkan pada

untaian sallen & key pelewat atas analog orde-2. dengan pemilihan susunan saklar

yang tepat pada tapis ini dapat dihasilkan seperti pada gambar 2.15.

Gambar 2-15. HPF Orde-2 menggunakan kapasitor tersaklar

Frekuensi pusat dan faktor kualitas ini ditetapkan dengan persamaan : 2 1 2 1 0 C C C C

F R R

clk

=

ω . . . (2-20)

Q

(

)

2 1 2 1 2 1 1 R R C C C C C C +

= . . . (2-21)

Apabila diambil nilai ternormalisasi, yakni dengan membuat ω0 =1, serta

membuat nilai kapasitor pada rangkaian analog C1 =C2 didapatkan hubungan

seperti berikut :

Q 2

1 1

2

1 = =

R

R . . . (2-22)

clk R R F R C C 1 2 1 1 1 =

= . . . (2-23)

Dengan mengetahui frekuensi pusat ω0 dari perancangan serta nilai Q ( dalam hal

ini untuk N = 2, Q = 0,7071 ), serta nilai kapasitor dan , maka nilai-nilai

pada untaian kapasitor tersaklar selanjutnya dapat ditentukan dari

persamaan-persamaan :

1

C C2

0

ω

= kf

(

C kf)

km= 1

[

]

clk R F C C 0 clk 1 2 F km Q 2 ω == . . . (2-24)

[

]

clkR F C C 2 F km 2Q 1 0 clk 2 ω =

Jadi dengan menentukan nilai ω0, , dan akan dapat dicari nilai-nilai

kapasitor tersaklar dan dari tapis pelewat tinggi orde dua.

C Fclk

1

R

C CR2

2.4.3. Tapis Pelewat Tinggi Orde lebih dari 2 Kapasitor Tersaklar

Disini perlu diperhatikan susunan atau posisi saklar. Contoh untuk tapis

pelawat tinggi orde-3 dapat digambarkan pada gambar 2-16.

Gambar 2-16. HPF Orde-3 menggunakan kapasitor tersaklar

Untuk mendapatkan nilai-nilai komponen kapasitor tersaklar dari tiap-tiap

tingkat dilakukan dengan perhitungan seperti halnya untuk pelewat tinggi orde-1

dan orde-2. untuk mendapatkan tanggapan tapis Butterworth, maka faktor kualitas

yang dipakai dalam perhitungan untuk tapis yang berorde lebih dari dua

dipergunakan nilai Q. Di mana untuk tanggapan Butterworth nilai Q sudah ditentu

sesuai dengan orde dari tapis. Misalkan orde-4, memiliki dua macam nilai Q yaitu

Q1= 0.54 dan Q = 1,31. Dari sini dapat dinyatakan bahwa pembentukan tapis

pelewat tinggi Butterworth orde-4 tidak sama dengan mengkaskade dua buah tapis

yang nilai Q-nya hanya satu macam. Tanggapan yang dikehendaki adalah

Butterworth, sehingga perhitungan nilai Q harus disesuaikan dengan orde tapis

BAB III

PERANCANGAN PERANGKAT KERAS

Perancangan perangkat keras ini terdiri dari dua bagian, bagian pertama

adalah Pembangkit detak dua fase non-overlap yang berfungsi untuk penyaklaran

saklar MOS berupa pembangkit detak dua fase yang tidak saling tumpang-tindih

( non-overlap ), bagian kedua adalah penapis pelewat tinggi orde-3 kapasitor

tersaklar yang berfungsi meneruskan atau meloloskan arus listrik pada

frekuensi-frekuensi atau jangkauan frekuensi-frekuensi tertentu, serta menahan atau menghalangi

frekuensi lainnya. Masukannya berupa frekuensi yang dapat berubah-ubah yang

menggunakan AFG (Audio Function Generator). Output dari rangkaian ini

ditampilkan ke Osiloskop.

3.1. Tapis pelewat tinggi orde-3 kapasitor tersaklar

Perancangan hasil perhitungan untuk membangun tapis pelewat atas

dengan kapasitor tersaklar, dirancang dengan 2 perancangan dengan nilai

kapasitor utamanya yang berbeda untuk sebagai perbandingan. Untuk frekuensi

penggal = 3 Khz, dengan frekuensi penyaklaran 100 KHz, dan ditentukan

dan (sebagai kapasitor utama), seperti berikut ini:

nF

C =56 C =5,6nF

Perancangan dengan nilai kapasitor utama C = 56 nF

KHz

f0 =3

KHz

Fclk =100

nF C

C

C = 1 = 2 =56

Untuk Q1= 1

(

) (

)

clk clk R F C f F CC = ω0 = 2π 0 (dari persamaan 2-19)

(

)

KHz nF KHz CR 100 56 32 × ×

= π

nF

CR =10,55≅10,5

pF nF

CR =10 +500

Untuk Q = 1 2

(

) (

)

clk clk R F C f F CC 0 0

1

2 Q 2 Q

2 ω = π

= (dari persamaan 2-24)

(

)

KHz nF KHz CR 100 56 3 2 1 2 1 × × × × = π nFnF nF

CR1 =20 +1

clk clk R F C f F C C Q 2 2 Q 2 0 0 2 π ω =

= (dari persamaan 2-25)

KHz nF KHz CR 100 1 2 56 3 2

2 × ×

× ×

= π

nF

CR2 =5,27≅5,3

nF nF nF

CR2 =3,3 +1 +1

Perancangan dengan nilai kapasitor utama C=5,6nF

KHz

f0 =3

KHz

Fclk =100

nF C

C

C = 1 = 2 =5,6

Untuk Q1= 1

(

) (

)

clk clk R F C f F CC = ω0 = 2π 0

(dari persamaan 2-19)

(

)

KHz nF KHz CR 100 6 , 5 32 × ×

= π

nF

CR =1,055≅1,05

pF nF

CR =1 +50

Untuk Q = 1 2

(

) (

)

clk clk R F C f F CC 0 0

1

2 Q 2 Q

2 ω π

=

(

)

KHz nF KHz CR 100 6 , 5 3 2 1 2 1 × × × × = π nF CR1 =2,111≅2,1pF nF

CR1 =2 +100

clk clk R F C f F C C Q 2 2 Q 2 0 0 2 π ω =

= (dari persamaan 2-25)

KHz nF KHz CR 100 1 2 6 , 5 3 2

2 × ×

× ×

= π

pF

CR2 =527≅530

pF pF

pF

CR2 =330 +100 +100

Gambar 3-2. HPF Orde-3 menggunakan kapasitor tersaklar dengan nilainya

Penguatan operasi yang dipergunakan adalah LF 353N yang memiliki laju

lantingan

s V

μ

pelewat tinggi kapasitor tersaklar ini dipakai saklar CMOS 4016 yang memiliki

sekitar 200 Ohm. Tegangan maksimal saklar digital dan analognya ± 7,5

Vpeak. ON

R

IC tipe CD4016

Gambar 3-3. IC saklar CMOS 4016

3.2. Pembangkit detak dua fase non-overlap

Di dalam merancang untai tapis pelewat tinggi dengan kapasitor tersaklar

perlu diperhatikan adanya frekuensi detak yang akan mengaktfkan saklar-saklar

MOS yang dipergunakan, frekuensi detak ini memiliki peranan yang penting

dalam tapis ini, karena frekuensi detak ini yang menentukan watak tapis dengan

kapasitor tersaklar.Untai frekuensi detak untuk penyaklaran saklar MOS berupa

pembangkit detak dua fase yang tidak saling tumpang-tindih ( non-overlap ).

Untuk mendapatkan detak yang non-overlap digunakan rangkaian seperti pada

Gambar 3-4. Untai pembangkit detak dua fase non-overlap

Keluaran rangkaian ini berupa φ1 dan φ2, yang keduanya tidak saling tumpang-tindih. Besarnya frekuensi sinyal keluaran detak adalah setengah dari

frekuensi masukan. Sedang lebar sela antar φ1 dan φ2, ditentukan oleh konstanta waktu RC yang terdapat pada flip-flop pertama dari gambar 3-4.

Frekuensi masukan pembangkit detak dua fase non-overlap dihasilkan dari

pewaktu (clock). Dalam implementasi ini dipakai dari IC LM555. IC ini

merupakan IC pewaktu untuk keperluan umum yang dapat dikonfigurasikan untuk

menghasilkan waktu tunda yang akurat atau frekuensi osilasi.

IC ini diaplikasikan pada operasi stabil seperti pada gambar 3-5. Dalam

rangkaian ini kita dapat mengatur siklus kerja (duty cycle) gelombang

keluarannya. Frekuensi keluaran ini ditentukan oleh komponen RC, yakni resistor

dan kapasitor. Peroses pengisian muatan kapasitor pewaktu ekternal C dilakukan

melalui resistor eksternal RA+RB hingga mencapai nilai catu tegangan positif.

Ketika tegangan kapasitor mencapai level referensi batas atas komparator

( Vcc

3

berubah, yang selanjutnya akan menyalakan saklar transistor. Peluahan muatan

kapasitor terjadi melalui resistor hingga tegangan pada terminal-terminal

kapasitor jatuh menuju level referensi batas bawah komparator ( B

R

cc

V 3

1 ).

Komparator ini kemudian akan memaksa status rangkaian flip-flop untuk berubah

kembali yang selanjutnya akan mematikan saklar transistor.

Gambar 3-5. Diagram skematik fungsional pewaktu 555 untuk operasi osilator

Frekuensi osilasi sinyal rangkaian diberikan oleh persamaan ;

(

R R)

C fB

A 2

44 , 1

+

= . . . (3-1)

Karena frekuensi penyaklaran yang digunakan 100 KHz, maka frekuensi

keluaran dua kali frekuensi penyaklaran yaitu 200 KHz. Dari sini dapat

ditentukan perbandingan nilai dan dengan menentukan nilai C.

Jika . Maka diperoleh nilai sebagai berikut :

A

R RB

B

A R

R =

KHz

f =200

nF

C =1

B

A R

R

(

R R)

nF R nF KHzB

A 3 1

44 , 1 1

2 44 , 1 200

× =

+ =

nF KHz R

1 200

44 , 1 3

× =

Ohm

R 7200

3 =

Ohm

R =2400

Ohm R

BAB IV

PENGUJIAN DAN PEMBAHASAN

Setelah merancang, langkah selanjutnya adalah melakukan pengukuran

terhadap alat yang telah dibuat. Pengukuran dilakukan untuk mengetahui apakah

alat yang dibuat dapat berjalan sesuai dengan yang diinginkan. Pengukuran dan

analisa yang dilakukan adalah dengan mengamati tanggapan frekuensi tapis.

Tanggapan frekuensi tapis dinyatakan dalam besaran yang membandingkan

amplitudo sinyal keluaran dengan amplitudo sinyal masukan tapis.

Pengukuran dilakukan dengan beberapa macam frekuensi, yaitu frekuensi

audio yang nilainya antara 20 Hz sampai 20 kHz. Namun untuk mengetahui watak

tapis yang lebih baik jangkauan frekuensi pengamatan diperbesar sampai 50 khz.

Data-data dihitung dari perbandingan antara nilai-nilai amplitudo keluaran dengan

masukan. Sehingga membentuk tanggapan frekuensi tapis yang dinyatakan dalam

deciBell (dB). Perhitungan menggunakan persamaan (2-1).

Setelah mendapatkan tanggapan frekuensi, sistem dibuatkan grafik

hubungan antara dari dalam dB dengan frekuensi agar dapat mengetahui kurva

tanggapan tapis. Data-data pengamatan untuk tanggapan frekuensi tapis pelewat

tinggi ini tercantum dalam tabel 4-1. dan tabel 4-2.

Untuk membandingkan tanggapan frekuensi yang telah direalisasi dengan tapis

analog, perlu diketahui watak tapis teoritis dengan menghitung secara teoritis

yang tercantum pada tabel 4-1. dan tabel 4-2. dengan f0 =3kHz untuk orde

ketiga.

4.1. Pengamatan tanggapan frekuensi

Pengamatan pada alat untuk frekuensi penggal, , dengan

frekuensi penyaklaran 100 kHz, untuk amplitudo masukan dan nilai

kapasitor utama dan

kHz

f0 =3

Vpp

Vin =8

nF

C =56 C =5,6nF.

Contoh hitungan teoritis :

Hz f =1000

( )

(

)

dBf At ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎣ ⎡ + = 6 1000 3000 1 1 log 20

( )

f dBAt =-28.6332

Contoh hitungan pengujian:

Hz f =1000

Vpp

Vin =8

Vpp Vout =2.7

( )

dBVpp Vpp f A ⎥ ⎦ ⎤ ⎢ ⎣ ⎡ = 8 7 . 2 log 20

( )

f dB4.1.1. Tapis pelewat tinggi menggunakan kapasitor utama 56 nF

Tabel 4-1. Data hasil pengujian dengan kapasitor utama C =56nF

( )

fA

( )

dB Frekuensi( )

Hz Vout( )

Vpp-44.9975 20 0.045

-43.2545 60 0.055

-42.3552 100 0.061

-39.5762 200 0.084

-31.6174 300 0.21

-25.5968 400 0.42

-22.0749 500 0.63

-18.2372 700 0.98

-15.7829 800 1.30

-12.4867 900 1.90

-9.4345 1000 2.70

-6.2405 1500 3.90

-5.3924 1600 4.30

-4.2578 1750 4.90

-3.9103 2000 5.10

-3.9103 2250 5.10

-3.7417 2500 5.20

-3.4139 2750 5.40

-3.4139 3000 5.40

-3.3319 3121 5.45

-3.2545 3250 5.50

-2.9443 3500 5.70

-2.9443 3750 5.70

-2.2139 4000 6.20

-2.0749 4500 6.30

-1.9382 5000 6.40

-1.8035 6000 6.50

-1.8035 7000 6.50

-1.8035 9000 6.50

-1.8035 10000 6.50

-1.8035 12000 6.50

-1.5403 15000 6.70

-0.7953 20000 7.30

-0.7953 30000 7.30

-0.6771 40000 7.40

TANGGAPAN FREKUENSI

-3.3319

3121 -13.9794 dB/oktaf

-50 -40 -30 -20 -10 0

10 100 1000 10000 100000

Frekuensi ( Hz )

P

eng

ua

ta

n (

dB

)

Gambar 4-1. Kurva tanggapan frekuensi untuk kapsitor utama C=56nF

Dari tabel 4-1. dapat dibuat kurva tanggapan frekuensi seperti terlihat pada

gambar 4-1. Frekuensi penggal

( )

fo dapat dicari dengan menambahkan -3 dBdengan penguatan maksimum adalah -(0.3319 + 3) = -3.3319. Frekuensi

penggalnya adalah 3121 Hz dan bila diamati nilai penguatan pada saat frekuensi

masukan 200 Hz dan 400 Hz pada gambar 4-1. dapat diketahui nilai rolloff adalah

4.1.2. Tapis pelewat tinggi menggunakan kapasitor utama 5,6 nF

Tabel 4-2. Data hasil pengujian dengan kapasitor utama C =5,6nF

( )

fA

( )

dB Frekuensi( )

Hz Vout( )

Vpp-48.5793 20 0.030

-46.4661 60 0.038

-45.1927 100 0.044

-40.4455 200 0.076

-38.6921 300 0.093

-28.2345 400 0.31

-21.1598 600 0.70

-20.5605 700 0.75

-18.0617 800 1.00

-15.7829 900 1.30

-10.8272 1000 2.30

-5.3924 1500 4.30

-3.7417 1600 5.20

-3.6771 1687 5.23

-3.2545 1750 5.50

-2.7932 2000 5.80

-2.4987 2250 6.00

-2.0749 2500 6.30

-2.0749 2750 6.30

-2.0749 3000 6.30

-2.0749 3250 6.30

-2.0749 3500 6.30

-2.0749 3750 6.30

-1.6709 4000 6.60

-1.6709 4500 6.60

-1.6709 5000 6.60

-1.5403 6000 6.70

-1.5403 7000 6.70

-1.5403 9000 6.70

-1.5403 10000 6.70

-1.5403 12000 6.70

-1.4116 15000 6.80

-1.4116 20000 6.80

-1.4116 30000 6.80

-1.4116 40000 6.80

TANGGAPAN FREKUENSI

-17.5323 dB/oktaf

-3.6771

1687 -50

-40 -30 -20 -10 0

10 100 1000 10000 100000

Frekuensi ( Hz )

Pe

ng

ua

ta

n (

dB

)

Gambar 4-2. Kurva tanggapan frekuensi untuk kapsitor utama C =5,6nF

Dari tabel 4-2. dapat dibuat kurva tanggapan frekuensi seperti terlihat pada

gambar 4-2. Frekuensi penggal

( )

fo dapat dicari dengan menambahkan -3 dBdengan penguatan maksimum adalah -(0.6771+ 3) = -3.6771. Frekuensi

penggalnya adalah 1687 Hz dan bila diamati nilai penguatan pada saat frekuensi

masukan 300 Hz dan 600 Hz pada gambar 4-2. dapat diketahui nilai rolloff adalah

4.2. Pembahasan

1. Tapis pelewat tinggi (high-pass filter) orde ketiga menggunakan kapasitor

tersaklar untuk kapasitor utama C=56nF dengan frekuensi penggal

( )

sebesar 3121 Hz yang mendekati dengan yang dirancang yaitu 3 kHz. Nilai

rolloff sebesar - 13.9794 dB/oktaf. Ada selisih sekitar -4.0822 dB/oktaf dari

nilai rolloff secara teori (=- 18.0617 dB/oktaf ).

o

f

2. Tapis pelewat tinggi (high-pass filter) orde ketiga menggunakan kapasitor

tersaklar untuk kapasitor utama C=5,6nF dengan frekuensi penggal

( )

sebesar 1687 Hz, yang nilai frekuensi penggalnya tidak sesuai dengan yang

dirancang yaitu memiliki selisih 1313 Hz yang jauh dari frekuensi penggal

rancangan 3 kHz. Nilai rolloff sebesar -17.5323 dB/oktaf. Ada selisih sekitar

-0.5293 dB/oktaf dari nilai rolloff secara teori (=-18.0616 dB/oktaf ).

o

f

Beberapa hal yang menjadikan perbedaan tanggapan tapis yang dihitung

secara teori dan secara analisis yaitu :

1. Adanya hambatan ON (Ron) pada saklar yang dipakai dalam realisasi tapis,

akan menyebabkan penambahan nilai hambatan ekuivalen kapasitor tersaklar.

Dengan adanya hambatan ON (Ron) ini mengakibatkan pergeseran frekuensi

penggal dari tapis yang dirancang. Sebagai contoh untuk CMOS 4016 pada

tegangan sumber 12 volt mempunyai hambatan ON (Ron) sekitar 220 Ohm

Contoh hitungan frekuensi penggal untuk kapasitor utama C =56nF

2

1 C

C

C= =

kHz

Fclk =100

nF

CR1 =21

nF CR2 =5,3

Hambatan ekuivalen :

clk R

eq 1C F

R = ×

3 9

clk 1 R

1 1C F 121 10 100 10

R × × × = × = − Ohm 476,19 R1 =

3 9

clk 2 R

2 1C F 15,3 10 100 10

R × × × = × = − Ohm 1886,79 R2 =

frekuensi penggalnya :

2 1 2 1 0 1 C C R R =

ω (dari persamaan 2-9)

9 9 2 1 2 1 0 10 56 10 56 79 , 1886 19 , 476 1 1 2 − − × × × × × = = C C R R f π Hz f 9 9 0 10 56 10 56 79 , 1886 19 , 476 2 1 − − × × × × × = π Hz

Karena adanya hambatan ON (Ron) 220 Ohm

frekuensi penggalnya :

(

1)(

2)

1 20 1 C C R R R

R + on + on

=

ω

(

1)(

2)

1 20 1 2 C C R R R R f on on + + = π

(

)(

)

9 90 10 56 10 56 220 79 , 1886 220 19 , 476 2 1 − − × × × × + + = π f Hz

f0 =2346,70

Contoh hitungan frekuensi penggal untuk kapasitor utama C =5,6nF

2

1 C

C

C= =

kHz

Fclk =100

nF CR1 =2,1

pF

CR2 =530

Hambatan ekuivalen :

clk R

eq 1C F

R = ×

3 9

clk 1 R

1 1C F 12,1 10 100 10

R × × × = × = − Ohm 4761,9 R1 =

3 12

clk 2 R

2 1C F 1530 10 100 10

frekuensi penggalnya : 2 1 2 1 0 1 C C R R =

ω (dari persamaan 2-9)

9 9 2 1 2 1 0 10 6 , 5 10 6 , 5 9 , 18867 9 , 4761 1 1 2 − − × × × × × = = C C R R f π Hz f 9 9 0 10 6 , 5 10 6 , 5 9 , 18867 9 , 4761 2 1 − − × × × × × = π Hz

f0 =2998,33

Karena adanya hambatan ON (Ron) 220 Ohm

frekuensi penggalnya :

(

1)(

2)

1 20 1 C C R R R

R + on + on

=

ω

(

1)(

2)

1 20 1 2 C C R R R R f on on + + = π

(

)(

)

9 90 10 6 , 5 10 6 , 5 220 9 , 18867 220 9 , 4761 2 1 − − × × × × + + = π f Hz

f0 =2914,44

2. Nilai hambatan ekivalen dari kapasitor tersaklar ditentukan oleh frekuensi

penyaklaran, dengan hubungan

clk R

eq 1C F

Tabel 4-3. Frekuensi penyaklaran

( )

Fclk(

Fclk perancangan( )

Fclk pengamatan100 kHz 66,661 kHz

Contoh perhitungan

( )

Req teoritis untuk CR1 =21nF :kHz

Fclk =100

Ohm 3 9 -clk R1

eq1 1C F 121 10 100 10

R × × × = × = Ohm 476,19 Req1 =

Contoh perhitungan

( )

Req pengujian untuk CR1 =21nF :kHz

Fclk =66,661

Ohm 3 9 -clk R1

eq1 1C F 121 10 66,661 10

R × × × = × = Ohm 714,34 Req1 =

Dengan mengambil nilai tetap, maka dengan adanya penurunan frekuensi

penyaklaran dapat mengakibatkan pembesaran hambatan ekuivalennya

R

C

(

Fclk( )

Req ataupun sebaliknya. Perubahan frekuensi penyaklaran mempengaruhiperubahan tanggapan frekuensi tapis.

)

BAB V

PENUTUP

5.1. Kesimpulan

Dalam mengkaji secara teknis dari pembahasan dan pengolahan data pada

bab sebelumnya, maka bisa diiambil kesimpulan sebagai berikut :

1. Alat bekerja kurang baik karena tidak sesuai dengan yang diharapkan

dalam perancangan.

2. Hambatan ekuivalenya dipengaruhi adanya hambatan ON dan frekuensi

penyaklaran yang tidak sesuai dengan yang dirancang. Sehingga adanya

pergeseran frekuensi penggal dan perubahan tanggapan frekuensi tapis.

5.2. Saran

Dari kesimpulan diatas ada beberapa saran yang dapat diajukan sebagai

bahan pertimbangan dari penulis antara lain :

1. Tapis pelewat tinggi menggunakan kapasitor tersaklar ini dapat

dikembangkan lebih lanjut dengan cara menambah jumlah orde penapis

dan memperbaiki nilai faktor kualitasnya.

2. Kapasitor tersaklar ini dapat diimplementasikan dalam penapis-penapis

lainnya, seperti tapis pelewat bawah (low pass filter), tapis pelewat jalur

3. Untuk frekuensi penyaklarannya dapat dibuat variasi dengan mengubah

nilai hambatan pada untaian pewaktu (clock).

4. Untuk merancang suatu penapis menggunakan kapasitor tersaklar

hendaknya diperhatikan nilai kapasitor-kapasitor yang digunakan,

DAFTAR PUSTAKA

Huelsman, Lawrence p, University of Arizona, “Aktive and Passive Analog Filter

Design”, McGraw-Hill Inc, 1993.

Malvino, Albert Paul, diterjemahkan oleh Ir. Joko, Alb.MT, “Prinsip-prinsip

Elektronika”, Salemba Teknikal, Jakarta, 2004.

Http://www.all-data-sheet.com, 2007.

Http://www.datasheetcatalog.com, 2007.

Http://www.fairchildsemi.com, 2007.

VCC -VCC EN 1 1 1 > > < < 4016 2 1 13 + -LF353 3 2 1 8 4 56 nF + -LF353 3 2 1 8 4 56 nF 200 4093 1 2 3 21 nF 56 nF EN1 1 1 > > < < 4016 2 1 13 10,5 nF 4013 5 3 1 2 6 4 Q D CLK Q S R 1 nF 1 2 3 2.4 K 2.4 K 100 nF 5 2 NE555 3 7 6 4 TR CV Q DIS THR R EN 1 1 1 > > < < 40 16 2 1 13 -VCC EN 1 1 1 > > < < 40 16 2 1 13 4093 1 2 3 EN1 1 1 > > < < 4016 2 1 13 4013 5 3 1 2 6 4 Q D CLK Q S R 5,3 nF VCC EN 1 1 1 > > < < 40 16 2 1 13 50 2 1 3 OUTPUT

4093 4093

INPUT

-VCC

TAPIS PELEWAT TINGGI KAPASITOR TERSAKLAR UNTUK C = 56 nF Title

A

VCC -VCC EN 1 1 1 > > < < 401 6 2 1 13 + -LF353 3 2 1 8 4 5,6 nF + -LF353 3 2 1 8 4 5,6 nF 200 4093 1 2 3 2,1 nF 5,6 nF EN1 1 1 > > < < 4016 2 1 13 1,05 nF 4013 5 3 1 2 6 4 D CLK Q Q S R 1 nF 1 2 3 2.4 K 2.4 K 100 nF 5 2 NE555 3 7 6 4 TR CV Q DIS THR R EN 1 1 1 > > < < 40 16 2 1 13 -VCC EN 1 1 1 > > < < 40 16 2 1 13 4093 1 2 3 EN1 1 1 > > < < 4016 2 1 13 4013 5 3 1 2 6 4 D CLK Q Q S R 530 pF VCC EN 1 1 1 > > < < 4 016 2 1 13 50 2 1 3 OUTPUT

4093 4093

INPUT

-VCC

TAPIS PELEWAT TINGGI KAPASITOR TERSAKLAR UNTUK C = 5,6 nF Title

A

www.fairchildsemi.com

LF3 5 3

Dua l Ope ra t iona l Am plifie r (J FET )

Features Description

• Internally trimmed offset voltage: 10mV The LF353 is a JFET input operational amplifier with an

• Low input bias current: 50pA internally compensated input offset voltage. The JFET input

• Wide gain bandwidth: 4MHz device provides wide bandwidth, low input bias currents and

• High slew rate: 13V/µs offset currents.

• High Input impedance: 1012Ω

8-DIP

1

8-SOP

1

LF353

Schematic Diagram

(One Section Only)

Absolute Maximum Ratings

Parameter Symbol Value Unit

Power Supply Voltage VCC ±18 V

Differential Input Voltage VI(DIFF) 30 V

Input Voltage Range VI ±15 V

Output Short Circuit Duration - Continuous

-Power Dissipation PD 500 mW

Operating Temperature Range TOPR 0 ~ +70 °C

LF353

Electrical Characteristics

(VCC =+15V, VEE= -15V, TA=25 °C, unless otherwise specified)

Parameter

Input Offset Voltage

Input Offset Voltage Drift

Input Offset Current

Input Bias Current

Input Resistance

Large Signal Voltage Gain

Output Voltage Swing Input Voltage Range

Common Mode Rejection Ratio Power Supply Rejection Ratio Power Supply Current Slew Rate

Gain-Bandwidth Product

Channel Seperation

Symbol Conditions

RS=10KΩ

VIO

0 °C≤TA≤+70 °C

∆VIO/∆T RS=10KΩ 0 °C≤TA≤+70 °C

IIO

0 °C≤TA≤+70 °C

IBIAS

0 °C≤TA≤+70 °C

RI

-VO(P-P) = ±10V

GV

RL = 2KΩ 0 °C≤TA≤+70 °C

VO(P_P) RL = 10KΩ

VI(R)

-CMRR RS ≤ 10KΩ

PSRR RS ≤ 10KΩ

ICC

-SR GV = 1

GBW

-f = 1Hz ~ 20KHz CS (Input referenced) Min. -25 15 ±12 ±11 70 70

-Typ. Max. Unit

5.0 10 mV

- -

-10 - µV/ °C

25 100 pA

- 4 nA

50 200 pA

- 8 nA

1012 - Ω

100 - V/mV

- -

-±13.5 - V

±15/-12 - V

100 - dB

100 - dB

3.6 6.5 mA

13 - V/µS

4 - MHz

120 - dB

-RS = 100Ω nV/

Equivalent Input Noise Voltage VNI - 16

-f = 1KHz Hz

pA/

Equivalent Input Noise Current INI f = 1KHz - 0.01

LF353

Mechanical Dimensions

Package

8-DIP

6.40 ±0.20

3.30 ±0.30 0.130 ±0.012

3.40 ±0.20 0.134 ±0.008 #1

#4 #5

#8 0.252 ±0.008

9.20

±

0.20

0.79

2.54 0.100

0.031

(

)

0.46

±

0.10

0.018

±

0.004

0.060

±

0.004

1.524

±

0.10

0.362

±

0.008

9.60 0.378

MAX

5.08 0.200

0.33 0.013 7.62

0~15°

0.300

MAX

MIN

0.25 +0.10–0.05

LF353 Mechanical Dimensions Package

8-SOP

0.1~0.25 MIN 0.004~0.001 4.92 ± 0.20 0.194 ± 0.008 0.41 ± 0.10 0.016 ± 0.004 1.27 0.050 5.72 0.2251.55 ±0.20 0.061 ±0.008

6.00 ±0.30 0.236 ±0.012

3.95 ±0.20 0.156 ±0.008

0.50 ±0.20 0.020 ±0.008

5.13 0.202

MAX

#1

#4 #5

LF353

Ordering Information

Product Number Package Operating Temperature

LF353N 8-DIP

0 ~ + 70°C

LF353M 8-SOP

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support

which, (a) are intended for surgical implant into the body, device or system whose failure to perform can be

or (b) support or sustain life, and (c) whose failure to reasonably expected to cause the failure of the life support

perform when properly used in accordance with device or system, or to affect its safety or effectiveness.

This datasheet has been download from:

www.datasheetcatalog.com

November 1983 Revised March 2002

CD401 6BC Quad Bi la ter a l Sw itc h

CD4016BC

Quad Bilateral Switch

General Description

The CD4016BC is a quad bilateral switch intended for the transmission or multiplexing of analog or digital signals. It is pin-for-pin compatible with CD4066BC.

Features

■ Wide supply voltage range: 3V to 15V

■ Wide range of digital and analog switching: ±7.5 VPEAK

■ “ON” Resistance for 15V operation: 400Ω (typ)

■ Matched “ON” Resistance over 15V signal input:

∆RON = 10Ω (typ) ■ High degree of linearity:

0.4% distortion (typ) @ fIS = 1 kHz, VIS = 5 Vp-p,

VDD−VSS = 10V, RL = 10 kΩ ■ Extremely low “OFF” switch leakage:

0.1 nA (typ.) @ VDD − VSS = 10V

TA = 25°C

■ Extremely high control input impedance: 1012Ω (typ) ■ Low crosstalk between switches:

−50 dB (typ.)

@ fIS = 0.9 MHz, RL = 1 kΩ

■ Frequency response, switch “ON”: 40 MHz (typ)

Applications

• Analog signal switching/multiplexing Signal gating

Squelch control Chopper

Modulator/Demodulator Commutating switch

• Digital signal switching/multiplexing • CMOS logic implementation

• Analog-to-digital/digital-to-analog conversion • Digital control of frequency, impedance, phase, and

analog-sign