LAPORAN PRAKTIKUM

SISTEM DIGITAL

Disusun oleh :

1. Agatha Elisabet S 1610631160005 2. Andi Boy Panroy 1610631160022 3. Ryan Ramadhan 1610631160129 4. Salsanabila M. Putri 1610631160130

LABORATORIUM DASAR TEKNIK ELEKTRO

FAKULTAS TEKNIK

UNIVERSITAS SINGAPERBANGSA KARAWANG

1.1

Tujuan Percobaan

1. Mengenal dan memahami beberapa karakteristik dari gerbang logika diantarannya voltage transfer, noise margin, dan propagation delay.

2. Mengenal dan memahami parameter dari gerbang logika yaitu operating point yang merepresentasikan range logika HIGH dan LOW.

3. Dapat membuat rangkaian kombinansional sederhana menggunakan IC logika CMOS.

1.2

Alat dan Bahan

1. Kit praktikum Gerbang Logika NOR TTL dan Parameter Gerbang Logika

2. Power Supply, Osiloskop dan Generator Sinyal 3. Komponen IC gerbang logika 7400,7404 4. Kabel jumper secukupnya

5. 1 buah Kabel BNC, 2 buah kabel Probe Kait / BNC-Jepit Buaya / BNC-Banana

6. 2 buah kabel Banana-Banana / Banana-Jepit Buaya merah dan hitam. voltage dari sebuah inverter 74LS04 dan inverter CMOS 4007.

Langkah Percobaan :

1. Digunakan kit praktikum Parameter Gerbang Logika Percobaan 1A dan 1B.

minimum keluaran adalah 0 V. Digunakan port OUTPUT sebagai keluaran bukan port TTL/CMOS. Di cek keluaran sinyal generator menggunakan osiloskop dengan mode coupling DC sebelum menyambungkannya dengan inverter karena dapat merusak IC.

3. Disambungkan output generator sinyal ke input gerbang logika (IN).

4. Disambungkan kanal 1 osiloskop dengan input gerbang logika (IN).

5. Disambungkan kanal 2 osiloskop dengan output gerbang logika (OUT).

6. Diatur setting power supply pada tegangan 5 V dan disambungkan dengan VCC dan GND.

7. Diatur setting osiloskop dengan mode X-Y. Sebelum melakukan pengamatan, diatur posisi sinyal pada mode X-Y dengan menekan tombol GND pada kedua kanal masukan hingga terlihat 1 titik kecil, ditempatkan titik yang terlihat pada tengah osiloskop / sumbu koordinat. Setelah itu ditekan tombol GND kembali untuk pengamatan bentuk sinyal.

8. Dilihat keluaran osiloskop, apakah mirip dengan gambar referensi ataukah terdapat perbedaannya.

9. Dicatat hasil percobaan pada BCL.

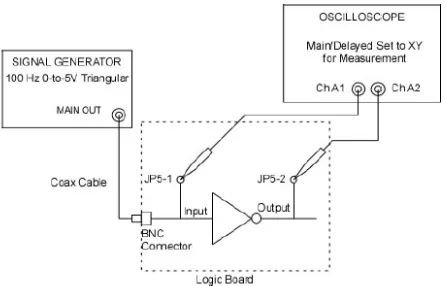

Gambar 1: rangkaian dalam percobaan

MENCARI NILAI NML DAN NMH

Pada percobaan ini dicari karakteristik static noise margin dari sebuah IC-74LS04 dan inverter CMOS 4007.

Langkah Percobaan :

1. Digunakan kit praktikum Parameter Gerbang Logika Percobaan 1A dan 1B.

2. Digambar kembali pada logbook keluaran mode X-Y dari percobaan sebelumnya.

3. Dilakukan langkah berikut untuk inverter TTL 74LS04.

4. Ditukarkan posisi probe osiloskop kanal 1 dan kanal 2 sehingga posisinya bertukar dari percobaan 1 (kanal 1 terhubung dengan output IC dan kanal 2 dengan input IC).

5. Didapatkan sinyal keluaran inverter dalam mode X-Y.

6. Kemudian digambarkan pula sinyal tersebut secara manual pada bidang gambar yang sama pada langkah a sehingga kedua gambar akan saling bertumpukan dan memberntuk seperti pada gambar a.

7. Dicantumkan gambar serta hitungan nilai.

8. Nilai posisi VOL, VOH, VIL, dan VIH dengan ketelitian 1 desimal.

9. Dibandingkan nilai NMH dan NML yang didapat dair percobaan berdasarkan rumus yang sudah diberikan dengan nilai yang tertera pada datasheet.

10. Dicatat hasil percobaan pada BCL.

11. Diulangi langkah D sampai I (percobaan 2) untuk inverter CMOS 4007.

1.3.3 Percobaan 1C

DELAY PROPAGASI

kemampuan osiloskop maka kita akan menggunakan konfigurasi 4 buah gerbang yang diserikan.

Dengan konfigurasi ini hasil delay propagasi yang didapatkan harus dibagi empatterlebih dahulu untuk mendapatkan nilai sebenarnya.

Langkah Percobaan :

1. Digunakan kit praktikum Parameter Gerbang Logika Percobaan 1.

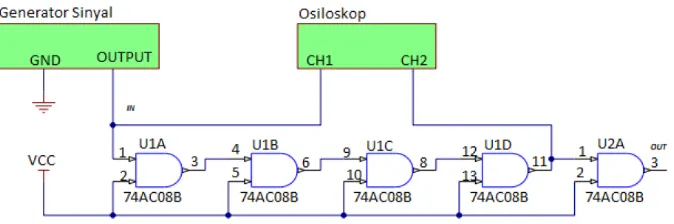

2. Disusun rangkaian seperti gambar 6 dibawah dengan kondisi seluruh alat dimatikan.

3. Kemudian disambungkan power supply dengan VCC dan GND kit praktikum.

4. Dinyalakan power supply.

5. Diubah setting triggering menggunakan tombol slope menjadi positive edge.

6. Diatur setting setiap kanal input manjadi 1V/div . disambungkan ground channel 1 dan channel 2 dan diatur setting TIME/DIV ke posisi terendah osiloskop yaitu 0.2 us atau 200 ns.

7. Diatur setting keluaran generator sinyal menjadi sinyal kotak dengan frekuensi 300 kHz. Digunakan port OUTPUT sebagai keluaran. Dicek keluaran sinyal generator menggunakan osiloskop sebelum menyambungkannya dengan gerbang logika kalau tidak bisa menyebabkan kerusakan.

8. Ditampilkan keluaran dari kedua kanal sehingga bentuk pulsa pada saat naik pada kanal 1 dan kanal 2 bisa diamati secara utuh. 9. Digunakan tombol X1/MAG untuk memperbesar hasil yang didapatkan, kemudian ditekan tombol x5-x10x20 dan diperbesar hingga 10 x agar lebih jelas terlihat.

10. Diatur posisi vertical kedua sinyal sehingga posisi 50% berada di sumbu X (nilai sinyal diatas dan dibawah sumbu X ada masing-masing kanal sama).

11. Digambarkan hasil yang didapat.Diubah setting triggering menjadi negative edge dan diulangi semua langkah diatas. 12. Digambarkan hasil yang didapatkan.

13. Digunakan nilai tPLH dan tPHL yang didapatkan untuk mencari tPD

dan tPD(average) menggunakan rumus yang telah diberikan

14. Dibaca datasheet dari 74LS08, kemudian dibandingkan tPD dan

tPD(average) yang didapatkan pada percobaan dengan rentang nilai

yang tertulis pada datasheet.

Gambar 2 Bentuk rangkaian percobaan 3

1.3.4 Percobaan 1D

VERIFIKASI FUNGSI LOGIKA

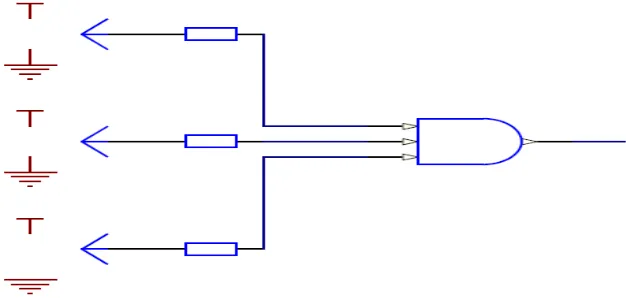

Diberikan sebuah IC logika yang nomor serinya disamarkan. IC yang digunakan memiliki 3 input, dilihat datasheet IC logika CMOS 3 input apa saja untuk verifikasi posisi pin karena semuanya memliki posisi pin yang sama.

Langkah Percobaan :

a. Digunakan kit praktikum Parameter Gerbang Logika Percobaan 1D.

b. Digunakan salah satu kanal masukan osiloskop untuj mengukur tegangan keluaran dari gerbang logika yang diukur serta voltmeter pada pin OUT.

Gambar 3 : Bentuk rangkaian untuk percobaan 1d

a. Dibuat persamaan logika : Q = A + B, menjadi persamaan yang hanya memuat operasi NAND atau NOR saja.

b. Dirancang dan digambar rangkaiannya pada logbook, kemudian dibuat rangkaiannya dari IC CMOS 7400 yang tersedia pada project-board.

c. Diverifikasi fungsionalitas rangkaian dengan memberikan kombinasi berbagai input yang mungkin, dicatat dan dibandingkan hasilnya dengan true table yang diharapkan.

1.2.6 Percobaan 1F

GERBANG LOGIKA NOR TTL

Langkah Percobaan :

b. Dihubungkan VCC dan GND ke power supply 5 V, dihubungkan multimeter pada terminal OUT untuk mengukur tegangan.

c. Diberikan input IN A, IN B, IN C logika 0 (tegangan 0 V), baca tegangan pada OUT. Dicatat nilai tegangan di seluruh simpul rangkaian.

d. Diubah salah satu nilai input menjadi logika 1 (tegangan 5 V), dibaca tegangan pada OUT. Dicatat nilai tegangan di seluruh simpul rangkaian

e. Diubah dua nilai input menjadi logika 1 (tegangan 5V) dibaca tegangan pada OUT.

f. Diubah semua nilai input menjadi 1 (tegangan 5V), dibaca tegangan pada OUT.

1.4 Data Percobaan

1.4.1 PERCOBAAN 1A

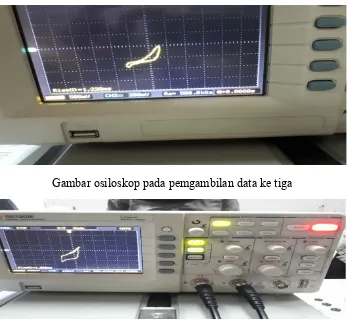

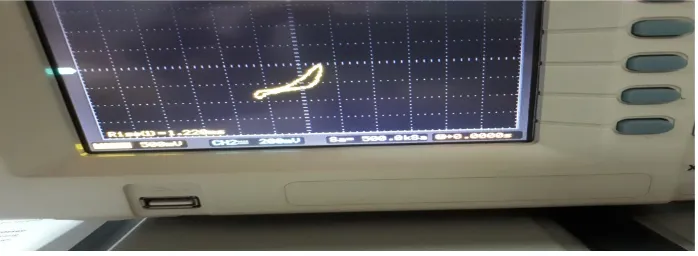

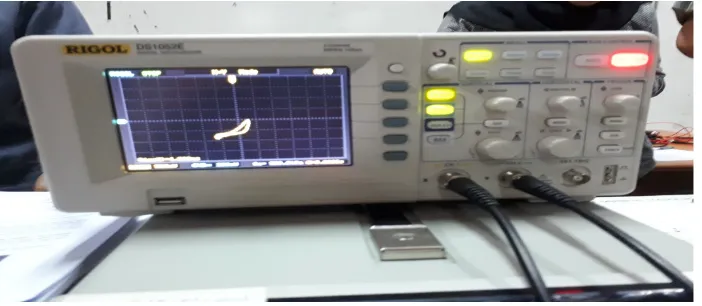

Gambar osiloskop pada pemgambilan data ke dua

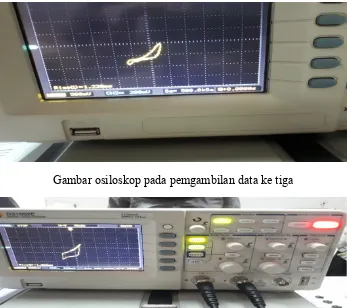

Gambar osiloskop pada pemgambilan data ke tiga

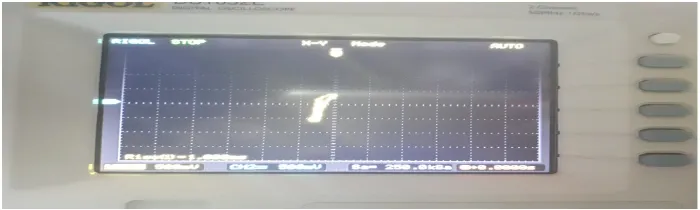

Gambar osiloskop pada pemgambilan data ke lima

1.4.2 PERCOBAAN 1B

Gambar osiloskop pada pemgambilan data ke satu

Gambar osiloskop pada pemgambilan data ke tiga

Gambar osiloskop pada pemgambilan data keempat

1.4.4 PERCOBAAN 1D

1.4.5 PERCOBAAN 1E

1.7 REFERENSI

https://id.scribd.com/document_downloads/363526963?

extension=docx&secret_password=53LFundxIXj8WK3X2WmZ

http://www.electroschematics.com/6529/7400-datasheet/