4/21/2015 Sistem Pengaturan dan Pemantauan Kecepatan Putar Motor DC berbasis FPGA dan VHDL | Agfianto Eko Putra Academia.edu

Sistem Pengaturan dan Pemantauan Kecepatan Putar

Motor DC berbasis FPGA dan VHDL

Log In Sign Up

Agfianto Eko Putra

Info

DownloadUploaded by PDF

SITIA 2013, Surabaya

Sistem Pengaturan dan Pemantauan Kecepatan Putar Motor DC

berbasis FPGA dan VHDL

Agfianto Eko Putra

1, Rahadian Mu’alif

2

1,2Program Studi Elektronika dan Instumentasi, Jurusan Ilmu Komputer dan Elektronika, Fakultas MIPA Universitas Gadjah Mada - Yogyakarta 55281

1[email protected] , 2[email protected]

Abstrak - Telah diimplementasikan sebuah rangkaian digital untuk pengaturan dan pemantauan kecepatan putar motor DC ke dalam FPGA Altera EPF10K10

menggunakan VHSIC Hardware Description

Language (VHDL). Sistem terdiri dari rangkaian penggerak dan rangkaian pembaca kecepatan putar motor DC. Sistem ini dapat menggerakkan motor DC dengan 10 variasi kecepatan dan besarnya kecepatan putar tersebut ditampilkan melalui 7-Segmen. FPGA menghasilkan luaran Pulse Width Modulation (PWM) untuk menggerakkan motor DC. Besarnya kecepatan

putar motor DC dibaca oleh sensor optokoplerkemudian diteruskan ke FPGA untuk ditampilkan

nilainya melalui 7-segmen dalam satuan Rotasi per Detik (RPD). Hasil pengujian luaran PWM pada FPGA menggunakan metode regresi linier, diperoleh ralat sebesar 0,04. Hasil pengujian kecepatan putar motor DC untuk arah putaran searah jarum jam yaitu dengan ralat sebesar 0,70. Sedangkan untuk yang berlawanan jarum jam diperoleh ralat sebesar 0,75. Jumlah LE dalam FPGA yang digunakan adalah 262

atau 45% dari kapasitas total LE yang dimiki FPGA Altera EPF10K10.

Kata kunci: FPGA, VHDL, PWM, Motor DC

1. PENDAHULUAN

Kendali PWM adalah suatu teknik pengendalian rangkaian analog dengan suatu keluaran pengolah digital [1]. Keluaran pengolah digital ini berupa pulsa dengan periode tertentu, dimana lebar pulsahigh-nya divariasikan. PWM ini biasanya digunakan dalam pengiriman data digital, regulasi tegangan, efek suara,

dan penguatan.

Motor DC bisa diatur kecepatan putarnya melalui

Pulse Width Modulation atau PWM, dengan

memanfaatkan chip FPGA sebagai inti rangkaian pengendalinya. Besarnya kecepatan putar motor DC (Rotasi per Detik atau RPD) dibaca oleh sensor dan ditampilkan melalui 7-Segmen juga menggunakan FPGA. Penggunaan FPGA ini diharapkan dapat

menggunakan luaran PWM yang dihasilkan melalui rangkaian digital yang diimplementasikan ke dalam FPGA Altera EPF10K10 dengan 10 macam variasi PWM (sekaligus 10 macam kecepatan putar).

Sebagaimana ditunjukkan pada Gambar 1, digunakan dua buah tombol (SW1 dan SW2) yang masing-masing digunakan untuk melebarkan pulsahigh PWM dan menyempitkan lebar pulsa high PWM. Dengan melebarnya pulsahigh PWM maka motor DC berputar makin cepat, sebaliknya dengan menyempitnya pulsa

high PWM maka motor berputar makin lambat. Saklar geser ataudipswitch digunakan untuk mengatur arah perputaran motor DC yaitu searah atau berlawanan jarum jam. Luaran FPGA yang berupa sinyal PWM dihubungkan dengan rangkaian penggerak motor DC.

Selanjutnya, kecepatan putar motor DC dibaca oleh sensorrotary plate yang luarannya berupa pulsa yang kemudian diumpankan ke FPGA untuk proses pembacaan, hasilnya ditampilkan dalam ratusan (tiga

digit) melalui 7-segmen.

2.1. Modul Pembagi Frekuensi

Modul ini digunakan untuk membagi frekuensi yang dihasilkan oleh osilator agar sesuai dengan kebutuhan detak modul rangkaian yang lain. Dalam hal ini osilator detak pada papan perancangan memiliki

frekuensi sebesar 9,6 MHz. Berikut kode VHDL-nya:

LI BRARY I EEE;

USE I EEE. STD_LOGI C_1164. ALL; USE I EEE. STD_L OGI C_UNSI GNED. ALL;

ENTI TY Pembagi _Fr ekuensi I S PORT ( Cl k : i n s t d_ l ogi c ; Cl ock1 : out st d_l ogi c; Cl ock2 : out std_l ogi c); END Pembagi _Fr ekuensi ;

ARCHI TECTURE Behavi or al OF Pembagi _F r ekuensi I S

SI GNAL Count er : st d_l ogi c_vect or ( 23 downto 0) ;

Search...

Modul ini digunakan untuk mengurangi efek bouncing yang biasa terjadi jika pushbutton pada papan

pengembangan wizard FLEX-A01 ditekan. Berikutkode VHDL-nya:

LI BRARY I EEE;

USE I EEE. STD_LOGI C_1164. ALL;

ENTI TY Debouncer I S PORT(

2.3. Modul Pencacah Naik Turun

Modul ini digunakan sebagai pencacah naik dan turun, mulai dari 1 sampai dengan 10, yang kemudian diumpankan luarannya ke modul penghasil PWM.

2.4. Modul Penghasil PWM

Pengaturan kecepatan putaran dilakukan dengan menggunakan menggunakan Pulse Width Modulation atau biasa disingkat sebagai PWM. Teknik PWM

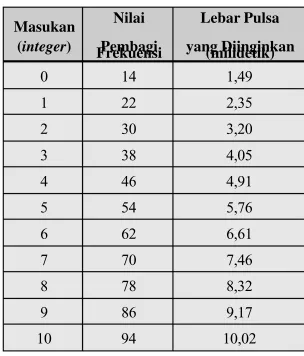

adalah cara pengalihan daya menggunakan sistem lebar pulsa untuk mengemudikan kecepatan motor. Pengaturan lebar pulsa ini menentukan kecepatan putar motor. Hubungan antara masukan terhadap

luaran PWM ditunjukkan pada Tabel 1.

Berikut kode VHDL untuk modul yang menghasilkan sinyal PWM:

LI BRARY I EEE;

USE I EEE. STD_LOGI C_1164. ALL; USE I EEE. STD_L OGI C_UNSI GNED. ALL;

SI GNAL count er : i nt eger;

Tabel 1. Hubungan Masukan dan Luaran PWM

Masukan

Modul ini digunakan menentukan arah berputarnya motor DC apakah searah jarum jam atau berlawanan. Berikut kode VHDL-nya:

LI BRARY I EEE;

USE I EEE. STD_LOGI C_1164. ALL;

4/21/2015 Sistem Pengaturan dan Pemantauan Kecepatan Putar Motor DC berbasis FPGA dan VHDL | Agfianto Eko Putra Academia.edu dengan masukan pada modul pencacah RPD.

2.7. Modul Pencacah RPD

Modul ini digunakan untuk menghitung banyaknya rotasi perputaran motor tiap detik. Berikut kode VHDL-nya:

LI BRARY I EEE;

USE I EEE. STD_LOGI C_1164. ALL; USE I EEE. STD_L OGI C_UNSI GNED. ALL;

ENTI TY Pencacah_RPD I S PORT( Cl oc k : i n s t d_ l ogi c ; Reset : i n std_l ogi c;

Q : out st d_l ogi c_vect or ( 7 downt o 0) ) ; END Pencacah_ RPD;

ARCHI TECTURE Behavi or al OF Pencacah_RPD I S

SI GNAL qi : st d_l ogi c_vect or ( 7 downt o 0) ;

2.8. Modul Konversi Biner BCD

Modul ini merupakan modul pengkonversian bilangan

dalam format biner ke Binary Coded Decimal (BCD) untuk keperluan tampilan 3x7-segmen. Berikut VHDL-nya:

LI BRARY I EEE;

USE I EEE. STD_LOGI C_1164. ALL; USE I EEE. STD_L OGI C_UNSI GNED. ALL;

ENTI TY Konver si _Bi n_BCD I S PORT(

Bi ner : i n STD_LOGI C_VECTOR ( 7 downt o 0) ; BCD: out STD_LOGI C_VECTOR ( 15 downt o 0) ) ; END Konver si _Bi n_BCD;

ARCHI TECTURE Behavi or al OF Konversi _Bi n_BCD I S

Modul ini digunakan sebagai pemilih dalam menentukan data dan 7-Segmen mana yang digunakan untuk menampilkan data tersebut.

2.10. Modul Multiplekser Tampilan

Modul ini merupakan modul multiplekser atau dapat dikatakan sebagai pemilih dari 3 data yang akan ditampilkan melalui 7-Segmen. Data tersebut berupa sebuah bilangan biner 16 bit dimana 12 bit terendah merepresentasikan 3 data yang dimaksud.

2.11. Modul Multiplekser 7-Segment

Modul ini diperlukan karena karakteristik tampilan 3x7-Segmen yang digunakan merupakan rangkaian multipleks. Walaupun agak rumit mengoperasikannya namun rangkaiannya menjadi lebih sederhana.

2.12. Modul Enkoder 7-Segmen

Modul ini digunakan untuk mengkonversikan kode dalam bentuk BCD ke led-led yang sesuai dalam 7-segmen.

3. RANCANGANSISTEMANALOG

3.1. Rangkaian Penggerak Motor DC

Rangkaian ini berfungsi sebagai penggerak (driver ) berputarnya motor DC dan pengkondisi sinyal luaran optokopler menjadi gelombang kotak sempurna.

Rangkaian ini terdiri dari rangkaian catudaya, penggerak motor DC dan Pemicu Schmitt,

sebagaimana ditunjukkan pada Gambar 2.

3.2. Rangkaian Optokopler

Optokopler adalah bagian penting dari sensor kecepatan putar motor DC. Rotary plate yang digunakan yaitu sebuah piringan dengan satu buah lobang dipinggirnya. Optokopler sebagai penghasil pulsa yang nantinya dikirim ke FPGA, sebagaimana

Job Board About Press Blog Stories Terms Privacy Copyright We're Hiring! Help Center